802 1 D Spanning Tree Compliant switch Gireesh

- Slides: 12

802. 1 D Spanning Tree Compliant switch Gireesh Shrimali, Jeslin Puthenparambil EE 384 Y Course Project 06/04/2003

Outline o o Features System Architecture Hardware Architecture Software n n o Architecture Software-Hardware interaction Test topologies

Features o 8 x 8 layer 2 switch n o o External SRAM (statically allocated) for packet storage Performs address learning - Max 4 addresses per port Implements 802. 1 D spanning tree protocol running from an external server

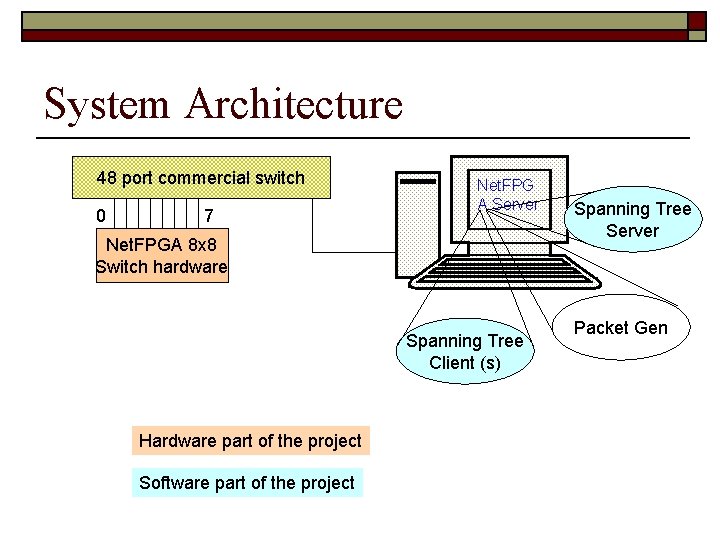

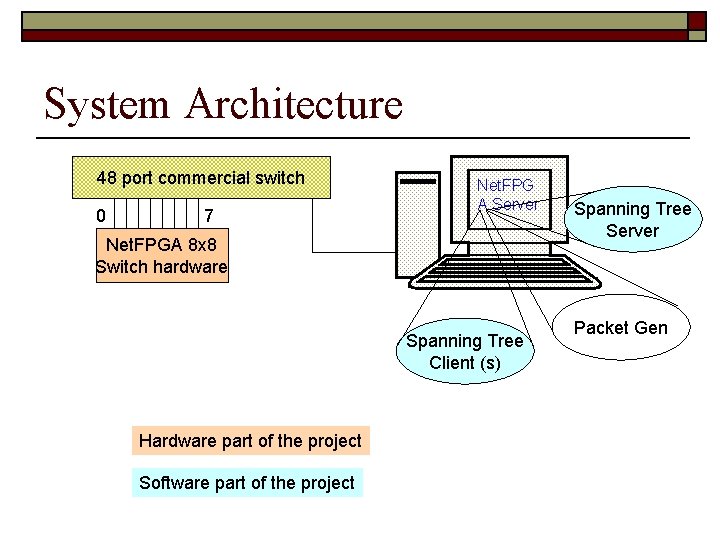

System Architecture 48 port commercial switch 0 7 Net. FPG A Server Net. FPGA 8 x 8 Switch hardware Spanning Tree Client (s) Hardware part of the project Software part of the project Spanning Tree Server Packet Gen

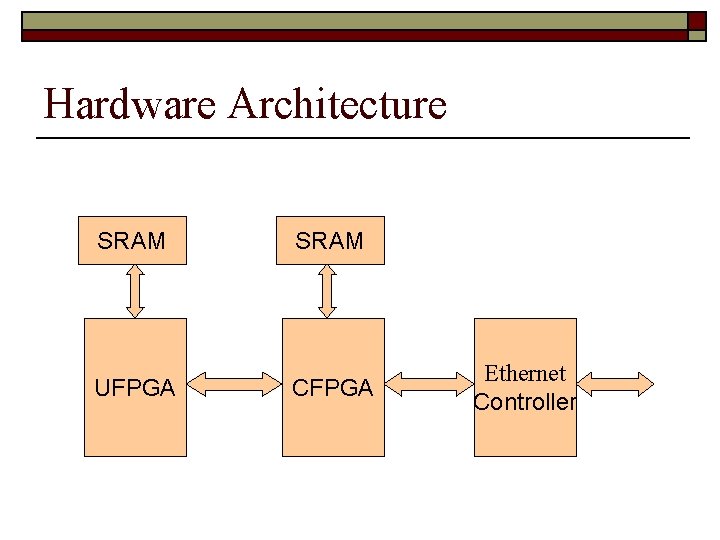

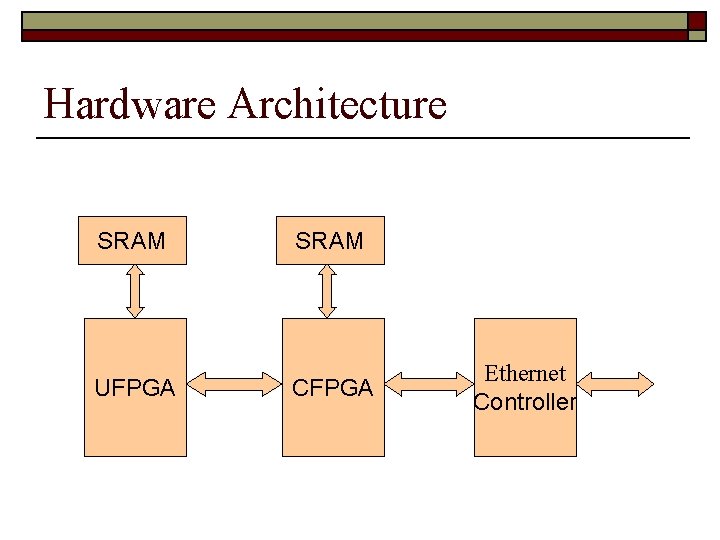

Hardware Architecture SRAM UFPGA CFPGA Ethernet Controller

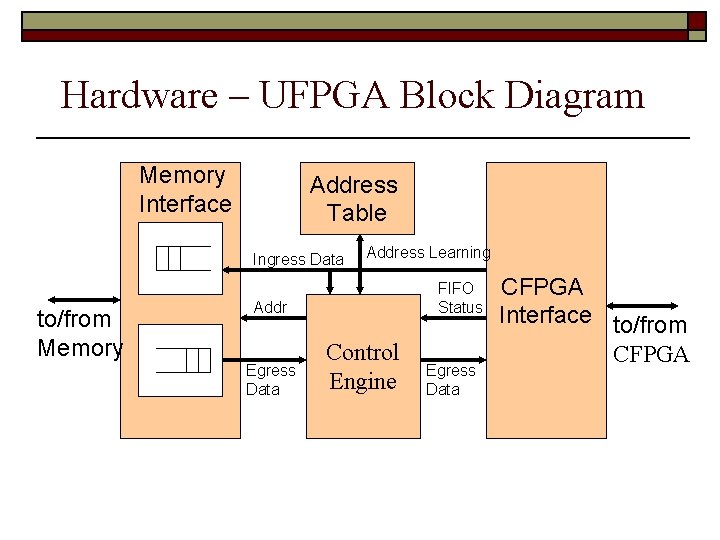

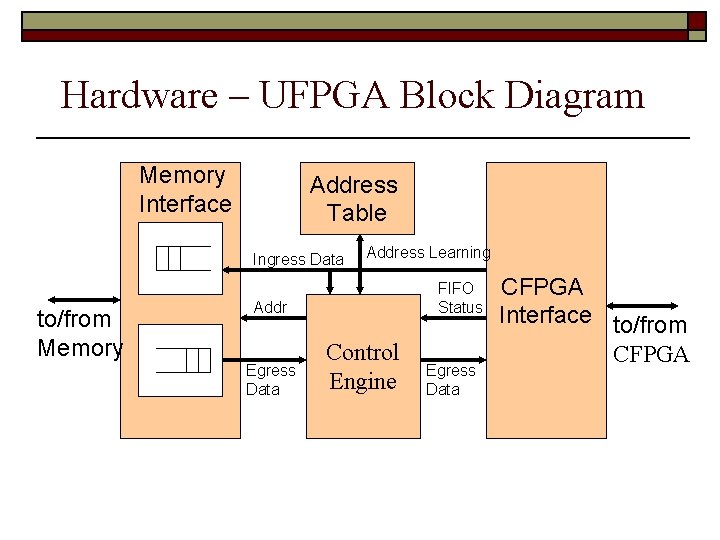

Hardware – UFPGA Block Diagram Memory Interface Address Table Ingress Data to/from Memory Address Learning FIFO Status Addr Egress Data Control Engine Egress Data CFPGA Interface to/from CFPGA

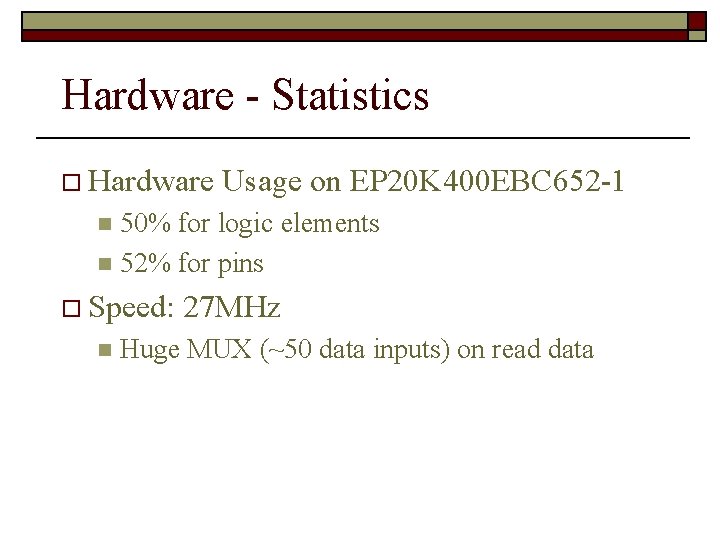

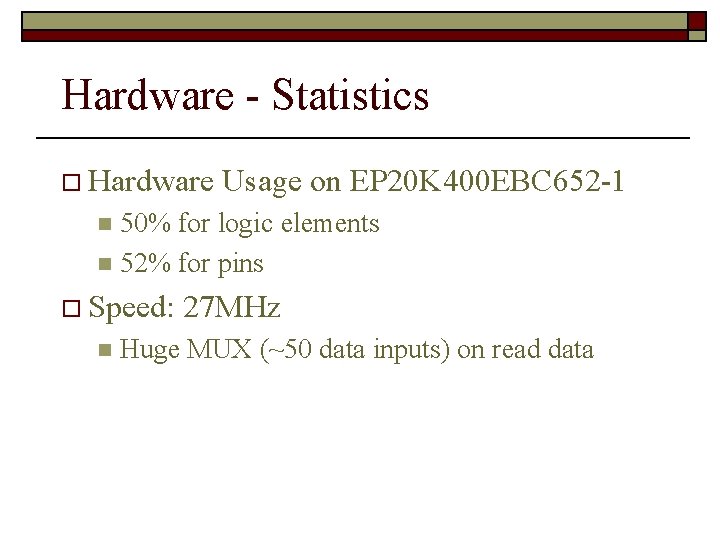

Hardware - Statistics o Hardware Usage on EP 20 K 400 EBC 652 -1 50% for logic elements n 52% for pins n o Speed: n 27 MHz Huge MUX (~50 data inputs) on read data

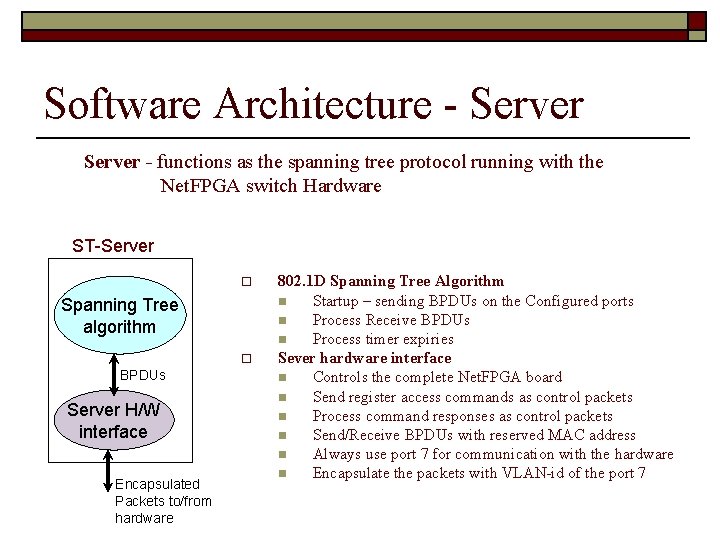

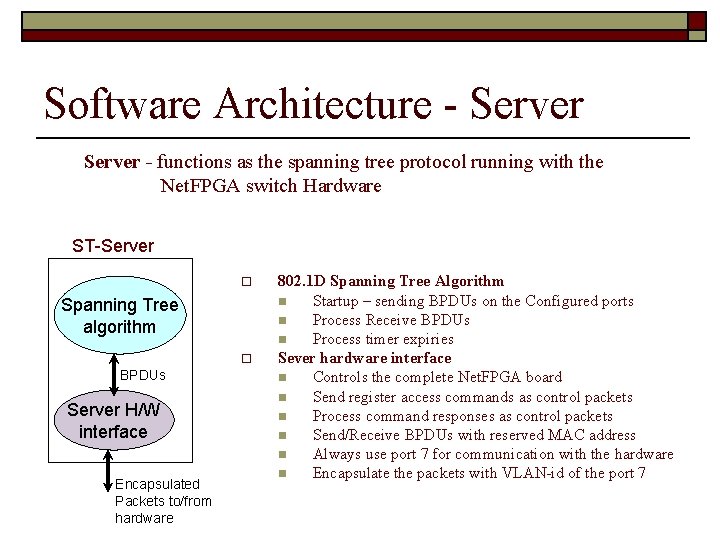

Software Architecture - Server - functions as the spanning tree protocol running with the Net. FPGA switch Hardware ST-Server o Spanning Tree algorithm o BPDUs Server H/W interface Encapsulated Packets to/from hardware 802. 1 D Spanning Tree Algorithm n Startup – sending BPDUs on the Configured ports n Process Receive BPDUs n Process timer expiries Sever hardware interface n Controls the complete Net. FPGA board n Send register access commands as control packets n Process command responses as control packets n Send/Receive BPDUs with reserved MAC address n Always use port 7 for communication with the hardware n Encapsulate the packets with VLAN-id of the port 7

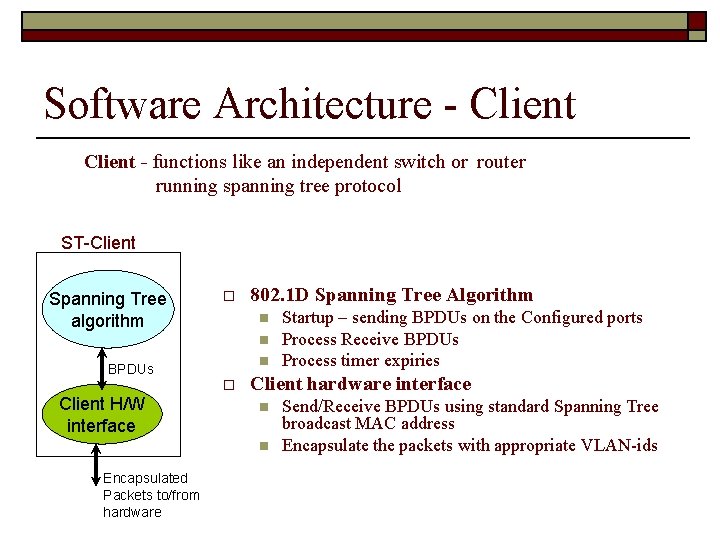

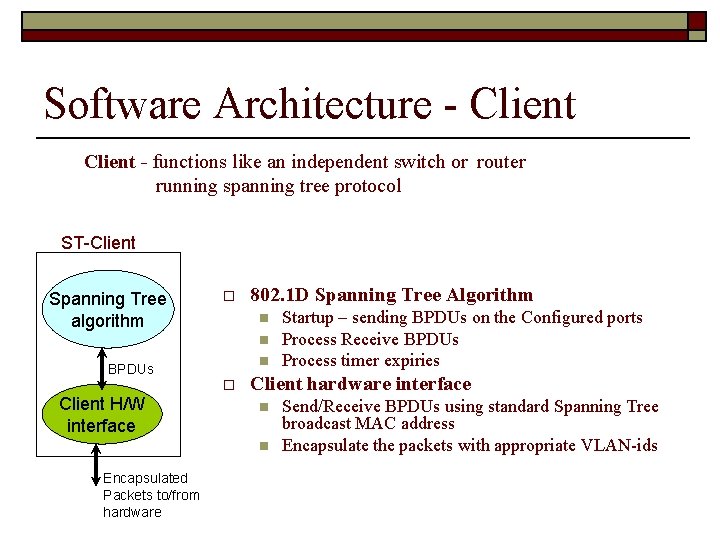

Software Architecture - Client - functions like an independent switch or router running spanning tree protocol ST-Client Spanning Tree algorithm o 802. 1 D Spanning Tree Algorithm n n n BPDUs o Client H/W interface Client hardware interface n n Encapsulated Packets to/from hardware Startup – sending BPDUs on the Configured ports Process Receive BPDUs Process timer expiries Send/Receive BPDUs using standard Spanning Tree broadcast MAC address Encapsulate the packets with appropriate VLAN-ids

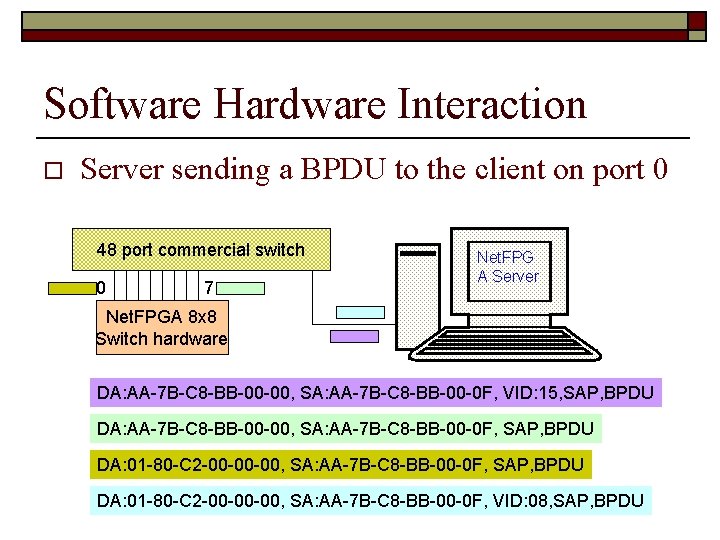

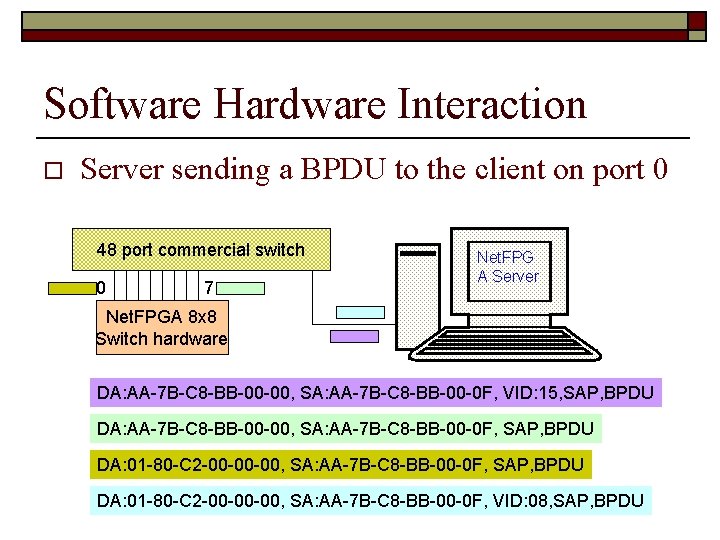

Software Hardware Interaction o Server sending a BPDU to the client on port 0 48 port commercial switch 0 7 Net. FPG A Server Net. FPGA 8 x 8 Switch hardware DA: AA-7 B-C 8 -BB-00 -00, SA: AA-7 B-C 8 -BB-00 -0 F, VID: 15, SAP, BPDU DA: AA-7 B-C 8 -BB-00 -00, SA: AA-7 B-C 8 -BB-00 -0 F, SAP, BPDU DA: 01 -80 -C 2 -00 -00 -00, SA: AA-7 B-C 8 -BB-00 -0 F, VID: 08, SAP, BPDU

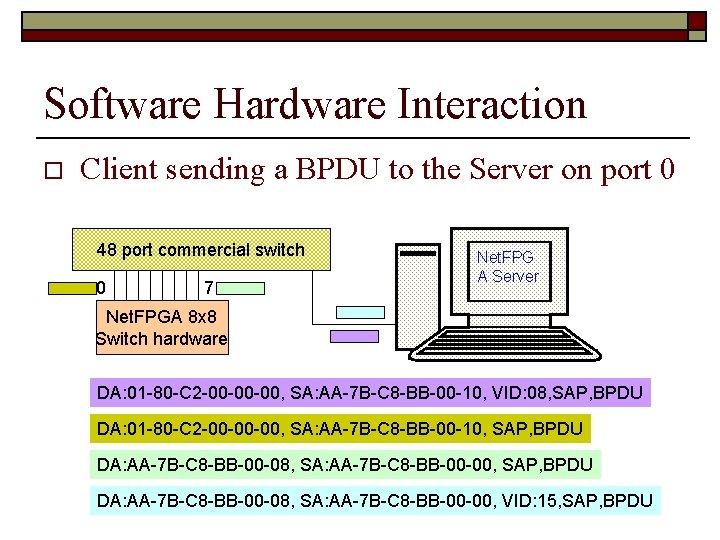

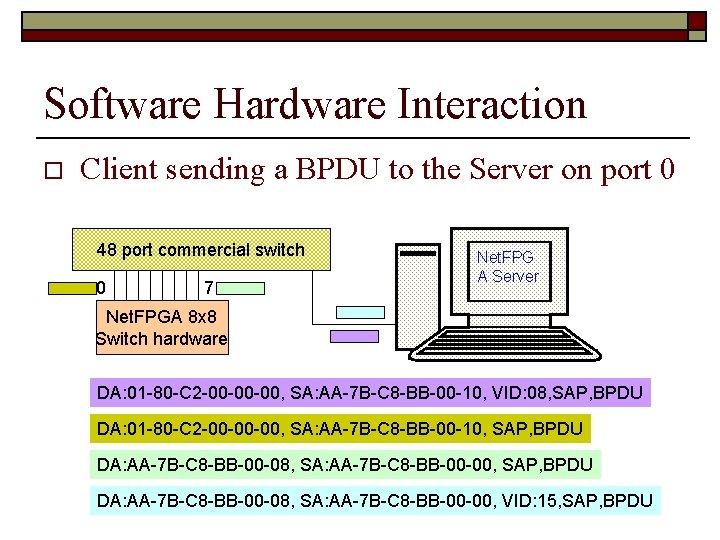

Software Hardware Interaction o Client sending a BPDU to the Server on port 0 48 port commercial switch 0 7 Net. FPG A Server Net. FPGA 8 x 8 Switch hardware DA: 01 -80 -C 2 -00 -00 -00, SA: AA-7 B-C 8 -BB-00 -10, VID: 08, SAP, BPDU DA: 01 -80 -C 2 -00 -00 -00, SA: AA-7 B-C 8 -BB-00 -10, SAP, BPDU DA: AA-7 B-C 8 -BB-00 -08, SA: AA-7 B-C 8 -BB-00 -00, VID: 15, SAP, BPDU

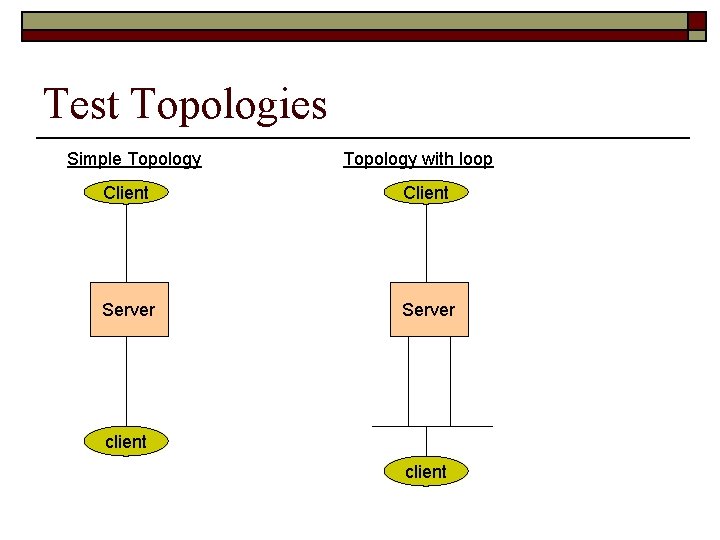

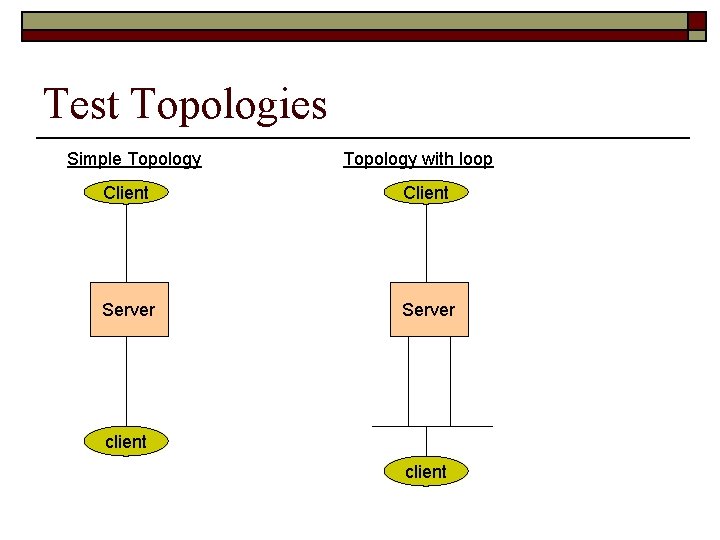

Test Topologies Simple Topology with loop Client Server client