240 334 Computer System Design Lecture 4 Wannarat

- Slides: 37

240 -334 Computer System Design Lecture 4 Wannarat Suntiamorntut 240 -334 By Wannarat

Part I : Single Data Path 240 -334 By Wannarat

Outline l l l Design a Processor step by step Requirement of instruction set Components and clocking Testing Datapath Control Datapath 240 -334 By Wannarat

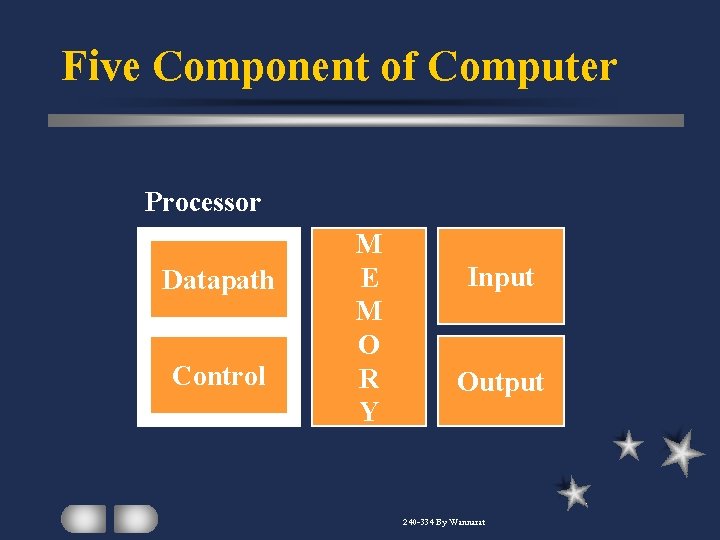

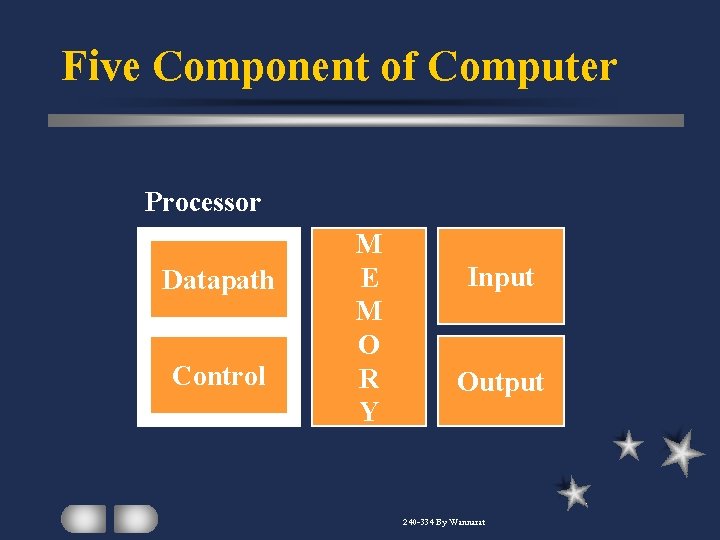

Five Component of Computer Processor Datapath Control M E M O R Y Input Output 240 -334 By Wannarat

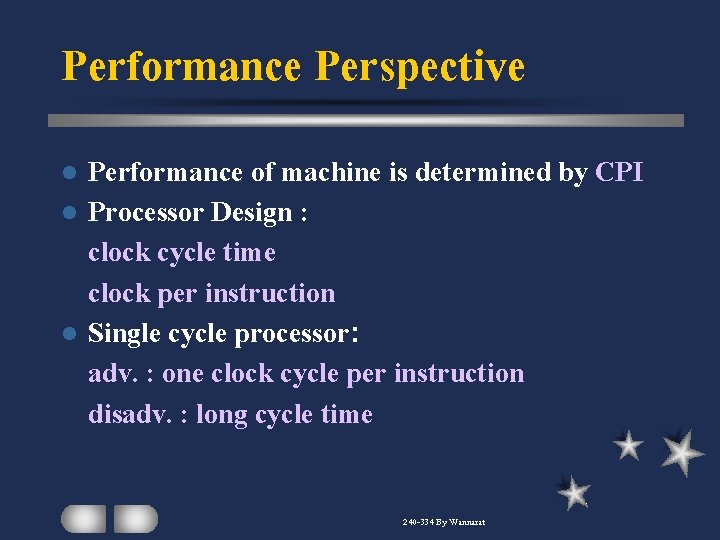

Performance Perspective Performance of machine is determined by CPI l Processor Design : clock cycle time clock per instruction l Single cycle processor: adv. : one clock cycle per instruction disadv. : long cycle time l 240 -334 By Wannarat

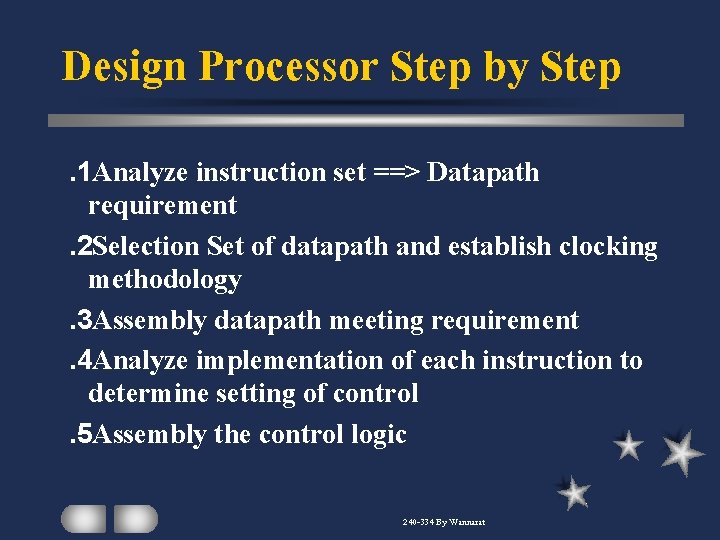

Design Processor Step by Step. 1 Analyze instruction set ==> Datapath requirement. 2 Selection Set of datapath and establish clocking methodology. 3 Assembly datapath meeting requirement. 4 Analyze implementation of each instruction to determine setting of control. 5 Assembly the control logic 240 -334 By Wannarat

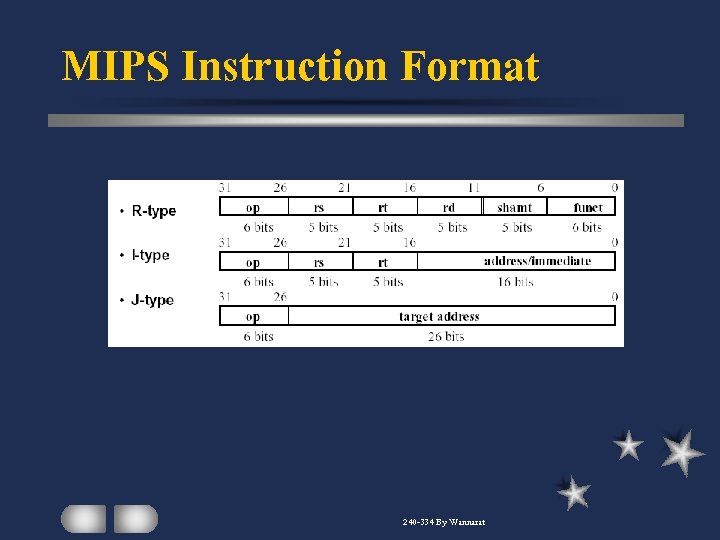

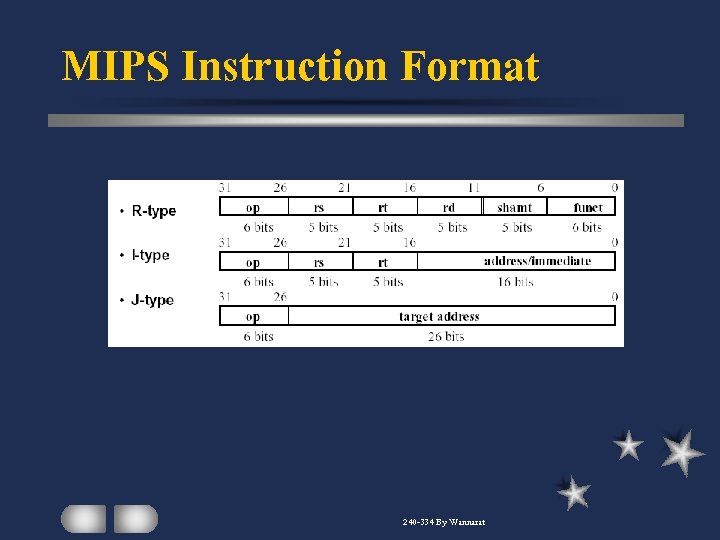

MIPS Instruction Format 240 -334 By Wannarat

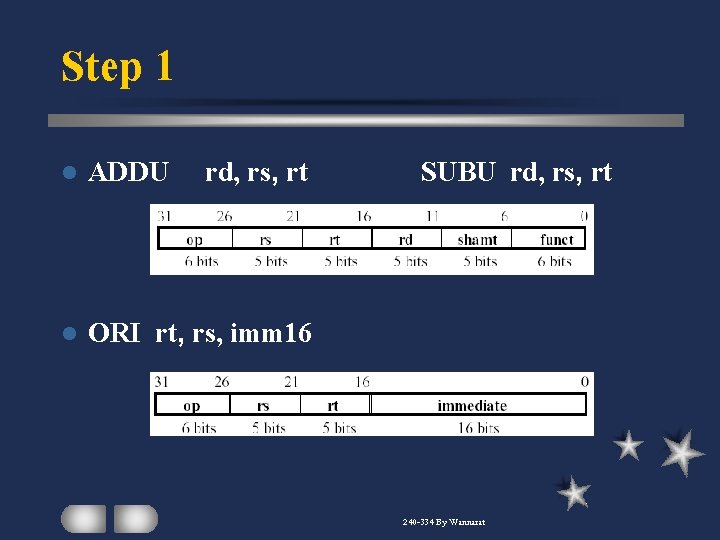

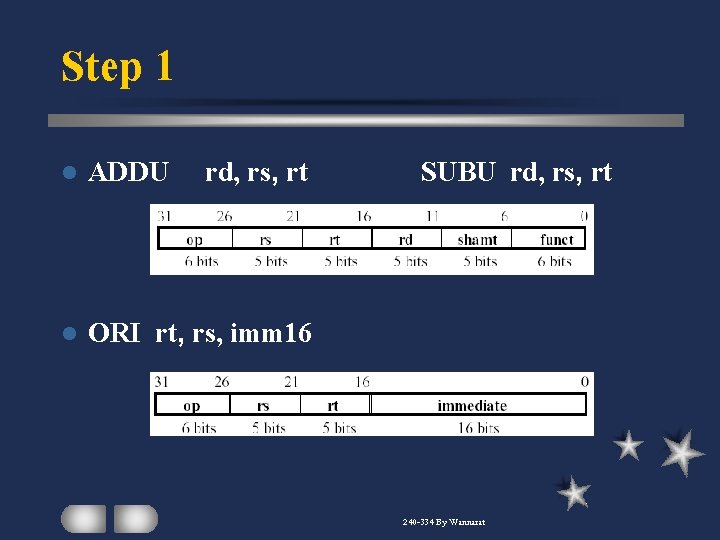

Step 1 l ADDU rd, rs, rt l ORI rt, rs, imm 16 SUBU rd, rs, rt 240 -334 By Wannarat

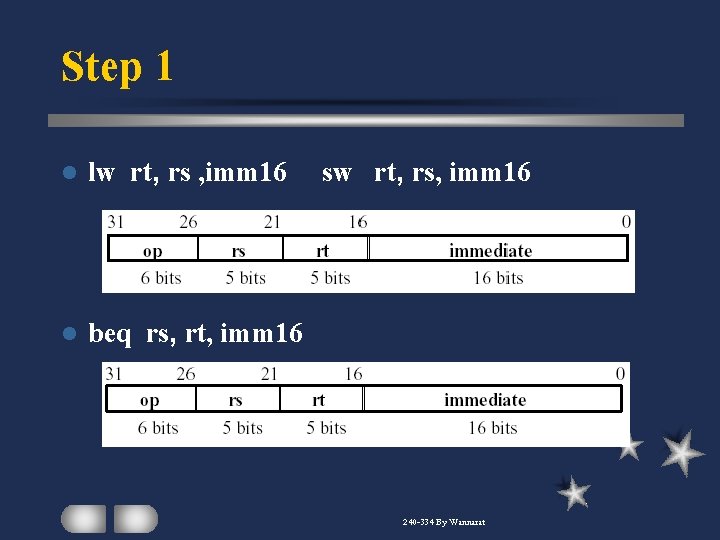

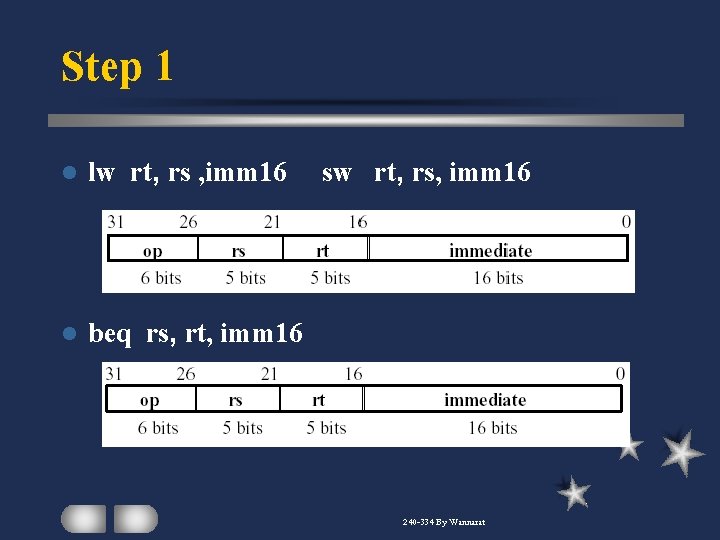

Step 1 l lw rt, rs , imm 16 l beq rs, rt, imm 16 sw rt, rs, imm 16 240 -334 By Wannarat

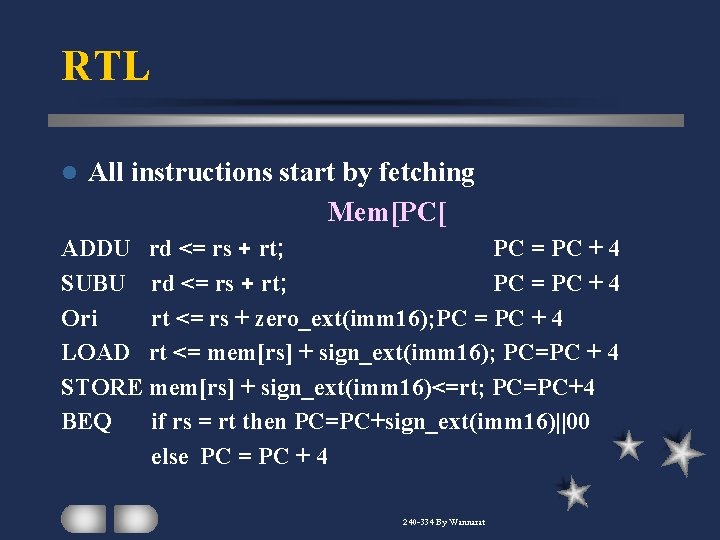

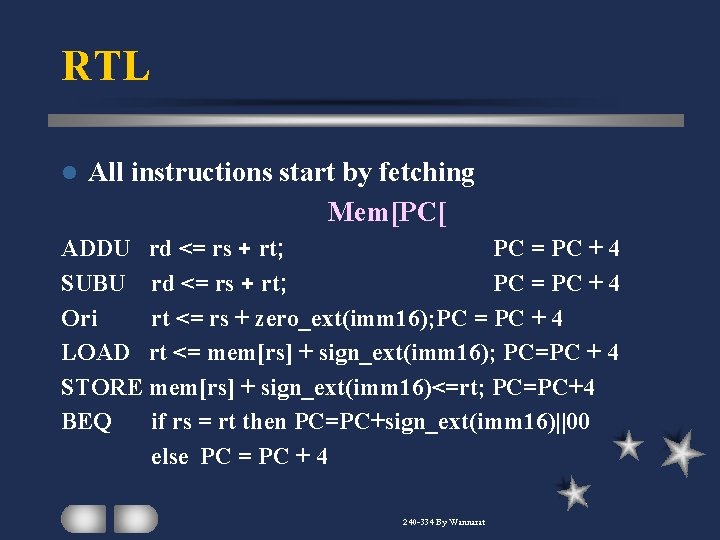

RTL l All instructions start by fetching Mem[PC[ ADDU rd <= rs + rt; PC = PC + 4 SUBU rd <= rs + rt; PC = PC + 4 Ori rt <= rs + zero_ext(imm 16); PC = PC + 4 LOAD rt <= mem[rs] + sign_ext(imm 16); PC=PC + 4 STORE mem[rs] + sign_ext(imm 16)<=rt; PC=PC+4 BEQ if rs = rt then PC=PC+sign_ext(imm 16)||00 else PC = PC + 4 240 -334 By Wannarat

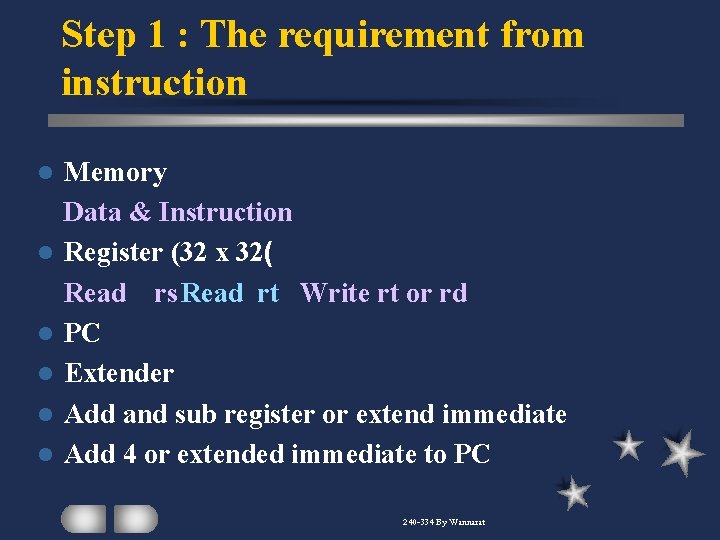

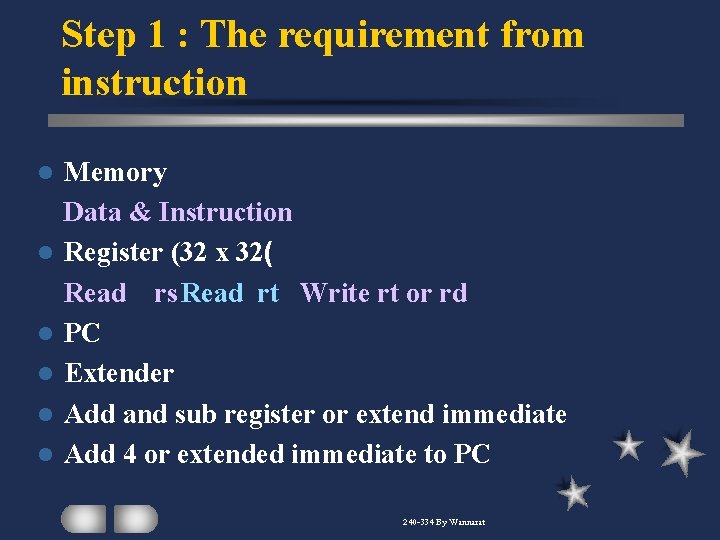

Step 1 : The requirement from instruction l l l Memory Data & Instruction Register (32 x 32( Read rs Read rt Write rt or rd PC Extender Add and sub register or extend immediate Add 4 or extended immediate to PC 240 -334 By Wannarat

Step 2 : Components of datapath Combination Element l Storage elements Clocking methodology l 240 -334 By Wannarat

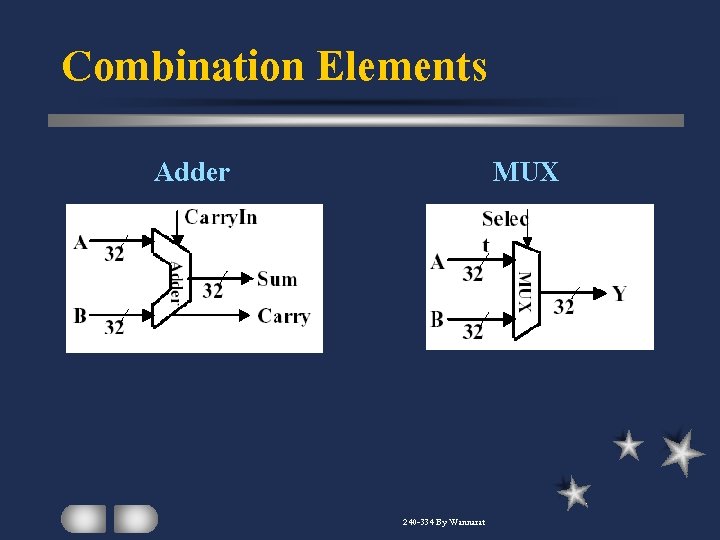

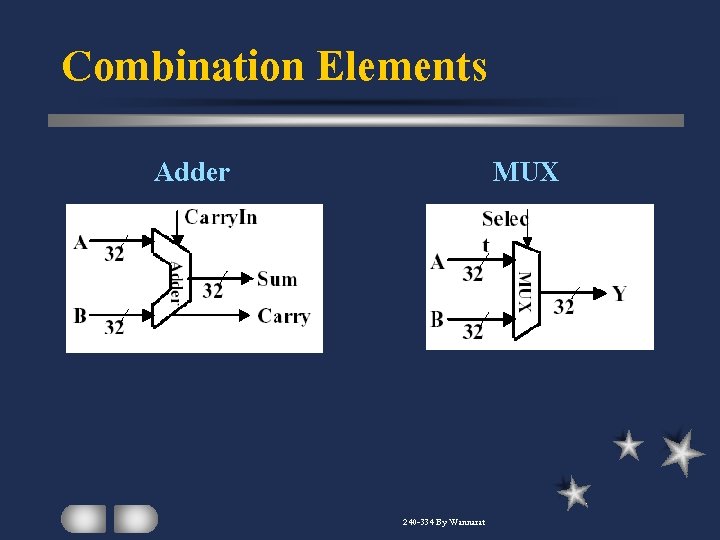

Combination Elements Adder MUX 240 -334 By Wannarat

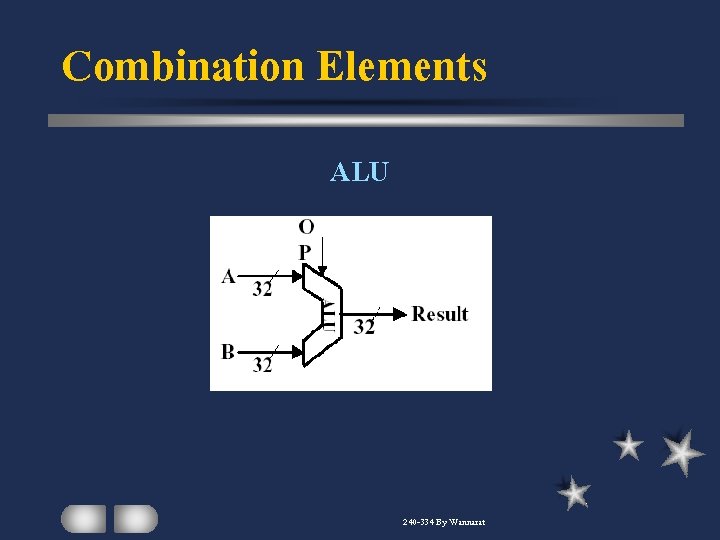

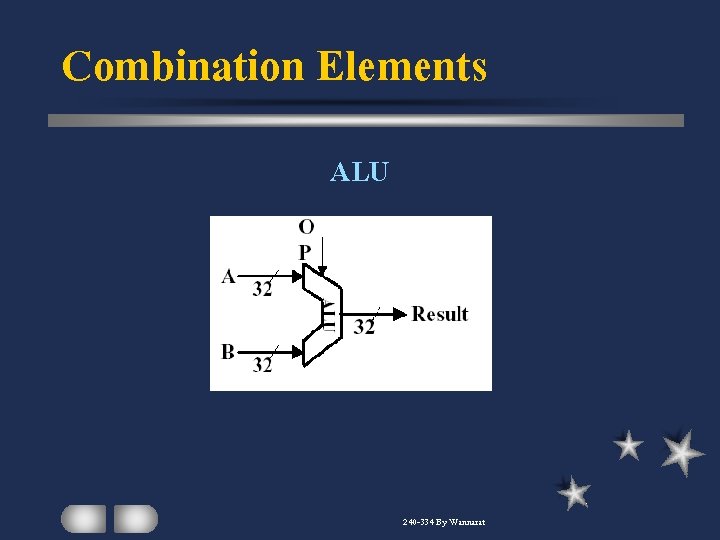

Combination Elements ALU 240 -334 By Wannarat

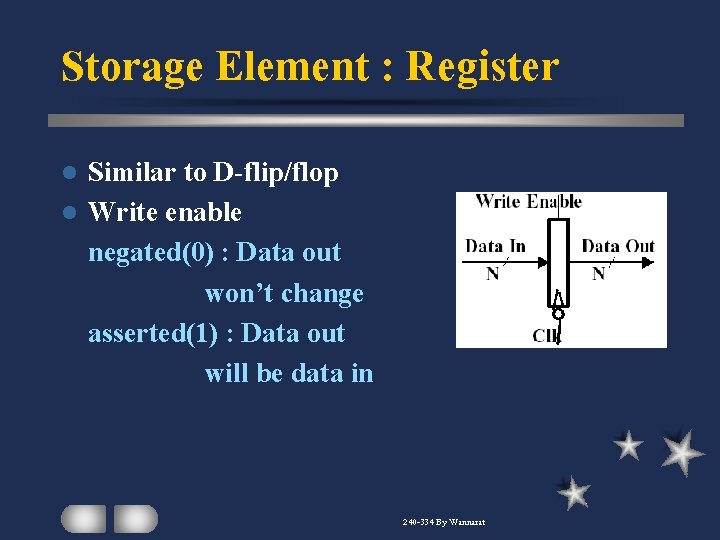

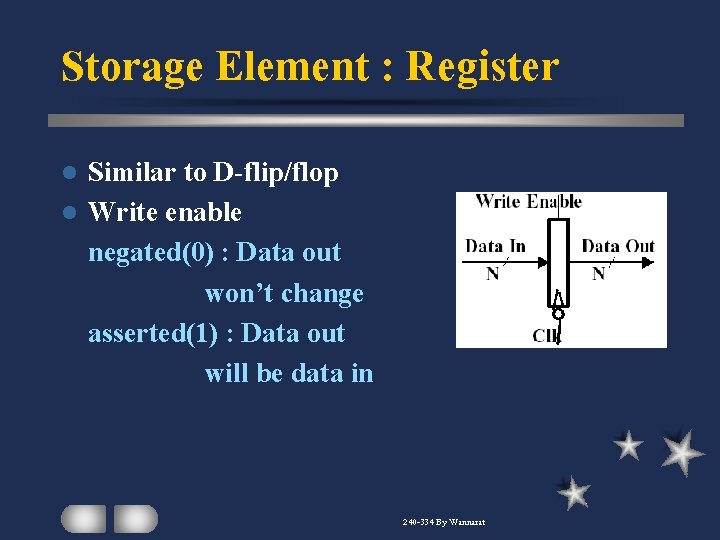

Storage Element : Register Similar to D-flip/flop l Write enable negated(0) : Data out won’t change asserted(1) : Data out will be data in l 240 -334 By Wannarat

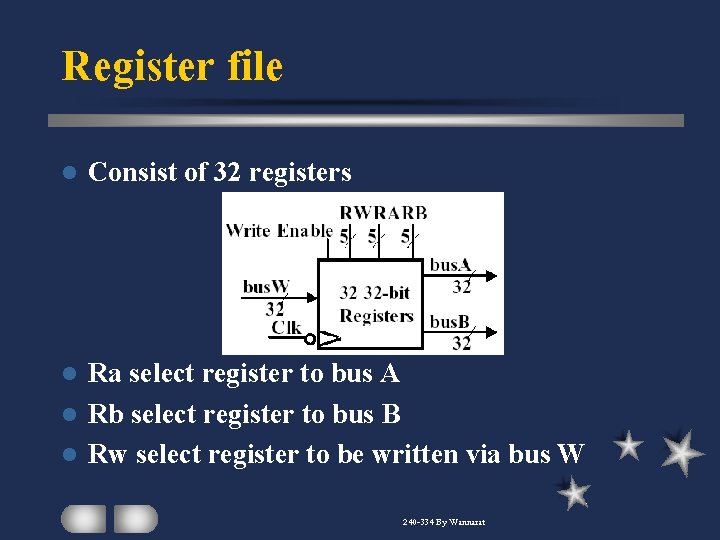

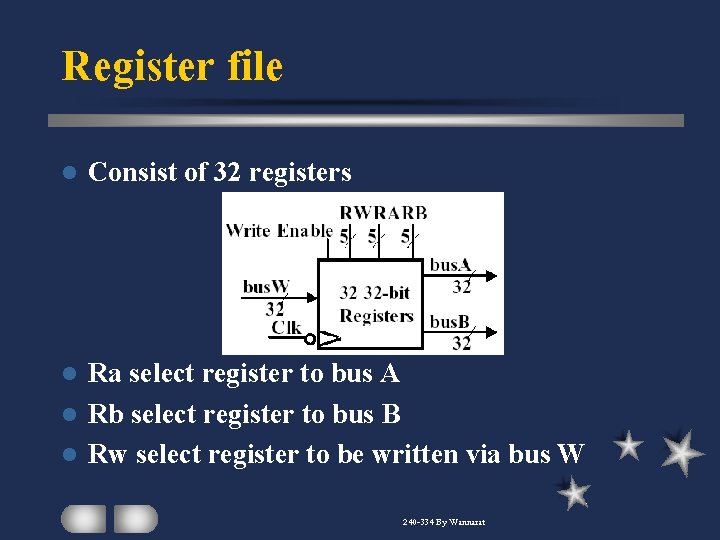

Register file l Consist of 32 registers Ra select register to bus A l Rb select register to bus B l Rw select register to be written via bus W l 240 -334 By Wannarat

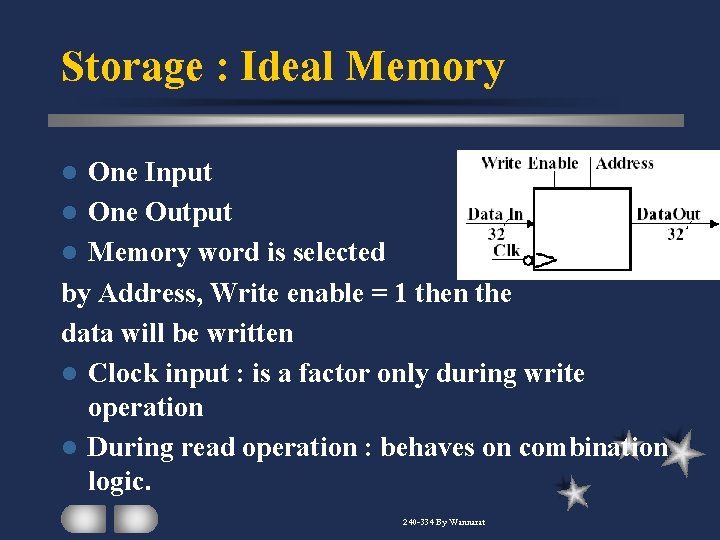

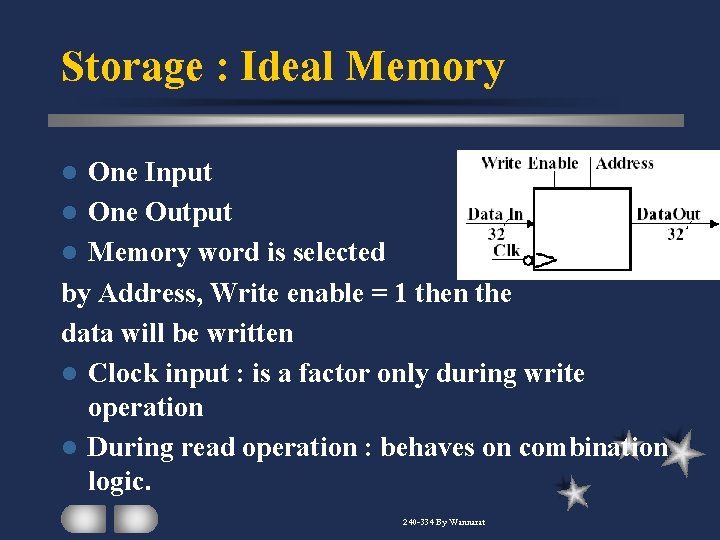

Storage : Ideal Memory One Input l One Output l Memory word is selected by Address, Write enable = 1 then the data will be written l Clock input : is a factor only during write operation l During read operation : behaves on combination logic. l 240 -334 By Wannarat

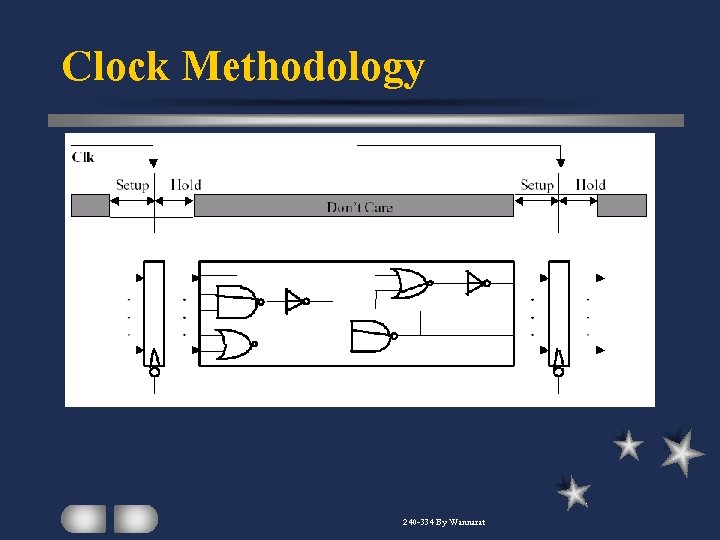

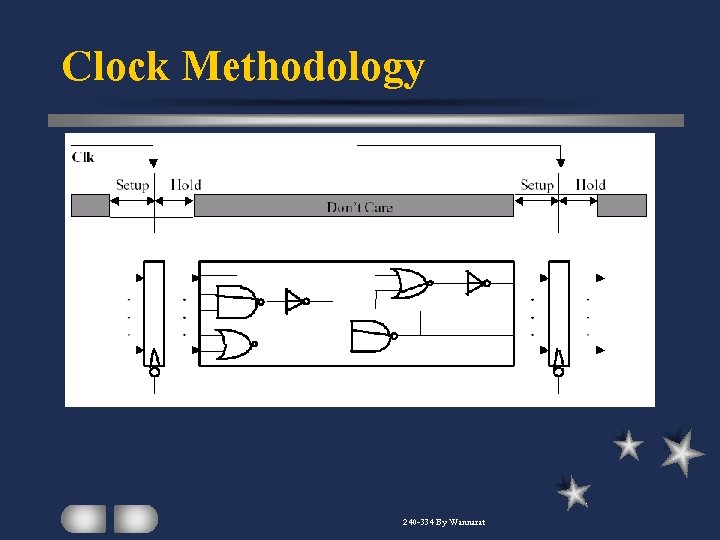

Clock Methodology 240 -334 By Wannarat

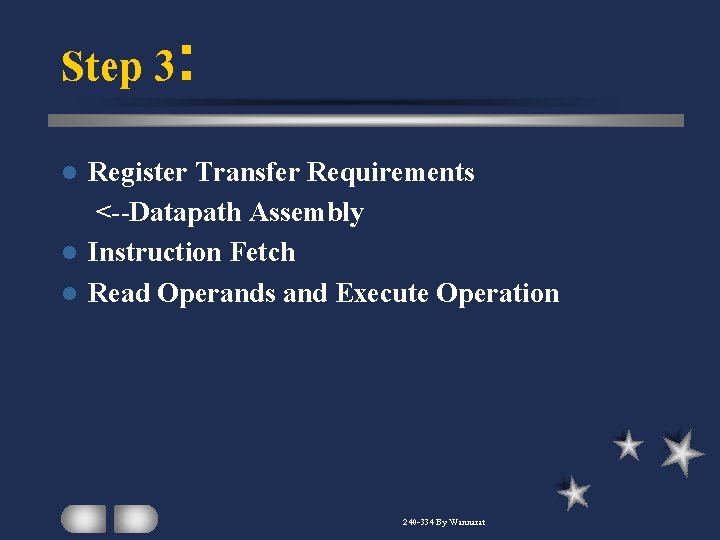

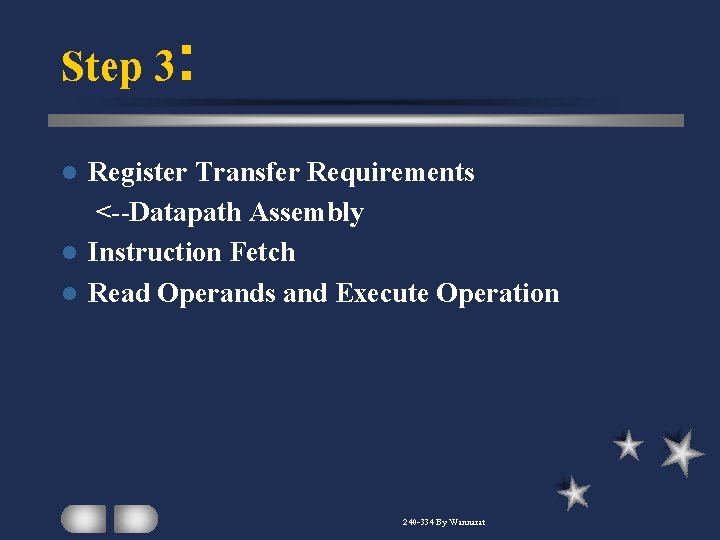

Step 3: Register Transfer Requirements <--Datapath Assembly l Instruction Fetch l Read Operands and Execute Operation l 240 -334 By Wannarat

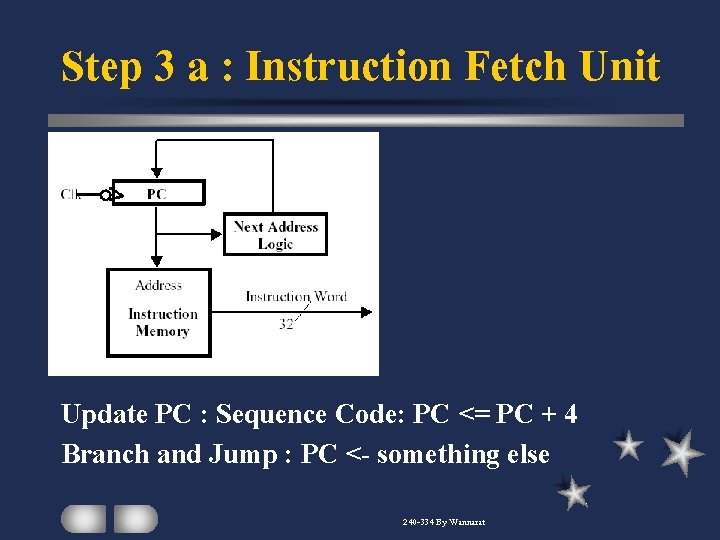

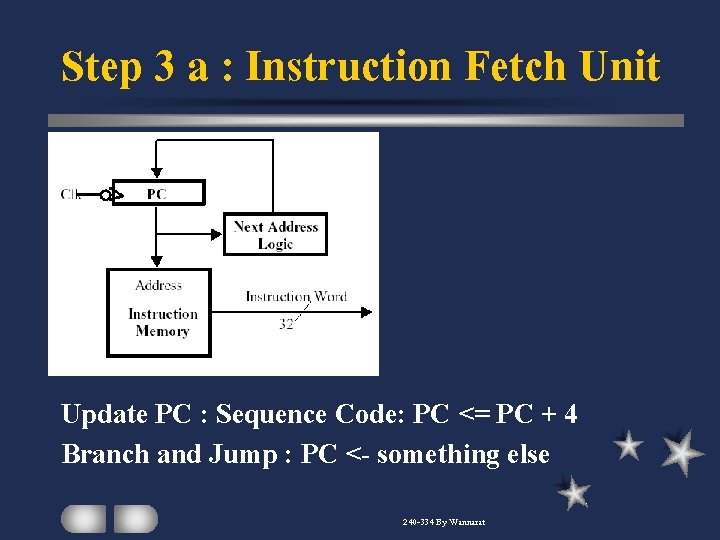

Step 3 a : Instruction Fetch Unit Update PC : Sequence Code: PC <= PC + 4 Branch and Jump : PC <- something else 240 -334 By Wannarat

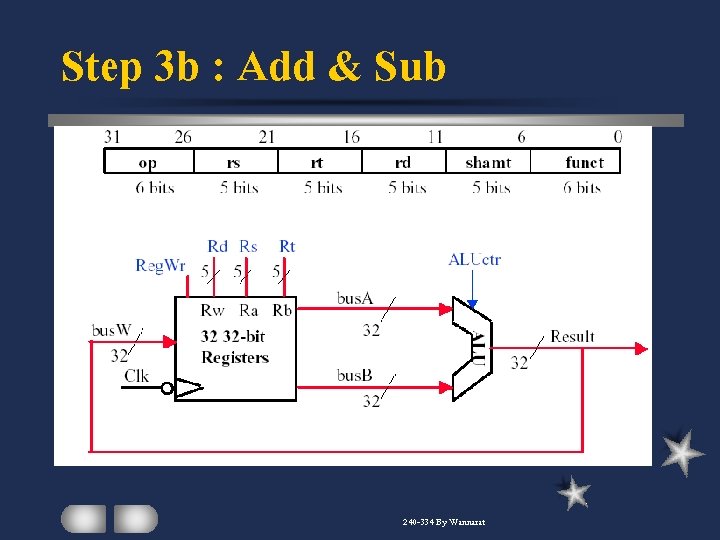

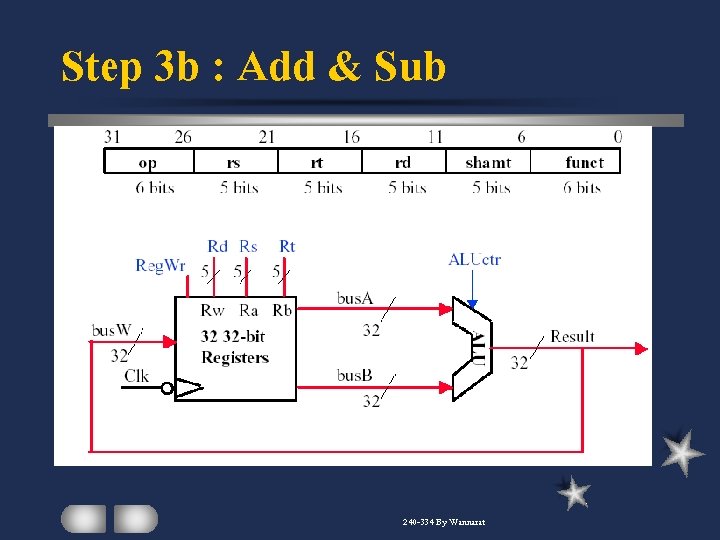

Step 3 b : Add & Sub 240 -334 By Wannarat

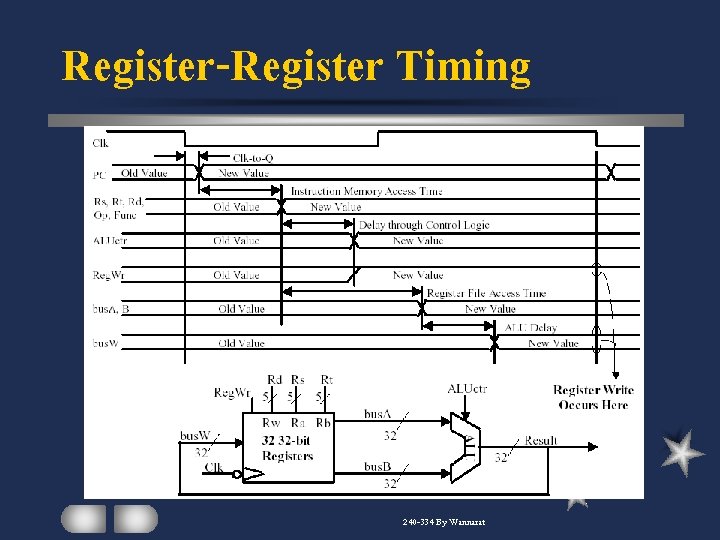

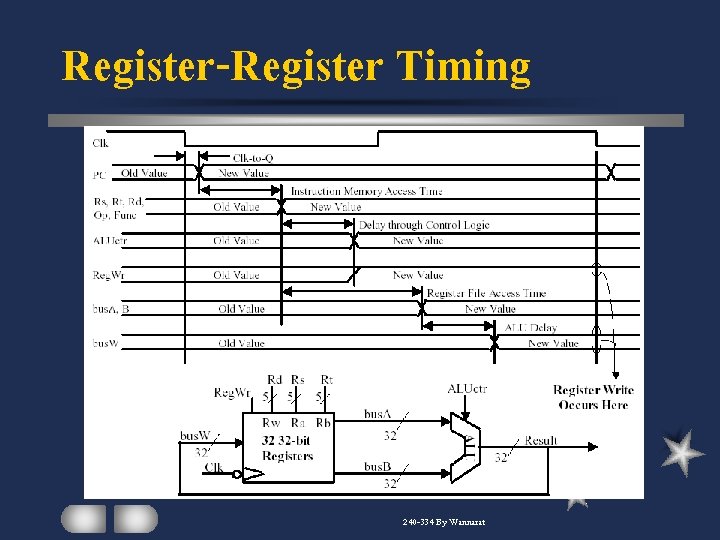

Register-Register Timing 240 -334 By Wannarat

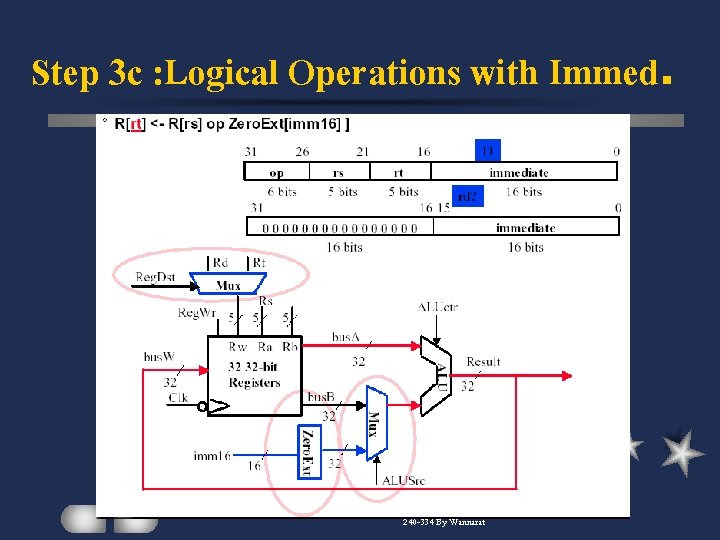

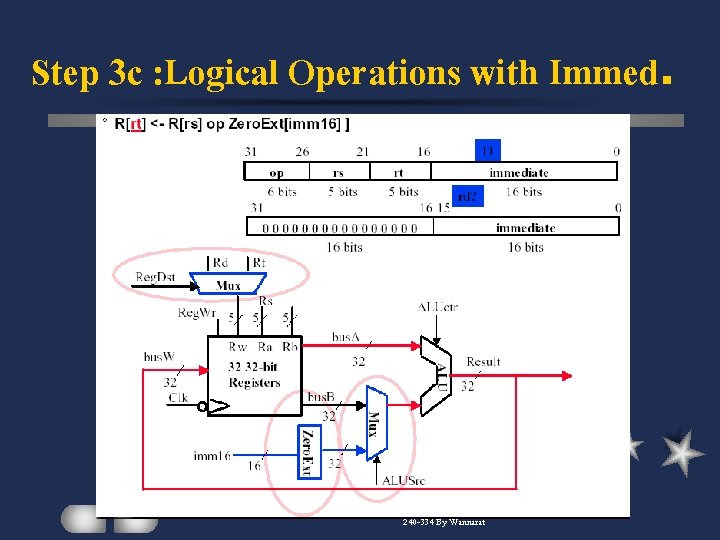

Step 3 c : Logical Operations with Immed. 240 -334 By Wannarat

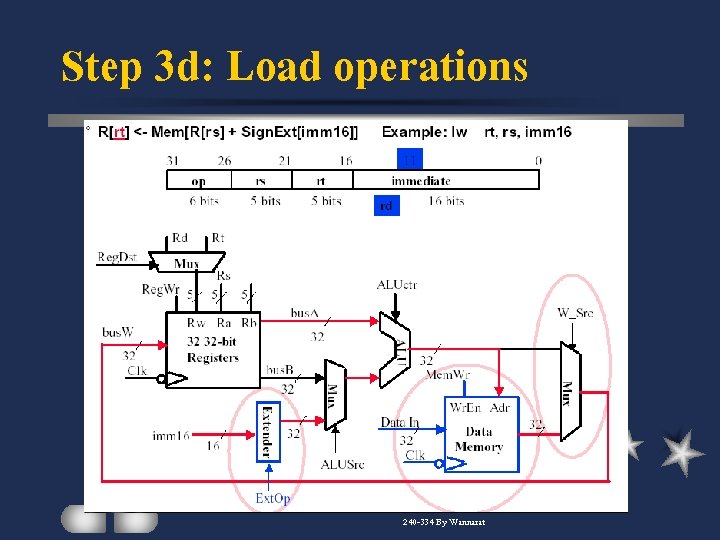

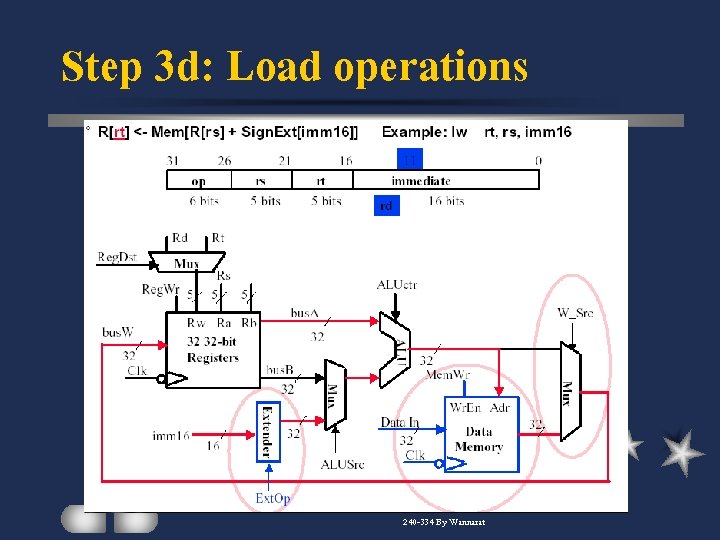

Step 3 d: Load operations 240 -334 By Wannarat

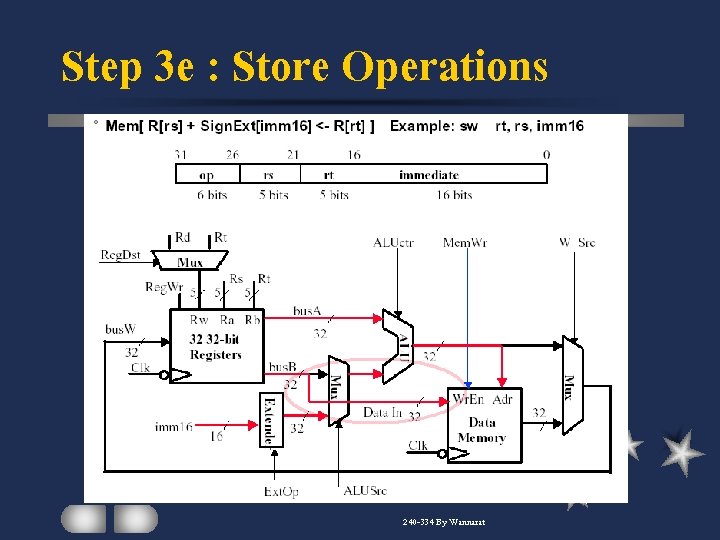

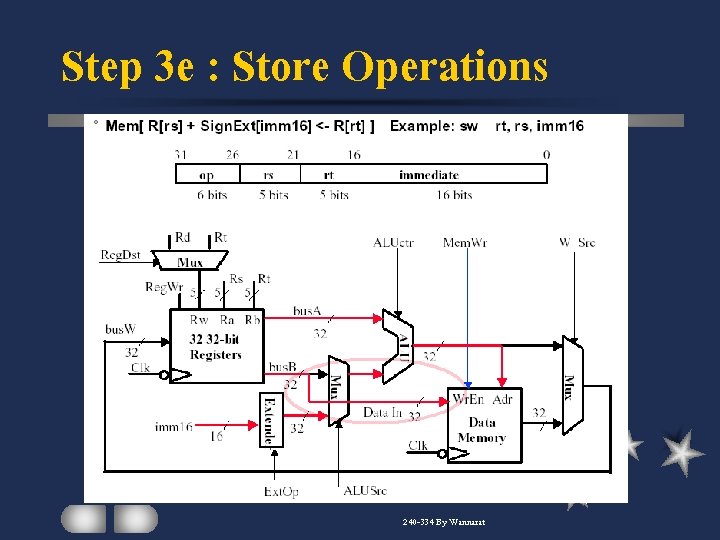

Step 3 e : Store Operations 240 -334 By Wannarat

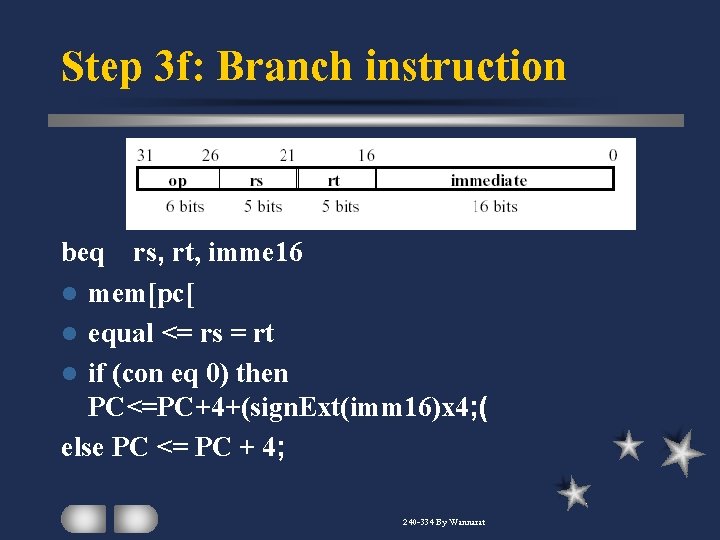

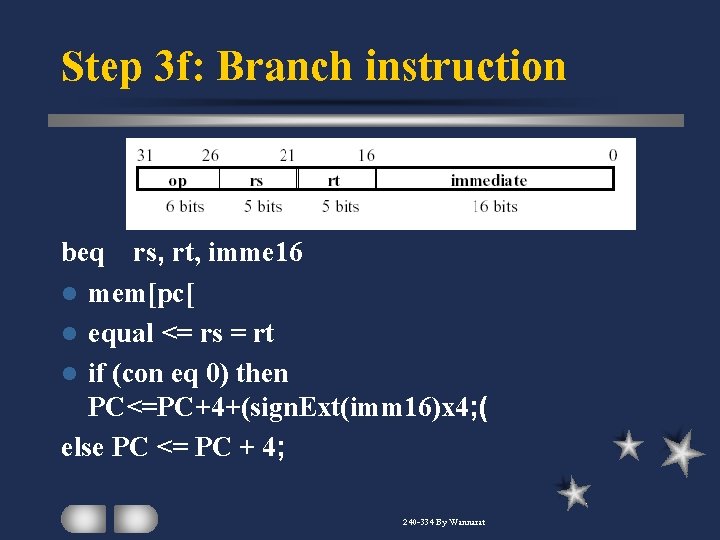

Step 3 f: Branch instruction beq rs, rt, imme 16 l mem[pc[ l equal <= rs = rt l if (con eq 0) then PC<=PC+4+(sign. Ext(imm 16)x 4; ( else PC <= PC + 4; 240 -334 By Wannarat

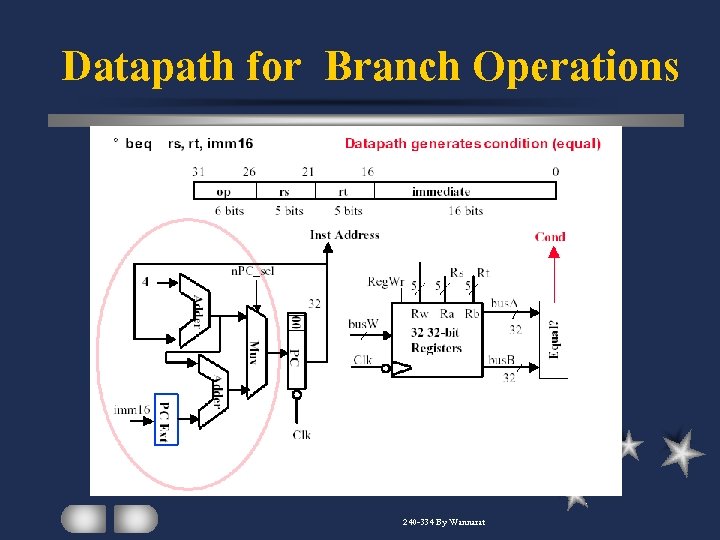

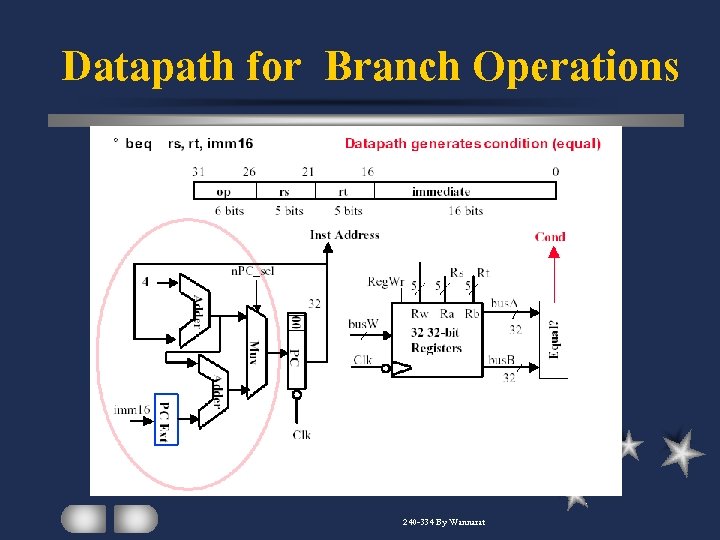

Datapath for Branch Operations 240 -334 By Wannarat

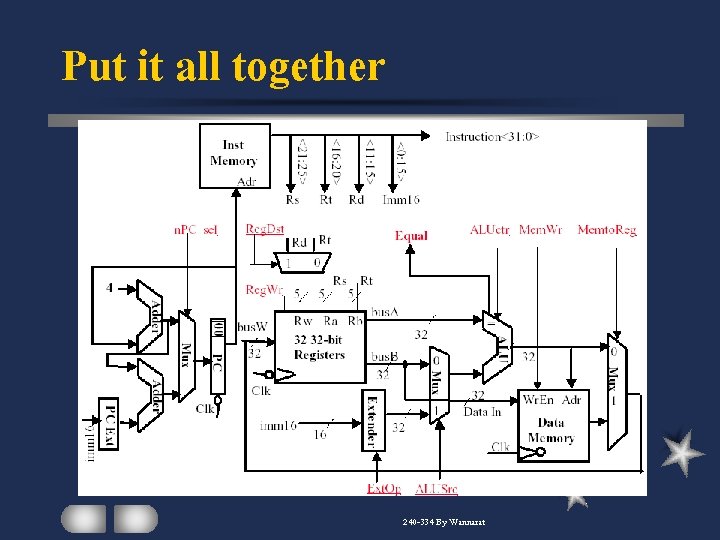

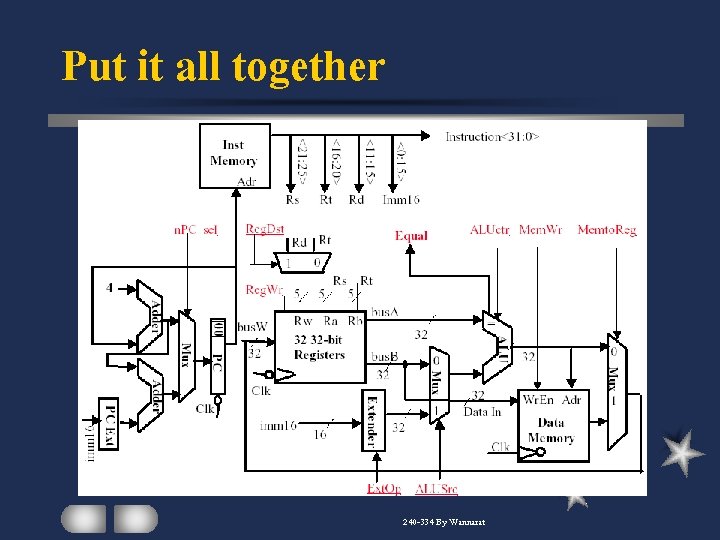

Put it all together 240 -334 By Wannarat

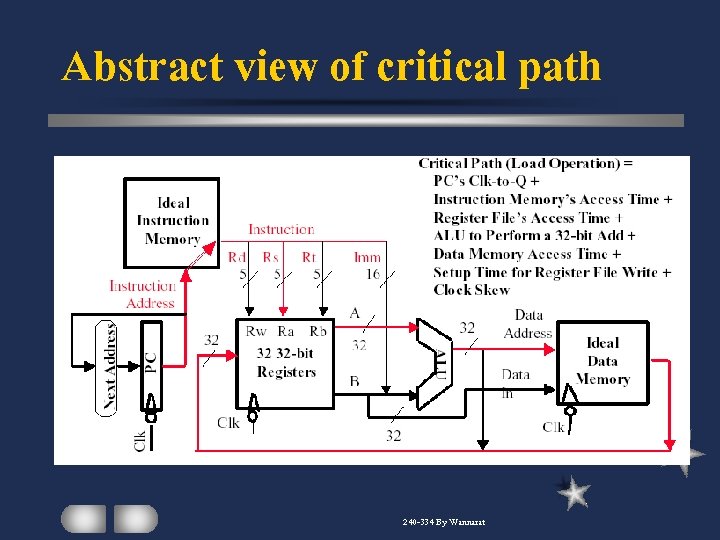

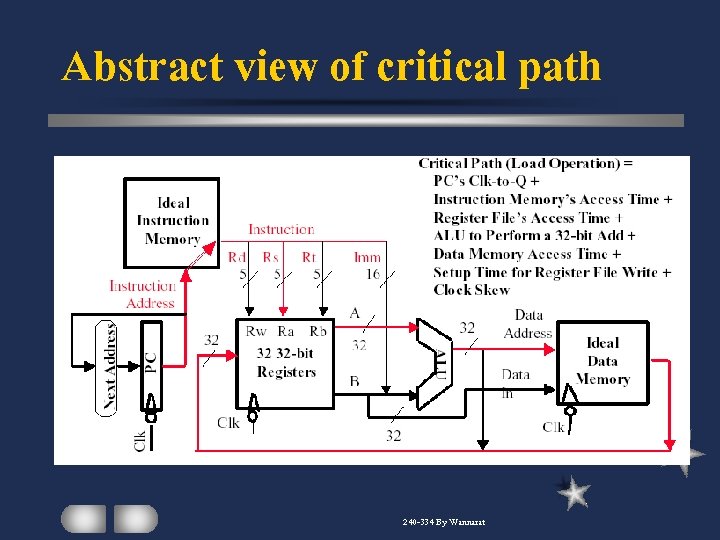

Abstract view of critical path 240 -334 By Wannarat

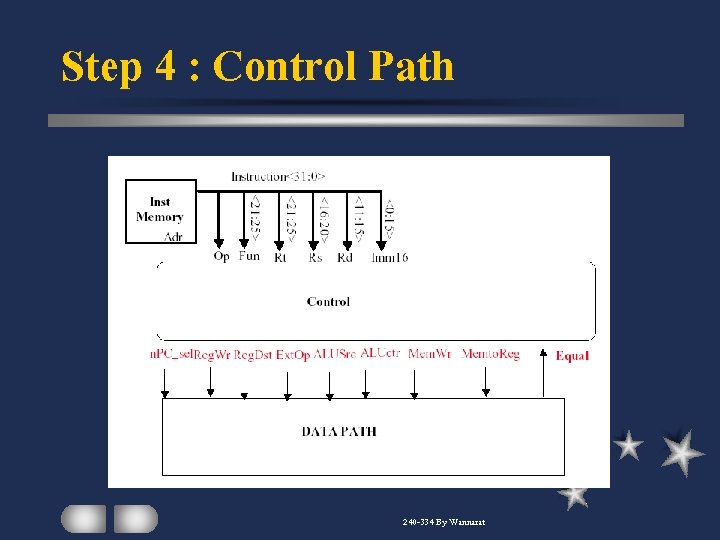

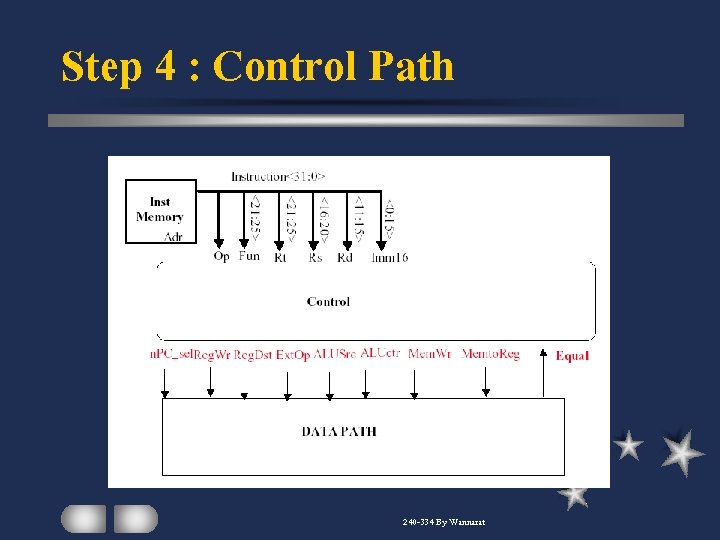

Step 4 : Control Path 240 -334 By Wannarat

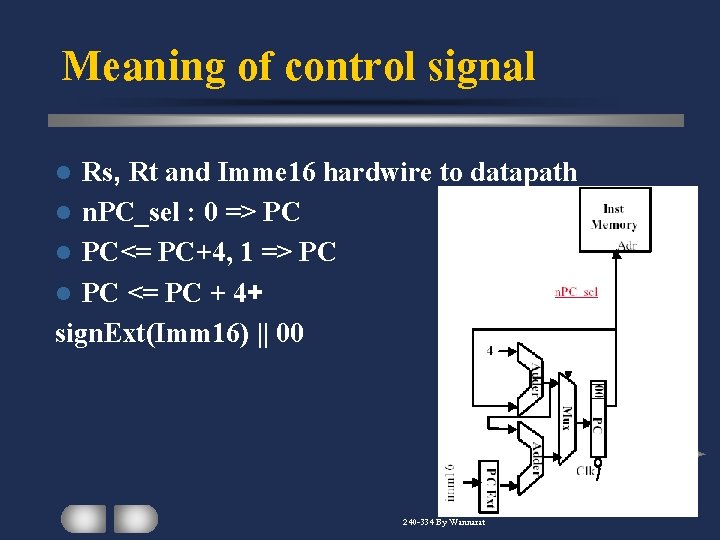

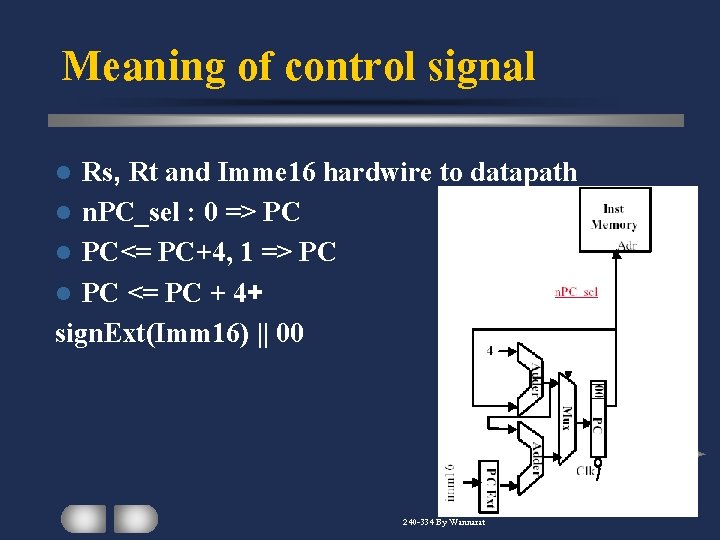

Meaning of control signal Rs, Rt and Imme 16 hardwire to datapath l n. PC_sel : 0 => PC l PC<= PC+4, 1 => PC l PC <= PC + 4+ sign. Ext(Imm 16) || 00 l 240 -334 By Wannarat

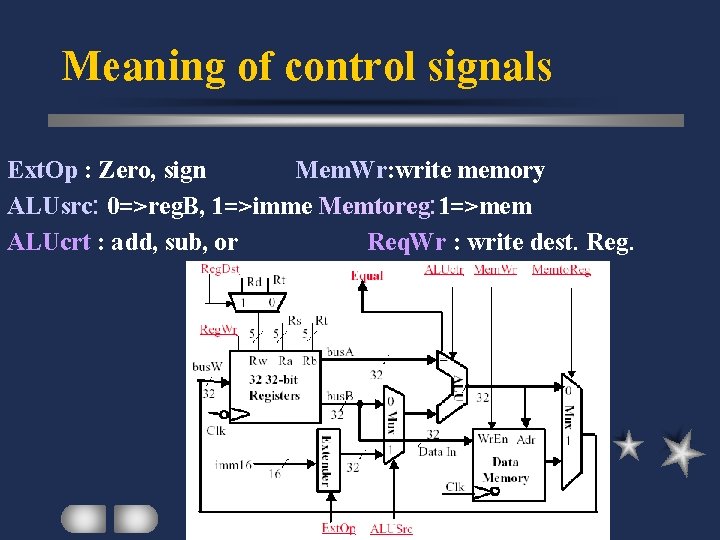

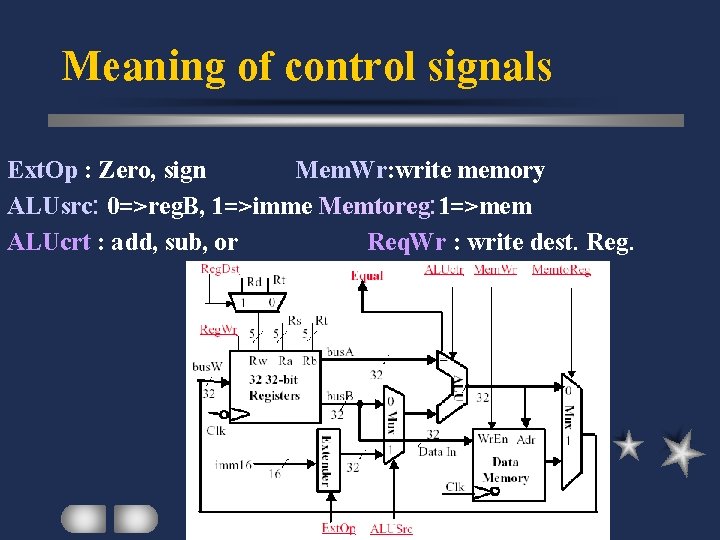

Meaning of control signals Ext. Op : Zero, sign Mem. Wr: write memory ALUsrc: 0=>reg. B, 1=>imme Memtoreg: 1=>mem ALUcrt : add, sub, or Req. Wr : write dest. Reg. 240 -334 By Wannarat

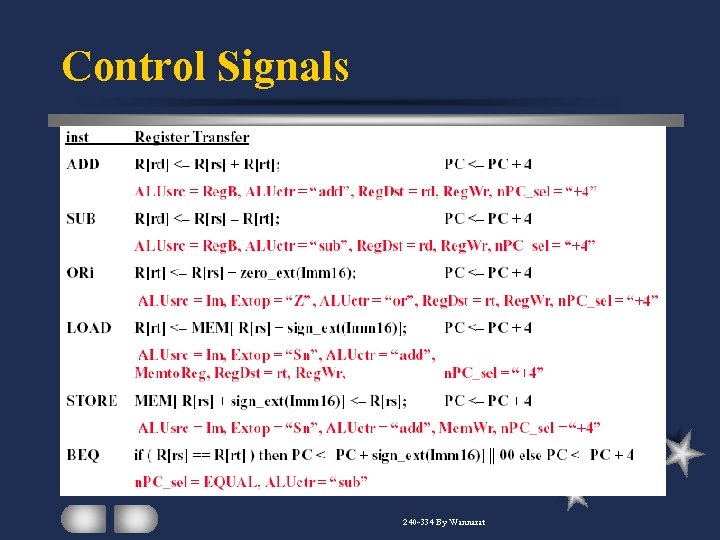

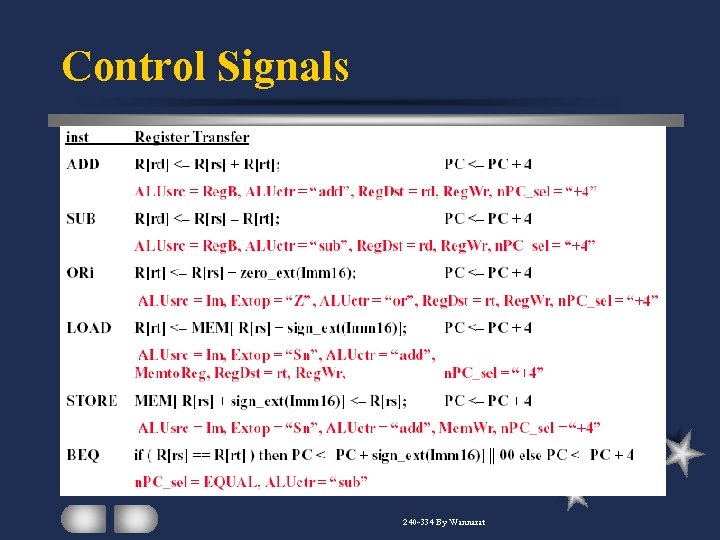

Control Signals 240 -334 By Wannarat

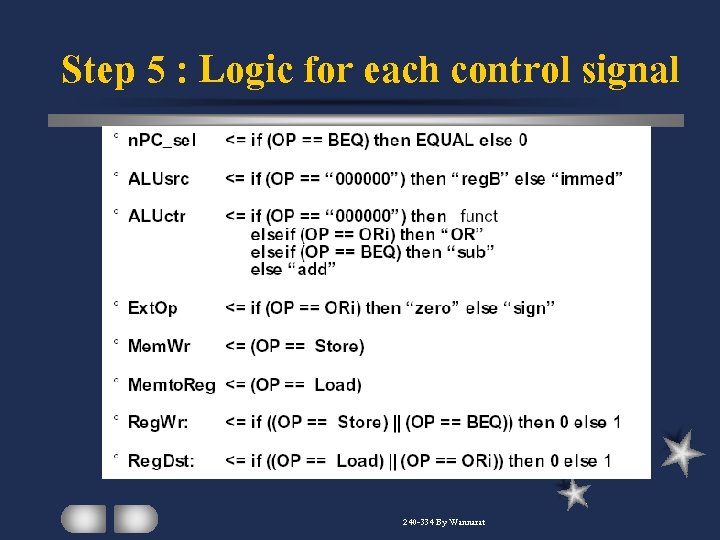

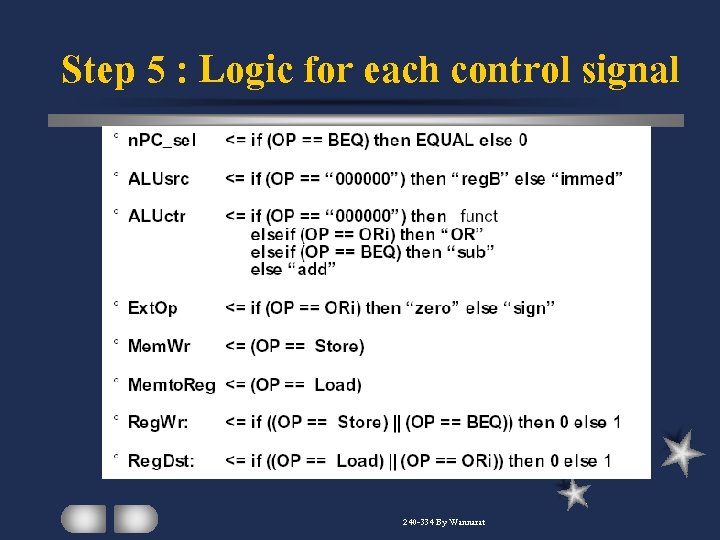

Step 5 : Logic for each control signal 240 -334 By Wannarat

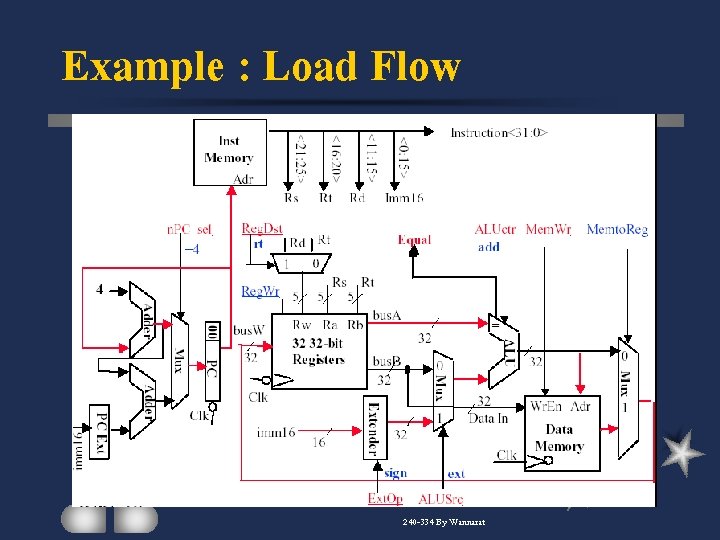

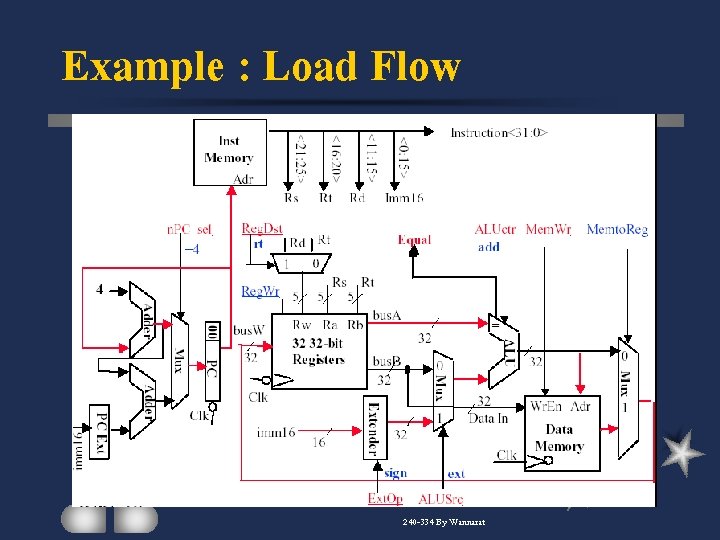

Example : Load Flow 240 -334 By Wannarat

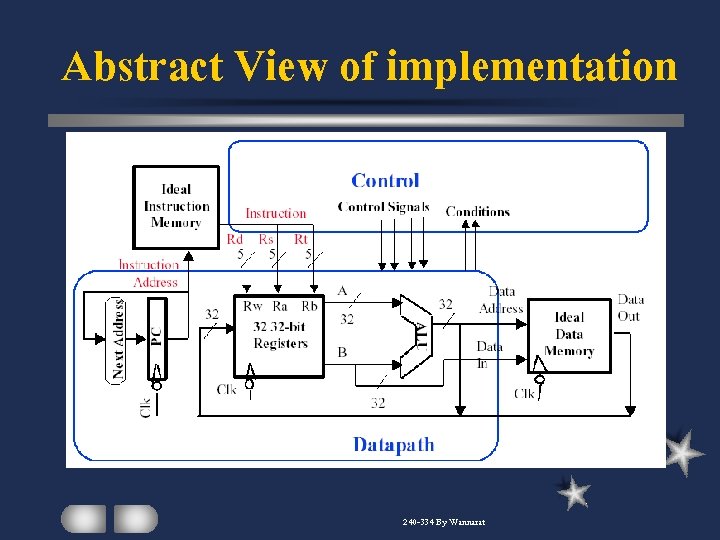

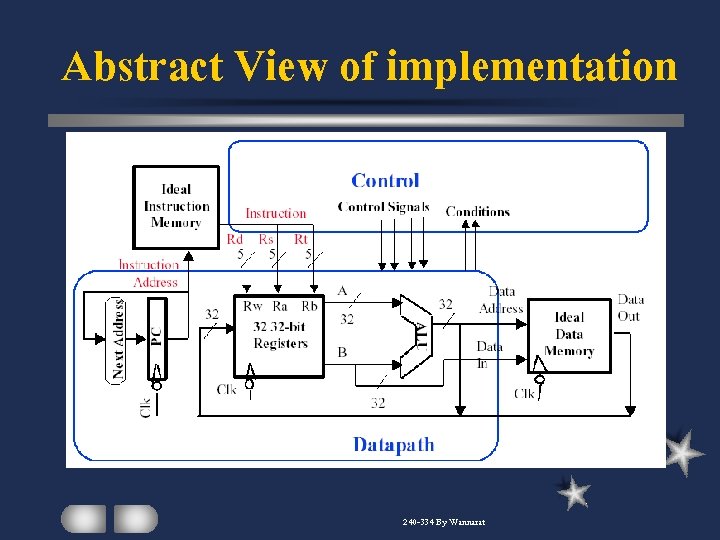

Abstract View of implementation 240 -334 By Wannarat

Next on Lecture 5 240 -334 By Wannarat