1 eindhoven university of technology Architectures of Digital

- Slides: 14

1/ eindhoven university of technology Architectures of Digital Information Systems part 5: Special and weird ‘processor’ types dr. ir. A. C. Verschueren Eindhoven University of Technology Section of Digital Information Systems / faculty of Electrical Engineering

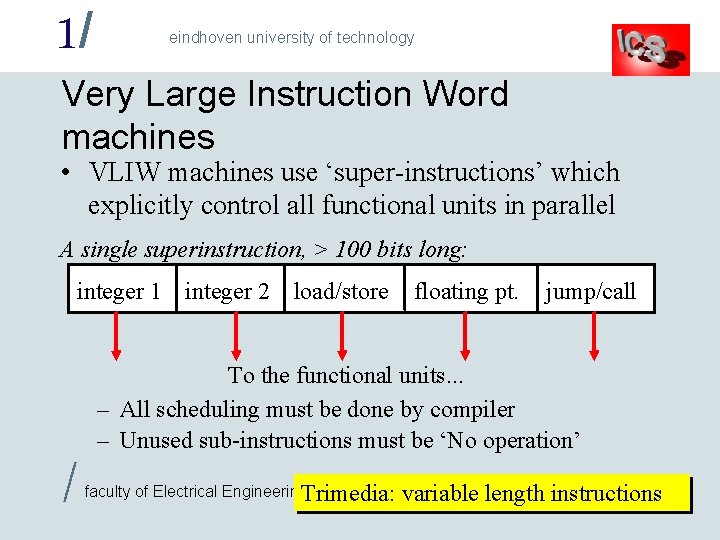

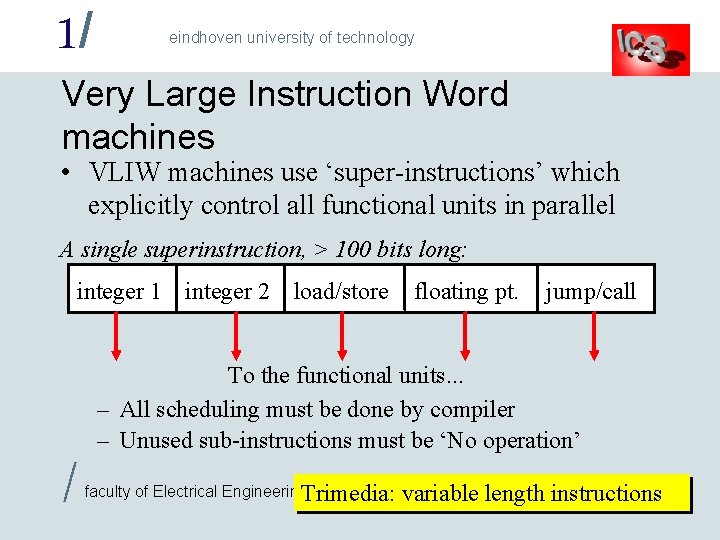

1/ eindhoven university of technology Very Large Instruction Word machines • VLIW machines use ‘super-instructions’ which explicitly control all functional units in parallel A single superinstruction, > 100 bits long: integer 1 integer 2 load/store / floating pt. jump/call To the functional units. . . – All scheduling must be done by compiler – Unused sub-instructions must be ‘No operation’ faculty of Electrical Engineering. Trimedia: variable length instructions

1/ eindhoven university of technology Single Instruction-Multiple Data machines • Lots of ALU’s performing the same operation Systolic array: – Number of ALU’s equals number of data elements – Can have local storage and neighbour connections Vector processor: – Number of ALU’s below number of data elements / – Lack of dependencies allows VERY fast pipelines faculty of Electrical Engineering Intel’s MMX is a kind of SIMD !

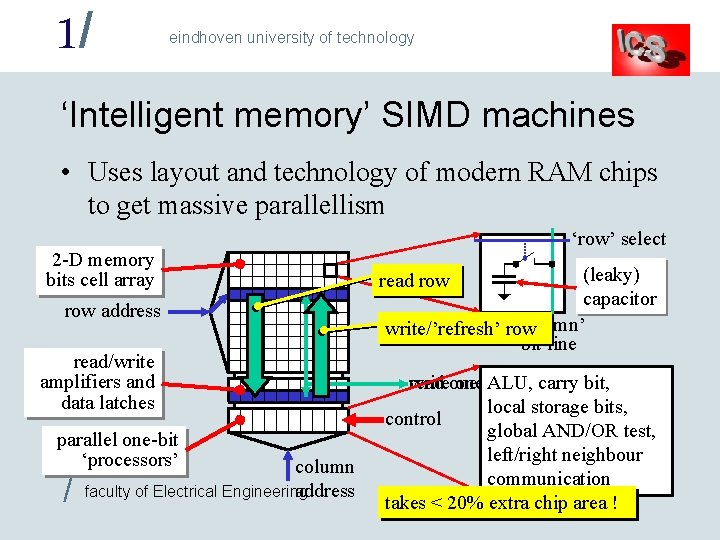

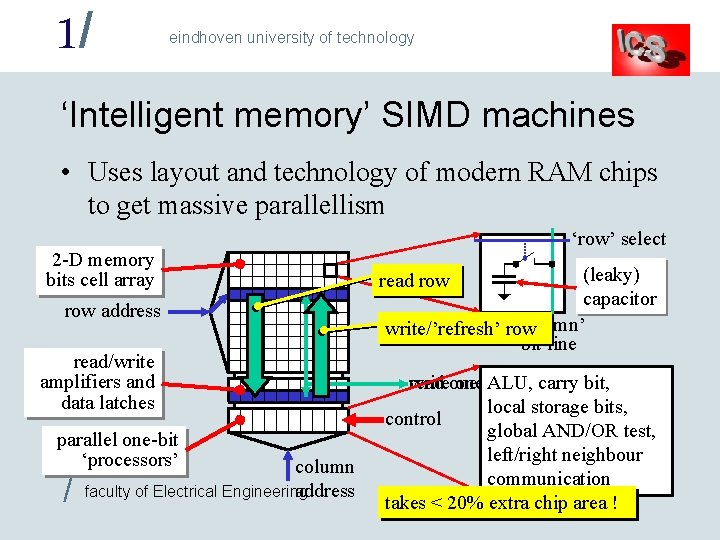

1/ eindhoven university of technology ‘Intelligent memory’ SIMD machines • Uses layout and technology of modern RAM chips to get massive parallellism 2 -D memory bits cell array row address read/write amplifiers and data latches parallel one-bit column address ‘processors’ column faculty of Electrical Engineering address / ‘row’ select (leaky) capacitor ‘column’ write/’refresh’ row bit line read row write one bit read one bit ALU, carry bit, local storage bits, control global AND/OR test, left/right neighbour communication takes < 20% extra chip area !

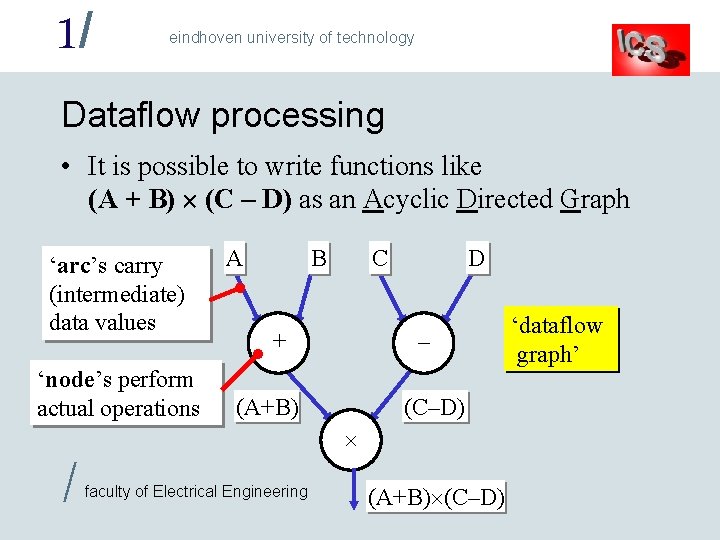

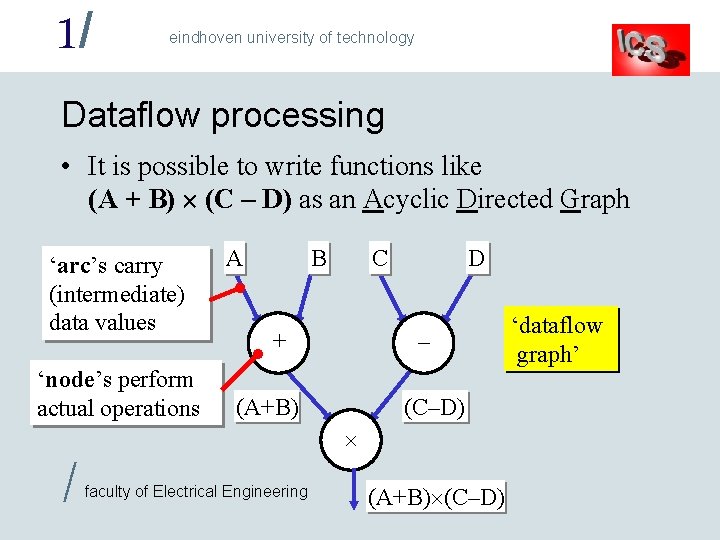

1/ eindhoven university of technology Dataflow processing • It is possible to write functions like (A + B) (C – D) as an Acyclic Directed Graph ‘arc’s carry (intermediate) data values ‘node’s perform actual operations / A B C + D – (A+B) (C–D) faculty of Electrical Engineering (A+B) (C–D) ‘dataflow graph’

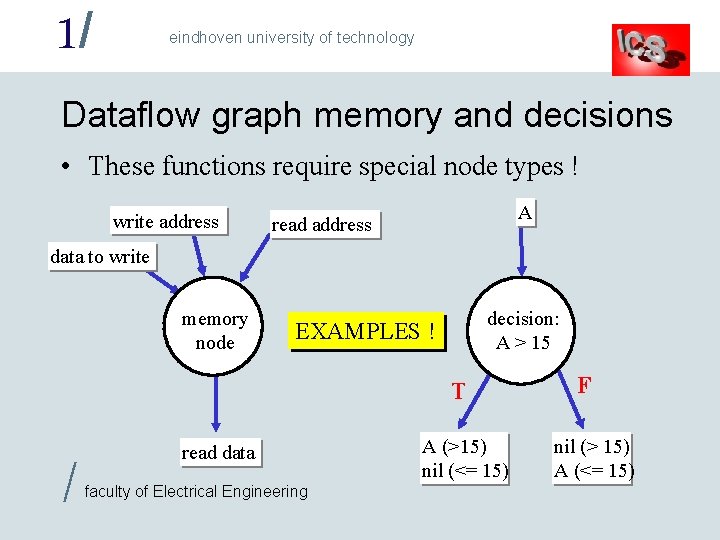

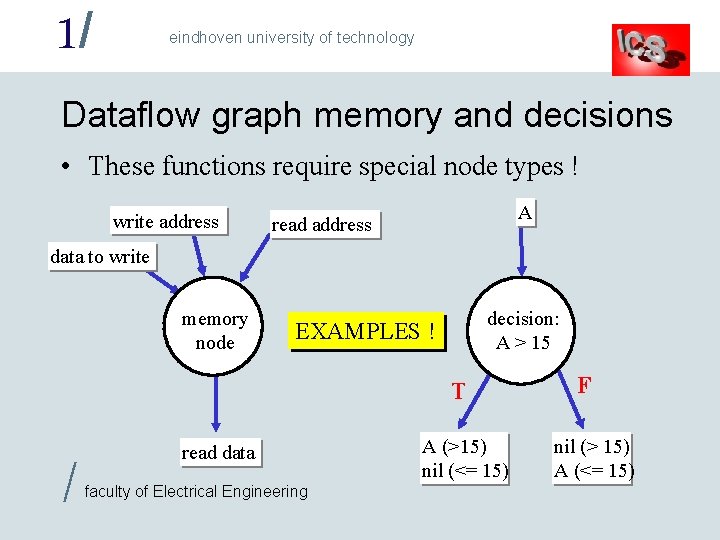

1/ eindhoven university of technology Dataflow graph memory and decisions • These functions require special node types ! write address A read address data to write memory node decision: A > 15 EXAMPLES ! T / read data faculty of Electrical Engineering A (>15) nil (<= 15) F nil (> 15) A (<= 15)

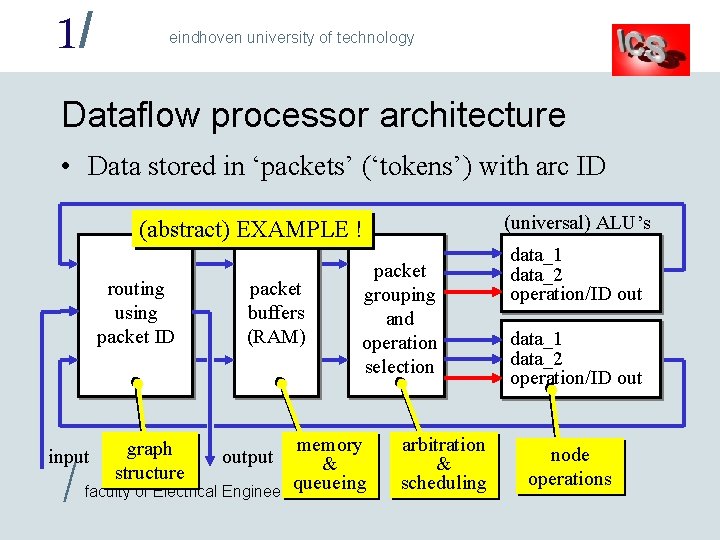

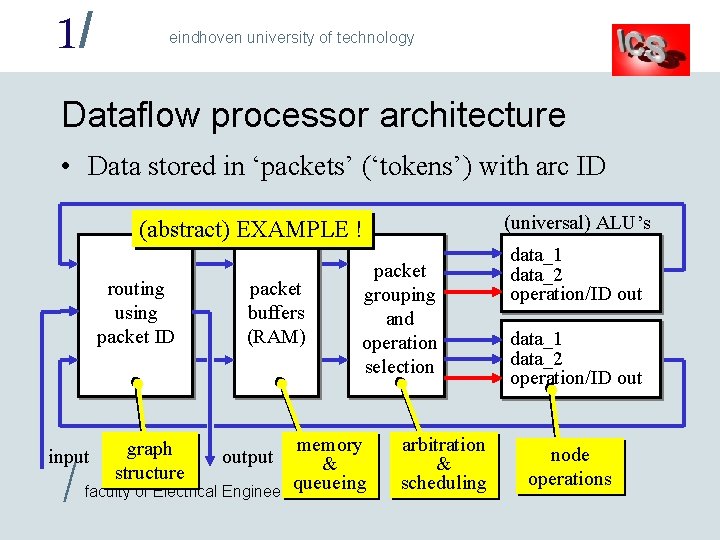

1/ eindhoven university of technology Dataflow processor architecture • Data stored in ‘packets’ (‘tokens’) with arc ID (universal) ALU’s (abstract) EXAMPLE ! routing using packet ID memory & queueing faculty of Electrical Engineering input / packet buffers (RAM) packet grouping and operation selection graph structure output arbitration & scheduling data_1 data_2 operation/ID out node operations

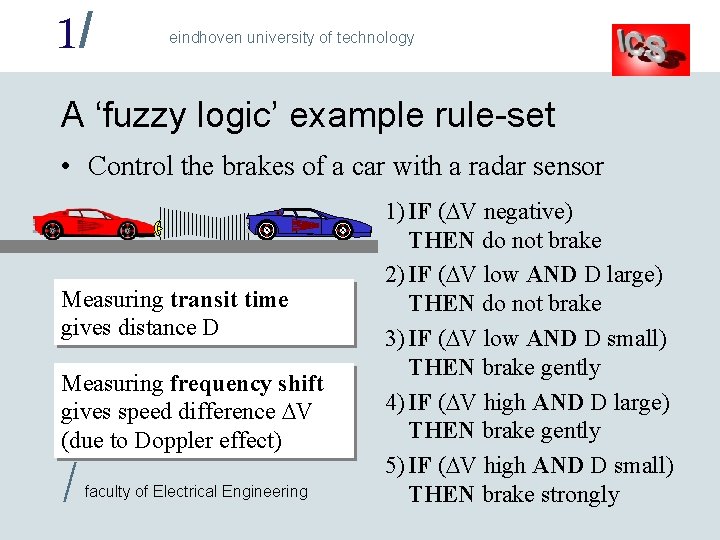

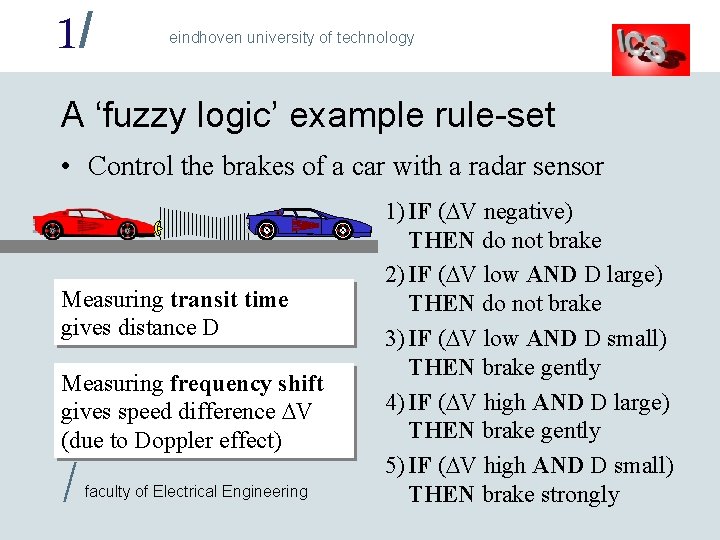

1/ eindhoven university of technology A ‘fuzzy logic’ example rule-set • Control the brakes of a car with a radar sensor Measuring transit time gives distance D Measuring frequency shift gives speed difference V (due to Doppler effect) / faculty of Electrical Engineering 1) IF ( V negative) THEN do not brake 2) IF ( V low AND D large) THEN do not brake 3) IF ( V low AND D small) THEN brake gently 4) IF ( V high AND D large) THEN brake gently 5) IF ( V high AND D small) THEN brake strongly

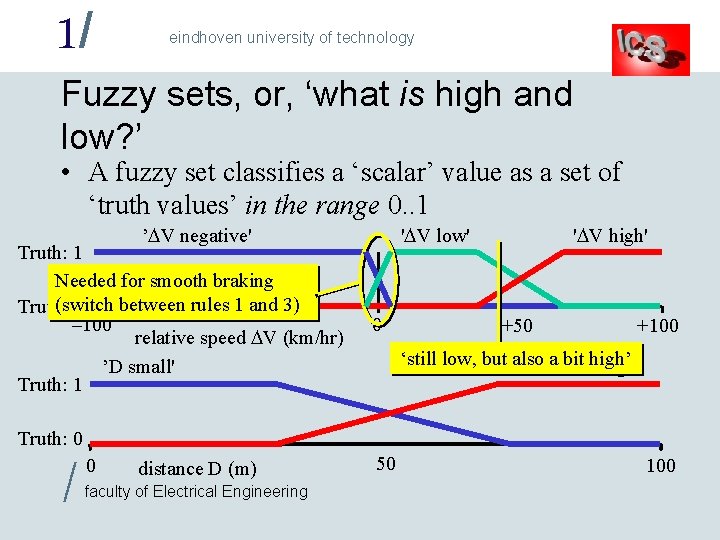

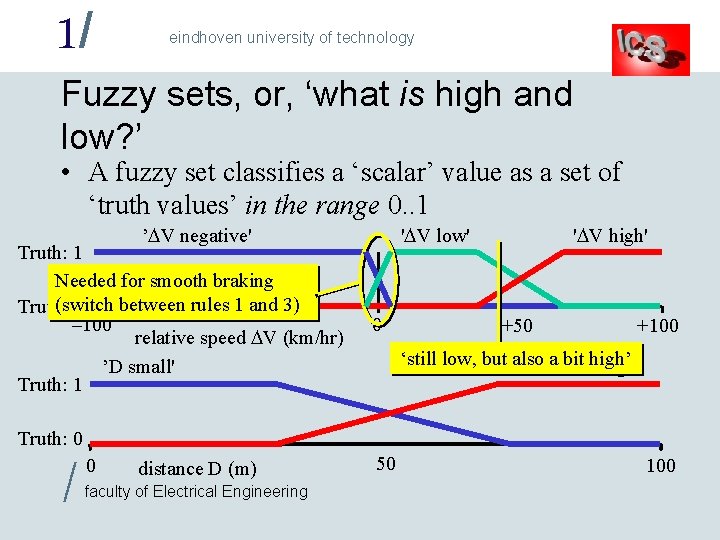

1/ eindhoven university of technology Fuzzy sets, or, ‘what is high and low? ’ • A fuzzy set classifies a ‘scalar’ value as a set of ‘truth values’ in the range 0. . 1 ’ V negative' Truth: 1 Needed for smooth braking (switch between rules 1 and 3) Truth: 0 – 100 relative speed V (km/hr) ’D small' Truth: 1 ' V low' 0 ' V high' +50 +100 ‘still low, but also a bit high’ ’D large' Truth: 0 / 0 distance D (m) faculty of Electrical Engineering 50 100

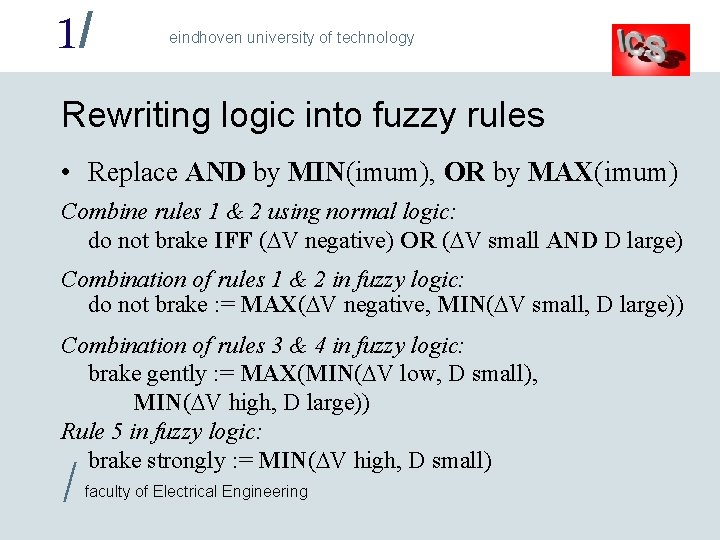

1/ eindhoven university of technology Rewriting logic into fuzzy rules • Replace AND by MIN(imum), OR by MAX(imum) Combine rules 1 & 2 using normal logic: do not brake IFF ( V negative) OR ( V small AND D large) Combination of rules 1 & 2 in fuzzy logic: do not brake : = MAX( V negative, MIN( V small, D large)) Combination of rules 3 & 4 in fuzzy logic: brake gently : = MAX(MIN( V low, D small), MIN( V high, D large)) Rule 5 in fuzzy logic: brake strongly : = MIN( V high, D small) / faculty of Electrical Engineering

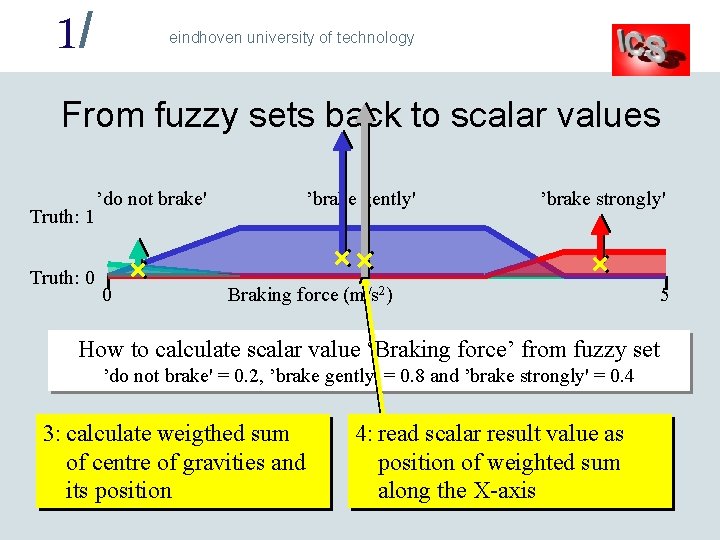

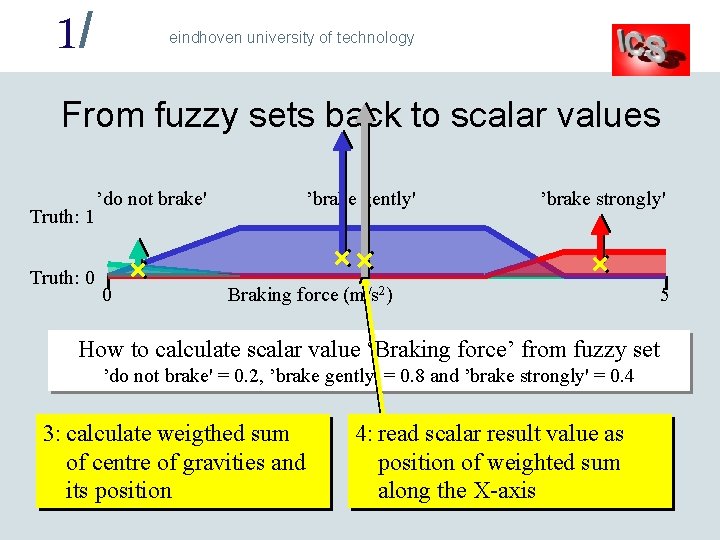

1/ eindhoven university of technology From fuzzy sets back to scalar values Truth: 1 Truth: 0 ’do not brake' 0 ’brake gently' ’brake strongly' Braking force (m/s 2) How to calculate scalar value ‘Braking force’ from fuzzy set ’do not brake' = 0. 2, ’brake gently' = 0. 8 and ’brake strongly' = 0. 4 2: 1: calculate weigthed sum calculate centre of gravity calculate weigthed sum 3: scale fuzzy set graphs 2: calculate centre of gravity 4: 3: read scalar result value as and surface area under the of centre of gravities and to their truth values and surface area under the position of weighted sum faculty of Electrical Engineering individual scaled graphs its position individual scaled graphs along the X-axis / 5

1/ eindhoven university of technology Fuzzy logic processors • Non time-critical applications: normal processors – Compilers exist: fuzzy set + logic rules C program • Fuzzy logic rules (‘MIN’/’MAX’) processors exist – Sometimes include scalar fuzzy set conversion – Almost never include fuzzy set scalar conversion – Advantageous to build them as dataflow machine • Fuzzy logic calculations need not be very precise / – Possible to build ‘processor’ with analog electronics ! faculty of Electrical Engineering

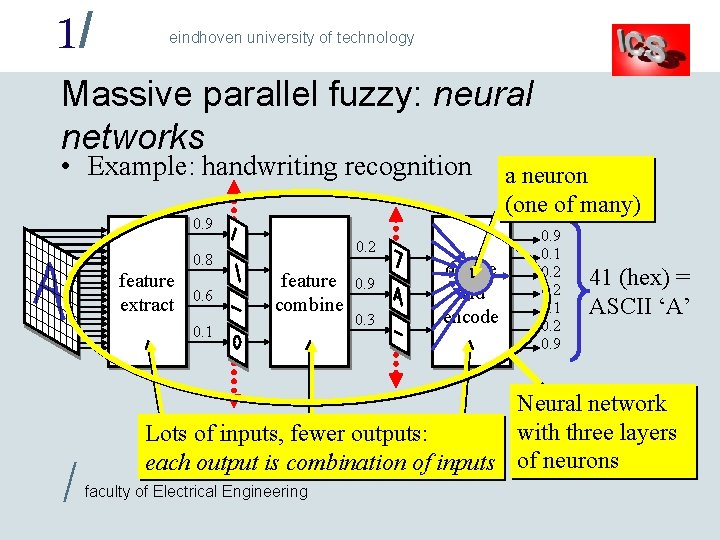

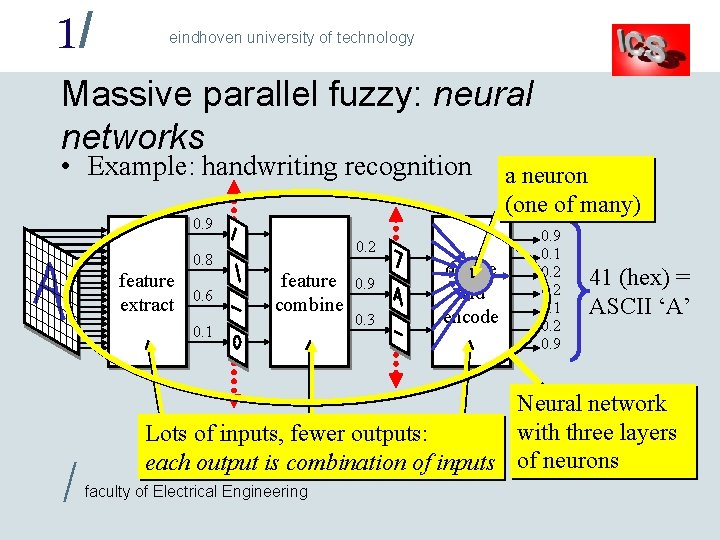

1/ eindhoven university of technology Massive parallel fuzzy: neural networks • Example: handwriting recognition 0. 9 0. 2 0. 8 feature extract 0. 6 feature combine 0. 1 / 0. 9 0. 3 decide and encode a neuron (one of many) 0. 9 0. 1 0. 2 0. 9 41 (hex) = ASCII ‘A’ Neural network with three layers Lots of inputs, fewer outputs: each output is combination of inputs of neurons faculty of Electrical Engineering

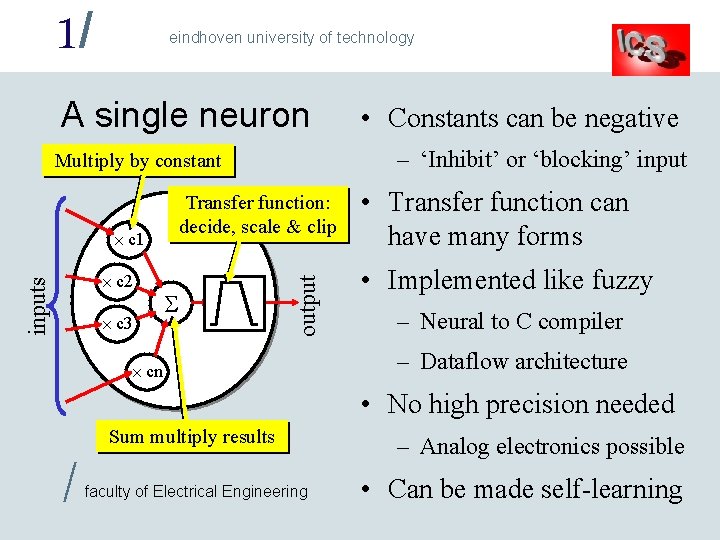

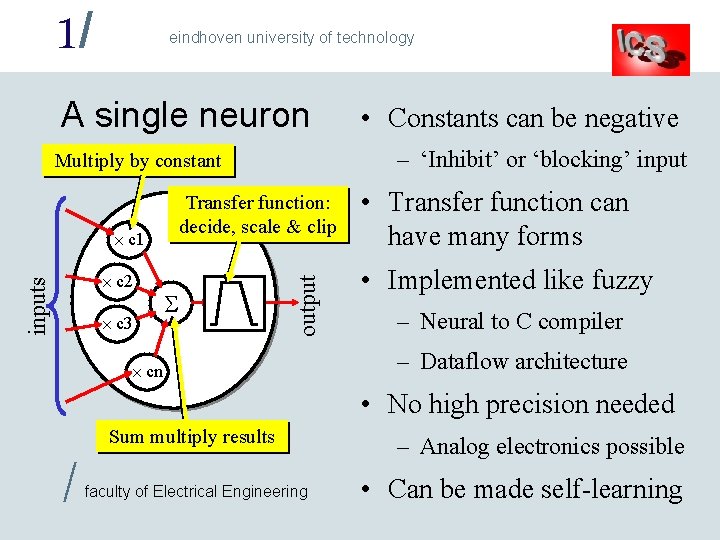

1/ eindhoven university of technology A single neuron – ‘Inhibit’ or ‘blocking’ input Multiply by constant inputs c 2 c 3 output Transfer function: decide, scale & clip c 1 • Constants can be negative cn • Transfer function can have many forms • Implemented like fuzzy – Neural to C compiler – Dataflow architecture • No high precision needed Sum multiply results / faculty of Electrical Engineering – Analog electronics possible • Can be made self-learning