VLSI Digital System Design InputOutput Pads 1 InputOutput

- Slides: 15

VLSI Digital System Design Input-Output Pads 1

Input-Output Pad Design • I-O pad design is highly specialized – Requires circuit design experience – Requires fabrication process understanding • Choose already-characterized library from: – Fabrication vendor – Third-party library vendor – In-house group 2

Pad Size and Spacing • Pad size – Smallest to which a wire can be bonded – 100 – 150 μm • Pad spacing – Smallest to which a bonding machine can bond – 150 – 200 μm 3

Interdigitated Pads • Allows more pads on die I-O circuitry 4

IBM C 4 I-O Pads • Bonding wires restrict I-O pads to die edge • IBM C 4 I-O pads can also be on interior of chip 1. Deposit solder ball on I-O pad 2. Heat die and board to reflow solder 3. Solder surface tension positions die on board 5

Latchup • Latchup occurs when voltage excursion outside VSS < v < VDD • Most likely at I-O pad – Large transistors – High current – Inductance of bonding wire – Connection to external circuitry 6

Output Pad Latchup Prevention • Separate the n. MOS and p. MOS transistors • Separate the power supplies for I-O from internal logic • Guard rings 7

Guard Rings • Ohmic contacts to metal – p+ diffusion in p-substrate – n+ diffusion in n-well • Collect minority carriers – Injected into substrate when drain diodes are forward-biased • Rings should be continuous diffusion – No crossovers 8

Double Guard Rings • Surround n. MOS transistor by: – p+ connection to VSS, surrounded by – n-well with n+ connection to VDD • Surround p. MOS transistor by: – p+ ring connected to VDD, surrounded by – n-well with n+ connection to VSS 9

Use Smaller Transistors in Parallel • Minimize gate – Reduce RC delay – I-O pad transistors often have long gates • Improve avalanche breakdown characteristics • Parallel metal-transistor connections – Minimize metal migration 10

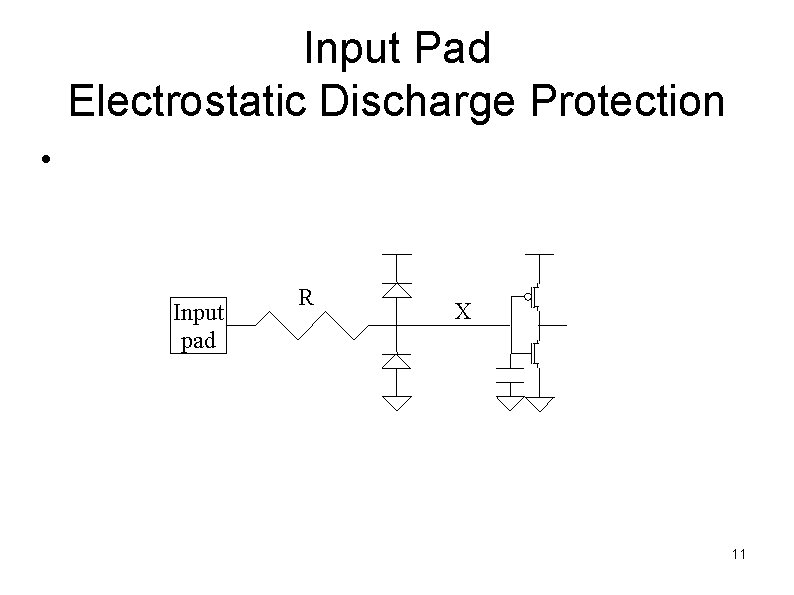

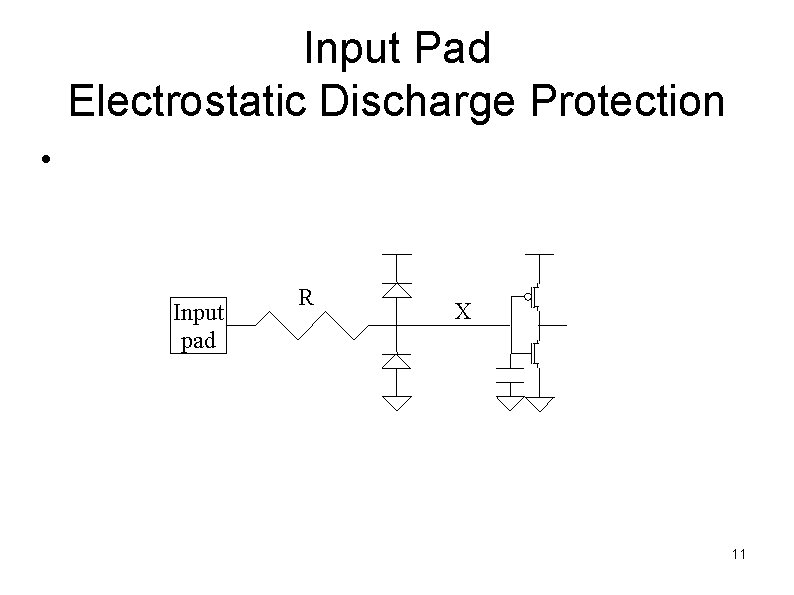

Input Pad Electrostatic Discharge Protection • Input pad R X 11

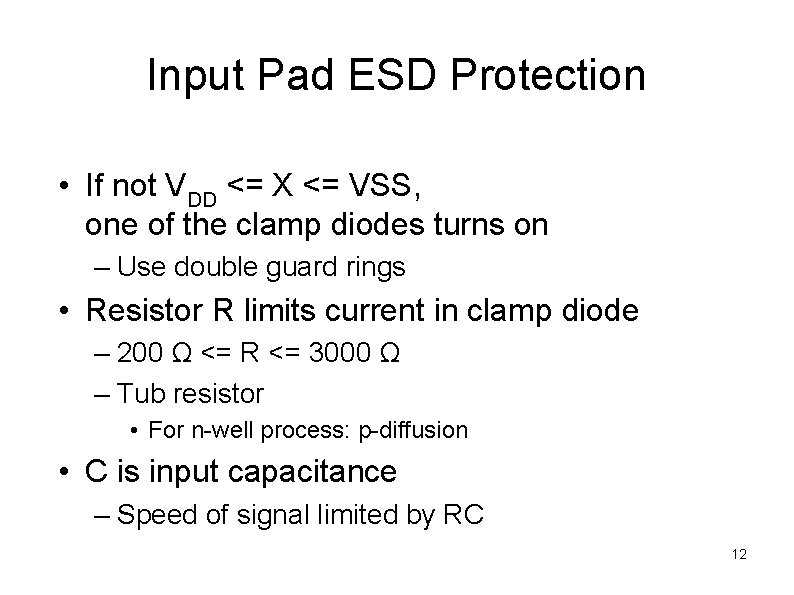

Input Pad ESD Protection • If not VDD <= X <= VSS, one of the clamp diodes turns on – Use double guard rings • Resistor R limits current in clamp diode – 200 Ω <= R <= 3000 Ω – Tub resistor • For n-well process: p-diffusion • C is input capacitance – Speed of signal limited by RC 12

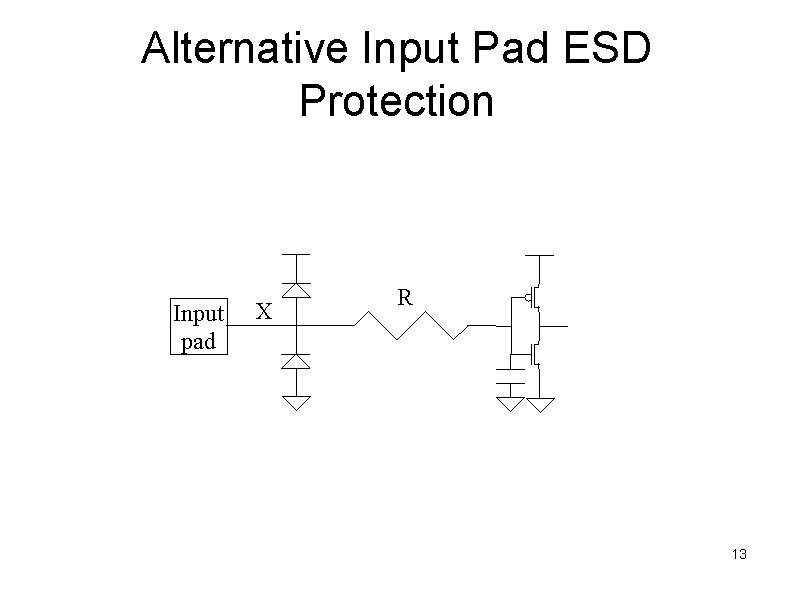

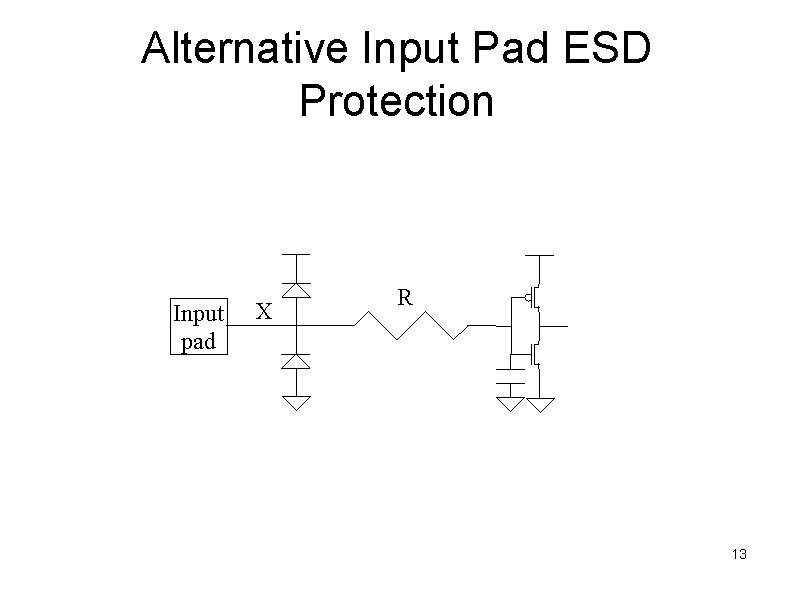

Alternative Input Pad ESD Protection Input pad X R 13

Punch-Through Device • Built of closely-spaced source and drain diffusions – No gate • “Avalanches” at c. 50 V 14

Pull-Up or Pull-Down Resistor • Long p. MOS transistor • Long n. MOS transistor • Connect gate to signal for IDDQ testing 15