UNIT 4 Central Processing Unit Mother Board 2

UNIT – 4 Central Processing Unit

Mother. Board 2

Mother. Board 3

4

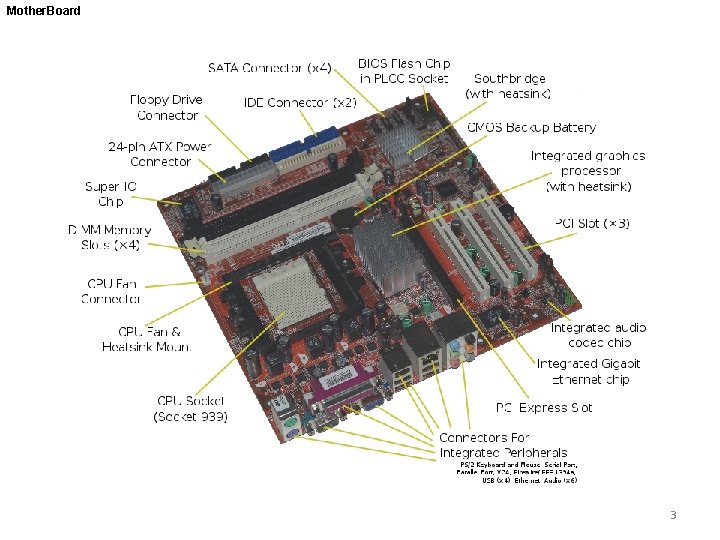

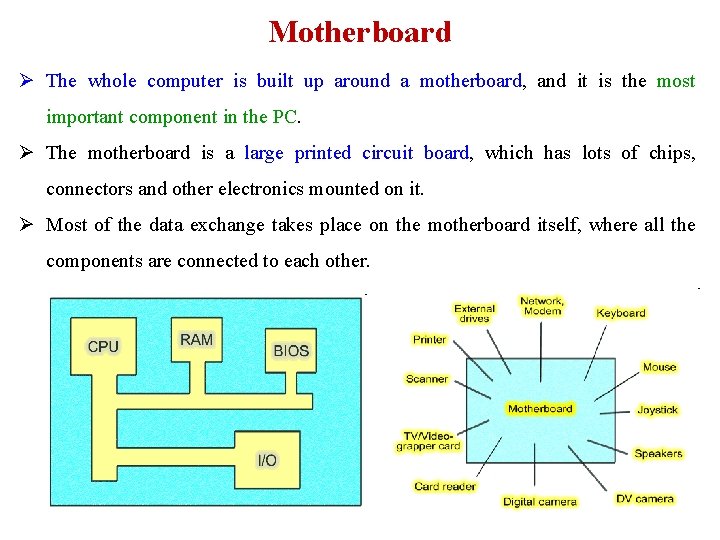

Motherboard Ø The whole computer is built up around a motherboard, and it is the most important component in the PC. Ø The motherboard is a large printed circuit board, which has lots of chips, connectors and other electronics mounted on it. Ø Most of the data exchange takes place on the motherboard itself, where all the components are connected to each other.

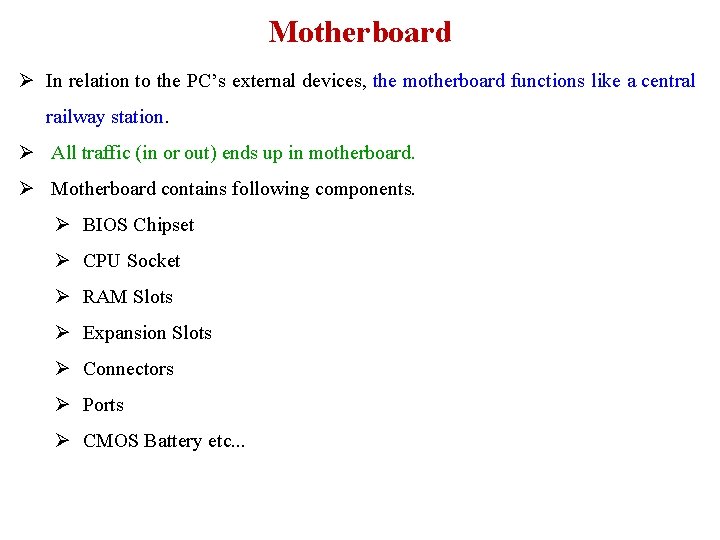

Motherboard Ø In relation to the PC’s external devices, the motherboard functions like a central railway station. Ø All traffic (in or out) ends up in motherboard. Ø Motherboard contains following components. Ø BIOS Chipset Ø CPU Socket Ø RAM Slots Ø Expansion Slots Ø Connectors Ø Ports Ø CMOS Battery etc. . .

What is BIOS? Ø Acronym for basic input/output system, the built-in software that determines what a computer can do without accessing programs from a disk. Ø On PCs, the BIOS contains all the code required to control the keyboard, display screen, disk drives, serial communications, and a number of miscellaneous functions. Ø The BIOS is typically placed in a ROM chip that comes with the computer. Ø This ensures that the BIOS will always be available and will not be damaged by disk failures. Ø RAM is faster than ROM, though, many computer manufacturers design systems so that the BIOS is copied from ROM to RAM each time the computer is booted. This is known as shadowing.

CPU Socket Ø Motherboards are subcategorized by the type of processor socket they have. Ø The processor socket (also called a CPU socket) is the connector on the motherboard that houses a CPU and forms the electrical interface and contact with the CPU. Ø Processor sockets use a pin grid array (PGA) where pins on the underside of the processor connect to holes in the processor socket.

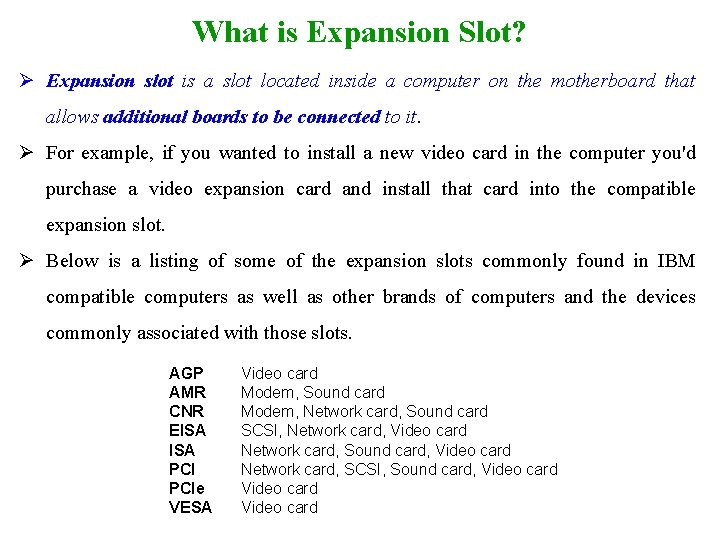

What is Expansion Slot? Ø Expansion slot is a slot located inside a computer on the motherboard that allows additional boards to be connected to it. Ø For example, if you wanted to install a new video card in the computer you'd purchase a video expansion card and install that card into the compatible expansion slot. Ø Below is a listing of some of the expansion slots commonly found in IBM compatible computers as well as other brands of computers and the devices commonly associated with those slots. AGP AMR CNR EISA PCI PCIe VESA Video card Modem, Sound card Modem, Network card, Sound card SCSI, Network card, Video card Network card, Sound card, Video card Network card, SCSI, Sound card, Video card

What is a CMOS battery? Ø All personal computers require a small battery on the system board that provides power to the Complementary Metal Oxide Semiconductor (CMOS) chip, even while the computer is turned off. Ø This chip contains information about the system configuration (e. g. , hard disk type, floppy drive types, date and time, and the order in which the computer will look for bootable disks).

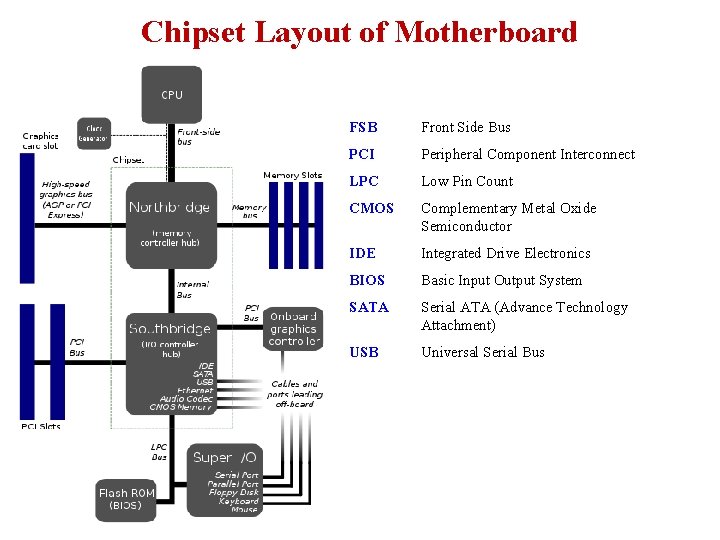

Chipset Layout of Motherboard FSB Front Side Bus PCI Peripheral Component Interconnect LPC Low Pin Count CMOS Complementary Metal Oxide Semiconductor IDE Integrated Drive Electronics BIOS Basic Input Output System SATA Serial ATA (Advance Technology Attachment) USB Universal Serial Bus

Chipset Ø A chipset, PC chipset, or chip set refers to a group of integrated circuits, or chips, that are designed to work together. Ø They are usually marketed as a single product. Ø A chipset is usually designed to work with a specific family of microprocessors. Because it controls communications between the processor and external devices, the chipset plays a crucial role in determining system performance. Ø Current manufacturers of chipsets : NVIDIA, AMD, VIA Technologies, Si. S, Intel and Broadcom.

CPU (Central Processing Unit) Ø CPU contains following sub components. Ø ALU Ø CU Ø Set of Registers to store data temporary. Ø The CPU Speed is depend on the Clock Rate ( Clock Speed ). Higher the Clock speed, Higher number of Instructions executed by the CPU. Ø CPU is connected with memory using three separate Buses (inside FSB). Ø Data Bus ( To transfer data from memory to cpu and vice versa. ) Ø Address Bus ( To transfer address from cpu to memory ) Ø Control Bus ( To transfer control like Read Data, Write Data etc. )

Front-Side Bus (FSB) Ø A front-side bus (FSB) is a computer communication interface (bus) often used in computers during the 1990 s and 2000 s. Ø It typically carries data between the central processing unit (CPU) and a memory controller hub, known as the northbridge. Ø Depending on the implementation, some computers may also have a back-side bus that connects the CPU to the cache. This bus and the cache connected to it are faster than accessing the system memory (or RAM) via the front-side bus. Ø The speed of the front side bus is often used as an important measure of the performance of a computer.

PCI Ø PCI is an short formed from Peripheral Component Interconnect, part of the PCI Local Bus standard. Ø PCI is a computer bus for attaching hardware devices in a computer. Ø These devices can take either the form of an integrated circuit fitted onto the motherboard itself, called a planar device in the PCI specification, or an expansion card that fits into a slot. Ø Typical PCI cards used in PCs include: network cards, sound cards, modems, extra ports such as USB or serial, TV tuner cards and disk controllers.

AGP (Accelerated Graphics Port) Ø The Accelerated Graphics Port (often shortened to AGP) is a high-speed point-to-point channel for attaching a video card to a computer's motherboard, primarily to assist in the acceleration of 3 D computer graphics. Ø The primary advantage of AGP over PCI is that it provides a dedicated pathway between the slot and the processor rather than sharing the PCI bus. In addition, the direct connection allows for higher clock speeds. Ø AGP also uses sideband addressing, meaning that the address and data buses are separated so the entire packet does not need to be read to get addressing information. Ø In addition, to load a texture, a PCI graphics card must copy it from the system's RAM into the card's framebuffer, whereas an AGP card is capable of reading textures directly from system RAM using the graphics address remapping table

North. Bridge Ø The Northbridge typically handles communications among the CPU, in some cases RAM, and PCI Express (or AGP) video cards, and the Southbridge. Ø Some Northbridge also contain integrated video controllers, also known as a Graphics and Memory Controller Hub (GMCH) in Intel systems. Ø There a few chipsets that support two types of RAM (generally these are available when there is a shift to a new standard). Ø For example, the Intel i 875 chipset will only work with systems using Pentium 4 processors or Celeron processors that have a clock speed greater than 1. 3 GHz and utilize DDR SDRAM, and the Intel i 915 g chipset only works with the Intel Pentium 4 and the Celeron, but it can use DDR or DDR 2 memory.

South. Bridge Ø A Southbridge chipset handles all of a computer's I/O functions, such as USB, audio, serial, the system BIOS, the ISA bus, the interrupt controller and the IDE channels. Ø Different combinations of Southbridge and Northbridge chips are possible, but these two kinds of chip must be designed to work together; there is no industry-wide standard for interoperability between different core logic chipset designs. Ø Traditionally, the interface between a Northbridge and Southbridge was the PCI bus. Ø The main bridging interfaces used now are DMI (Direct Media Interface ) for Intel and UMI (Unified Media Interface) for AMD.

CISC Processor Ø CISC is an acronym for Complex Instruction Set Computer. Ø CISC are chips that are easy to program and which make efficient use of memory. Ø Since the earliest machines were programmed in assembly language and memory was slow and expensive, the CISC philosophy made sense, and was commonly implemented in such large computers. Ø Most common microprocessor designs such as the Intel 80 x 86 and Motorola 68 K series followed the CISC philosophy. Ø CISC was developed to make compiler development simpler. It shifts most of the burden of generating machine instructions to the processor.

CISC Processor Ø For example, instead of having to make a compiler write long machine instructions to calculate a square-root, a CISC processor would have a built-in ability to do this. CISC Processor Attributes Ø A 2 -operand format, where instructions have a source and a destination. Register to register, register to memory, and memory to register commands. Ø Variable length instructions where the length often varies according to the addressing mode Ø Instructions which require multiple clock cycles to execute. Ø E. g. Pentium is considered a modern CISC processor

RISC Processor Ø RISC is an acronym for Reduced Instruction Set Computer. Ø It is a type of microprocessor architecture that utilizes a small, highly-optimized set of instructions, rather than a more specialized set of instructions often found in other types of architectures. Attributes of most RISC processors: Ø one cycle execution time: RISC processors have a CPI (clock per instruction) of one cycle. This is due to the optimization of each instruction on the CPU and a technique called PIPELINING Ø pipelining: a technique that allows for simultaneous execution of parts, or stages, of instructions to more efficiently process instructions; Ø large number of registers: the RISC design philosophy generally incorporates a larger number of registers to prevent in large amounts of interactions with memory

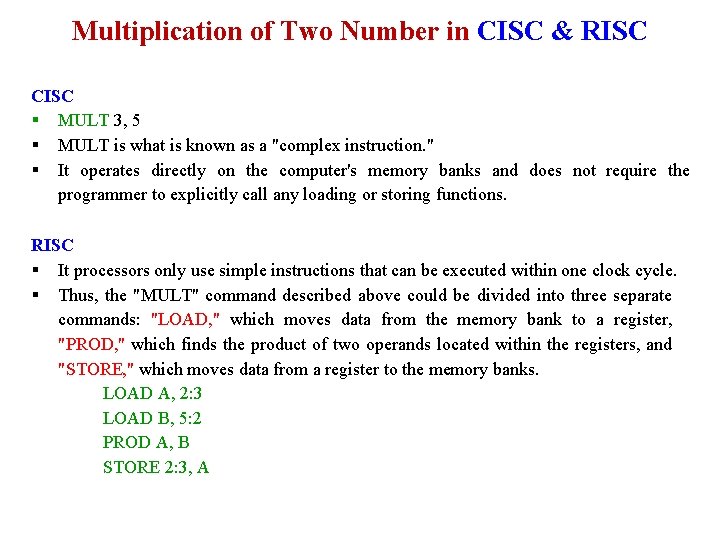

Multiplication of Two Number in CISC & RISC CISC § MULT 3, 5 § MULT is what is known as a "complex instruction. " § It operates directly on the computer's memory banks and does not require the programmer to explicitly call any loading or storing functions. RISC § It processors only use simple instructions that can be executed within one clock cycle. § Thus, the "MULT" command described above could be divided into three separate commands: "LOAD, " which moves data from the memory bank to a register, "PROD, " which finds the product of two operands located within the registers, and "STORE, " which moves data from a register to the memory banks. LOAD A, 2: 3 LOAD B, 5: 2 PROD A, B STORE 2: 3, A

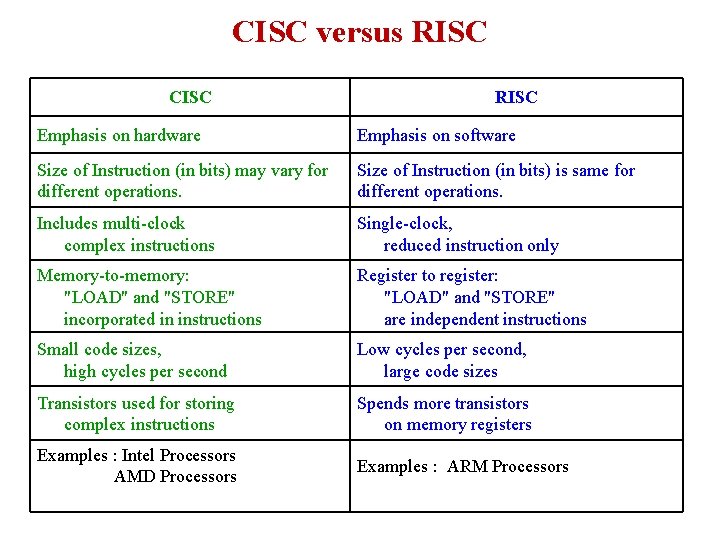

CISC versus RISC CISC RISC Emphasis on hardware Emphasis on software Size of Instruction (in bits) may vary for different operations. Size of Instruction (in bits) is same for different operations. Includes multi-clock complex instructions Single-clock, reduced instruction only Memory-to-memory: "LOAD" and "STORE" incorporated in instructions Register to register: "LOAD" and "STORE" are independent instructions Small code sizes, high cycles per second Low cycles per second, large code sizes Transistors used for storing complex instructions Spends more transistors on memory registers Examples : Intel Processors AMD Processors Examples : ARM Processors

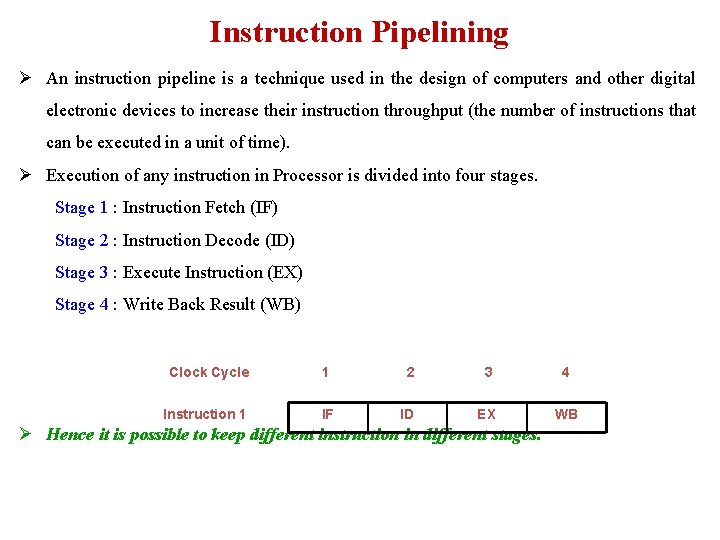

Instruction Pipelining Ø An instruction pipeline is a technique used in the design of computers and other digital electronic devices to increase their instruction throughput (the number of instructions that can be executed in a unit of time). Ø Execution of any instruction in Processor is divided into four stages. Stage 1 : Instruction Fetch (IF) Stage 2 : Instruction Decode (ID) Stage 3 : Execute Instruction (EX) Stage 4 : Write Back Result (WB) Clock Cycle 1 2 3 4 Instruction 1 IF ID EX WB Ø Hence it is possible to keep different instruction in different stages.

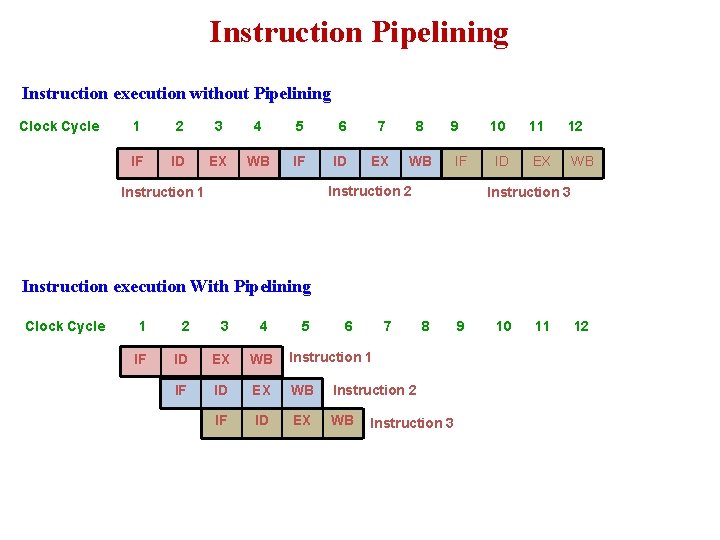

Instruction Pipelining Instruction execution without Pipelining Clock Cycle 1 2 3 4 5 6 7 8 IF ID EX WB 9 IF Instruction 2 Instruction 1 10 ID 11 12 EX WB Instruction 3 Instruction execution With Pipelining Clock Cycle 1 2 3 4 5 6 7 IF ID EX WB Instruction 1 IF ID EX WB Instruction 2 IF ID EX WB 8 Instruction 3 9 10 11 12

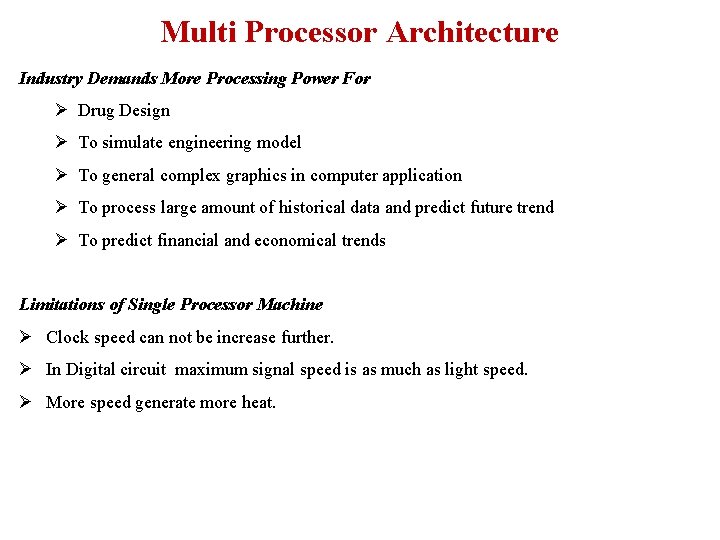

Multi Processor Architecture Industry Demands More Processing Power For Ø Drug Design Ø To simulate engineering model Ø To general complex graphics in computer application Ø To process large amount of historical data and predict future trend Ø To predict financial and economical trends Limitations of Single Processor Machine Ø Clock speed can not be increase further. Ø In Digital circuit maximum signal speed is as much as light speed. Ø More speed generate more heat.

Multi Processor Architecture Ø A multiprocessor is a computer system with two or more central processing units (CPUs), with each one sharing the common main memory as well as the peripherals. This helps in simultaneous processing of programs. Benefits of using a multiprocessor include: Ø Enhanced performance Ø Multiple applications Ø Multiple users Ø Multi-tasking inside an application Ø High throughput and/or responsiveness Ø Hardware sharing among CPUs

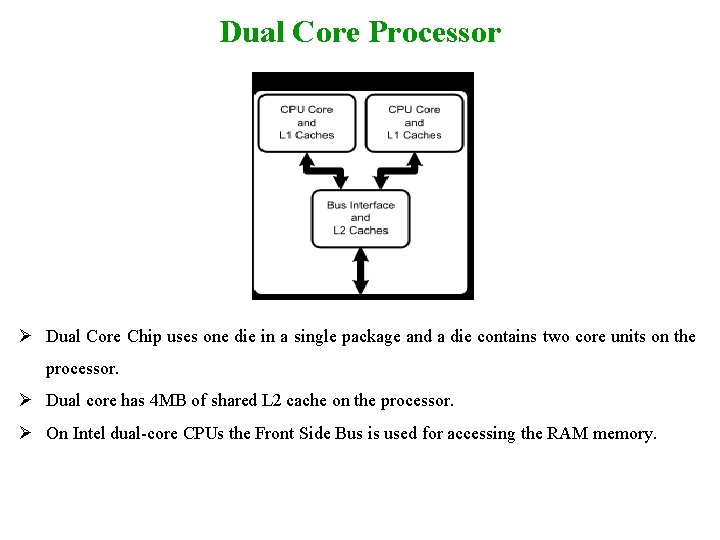

Dual Core Processor Ø Dual Core Chip uses one die in a single package and a die contains two core units on the processor. Ø Dual core has 4 MB of shared L 2 cache on the processor. Ø On Intel dual-core CPUs the Front Side Bus is used for accessing the RAM memory.

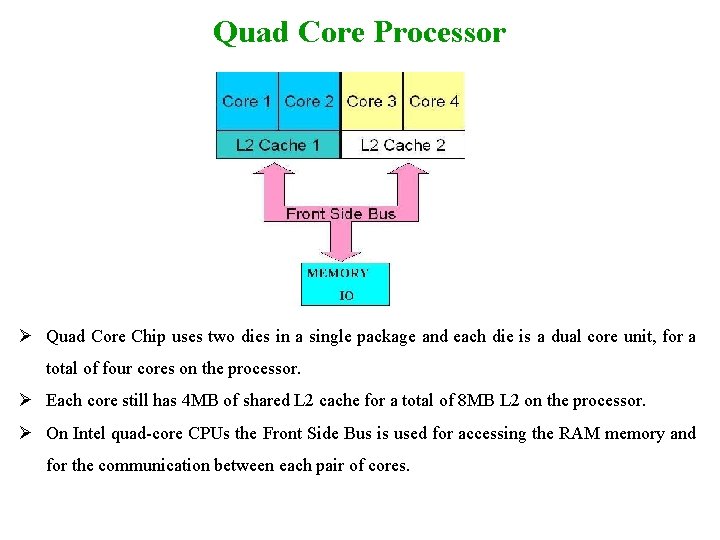

Quad Core Processor Ø Quad Core Chip uses two dies in a single package and each die is a dual core unit, for a total of four cores on the processor. Ø Each core still has 4 MB of shared L 2 cache for a total of 8 MB L 2 on the processor. Ø On Intel quad-core CPUs the Front Side Bus is used for accessing the RAM memory and for the communication between each pair of cores.

Multiprocessor in Multi computers Ø Multiprocessor systems can be build by connecting hundred of computers with single processor. Ø Computers co ordinate by various programming language facility like message passing. Ø This is a low cost solution to achieve 100 CPUs speed using ordinary computers. Ø Examples are Cluster Computing, Grid Computing, Cloud Computing

I/O devices Data Transfer Methods Ø Three methods are used to transfer data between memory and I/O devices. Ø Programmed I/O transfer Ø Interrupted I/O transfer Ø DMA (Direct Memory Access ) transfer

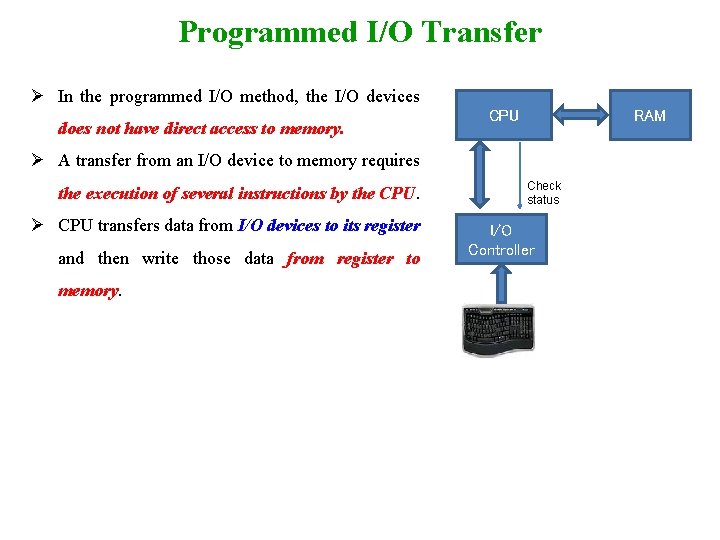

Programmed I/O Transfer Ø In the programmed I/O method, the I/O devices does not have direct access to memory. CPU RAM Ø A transfer from an I/O device to memory requires the execution of several instructions by the CPU. Ø CPU transfers data from I/O devices to its register and then write those data from register to memory. Check status I/O Controller

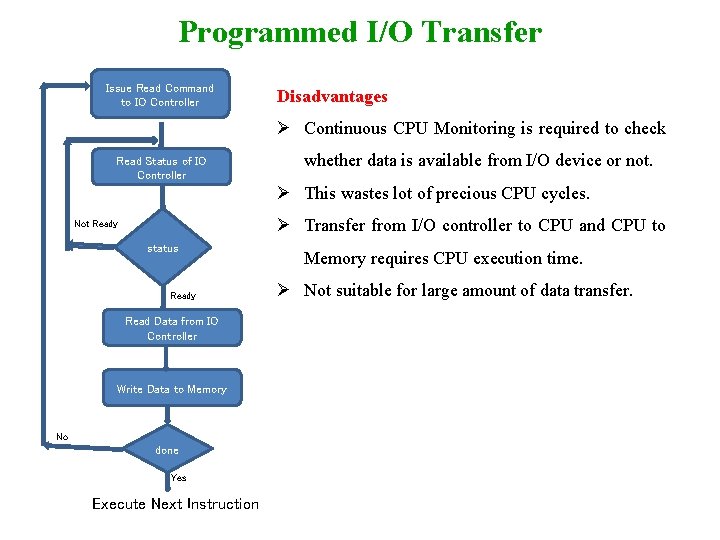

Programmed I/O Transfer Issue Read Command to IO Controller Disadvantages Ø Continuous CPU Monitoring is required to check Read Status of IO Controller whether data is available from I/O device or not. Ø This wastes lot of precious CPU cycles. Ø Transfer from I/O controller to CPU and CPU to Not Ready status Ready Read Data from IO Controller Write Data to Memory No done Yes Execute Next Instruction Memory requires CPU execution time. Ø Not suitable for large amount of data transfer.

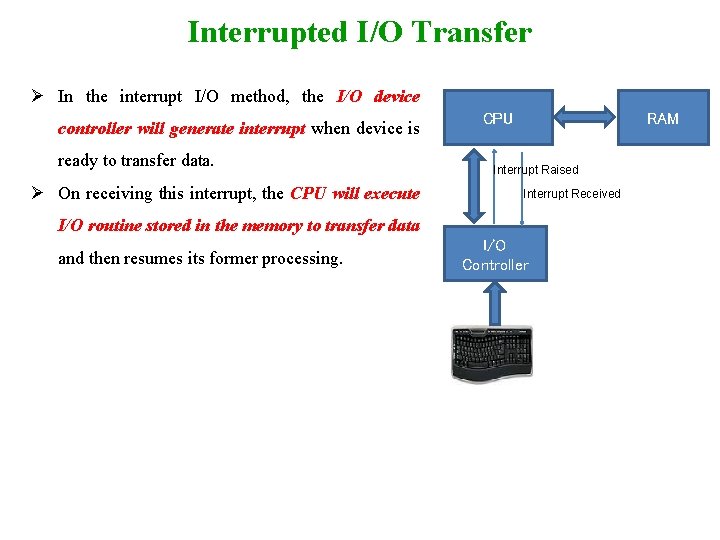

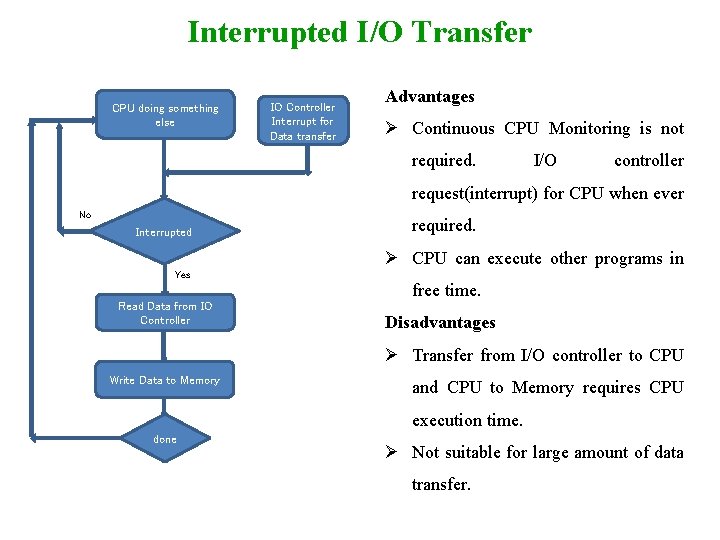

Interrupted I/O Transfer Ø In the interrupt I/O method, the I/O device controller will generate interrupt when device is ready to transfer data. Ø On receiving this interrupt, the CPU will execute CPU RAM Interrupt Raised Interrupt Received I/O routine stored in the memory to transfer data and then resumes its former processing. I/O Controller

Interrupted I/O Transfer CPU doing something else IO Controller Interrupt for Data transfer Advantages Ø Continuous CPU Monitoring is not required. I/O controller request(interrupt) for CPU when ever No Interrupted required. Ø CPU can execute other programs in Yes Read Data from IO Controller free time. Disadvantages Ø Transfer from I/O controller to CPU Write Data to Memory and CPU to Memory requires CPU execution time. done Ø Not suitable for large amount of data transfer.

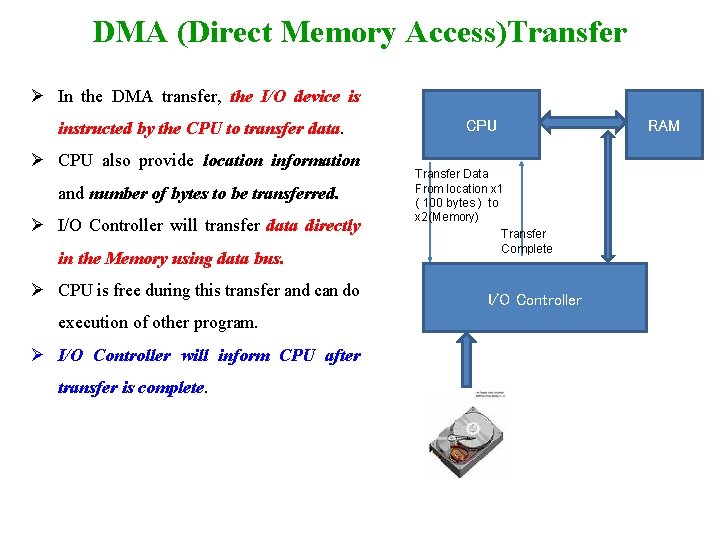

DMA (Direct Memory Access)Transfer Ø In the DMA transfer, the I/O device is instructed by the CPU to transfer data. Ø CPU also provide location information and number of bytes to be transferred. Ø I/O Controller will transfer data directly in the Memory using data bus. Ø CPU is free during this transfer and can do execution of other program. Ø I/O Controller will inform CPU after transfer is complete. CPU Transfer Data From location x 1 ( 100 bytes ) to x 2(Memory) Transfer Complete I/O Controller RAM

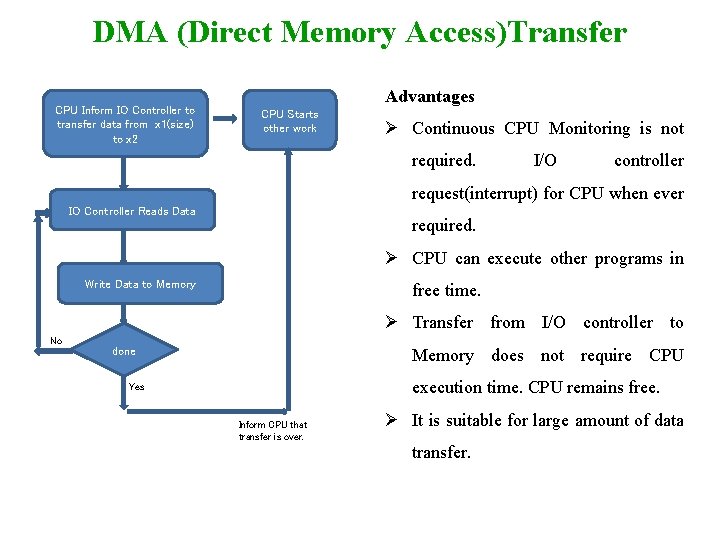

DMA (Direct Memory Access)Transfer CPU Inform IO Controller to transfer data from x 1(size) to x 2 Advantages CPU Starts other work Ø Continuous CPU Monitoring is not required. I/O controller request(interrupt) for CPU when ever IO Controller Reads Data required. Ø CPU can execute other programs in Write Data to Memory free time. Ø Transfer from I/O controller to No done Memory does not require CPU execution time. CPU remains free. Yes Inform CPU that transfer is over. Ø It is suitable for large amount of data transfer.

Thank You 38

- Slides: 38