UltraLow Power OnChip Differential Interconnects Using HighResolution Comparator

- Slides: 22

Ultra-Low Power On-Chip Differential Interconnects Using High-Resolution Comparator Hao Liu and Chung-Kuan Cheng University of California, San Diego 10/22/2012

• Content • Introduction • Architecture of On-Chip Global Link • Receiver: Comparator and Latch • Transmission-line • Driver: CTLE and LVDS • Simulation Results • Conclusion Page 2

• Ultra-Low Power On-Chip Differential Interconnects Using High-Resolution Comparator Introduction Page 3

Introduction On-Chip Interconnect Issues (45 nm node) Power: ~0. 2 p. J/mm/b Delay: ~70 ps/mm Throughput: ~10 Gbp/um Current Density Page 4

Introduction Goal • Ultra-low power on chip interconnection • Ultra-low power high resolution comparator • LTE-combined LVDS buffer • Model as PTM 64 nm LVT • 1. 1 V, 0. 8 v split power supply • 10 GHz, top Layer 10 mm/intermediate layer 2. 5 mm connection • FOM ~20 f. J/mm/b Page 5

• Ultra-Low Power On-Chip Differential Interconnects Using High-Resolution Comparator Architecture of On-Chip Global Link Page 6

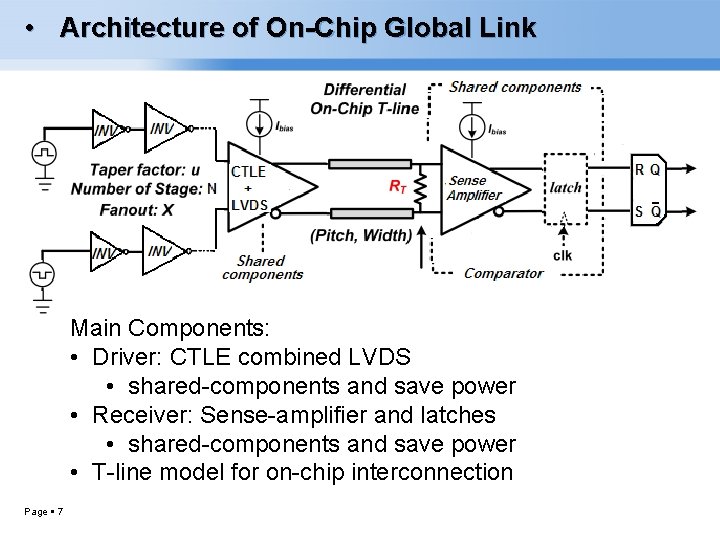

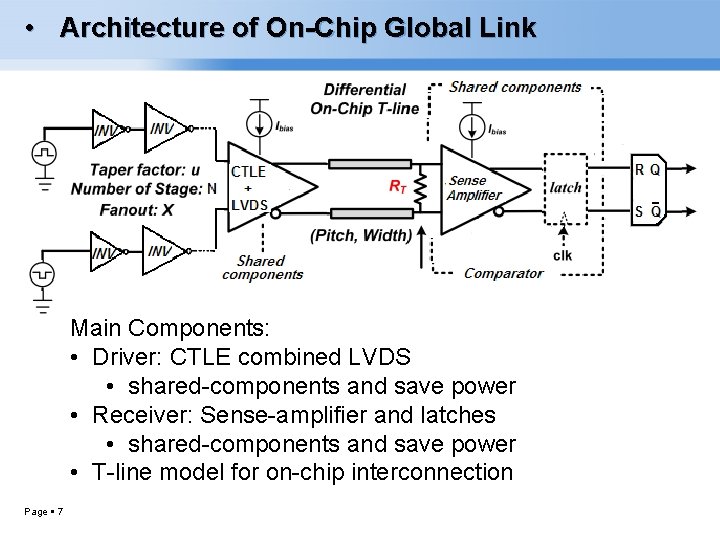

• Architecture of On-Chip Global Link Main Components: • Driver: CTLE combined LVDS • shared-components and save power • Receiver: Sense-amplifier and latches • shared-components and save power • T-line model for on-chip interconnection Page 7

• Ultra-Low Power On-Chip Differential Interconnects Using High-Resolution Comparator Receiver: Comparator and Latch Page 8

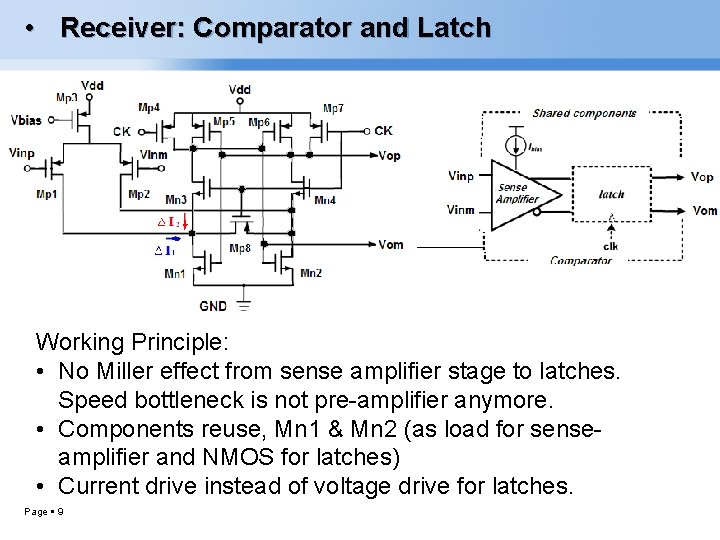

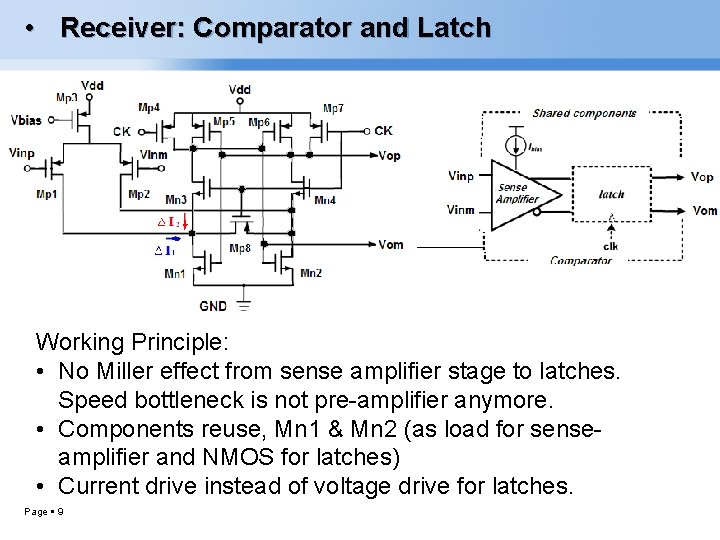

• Receiver: Comparator and Latch Working Principle: • No Miller effect from sense amplifier stage to latches. Speed bottleneck is not pre-amplifier anymore. • Components reuse, Mn 1 & Mn 2 (as load for senseamplifier and NMOS for latches) • Current drive instead of voltage drive for latches. Page 9

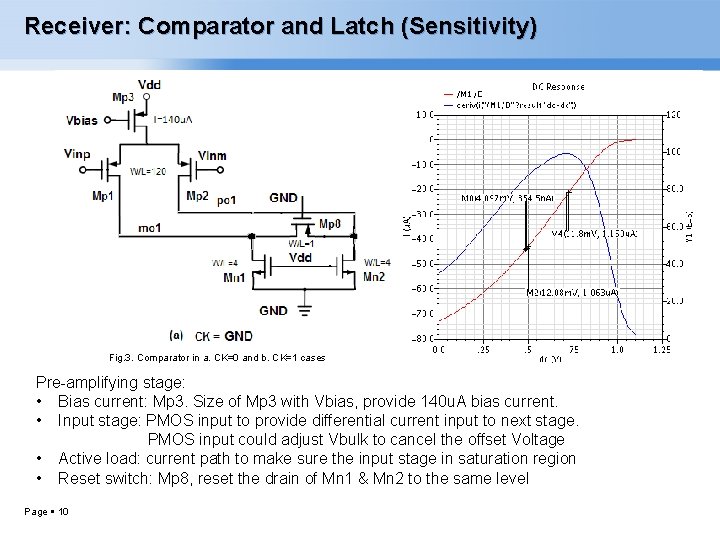

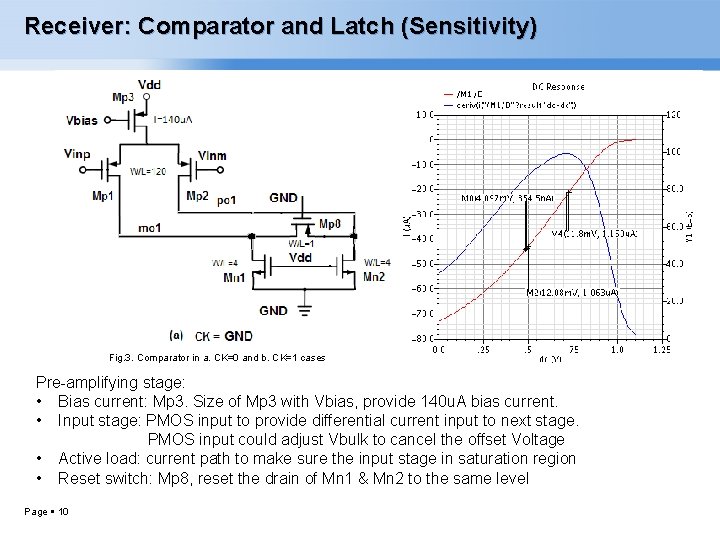

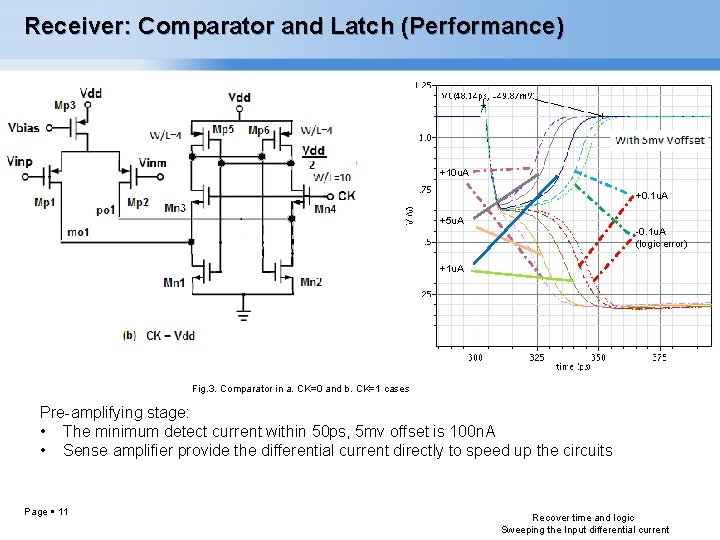

Receiver: Comparator and Latch (Sensitivity) Fig. 3. Comparator in a. CK=0 and b. CK=1 cases Pre-amplifying stage: • Bias current: Mp 3. Size of Mp 3 with Vbias, provide 140 u. A bias current. • Input stage: PMOS input to provide differential current input to next stage. PMOS input could adjust Vbulk to cancel the offset Voltage • Active load: current path to make sure the input stage in saturation region • Reset switch: Mp 8, reset the drain of Mn 1 & Mn 2 to the same level Page 10

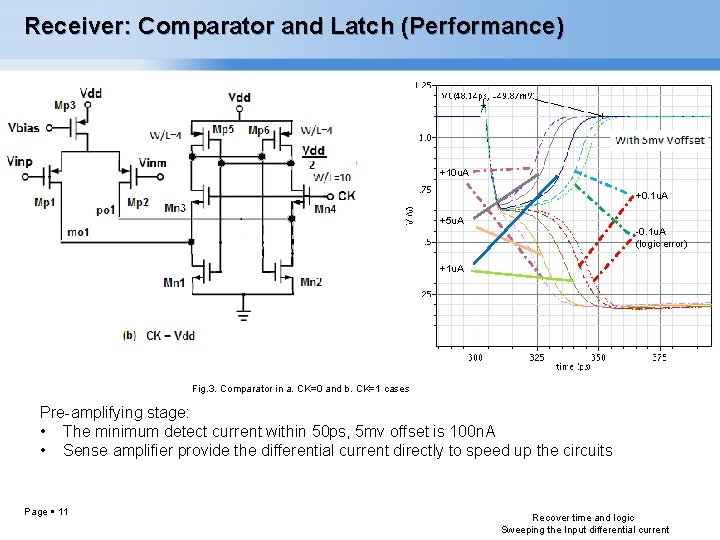

Receiver: Comparator and Latch (Performance) +10 u. A +0. 1 u. A +5 u. A -0. 1 u. A (logic error) +1 u. A Fig. 3. Comparator in a. CK=0 and b. CK=1 cases Pre-amplifying stage: • The minimum detect current within 50 ps, 5 mv offset is 100 n. A • Sense amplifier provide the differential current directly to speed up the circuits Page 11 Recover time and logic Sweeping the Input differential current

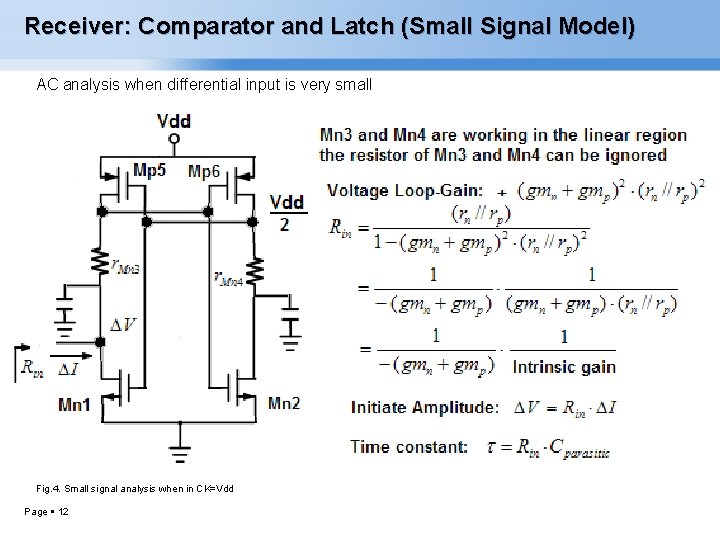

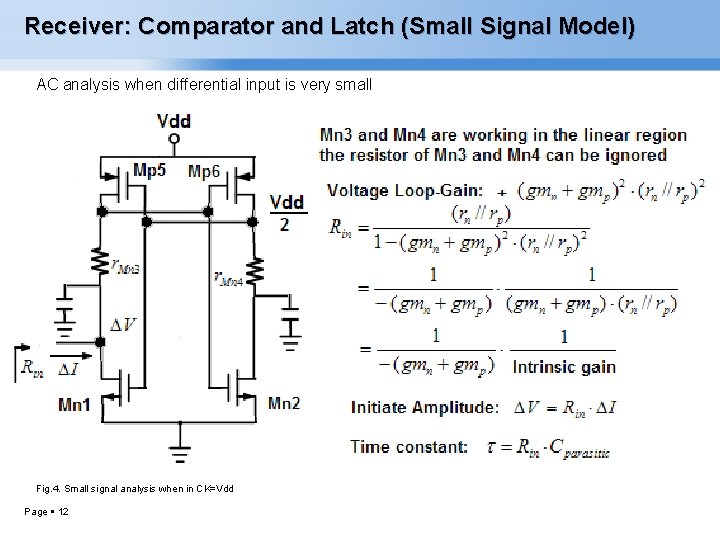

Receiver: Comparator and Latch (Small Signal Model) AC analysis when differential input is very small Fig. 4. Small signal analysis when in CK=Vdd Page 12

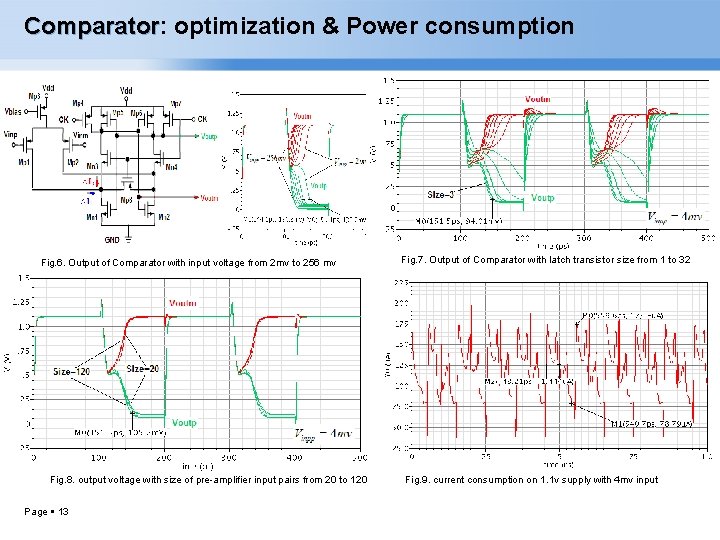

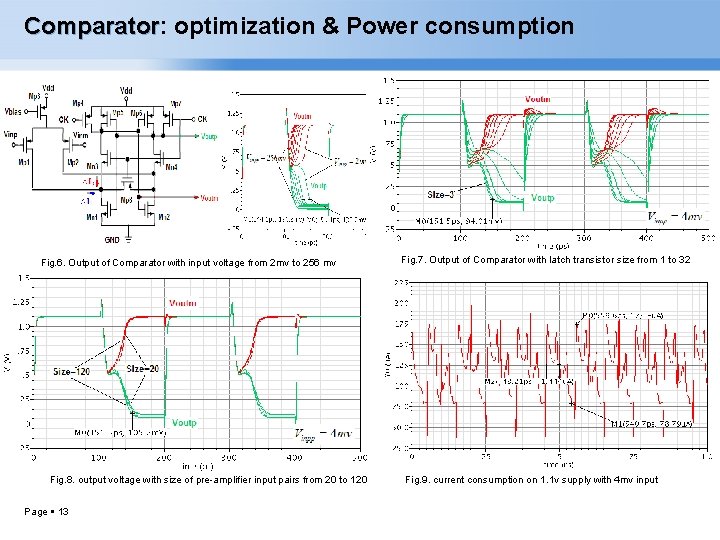

Comparator: Comparator optimization & Power consumption Fig. 6. Output of Comparator with input voltage from 2 mv to 256 mv Fig. 8. output voltage with size of pre-amplifier input pairs from 20 to 120 Page 13 Fig. 7. Output of Comparator with latch transistor size from 1 to 32 Fig. 9. current consumption on 1. 1 v supply with 4 mv input

• Ultra-Low Power On-Chip Differential Interconnects Using High-Resolution Comparator Transmission-line Page 14

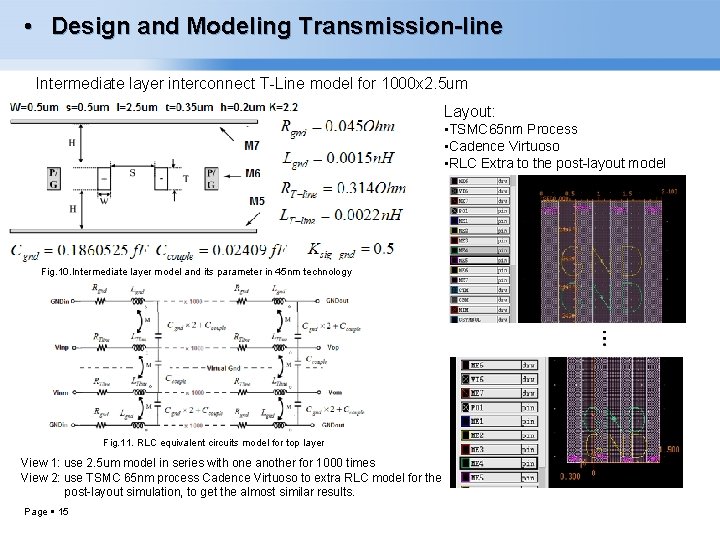

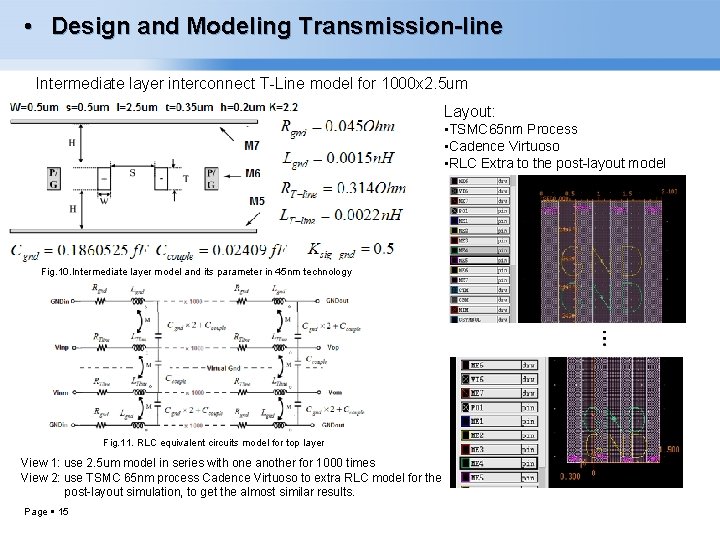

• Design and Modeling Transmission-line Intermediate layer interconnect T-Line model for 1000 x 2. 5 um Layout: • TSMC 65 nm Process • Cadence Virtuoso • RLC Extra to the post-layout model Fig. 10. Intermediate layer model and its parameter in 45 nm technology Fig. 11. RLC equivalent circuits model for top layer View 1: use 2. 5 um model in series with one another for 1000 times View 2: use TSMC 65 nm process Cadence Virtuoso to extra RLC model for the post-layout simulation, to get the almost similar results. Page 15

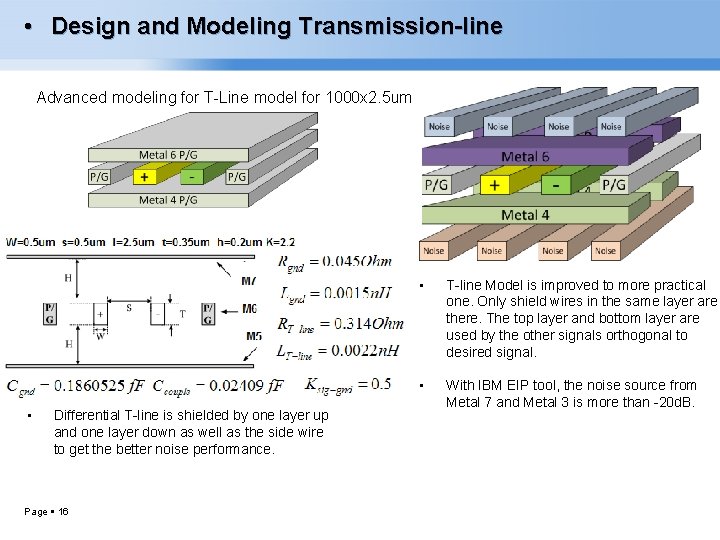

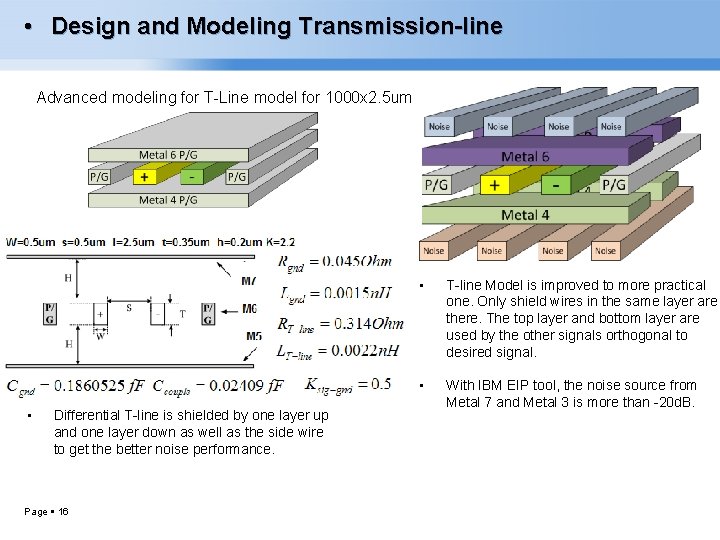

• Design and Modeling Transmission-line Advanced modeling for T-Line model for 1000 x 2. 5 um • Differential T-line is shielded by one layer up and one layer down as well as the side wire to get the better noise performance. Page 16 • T-line Model is improved to more practical one. Only shield wires in the same layer are there. The top layer and bottom layer are used by the other signals orthogonal to desired signal. • With IBM EIP tool, the noise source from Metal 7 and Metal 3 is more than -20 d. B.

• Ultra-Low Power On-Chip Differential Interconnects Using High-Resolution Comparator Driver: CTLE + LVDS Buffer Page 17

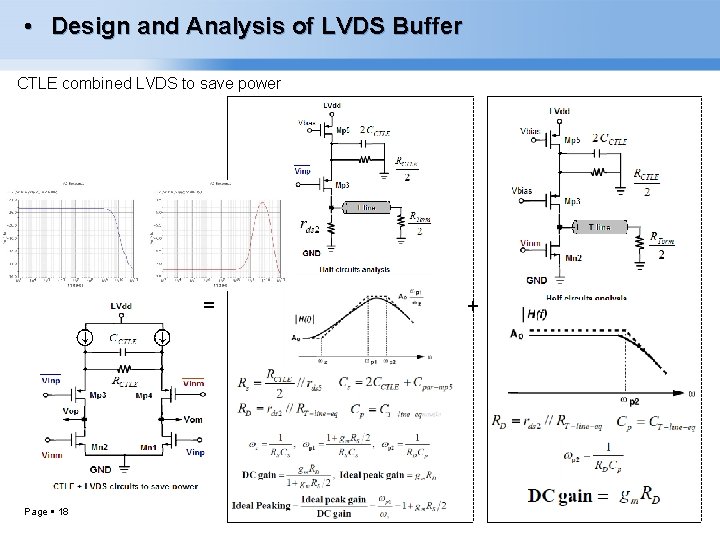

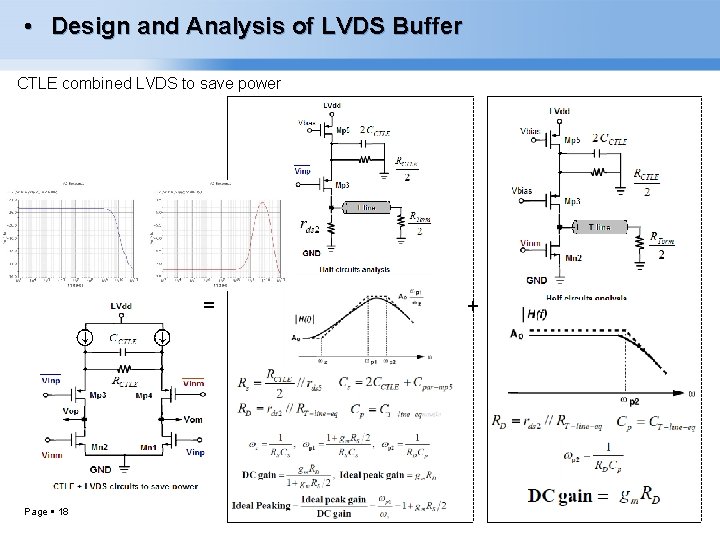

• Design and Analysis of LVDS Buffer CTLE combined LVDS to save power = Page 18 +

• Ultra-Low Power On-Chip Differential Interconnects Using High-Resolution Comparator Simulation Results & Conclusion Page 19

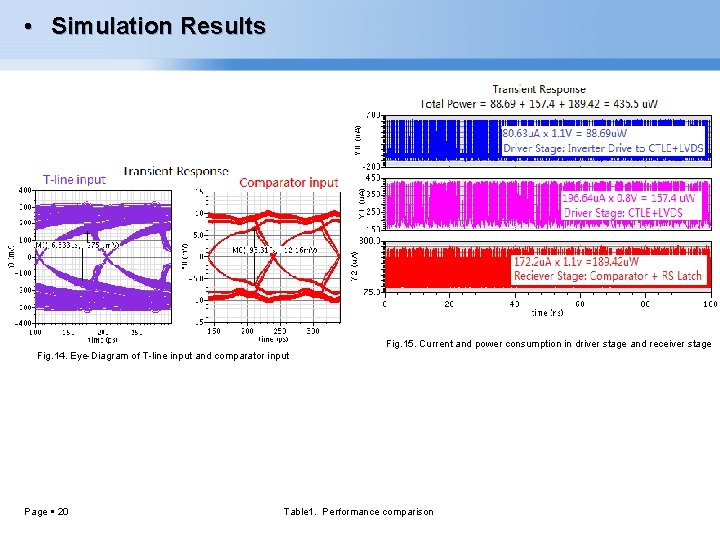

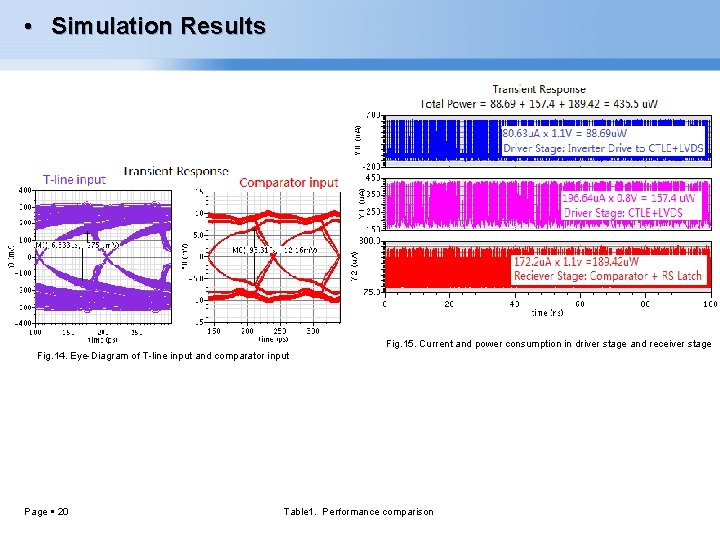

• Simulation Results Fig. 15. Current and power consumption in driver stage and receiver stage Fig. 14. Eye-Diagram of T-line input and comparator input Page 20 Table 1. Performance comparison

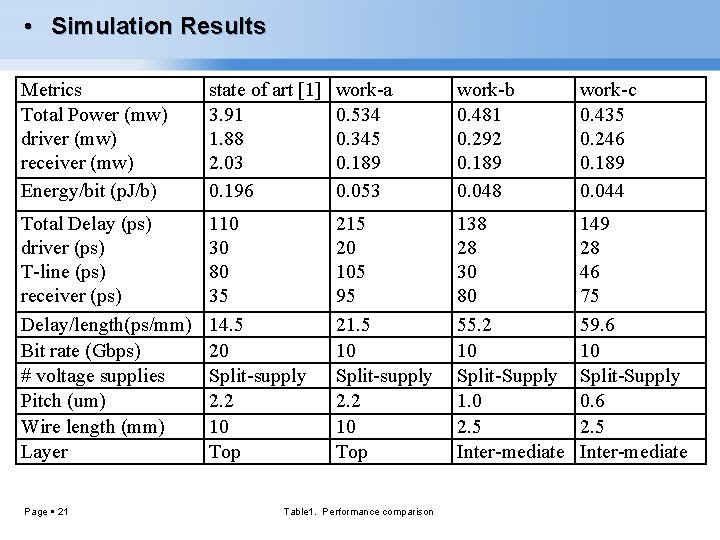

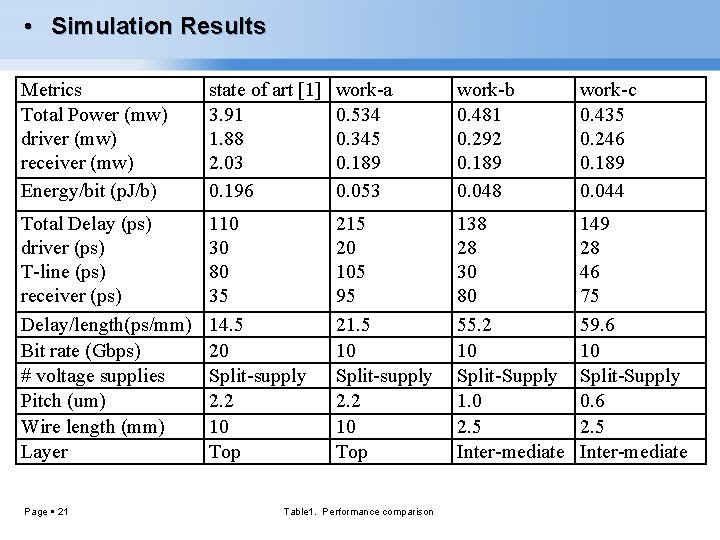

• Simulation Results Metrics Total Power (mw) driver (mw) receiver (mw) Energy/bit (p. J/b) state of art [1] 3. 91 1. 88 2. 03 0. 196 work-a 0. 534 0. 345 0. 189 0. 053 work-b 0. 481 0. 292 0. 189 0. 048 work-c 0. 435 0. 246 0. 189 0. 044 Total Delay (ps) driver (ps) T-line (ps) receiver (ps) Delay/length(ps/mm) Bit rate (Gbps) # voltage supplies Pitch (um) Wire length (mm) Layer 110 30 80 35 14. 5 20 Split-supply 2. 2 10 Top 215 20 105 95 21. 5 10 Split-supply 2. 2 10 Top 138 28 30 80 55. 2 10 Split-Supply 1. 0 2. 5 Inter-mediate 149 28 46 75 59. 6 10 Split-Supply 0. 6 2. 5 Inter-mediate Page 21 Table 1. Performance comparison

• Ultra-Low Power On-Chip Differential Interconnects Using High-Resolution Comparator Thank you ! Page 22