Abstract UltraLow Voltage Latches and FlipFlops Ultralow voltage

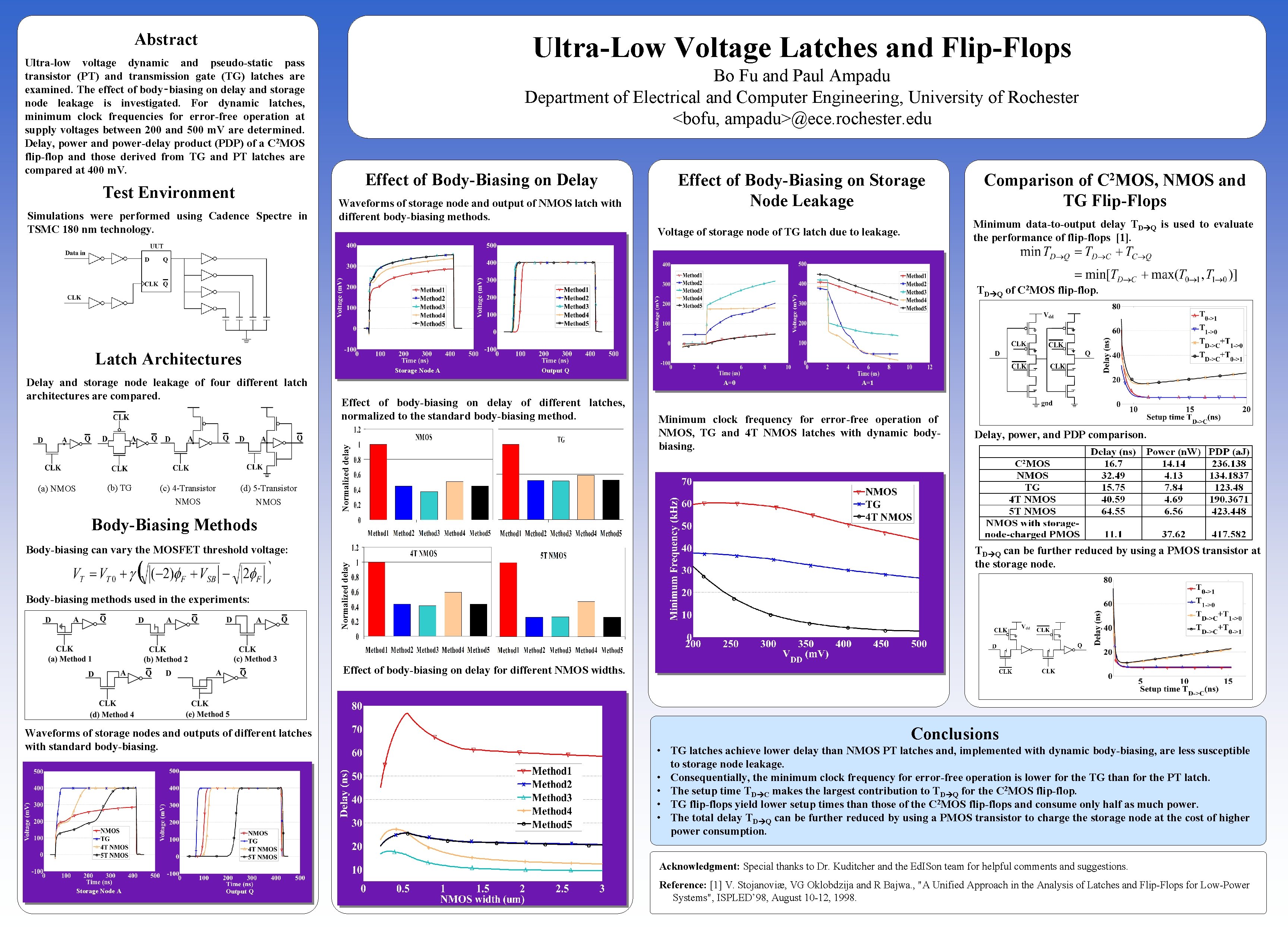

Abstract Ultra-Low Voltage Latches and Flip-Flops Ultra-low voltage dynamic and pseudo-static pass transistor (PT) and transmission gate (TG) latches are examined. The effect of body‑biasing on delay and storage node leakage is investigated. For dynamic latches, minimum clock frequencies for error-free operation at supply voltages between 200 and 500 m. V are determined. Delay, power and power-delay product (PDP) of a C 2 MOS flip-flop and those derived from TG and PT latches are compared at 400 m. V. Test Environment Simulations were performed using Cadence Spectre in TSMC 180 nm technology. Bo Fu and Paul Ampadu Department of Electrical and Computer Engineering, University of Rochester <bofu, ampadu>@ece. rochester. edu Effect of Body-Biasing on Delay Waveforms of storage node and output of NMOS latch with different body-biasing methods. Effect of Body-Biasing on Storage Node Leakage Comparison of C 2 MOS, NMOS and TG Flip-Flops Minimum data-to-output delay TD Q is used to evaluate the performance of flip-flops [1]. Voltage of storage node of TG latch due to leakage. TD Q of C 2 MOS flip-flop. Latch Architectures Storage Node A (a) NMOS (b) TG (c) 4 -Transistor (d) 5 -Transistor NMOS A=0 Effect of body-biasing on delay of different latches, normalized to the standard body-biasing method. Normalized delay Delay and storage node leakage of four different latch architectures are compared. Output Q A=1 Minimum clock frequency for error-free operation of NMOS, TG and 4 T NMOS latches with dynamic bodybiasing. Delay, power, and PDP comparison. Body-Biasing Methods Body-biasing methods used in the experiments: Normalized delay Body-biasing can vary the MOSFET threshold voltage: TD Q can be further reduced by using a PMOS transistor at the storage node. Effect of body-biasing on delay for different NMOS widths. Waveforms of storage nodes and outputs of different latches with standard body-biasing. Conclusions • TG latches achieve lower delay than NMOS PT latches and, implemented with dynamic body-biasing, are less susceptible to storage node leakage. • Consequentially, the minimum clock frequency for error-free operation is lower for the TG than for the PT latch. • The setup time TD C makes the largest contribution to TD Q for the C 2 MOS flip-flop. • TG flip-flops yield lower setup times than those of the C 2 MOS flip-flops and consume only half as much power. • The total delay TD Q can be further reduced by using a PMOS transistor to charge the storage node at the cost of higher power consumption. Acknowledgment: Special thanks to Dr. Kuditcher and the Ed. ISon team for helpful comments and suggestions. Storage Node A Output Q Reference: [1] V. Stojanoviæ, VG Oklobdzija and R Bajwa. , "A Unified Approach in the Analysis of Latches and Flip-Flops for Low-Power Systems", ISPLED’ 98, August 10 -12, 1998.

- Slides: 1