ADDER KOMPARATOR Sistem digital Oleh SHOFFIN NAHWA UTAMA

- Slides: 26

ADDER & KOMPARATOR Sistem digital Oleh : SHOFFIN NAHWA UTAMA, M. T

Adder �Komputer dan kalkulator melakukan operasi penjumlahan atas dua bilangan biner secara berturut-turut digit demi digit yang mana tiap-tiap bilangan biner dapat memiliki beberapa digit biner

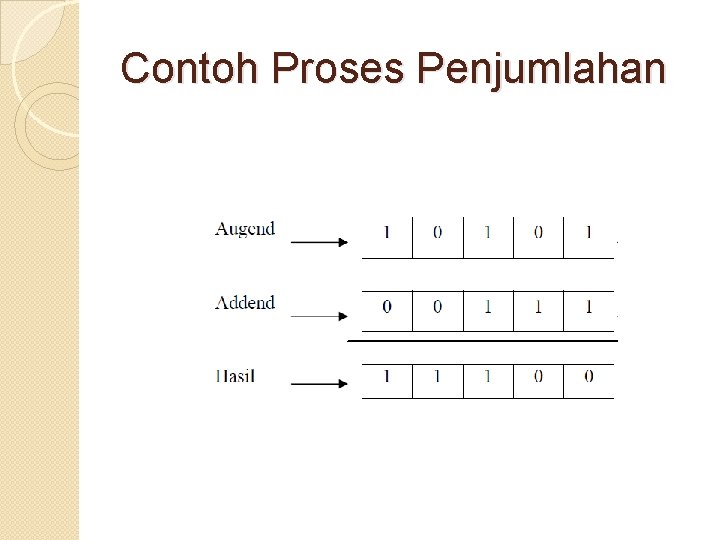

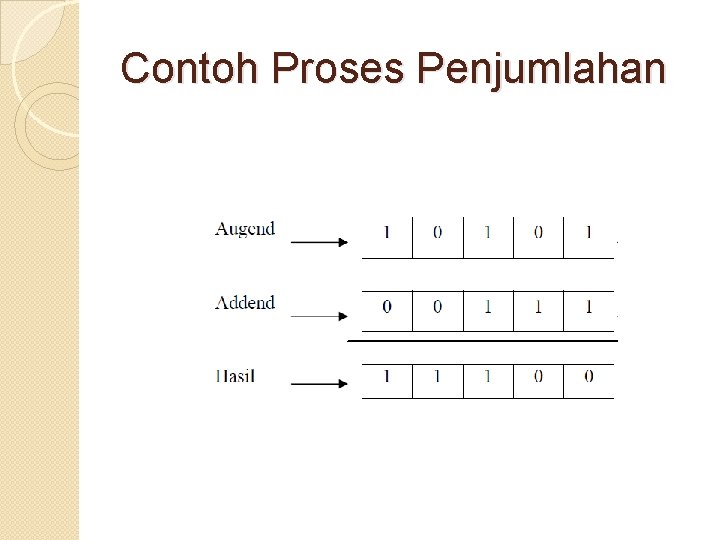

Proses Penjumlahan �Proses penjumlahan dimulai dengan menjumlahkan LSB dari augend (bilangan yang ditambah) dan addend (bilangan penambah). Jadi , 1 + 1 = 10 , yang berarti bahwa sum untuk posisi ini sama dengan 0 dengan carry 1. Carry ini harus ditambahkan pada posisi berikutnya, yaitu dijumlahkan menjadi satu dengan augend dan addend pada posisi tersebut.

�Jadi, pada posisi kedua, 1 + 0 + 1 = 10, sum nya sama dengan 0 dan carry 1. Carry ini ditambahkan pada posisi berikutnya bersama-sama dengan bitbit augend dan addend pada posisi itu, dan demikian seterusnya untuk posisi-posisi yang lainnya.

Contoh Proses Penjumlahan

Rangkaian Penjumlahan Biner �Pada rangkaian penjumlahan biner dibagi menjadi 2 1. Half Adder 2. Full Adder

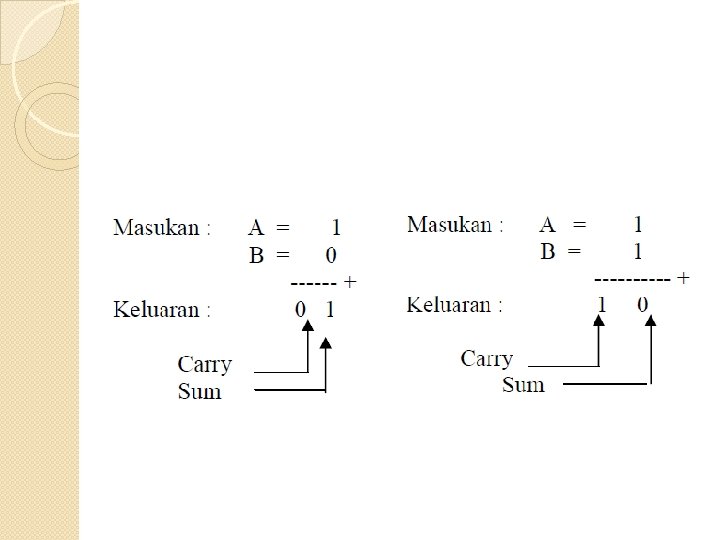

Half Adder �Half adder adalah suatu rangkaian penjumlah system bilangan biner yang paling sederhana. Rangkaian ini hanya dapat digunakan untuk operasi penjumlahan data bilangan biner sampai 1 bit saja.

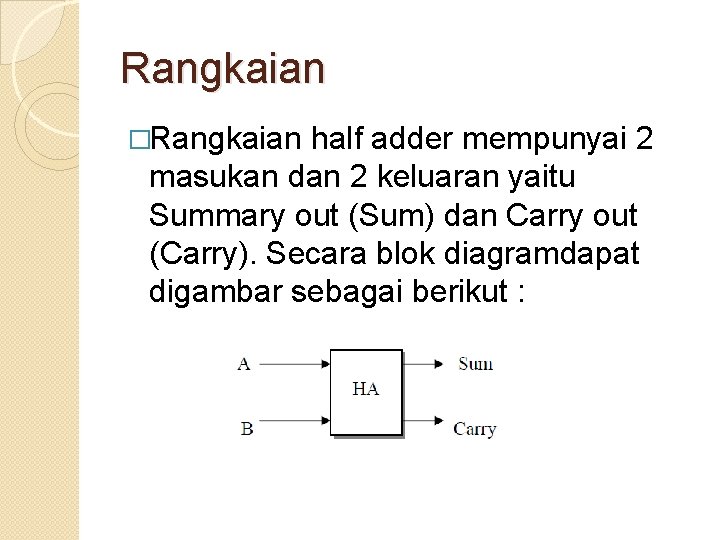

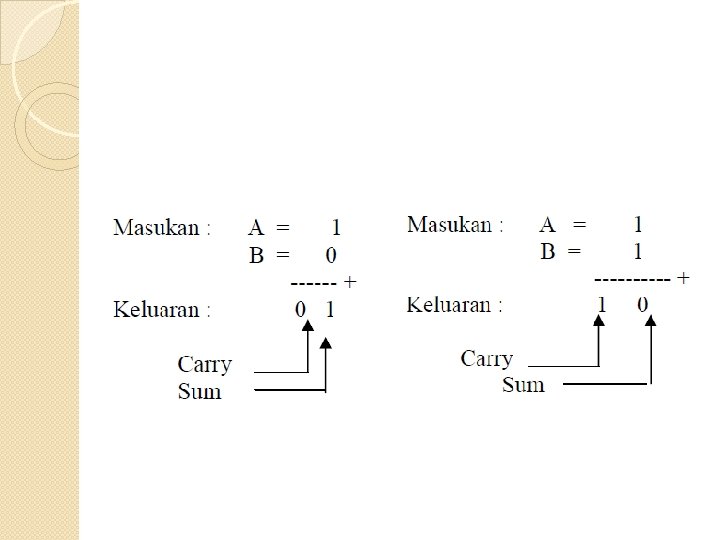

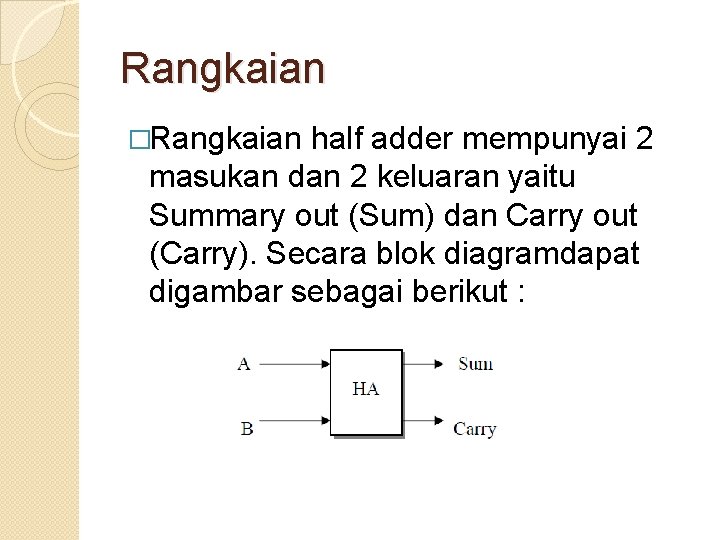

Rangkaian �Rangkaian half adder mempunyai 2 masukan dan 2 keluaran yaitu Summary out (Sum) dan Carry out (Carry). Secara blok diagramdapat digambar sebagai berikut :

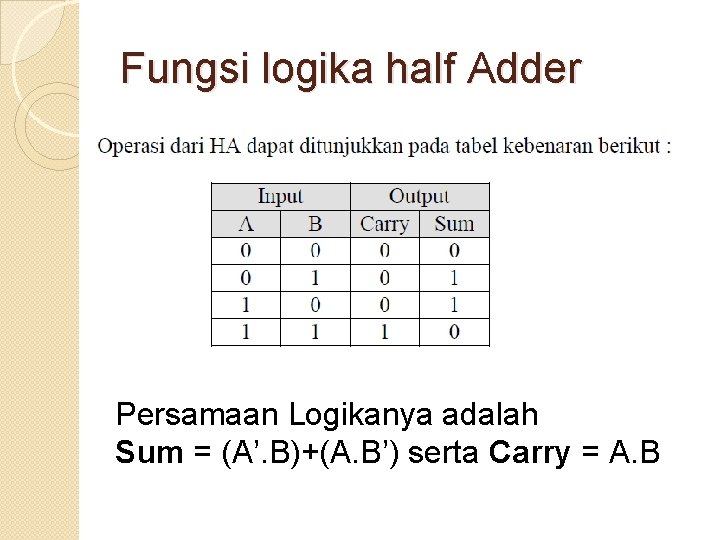

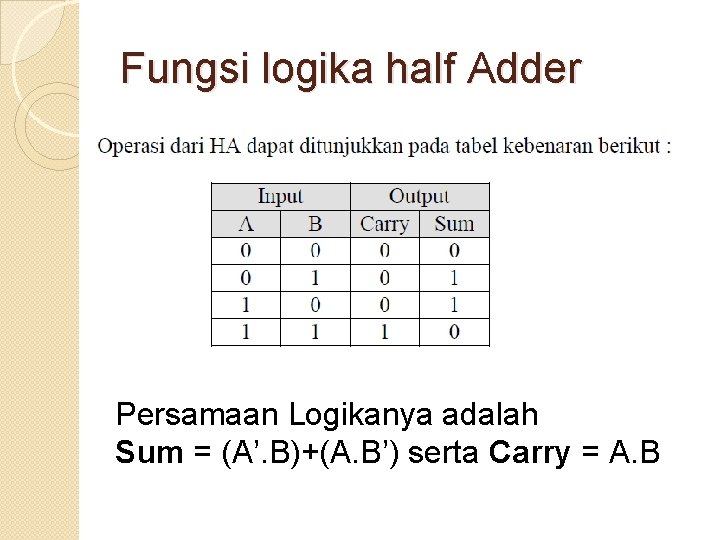

Fungsi logika half Adder Persamaan Logikanya adalah Sum = (A’. B)+(A. B’) serta Carry = A. B

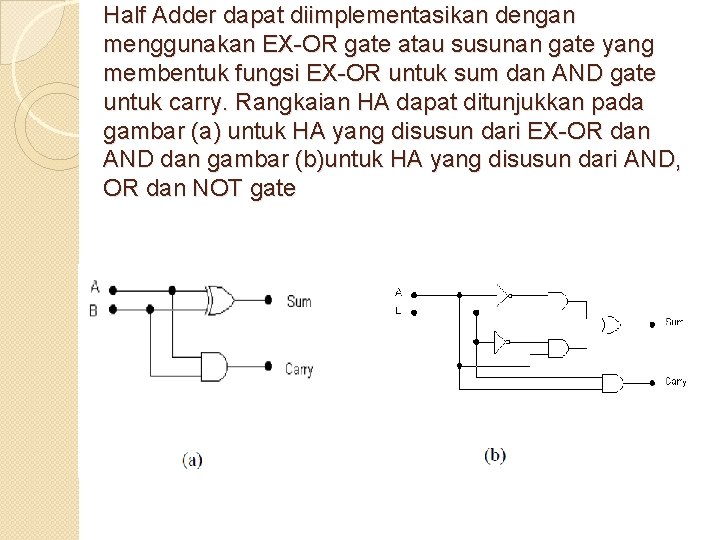

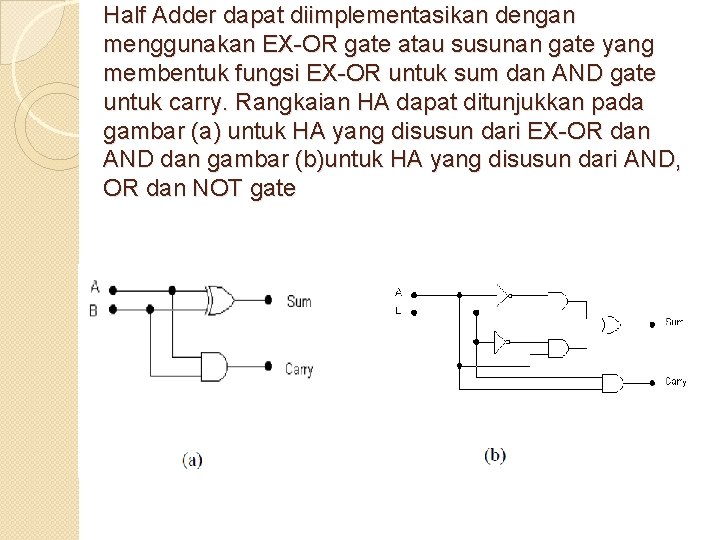

Half Adder dapat diimplementasikan dengan menggunakan EX-OR gate atau susunan gate yang membentuk fungsi EX-OR untuk sum dan AND gate untuk carry. Rangkaian HA dapat ditunjukkan pada gambar (a) untuk HA yang disusun dari EX-OR dan AND dan gambar (b)untuk HA yang disusun dari AND, OR dan NOT gate

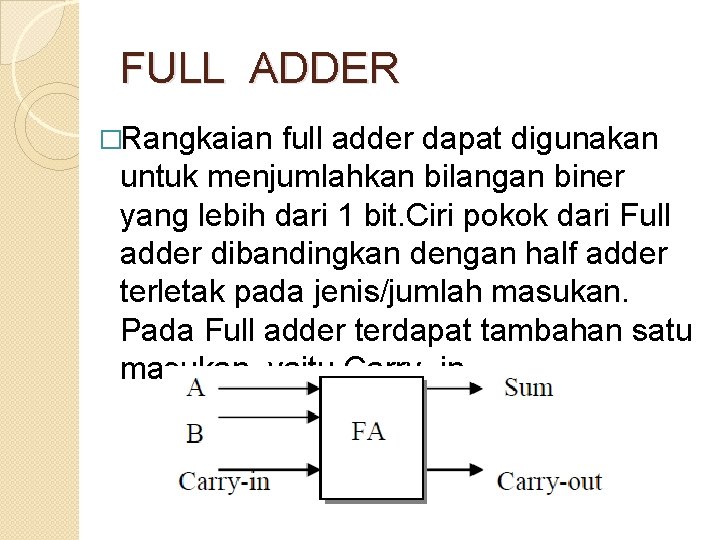

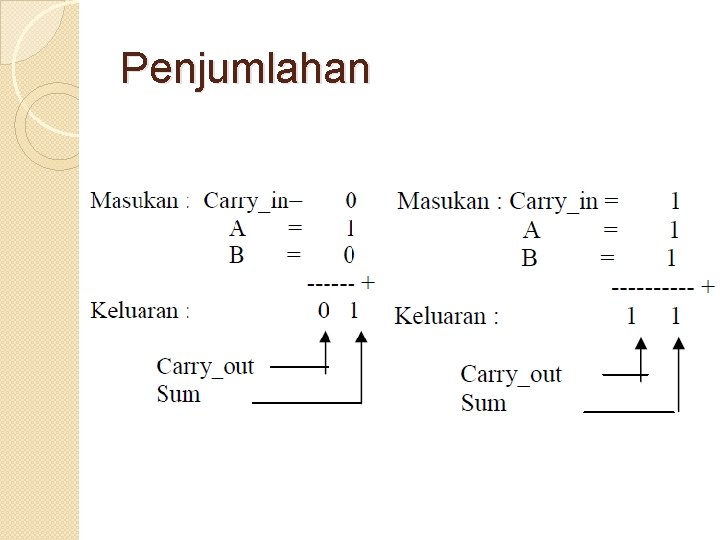

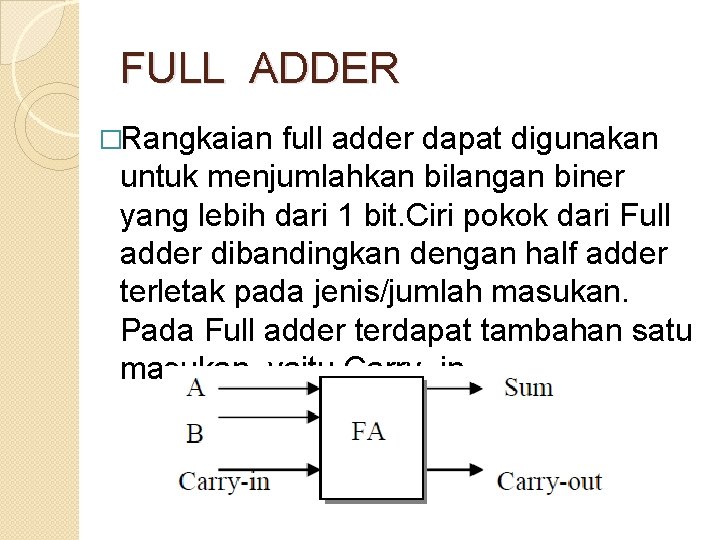

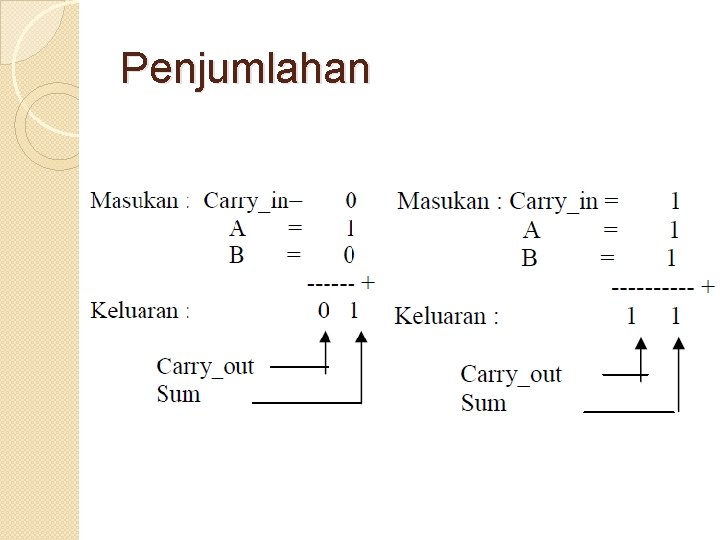

FULL ADDER �Rangkaian full adder dapat digunakan untuk menjumlahkan bilangan biner yang lebih dari 1 bit. Ciri pokok dari Full adder dibandingkan dengan half adder terletak pada jenis/jumlah masukan. Pada Full adder terdapat tambahan satu masukan, yaitu Carry_in.

Penjumlahan

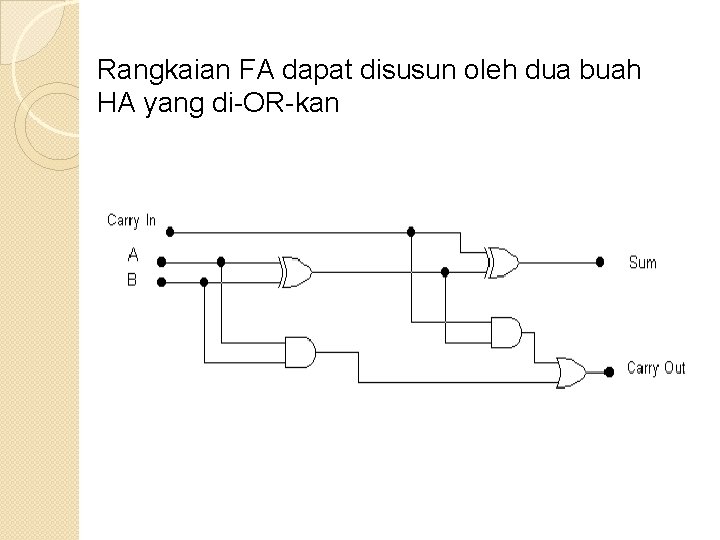

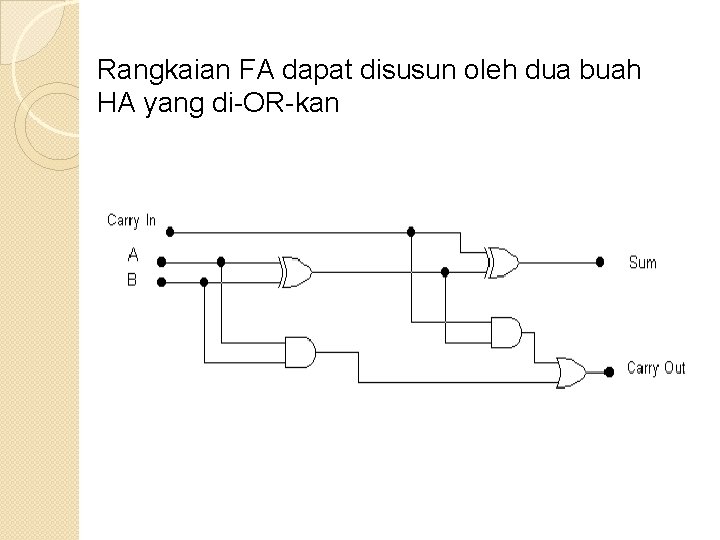

Rangkaian FA dapat disusun oleh dua buah HA yang di-OR-kan

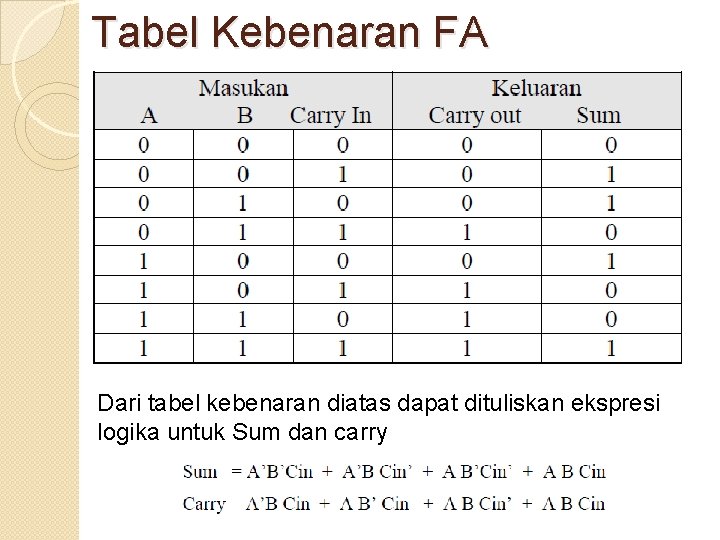

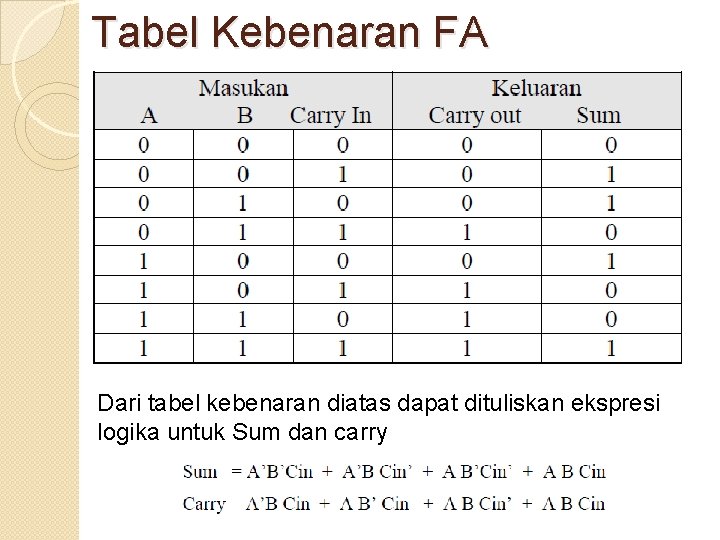

Tabel Kebenaran FA Dari tabel kebenaran diatas dapat dituliskan ekspresi logika untuk Sum dan carry

Next Mater i

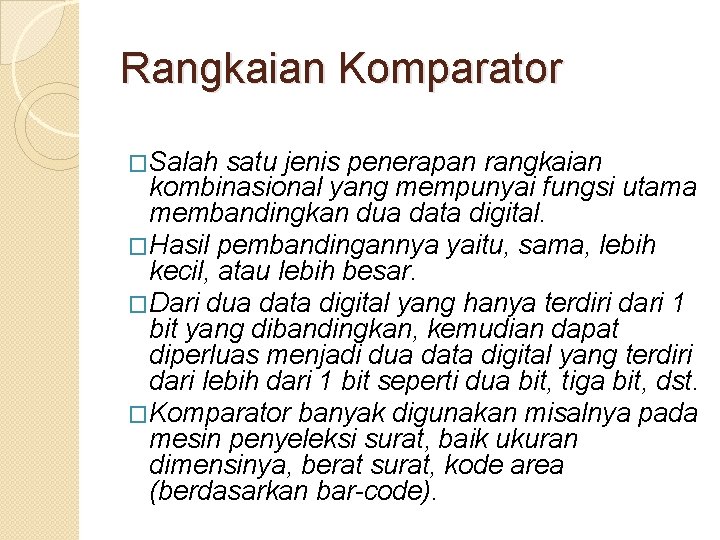

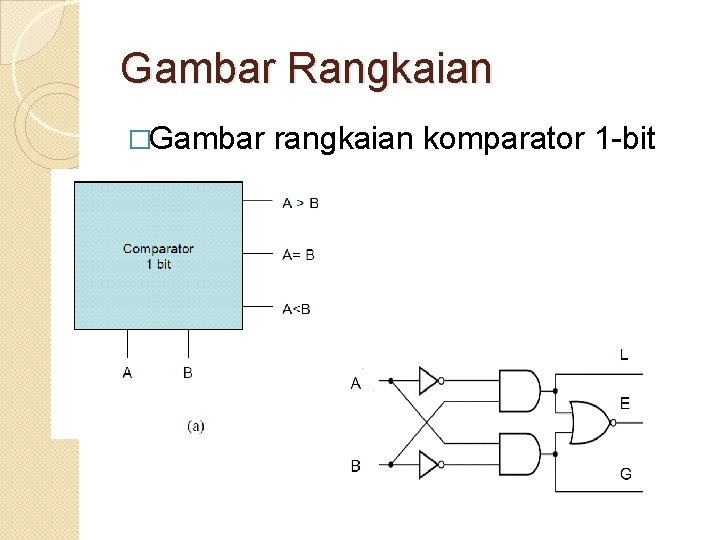

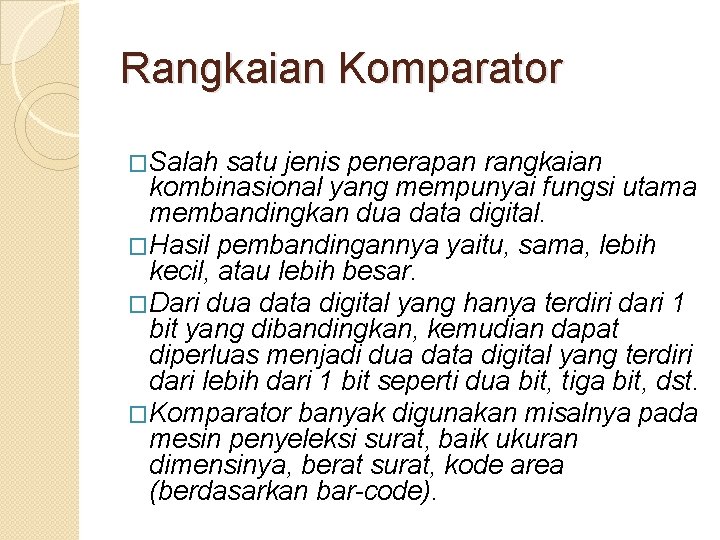

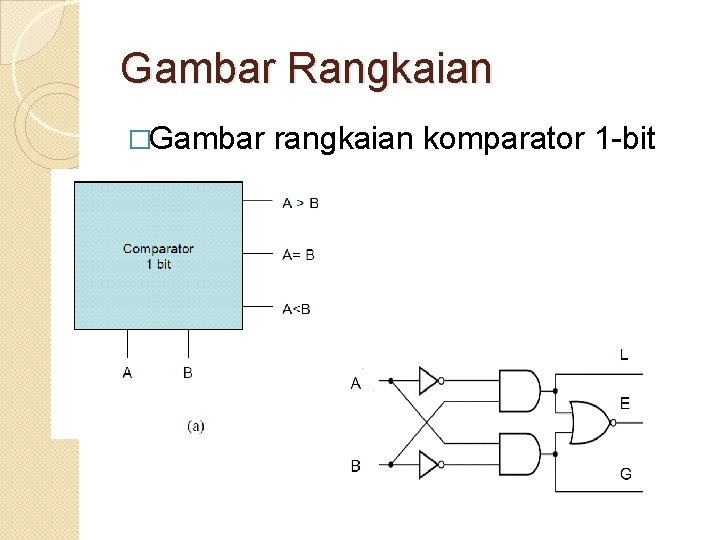

Rangkaian Komparator �Salah satu jenis penerapan rangkaian kombinasional yang mempunyai fungsi utama membandingkan dua data digital. �Hasil pembandingannya yaitu, sama, lebih kecil, atau lebih besar. �Dari dua data digital yang hanya terdiri dari 1 bit yang dibandingkan, kemudian dapat diperluas menjadi dua data digital yang terdiri dari lebih dari 1 bit seperti dua bit, tiga bit, dst. �Komparator banyak digunakan misalnya pada mesin penyeleksi surat, baik ukuran dimensinya, berat surat, kode area (berdasarkan bar-code).

Gambar Rangkaian �Gambar rangkaian komparator 1 -bit

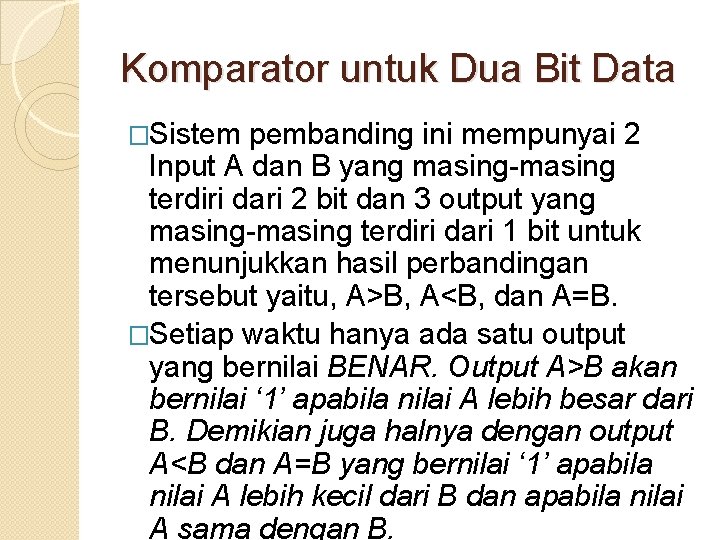

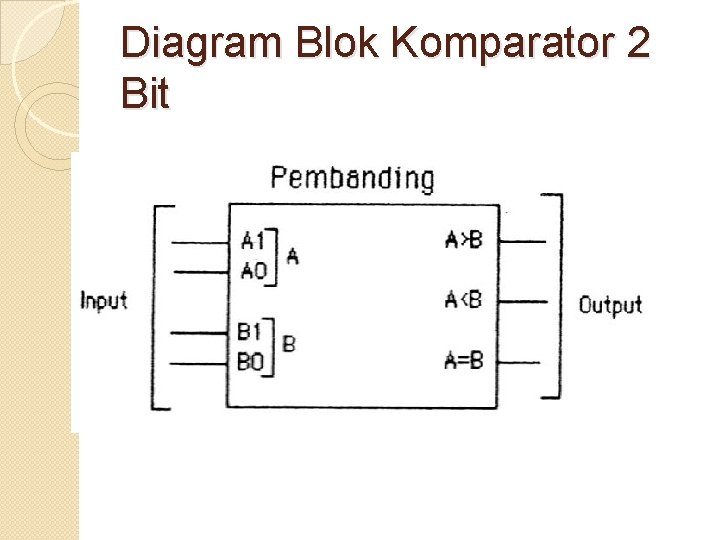

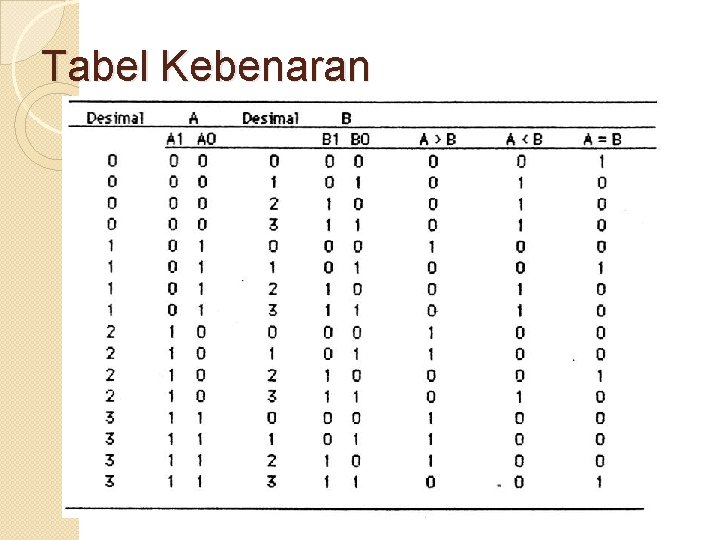

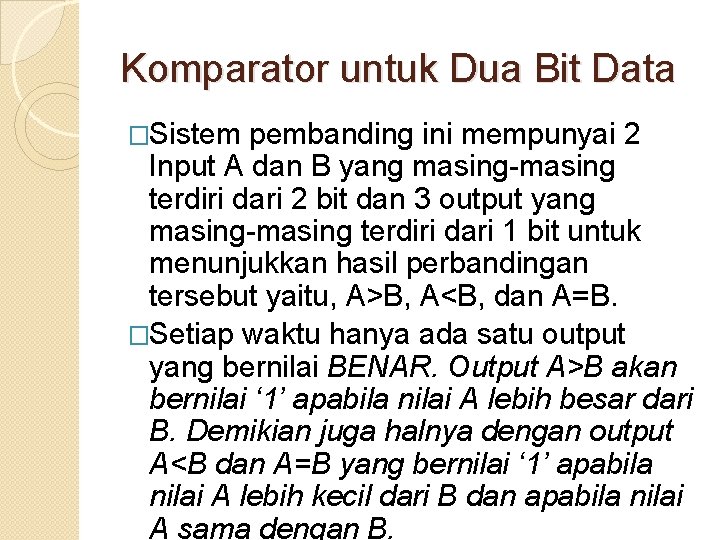

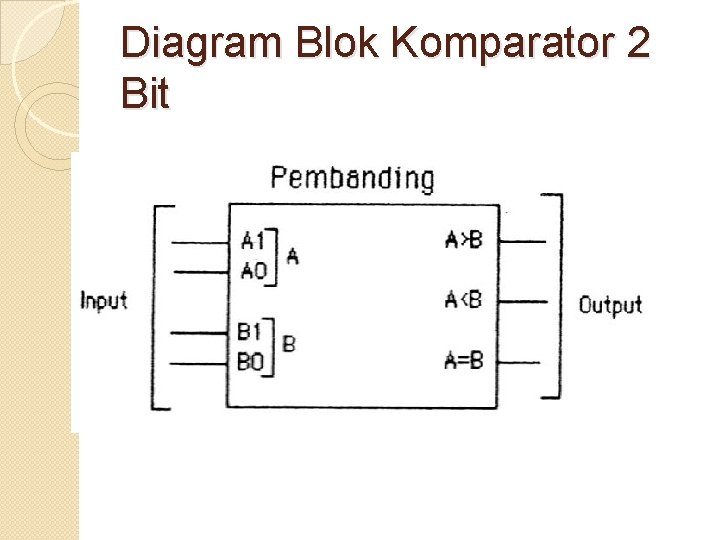

Komparator untuk Dua Bit Data �Sistem pembanding ini mempunyai 2 Input A dan B yang masing-masing terdiri dari 2 bit dan 3 output yang masing-masing terdiri dari 1 bit untuk menunjukkan hasil perbandingan tersebut yaitu, A>B, A<B, dan A=B. �Setiap waktu hanya ada satu output yang bernilai BENAR. Output A>B akan bernilai ‘ 1’ apabila nilai A lebih besar dari B. Demikian juga halnya dengan output A<B dan A=B yang bernilai ‘ 1’ apabila nilai A lebih kecil dari B dan apabila nilai A sama dengan B.

Diagram Blok Komparator 2 Bit

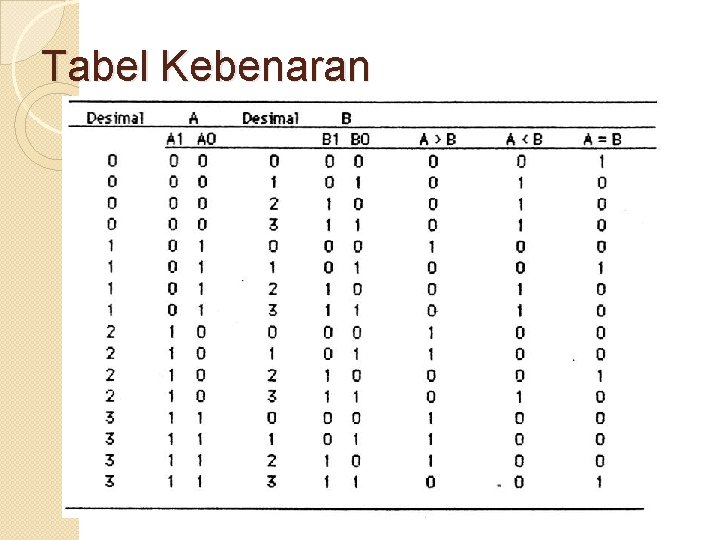

Tabel Kebenaran

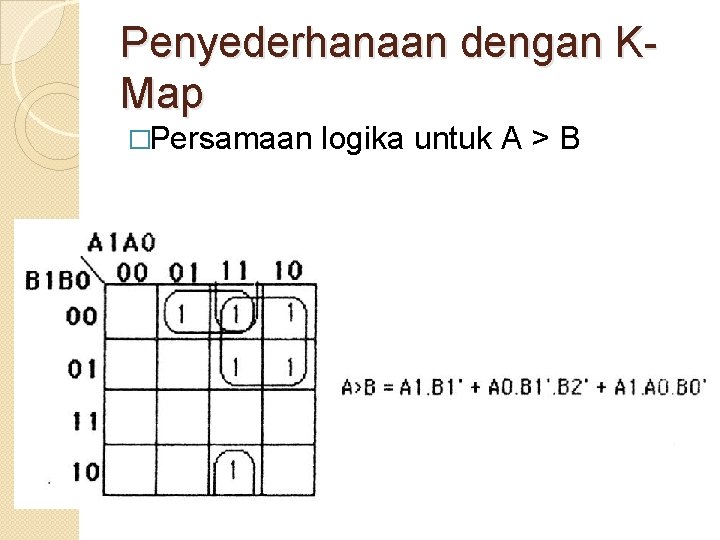

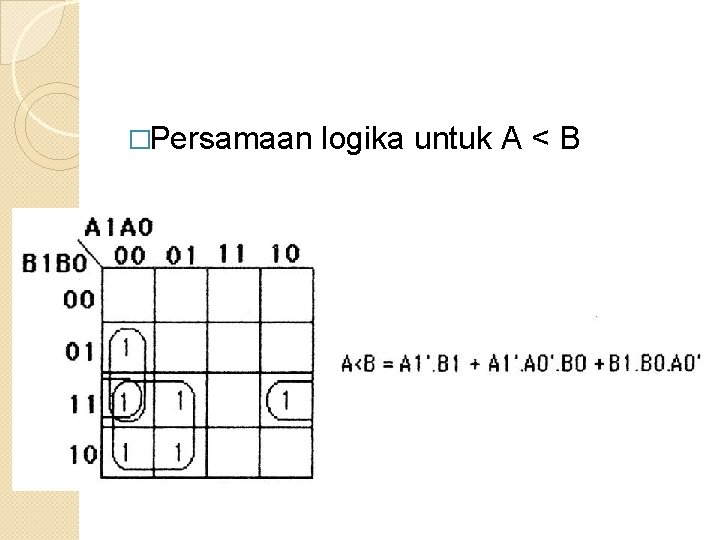

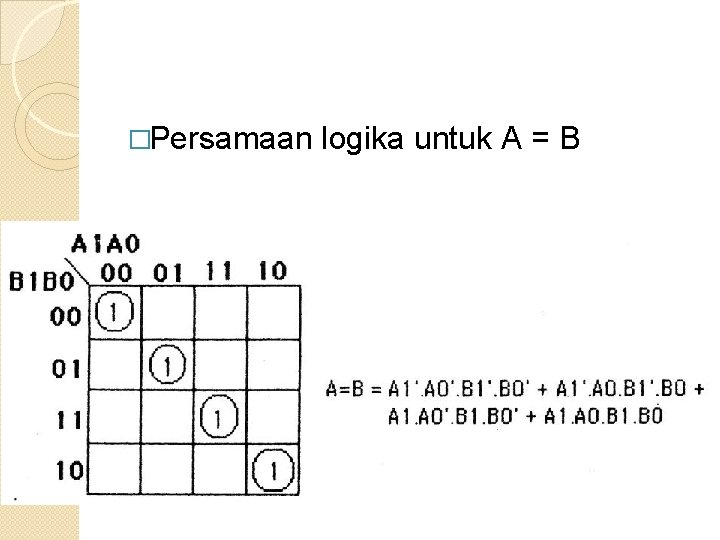

Persamaan �Sistem ini akan mempunyai 3 persamaan logika karena adanya 3 output. �Perlu adanya penyederhanaan dan persamaan logika yang di peroleh untuk output-output A > B, A < B, dan A = B.

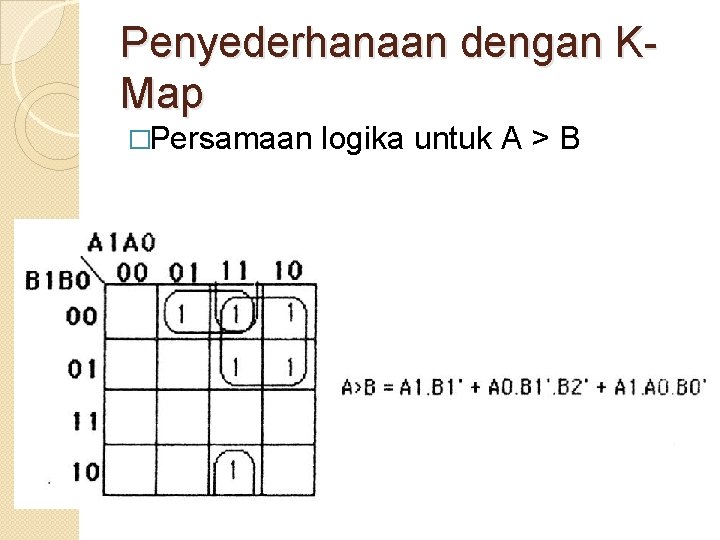

Penyederhanaan dengan KMap �Persamaan logika untuk A > B

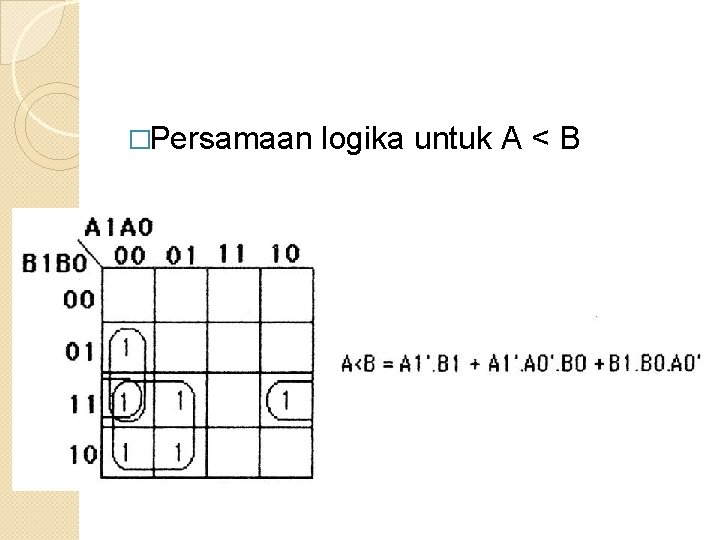

�Persamaan logika untuk A < B

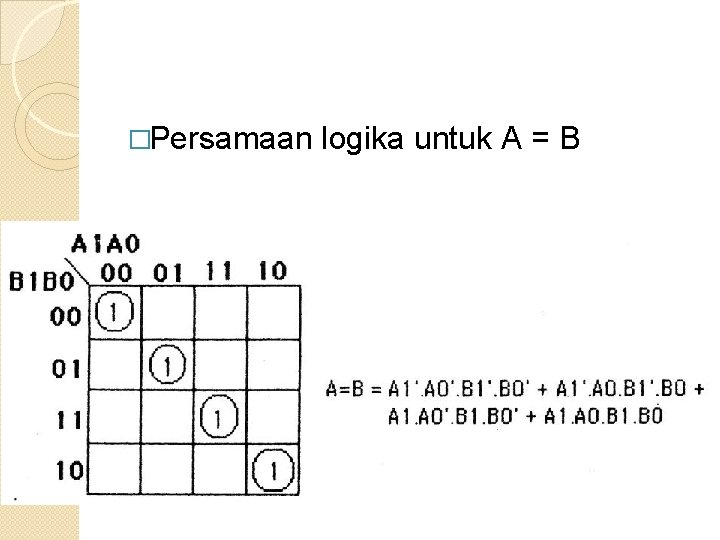

�Persamaan logika untuk A = B

Sekian & Terimakasih