State Machine Design Digital Electronics State Machine Design

- Slides: 15

State Machine Design Digital Electronics

State Machine Design This presentation will • Give the definition of a state machine. • Provide several examples of everyday items that are controlled by state machines. • Show the block diagram for a state machine • Review the design steps in the state machine design process. • Give an example of a simple state machine design. 2

Definition of a State Machine : A synchronous sequential circuit, consisting of a sequential logic section and a combinational logic section, whose outputs and internal flip-flops progress through a predictable sequence of states in responde to a clock and other input signals. 3

Examples of State Machine There are numerous examples of everyday devices that are controlled by a state machine: Traffic Light Garage Door Numeric Keypad Vending Machine 4

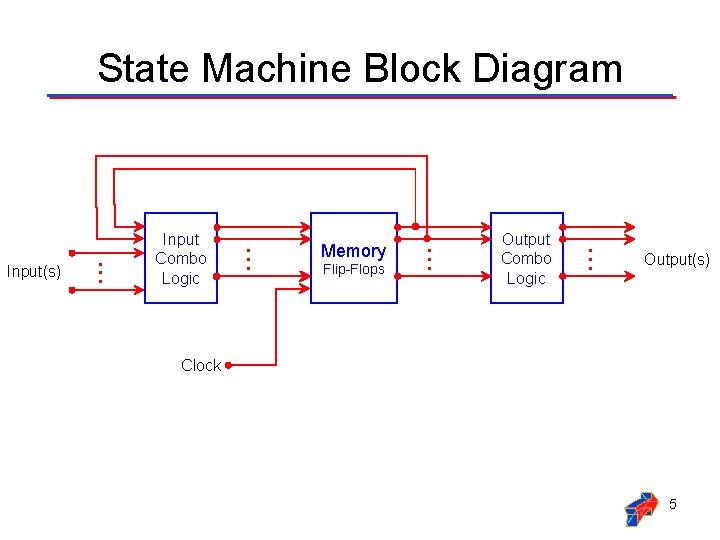

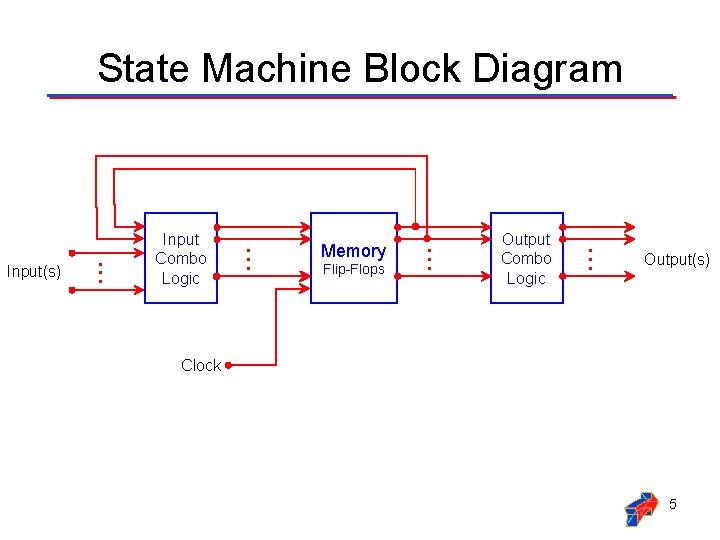

State Machine Block Diagram Flip-Flops Output Combo Logic . . . Memory . . Input(s) Input Combo Logic Output(s) Clock 5

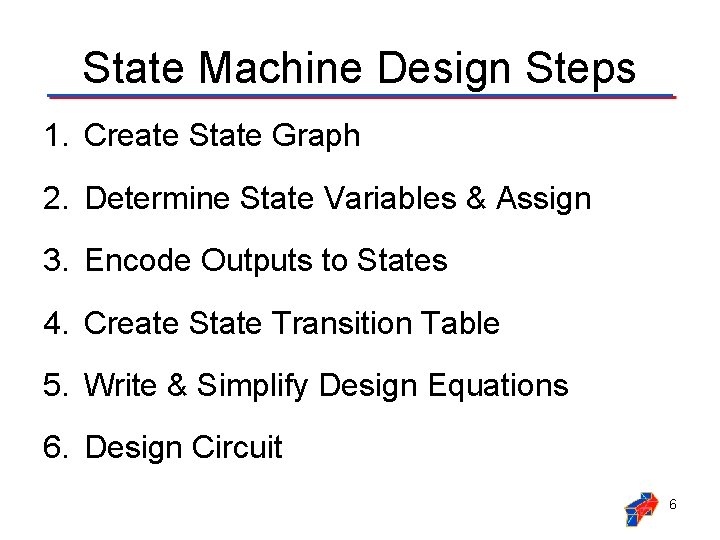

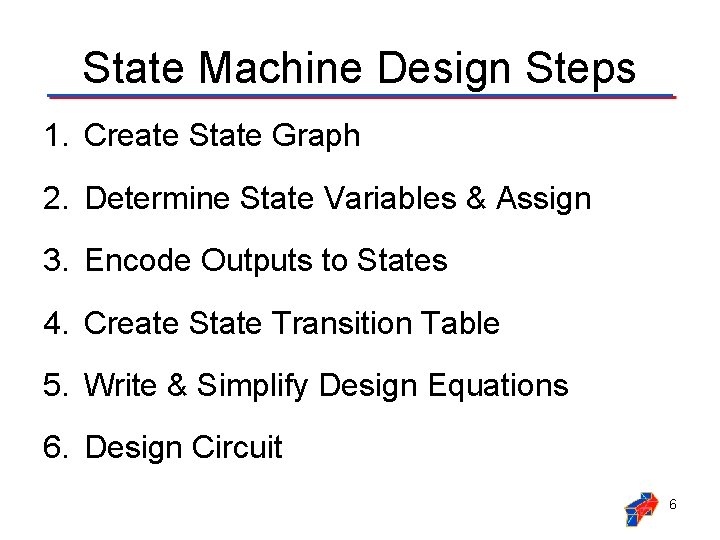

State Machine Design Steps 1. Create State Graph 2. Determine State Variables & Assign 3. Encode Outputs to States 4. Create State Transition Table 5. Write & Simplify Design Equations 6. Design Circuit 6

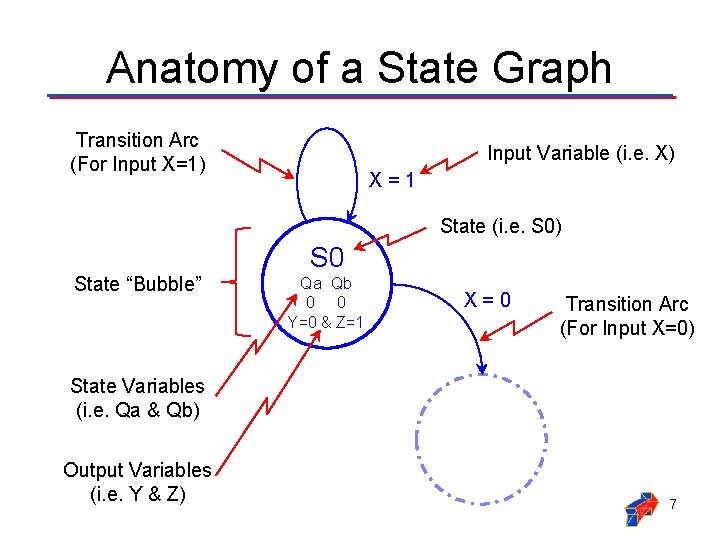

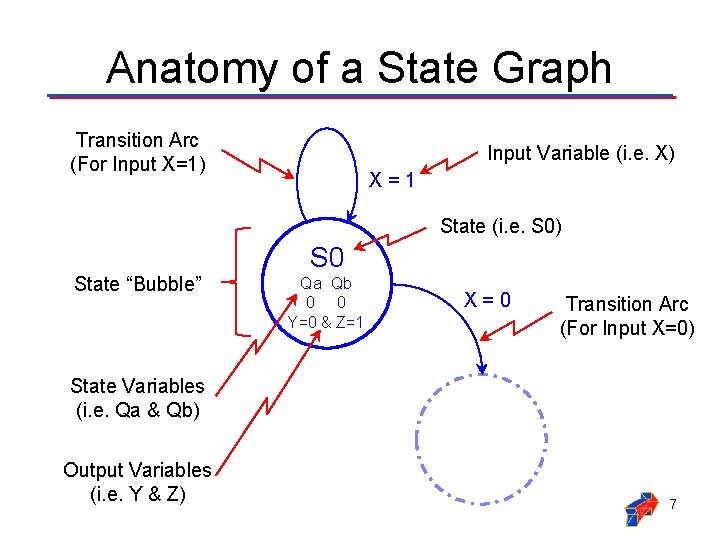

Anatomy of a State Graph Transition Arc (For Input X=1) Input Variable (i. e. X) X=1 State (i. e. S 0) State “Bubble” S 0 Qa Qb 0 0 Y=0 & Z=1 X=0 Transition Arc (For Input X=0) State Variables (i. e. Qa & Qb) Output Variables (i. e. Y & Z) 7

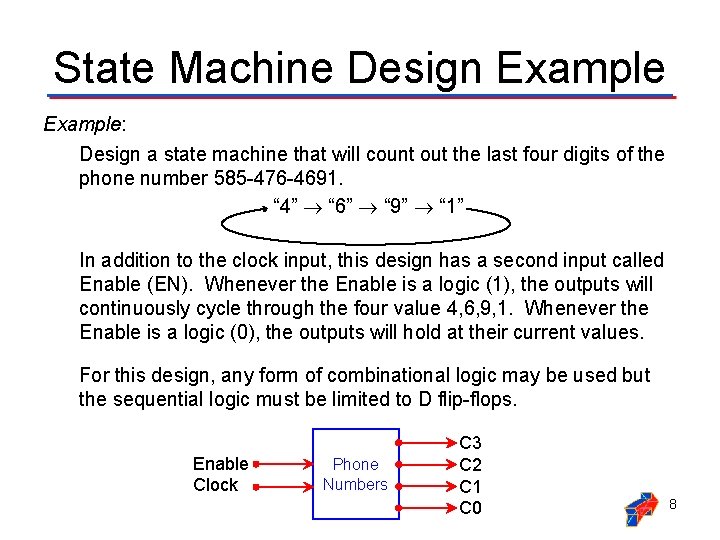

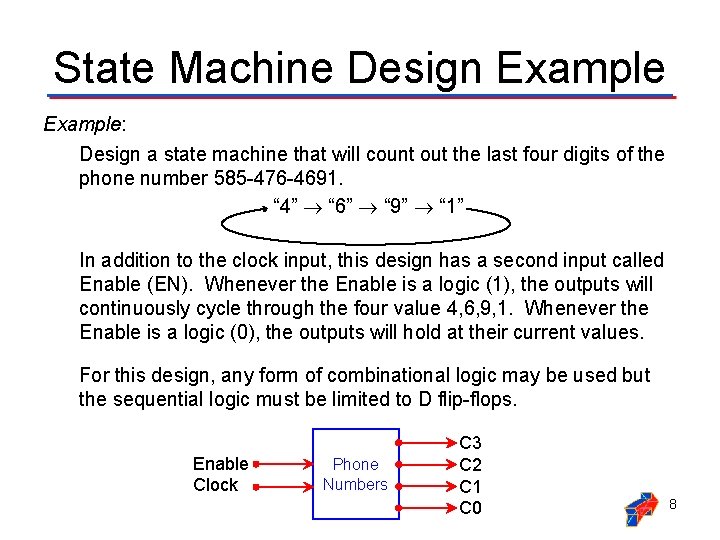

State Machine Design Example: Design a state machine that will count out the last four digits of the phone number 585 -476 -4691. “ 4” “ 6” “ 9” “ 1” In addition to the clock input, this design has a second input called Enable (EN). Whenever the Enable is a logic (1), the outputs will continuously cycle through the four value 4, 6, 9, 1. Whenever the Enable is a logic (0), the outputs will hold at their current values. For this design, any form of combinational logic may be used but the sequential logic must be limited to D flip-flops. Enable Clock Phone Numbers C 3 C 2 C 1 C 0 8

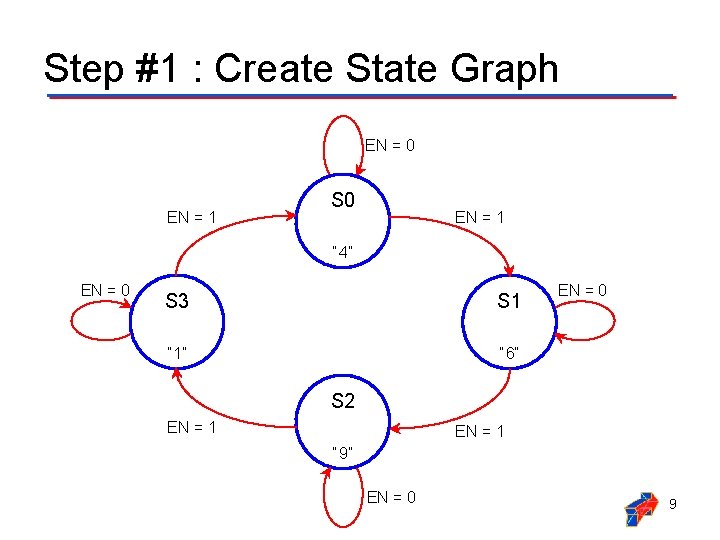

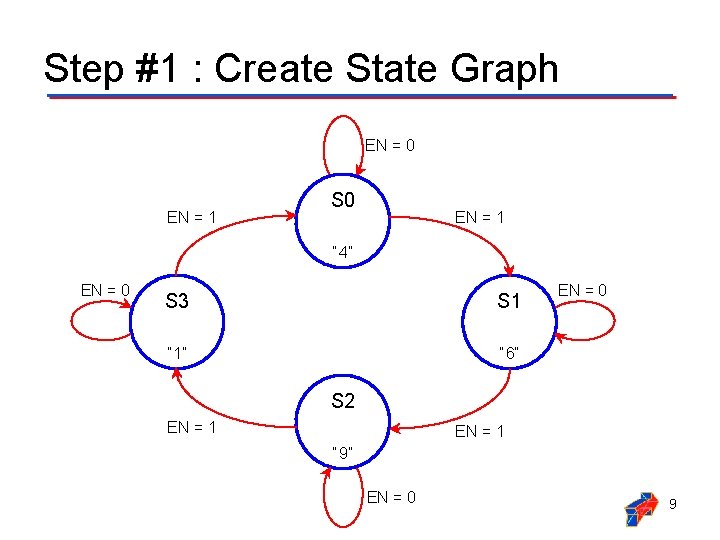

Step #1 : Create State Graph EN = 0 EN = 1 S 0 EN = 1 “ 4” EN = 0 S 3 S 1 “ 1” “ 6” EN = 0 S 2 EN = 1 “ 9” EN = 0 9

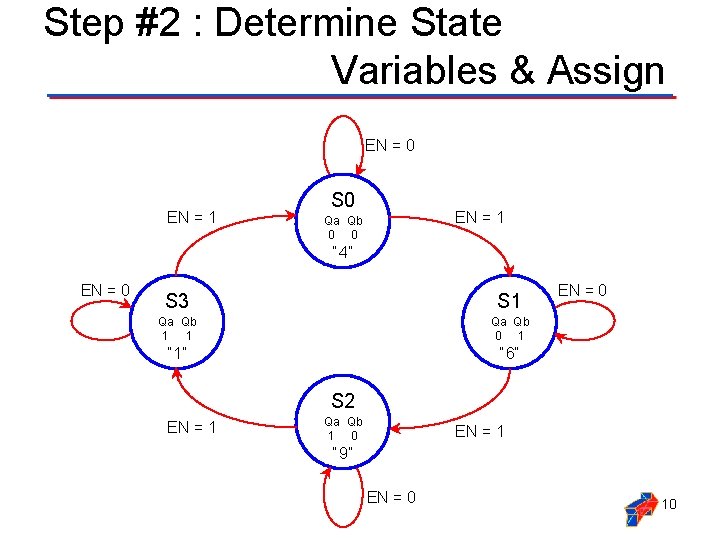

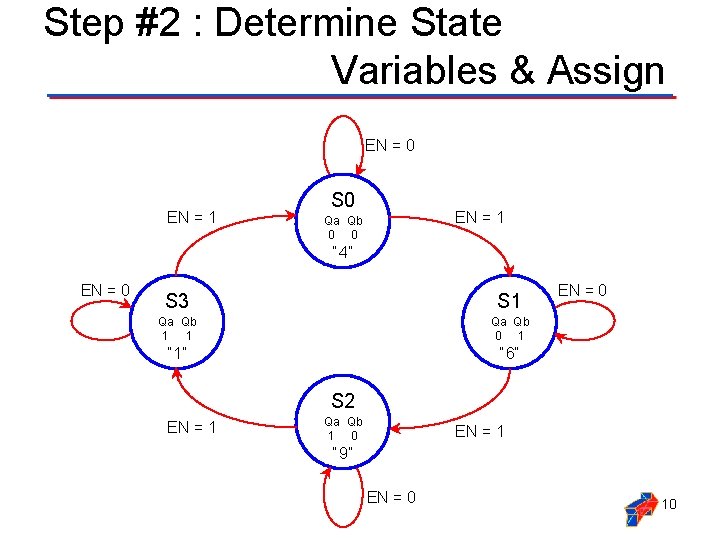

Step #2 : Determine State Variables & Assign EN = 0 EN = 1 S 0 EN = 1 Qa Qb 0 0 “ 4” EN = 0 S 3 S 1 Qa Qb 1 1 Qa Qb 0 1 “ 1” “ 6” EN = 0 S 2 EN = 1 Qa Qb 1 0 EN = 1 “ 9” EN = 0 10

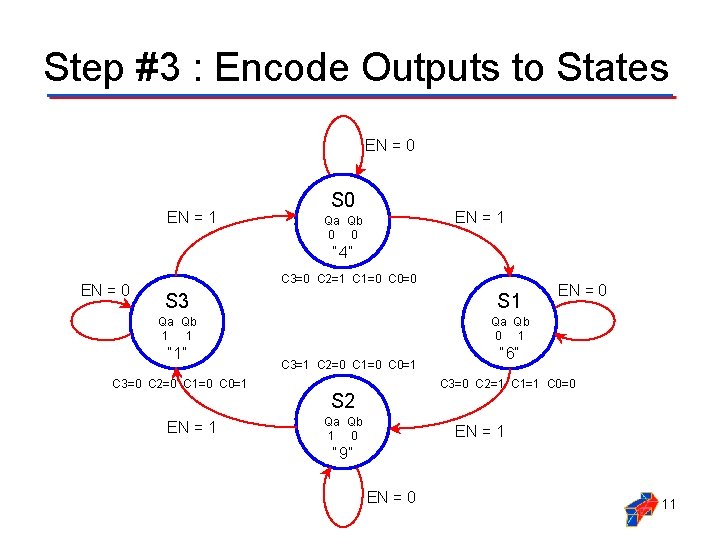

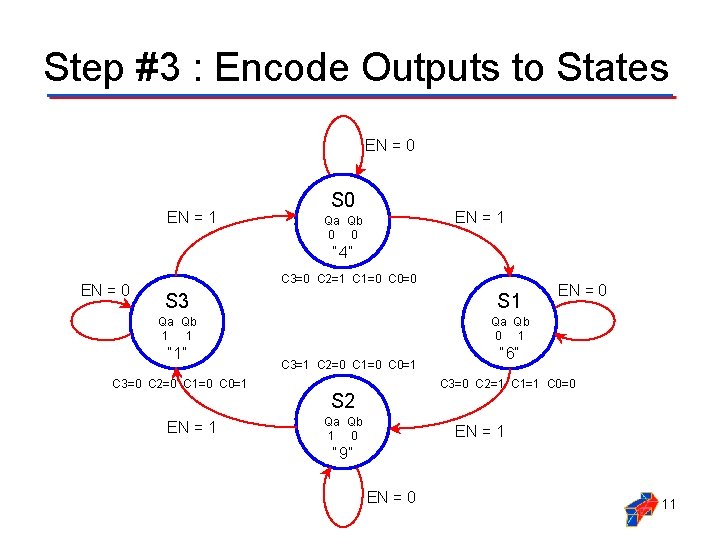

Step #3 : Encode Outputs to States EN = 0 EN = 1 S 0 EN = 1 Qa Qb 0 0 “ 4” EN = 0 C 3=0 C 2=1 C 1=0 C 0=0 S 3 S 1 Qa Qb 1 1 Qa Qb 0 1 “ 1” C 3=0 C 2=0 C 1=0 C 0=1 EN = 1 C 3=1 C 2=0 C 1=0 C 0=1 EN = 0 “ 6” C 3=0 C 2=1 C 1=1 C 0=0 S 2 Qa Qb 1 0 EN = 1 “ 9” EN = 0 11

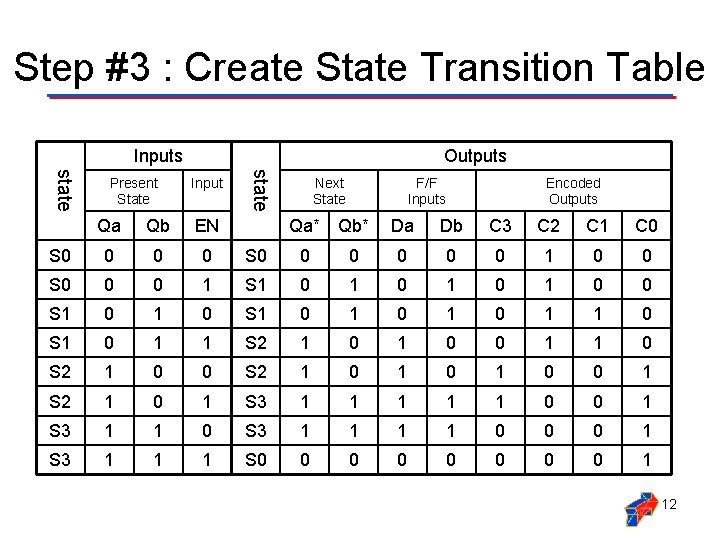

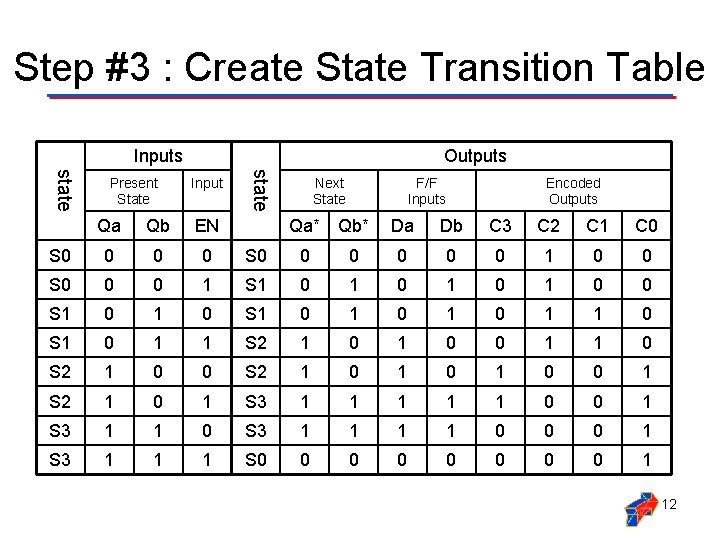

Step #3 : Create State Transition Table Inputs Input state Present State Outputs Next State Qa Qb EN S 0 0 0 1 S 1 0 1 S 2 F/F Inputs Qa* Qb* Encoded Outputs Da Db C 3 C 2 C 1 C 0 0 0 1 0 1 0 0 S 1 0 1 0 1 S 2 1 0 0 1 1 0 0 0 S 2 1 0 1 0 0 1 1 0 1 S 3 1 1 1 0 0 1 S 3 1 1 0 0 0 1 S 3 1 1 1 S 0 0 0 0 1 12

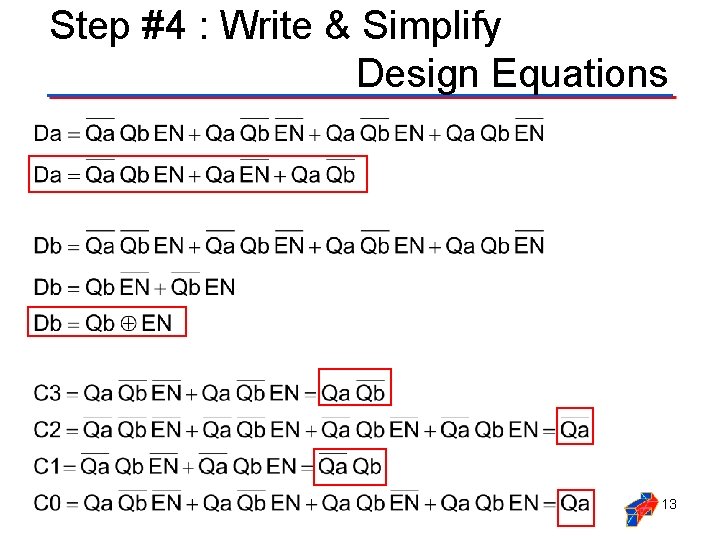

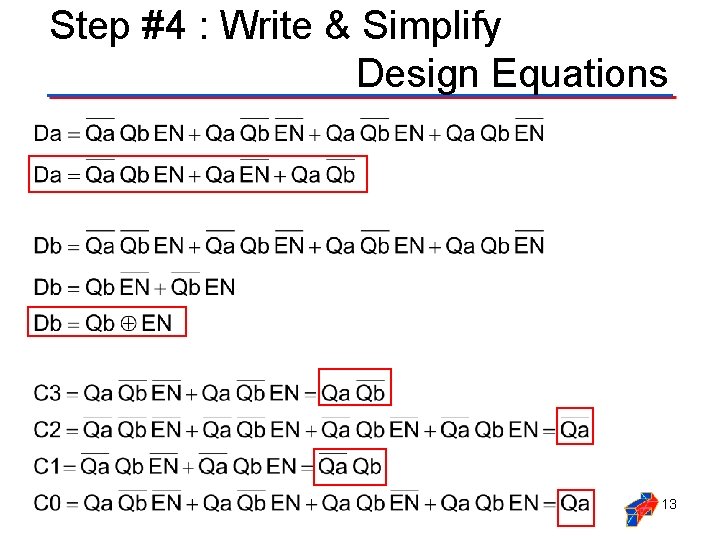

Step #4 : Write & Simplify Design Equations 13

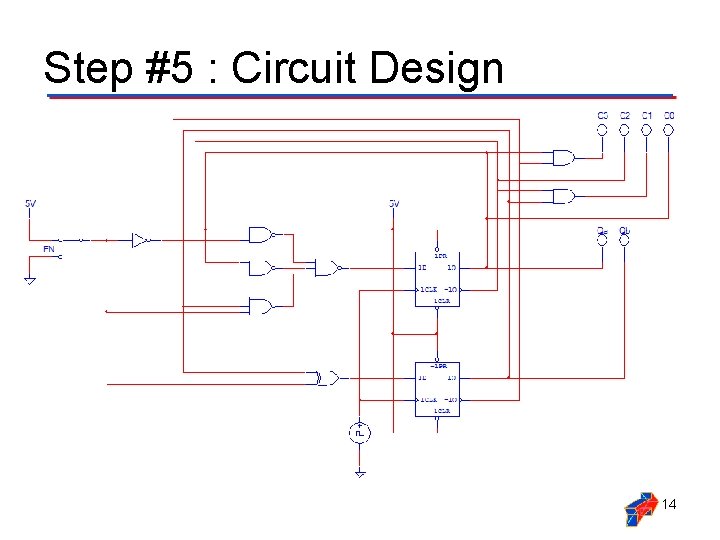

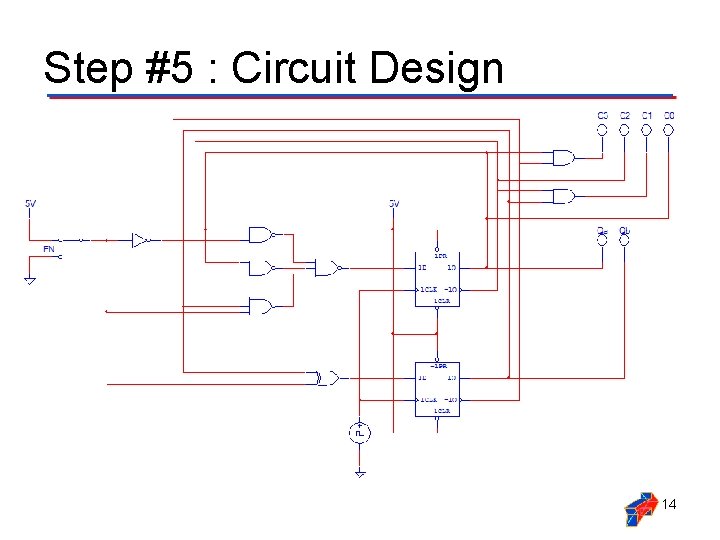

Step #5 : Circuit Design 14

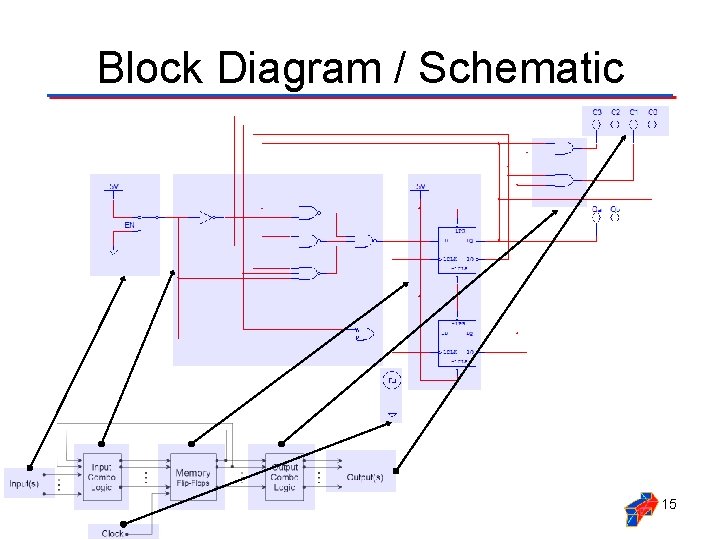

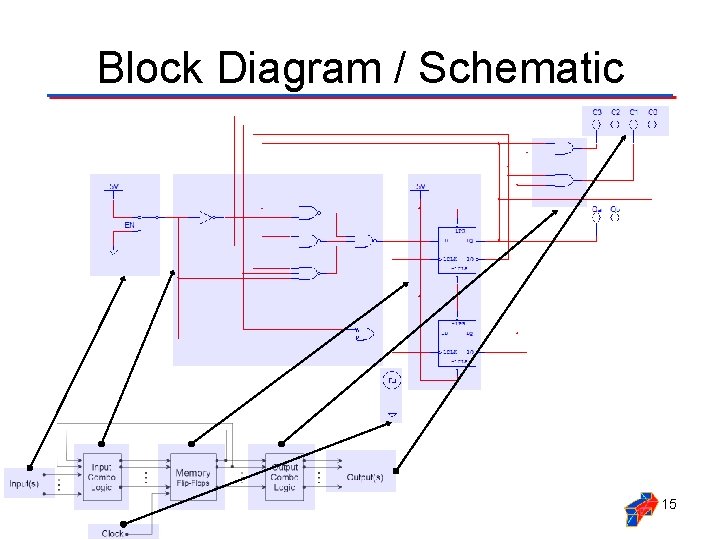

Block Diagram / Schematic 15