Sequential Statements Executed according to the order in

![Loop Syntax [LOOP_LABEL : ] for IDENTIFIER in DISCRETE_RANGE loop -- sequential statements end Loop Syntax [LOOP_LABEL : ] for IDENTIFIER in DISCRETE_RANGE loop -- sequential statements end](https://slidetodoc.com/presentation_image_h2/89929f0cd6e78817feb1e0bd86c9ec3c/image-10.jpg)

- Slides: 20

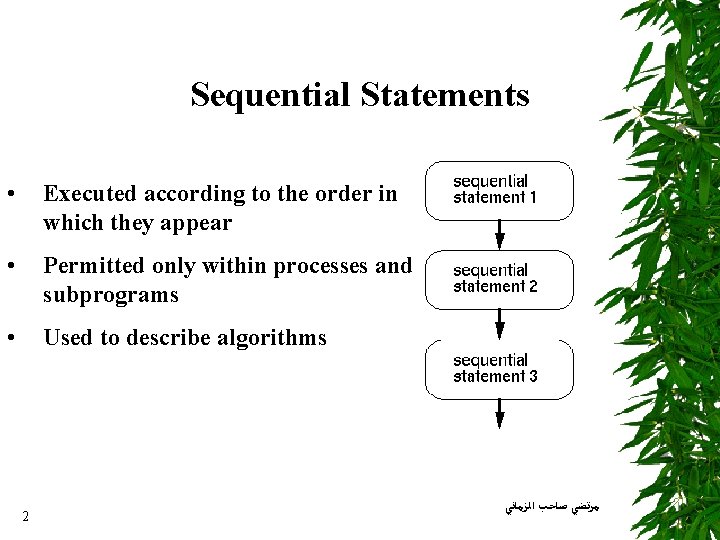

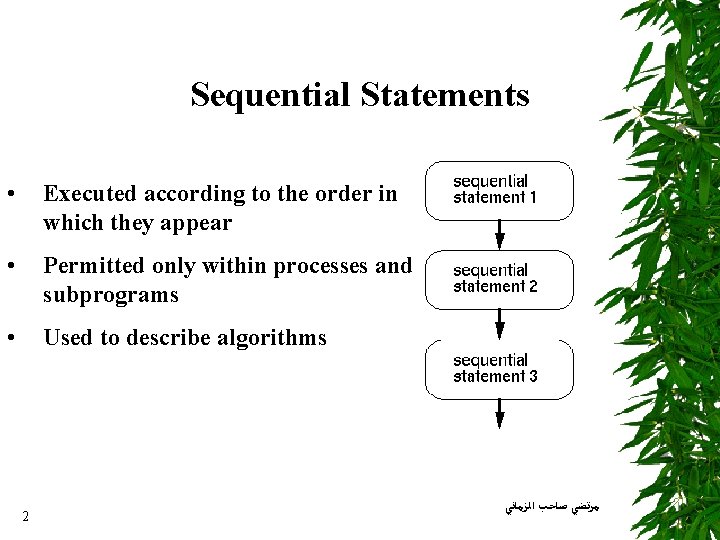

Sequential Statements • Executed according to the order in which they appear • Permitted only within processes and subprograms • Used to describe algorithms 2 ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

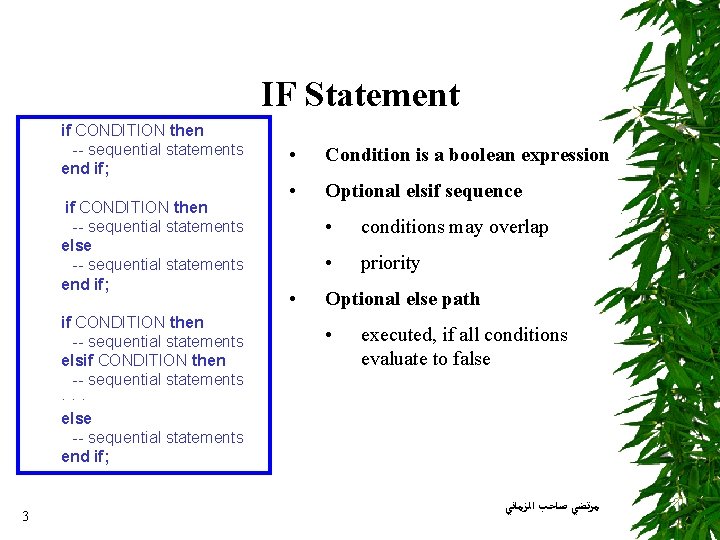

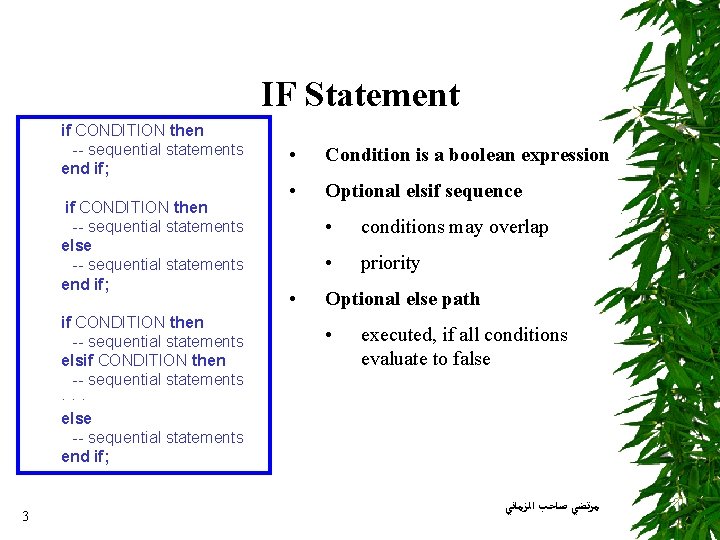

IF Statement if CONDITION then -- sequential statements end if; if CONDITION then -- sequential statements else -- sequential statements end if; if CONDITION then -- sequential statements elsif CONDITION then -- sequential statements ··· else -- sequential statements end if; 3 • Condition is a boolean expression • Optional elsif sequence • • conditions may overlap • priority Optional else path • executed, if all conditions evaluate to false ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

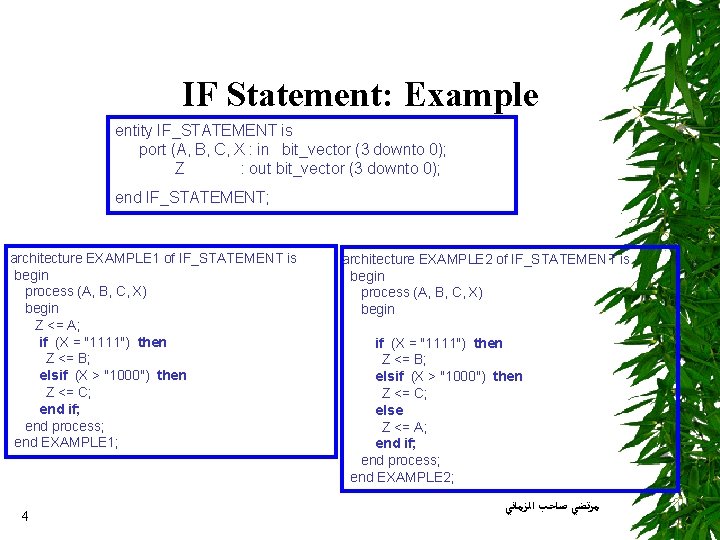

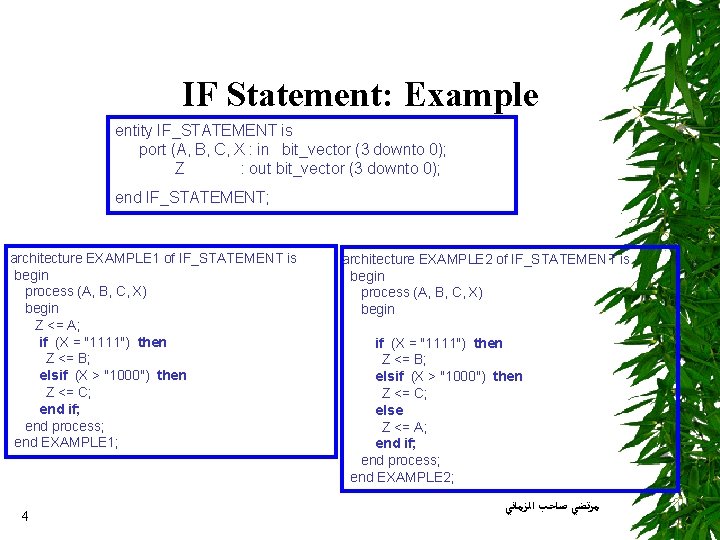

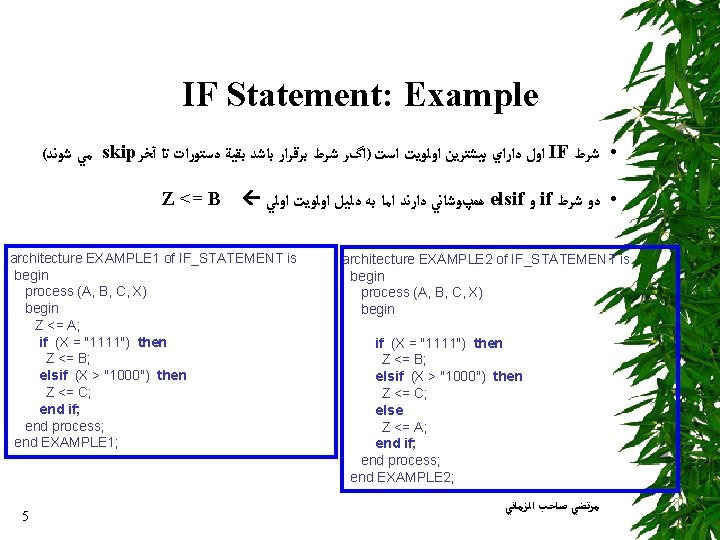

IF Statement: Example entity IF_STATEMENT is port (A, B, C, X : in bit_vector (3 downto 0); Z : out bit_vector (3 downto 0); end IF_STATEMENT; architecture EXAMPLE 1 of IF_STATEMENT is begin process (A, B, C, X) begin Z <= A; if (X = "1111") then Z <= B; elsif (X > "1000") then Z <= C; end if; end process; end EXAMPLE 1; 4 architecture EXAMPLE 2 of IF_STATEMENT is begin process (A, B, C, X) begin if (X = "1111") then Z <= B; elsif (X > "1000") then Z <= C; else Z <= A; end if; end process; end EXAMPLE 2; ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

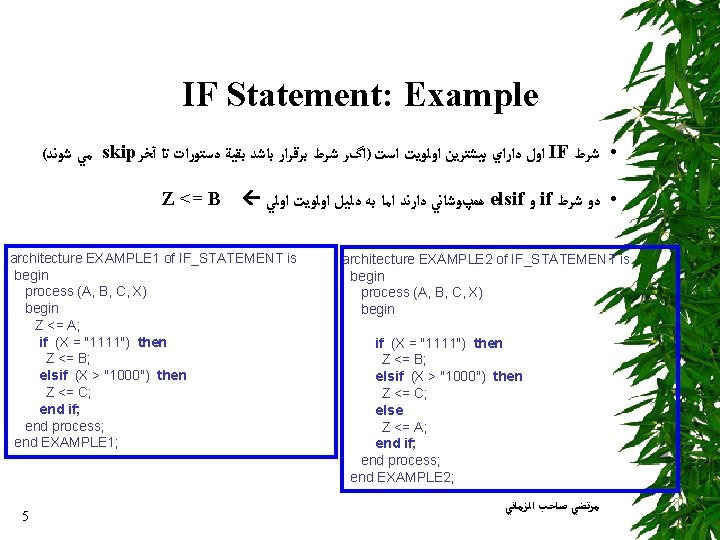

IF Statement: Example ( ﻣﻲ ﺷﻮﻧﺪ skip ﺍﻭﻝ ﺩﺍﺭﺍﻱ ﺑﻴﺸﺘﺮﻳﻦ ﺍﻭﻟﻮﻳﺖ ﺍﺳﺖ )ﺍگﺮ ﺷﺮﻁ ﺑﺮﻗﺮﺍﺭ ﺑﺎﺷﺪ ﺑﻘﻴﺔ ﺩﺳﺘﻮﺭﺍﺕ ﺗﺎ آﺨﺮ IF • ﺷﺮﻁ Z <= B ﻫﻤپﻮﺷﺎﻧﻲ ﺩﺍﺭﻧﺪ ﺍﻣﺎ ﺑﻪ ﺩﻟﻴﻞ ﺍﻭﻟﻮﻳﺖ ﺍﻭﻟﻲ elsif ﻭ if • ﺩﻭ ﺷﺮﻁ architecture EXAMPLE 1 of IF_STATEMENT is begin process (A, B, C, X) begin Z <= A; if (X = "1111") then Z <= B; elsif (X > "1000") then Z <= C; end if; end process; end EXAMPLE 1; 5 architecture EXAMPLE 2 of IF_STATEMENT is begin process (A, B, C, X) begin if (X = "1111") then Z <= B; elsif (X > "1000") then Z <= C; else Z <= A; end if; end process; end EXAMPLE 2; ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

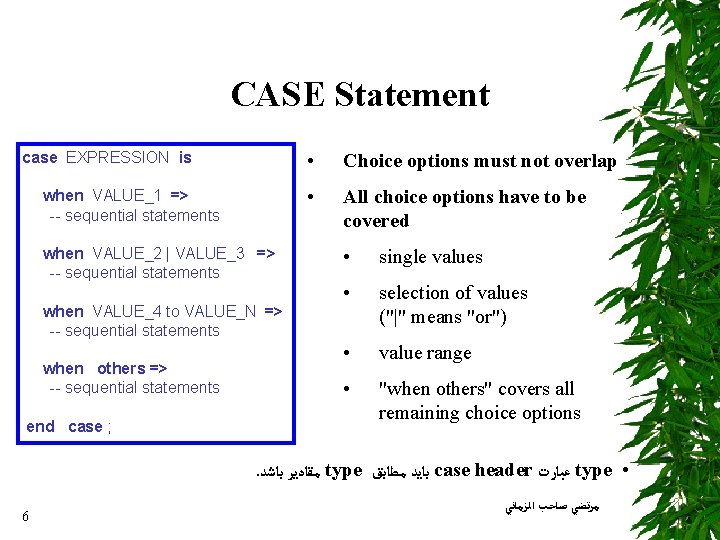

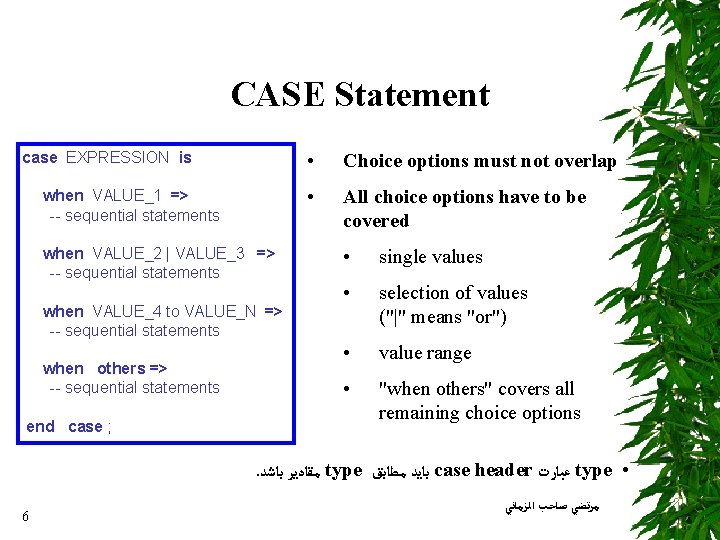

CASE Statement case EXPRESSION is when VALUE_1 => -- sequential statements when VALUE_2 | VALUE_3 => -- sequential statements when VALUE_4 to VALUE_N => -- sequential statements when others => -- sequential statements end case ; • Choice options must not overlap • All choice options have to be covered • single values • selection of values ("|" means "or") • value range • "when others" covers all remaining choice options . ﻣﻘﺎﺩﻳﺮ ﺑﺎﺷﺪ type ﺑﺎﻳﺪ ﻣﻄﺎﺑﻖ case header ﻋﺒﺎﺭﺕ type • 6 ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

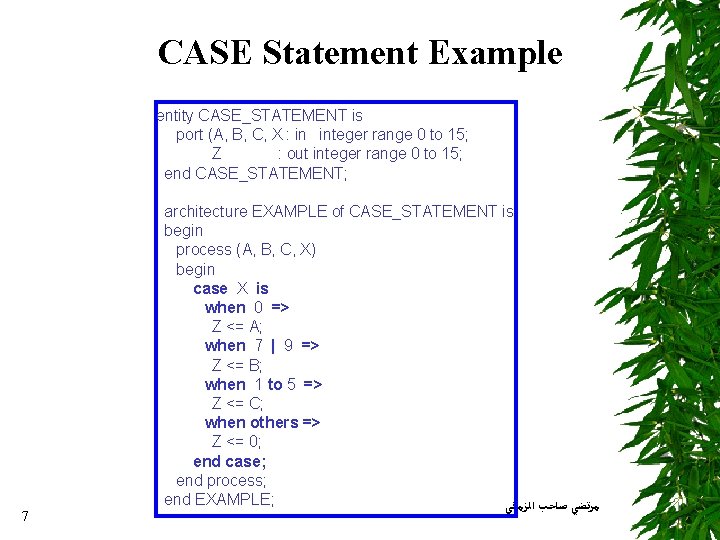

CASE Statement Example entity CASE_STATEMENT is port (A, B, C, X : in integer range 0 to 15; Z : out integer range 0 to 15; end CASE_STATEMENT; 7 architecture EXAMPLE of CASE_STATEMENT is begin process (A, B, C, X) begin case X is when 0 => Z <= A; when 7 | 9 => Z <= B; when 1 to 5 => Z <= C; when others => Z <= 0; end case; end process; end EXAMPLE; ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

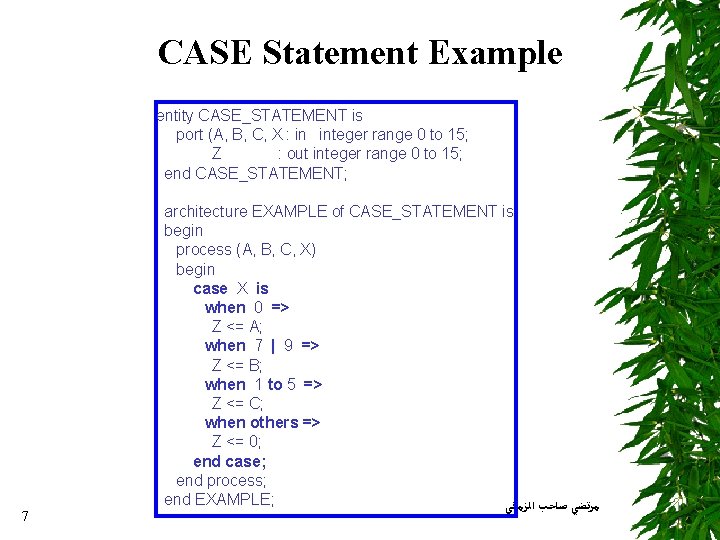

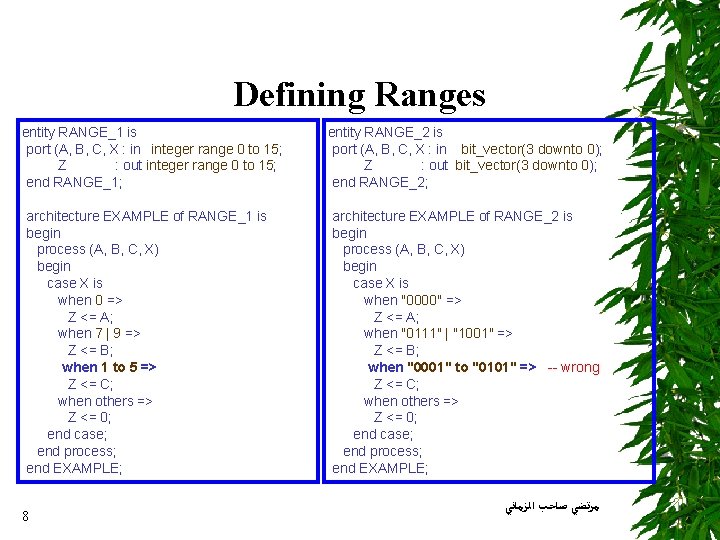

Defining Ranges entity RANGE_1 is port (A, B, C, X : in integer range 0 to 15; Z : out integer range 0 to 15; end RANGE_1; architecture EXAMPLE of RANGE_1 is begin process (A, B, C, X) begin case X is when 0 => Z <= A; when 7 | 9 => Z <= B; when 1 to 5 => Z <= C; when others => Z <= 0; end case; end process; end EXAMPLE; 8 entity RANGE_2 is port (A, B, C, X : in bit_vector(3 downto 0); Z : out bit_vector(3 downto 0); end RANGE_2; architecture EXAMPLE of RANGE_2 is begin process (A, B, C, X) begin case X is when "0000" => Z <= A; when "0111" | "1001" => Z <= B; when "0001" to "0101" => -- wrong Z <= C; when others => Z <= 0; end case; end process; end EXAMPLE; ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

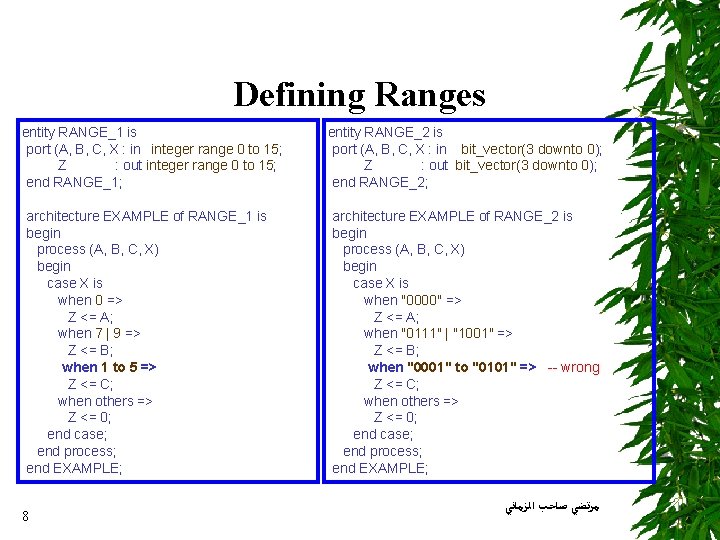

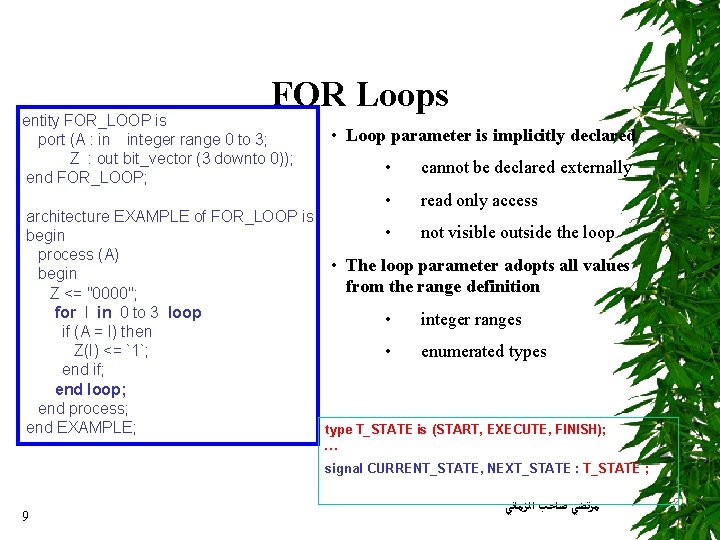

FOR Loops entity FOR_LOOP is port (A : in integer range 0 to 3; Z : out bit_vector (3 downto 0)); end FOR_LOOP; • Loop parameter is implicitly declared • cannot be declared externally • read only access architecture EXAMPLE of FOR_LOOP is • not visible outside the loop begin process (A) • The loop parameter adopts all values begin from the range definition Z <= "0000"; for I in 0 to 3 loop • integer ranges if (A = I) then Z(I) <= `1`; • enumerated types end if; end loop; end process; end EXAMPLE; type T_STATE is (START, EXECUTE, FINISH); … signal CURRENT_STATE, NEXT_STATE : T_STATE ; 9 ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

![Loop Syntax LOOPLABEL for IDENTIFIER in DISCRETERANGE loop sequential statements end Loop Syntax [LOOP_LABEL : ] for IDENTIFIER in DISCRETE_RANGE loop -- sequential statements end](https://slidetodoc.com/presentation_image_h2/89929f0cd6e78817feb1e0bd86c9ec3c/image-10.jpg)

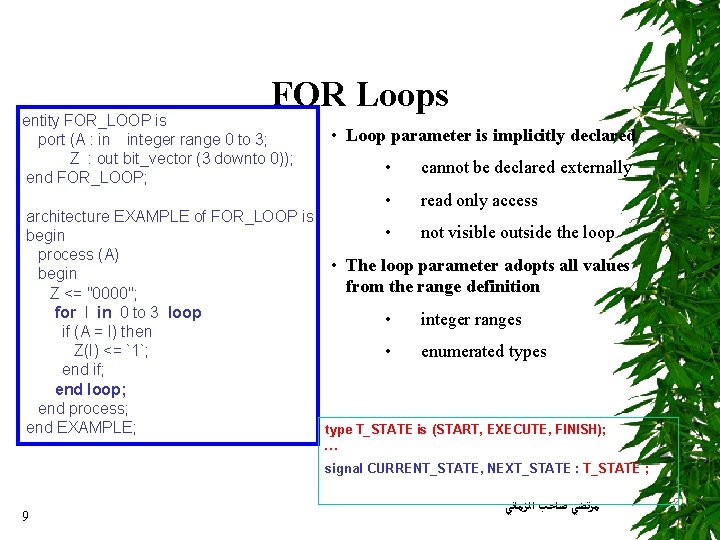

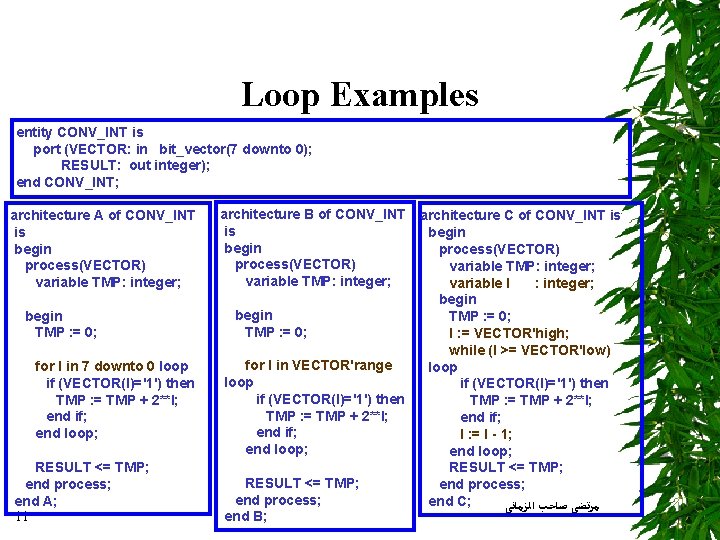

Loop Syntax [LOOP_LABEL : ] for IDENTIFIER in DISCRETE_RANGE loop -- sequential statements end loop [LOOP_LABEL] ; • Optional label • Use especially for nested loops • Range attributes [LOOP_LABEL : ] while CONDITION loop -- sequential statements end loop [LOOP_LABEL] ; • ‘low • ‘high • ‘range Synthesis requirements: - Loops must have a fixed range - 'while' constructs usually cannot be synthesized 10 ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

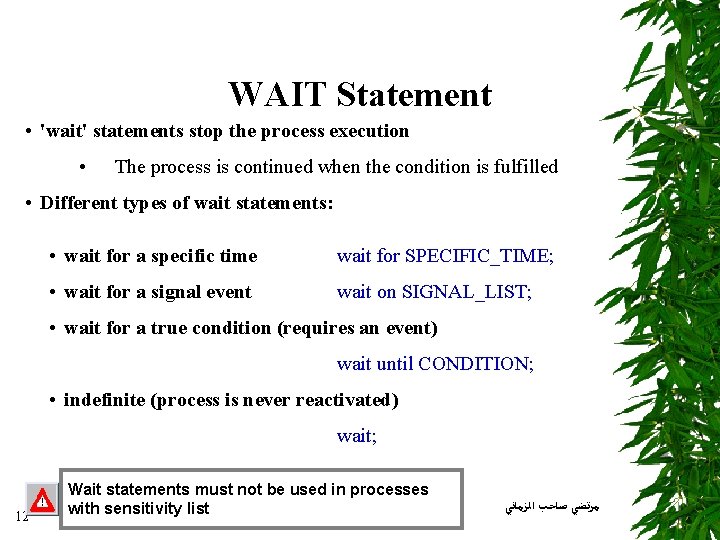

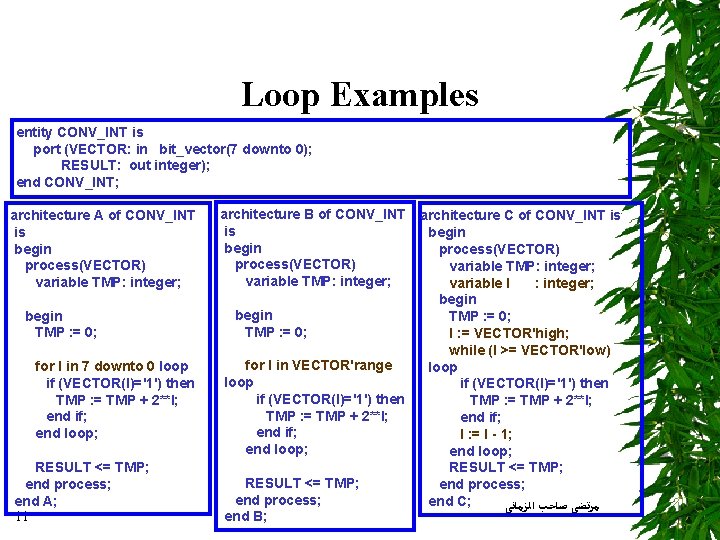

Loop Examples entity CONV_INT is port (VECTOR: in bit_vector(7 downto 0); RESULT: out integer); end CONV_INT; architecture A of CONV_INT is begin process(VECTOR) variable TMP: integer; begin TMP : = 0; for I in 7 downto 0 loop if (VECTOR(I)='1') then TMP : = TMP + 2**I; end if; end loop; RESULT <= TMP; end process; end A; 11 architecture B of CONV_INT is begin process(VECTOR) variable TMP: integer; begin TMP : = 0; for I in VECTOR'range loop if (VECTOR(I)='1') then TMP : = TMP + 2**I; end if; end loop; RESULT <= TMP; end process; end B; architecture C of CONV_INT is begin process(VECTOR) variable TMP: integer; variable I : integer; begin TMP : = 0; I : = VECTOR'high; while (I >= VECTOR'low) loop if (VECTOR(I)='1') then TMP : = TMP + 2**I; end if; I : = I - 1; end loop; RESULT <= TMP; end process; end C; ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

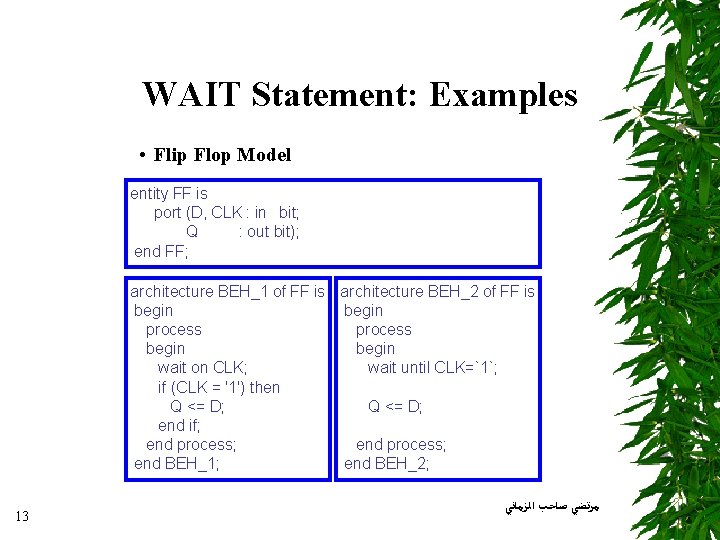

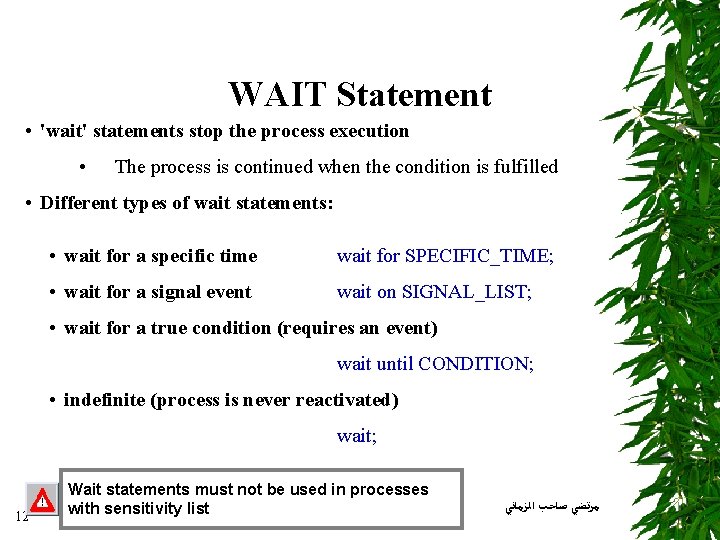

WAIT Statement • 'wait' statements stop the process execution • The process is continued when the condition is fulfilled • Different types of wait statements: • wait for a specific time wait for SPECIFIC_TIME; • wait for a signal event wait on SIGNAL_LIST; • wait for a true condition (requires an event) wait until CONDITION; • indefinite (process is never reactivated) wait; 12 Wait statements must not be used in processes with sensitivity list ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

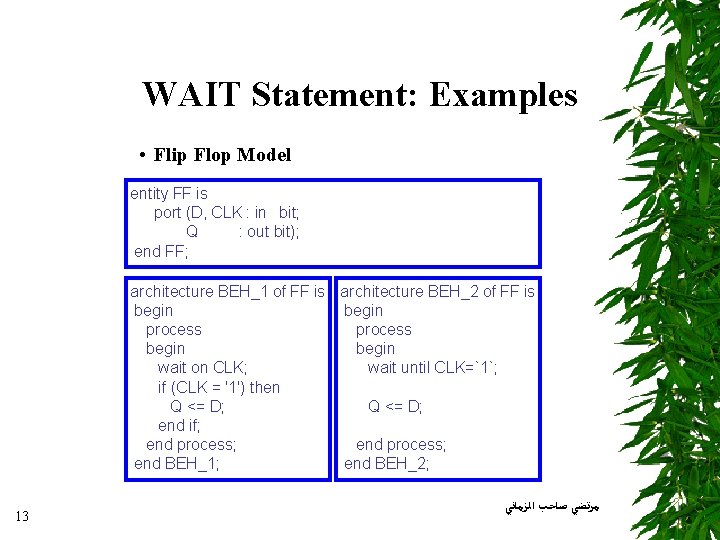

WAIT Statement: Examples • Flip Flop Model entity FF is port (D, CLK : in bit; Q : out bit); end FF; architecture BEH_1 of FF is architecture BEH_2 of FF is begin process begin wait on CLK; wait until CLK=`1`; if (CLK = '1') then Q <= D; end if; end process; end BEH_1; end BEH_2; 13 ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

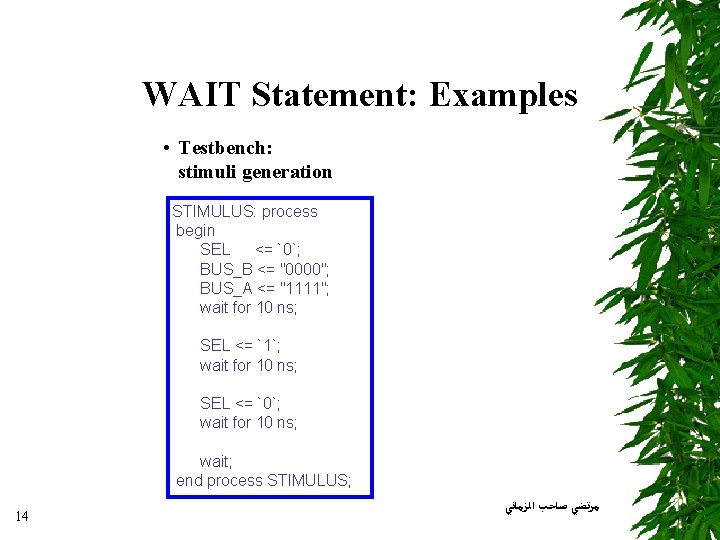

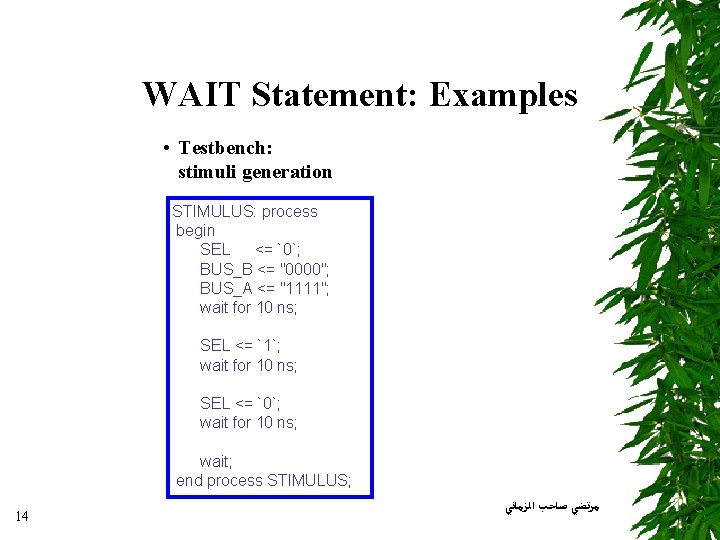

WAIT Statement: Examples • Testbench: stimuli generation STIMULUS: process begin SEL <= `0`; BUS_B <= "0000"; BUS_A <= "1111"; wait for 10 ns; SEL <= `1`; wait for 10 ns; SEL <= `0`; wait for 10 ns; wait; end process STIMULUS; 14 ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

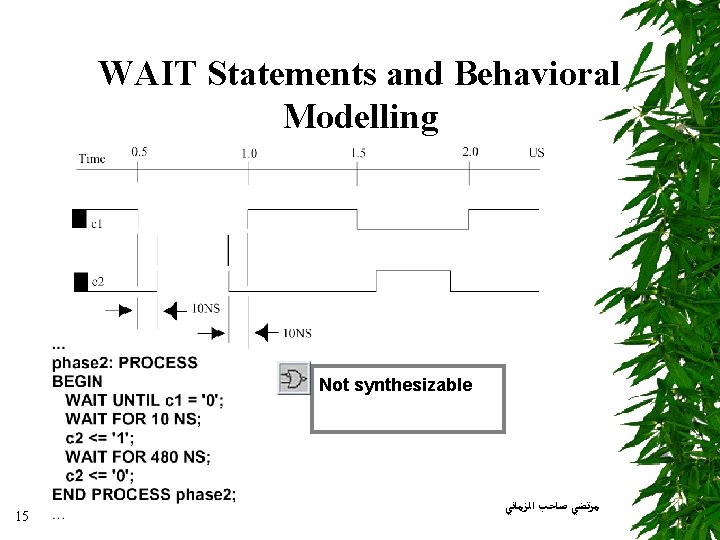

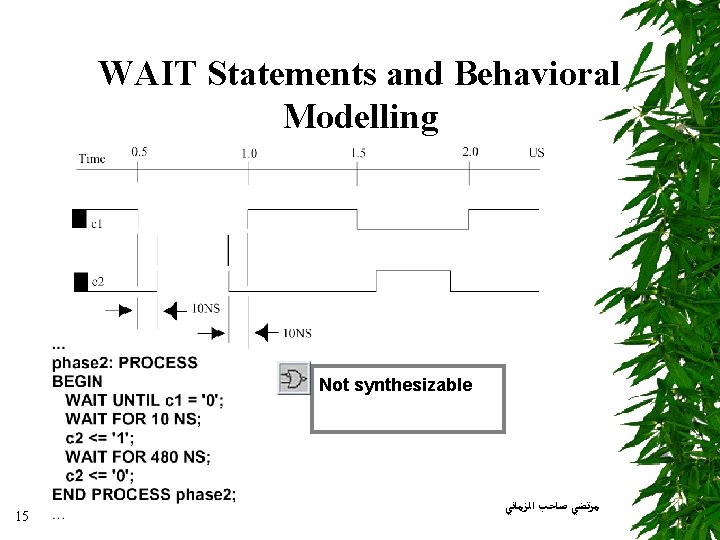

WAIT Statements and Behavioral Modelling Not synthesizable 15 ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

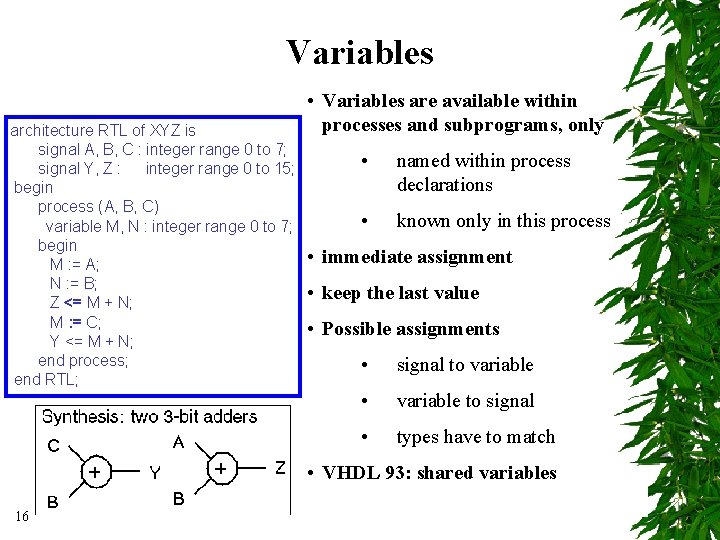

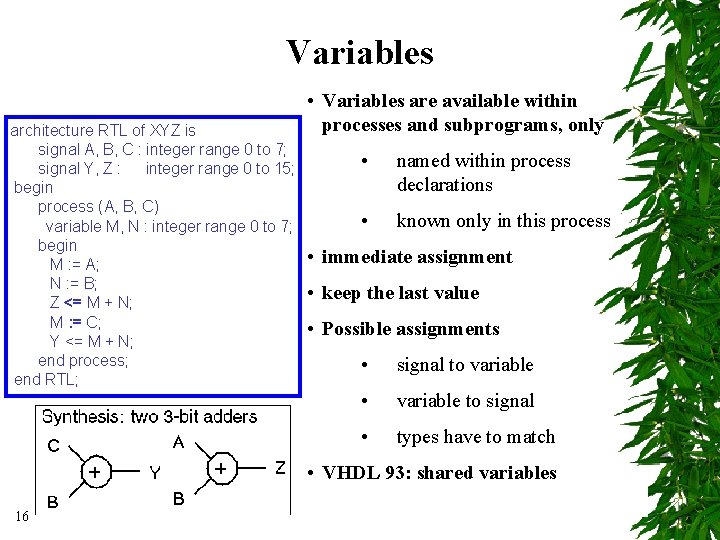

Variables architecture RTL of XYZ is signal A, B, C : integer range 0 to 7; signal Y, Z : integer range 0 to 15; begin process (A, B, C) variable M, N : integer range 0 to 7; begin M : = A; N : = B; Z <= M + N; M : = C; Y <= M + N; end process; end RTL; • Variables are available within processes and subprograms, only • named within process declarations • known only in this process • immediate assignment • keep the last value • Possible assignments • signal to variable • variable to signal • types have to match • VHDL 93: shared variables 16 ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

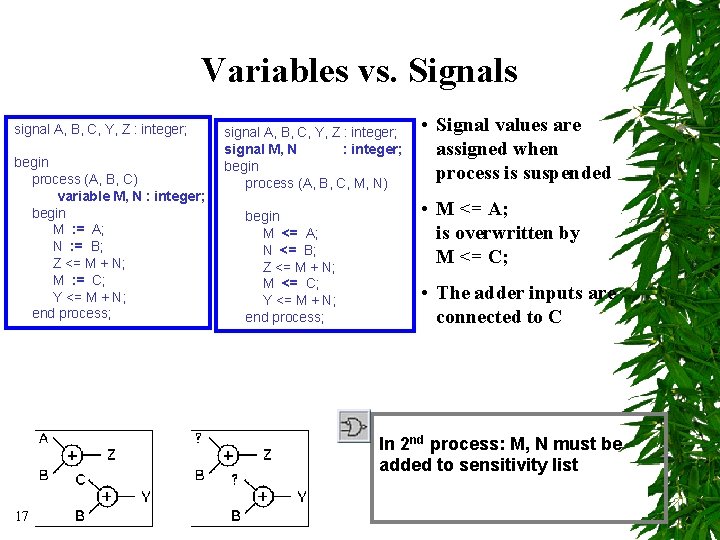

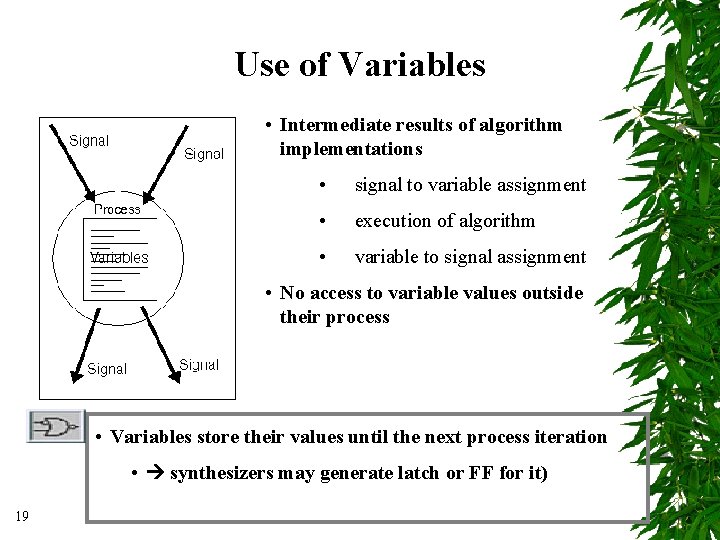

Variables vs. Signals signal A, B, C, Y, Z : integer; begin process (A, B, C) variable M, N : integer; begin M : = A; N : = B; Z <= M + N; M : = C; Y <= M + N; end process; signal A, B, C, Y, Z : integer; signal M, N : integer; begin process (A, B, C, M, N) begin M <= A; N <= B; Z <= M + N; M <= C; Y <= M + N; end process; • Signal values are assigned when process is suspended • M <= A; is overwritten by M <= C; • The adder inputs are connected to C In 2 nd process: M, N must be added to sensitivity list 17 ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

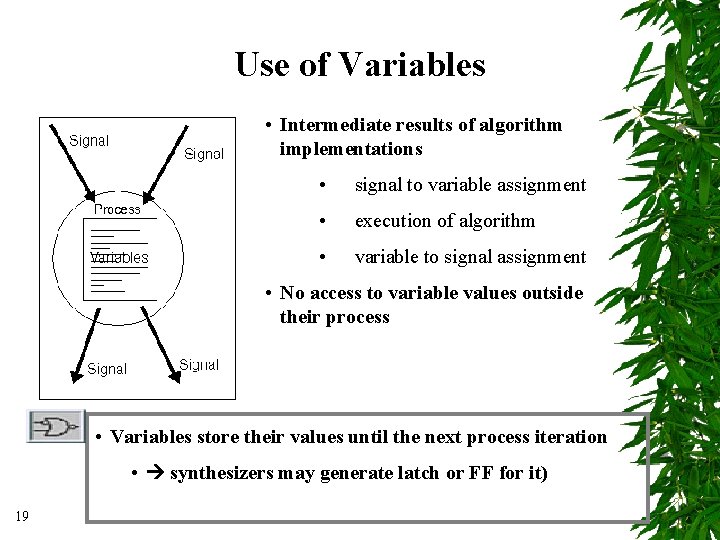

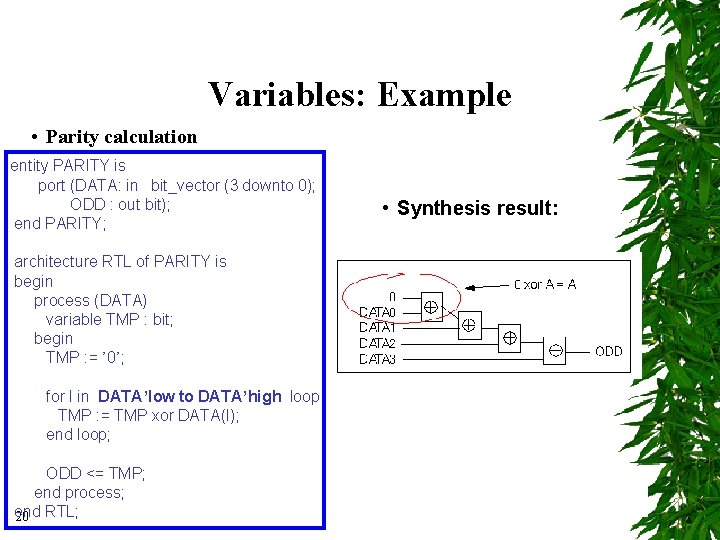

Use of Variables • Intermediate results of algorithm implementations • signal to variable assignment • execution of algorithm • variable to signal assignment • No access to variable values outside their process • Variables store their values until the next process iteration • synthesizers may generate latch or FF for it) 19 ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

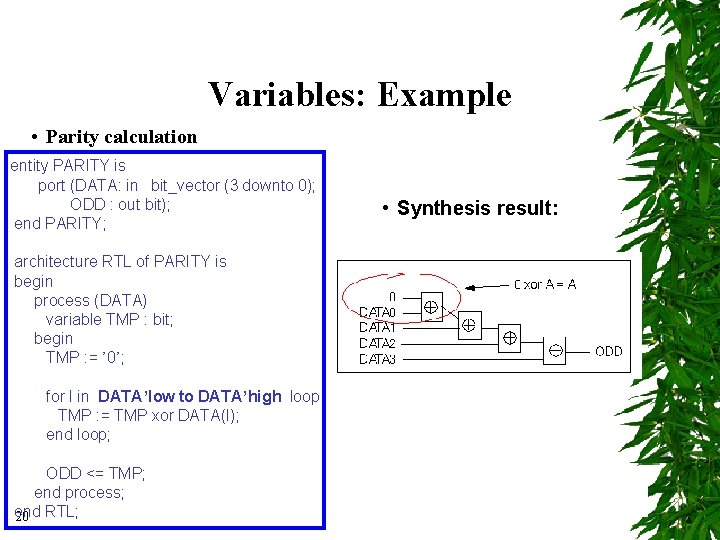

Variables: Example • Parity calculation entity PARITY is port (DATA: in bit_vector (3 downto 0); ODD : out bit); end PARITY; • Synthesis result: architecture RTL of PARITY is begin process (DATA) variable TMP : bit; begin TMP : = ’ 0’; for I in DATA’low to DATA’high loop TMP : = TMP xor DATA(I); end loop; ODD <= TMP; end process; end 20 RTL; ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ

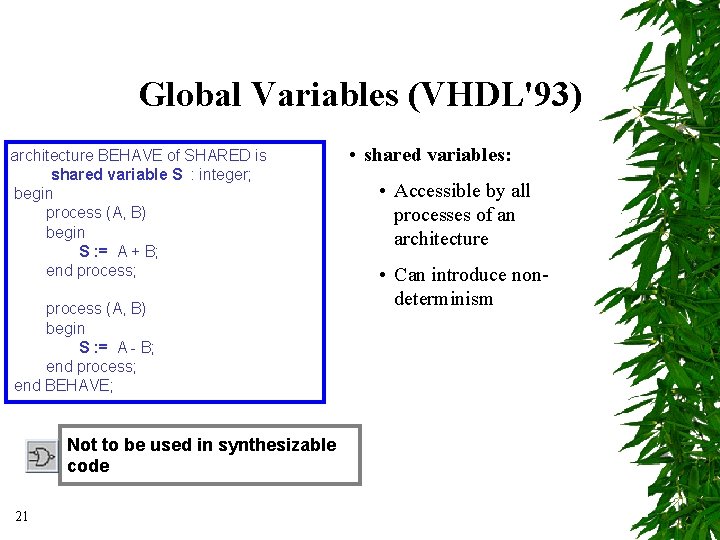

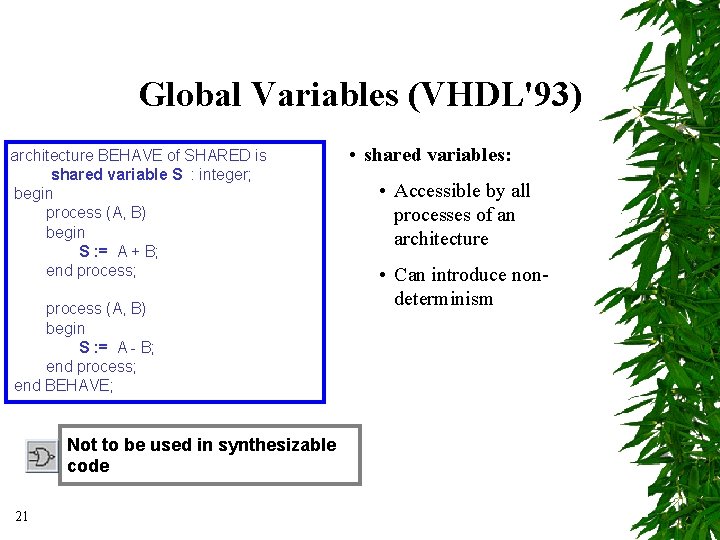

Global Variables (VHDL'93) architecture BEHAVE of SHARED is shared variable S : integer; begin process (A, B) begin S : = A + B; end process; process (A, B) begin S : = A - B; end process; end BEHAVE; • shared variables: • Accessible by all processes of an architecture • Can introduce nondeterminism Not to be used in synthesizable code 21 ﻣﺮﺗﻀﻲ ﺻﺎﺣﺐ ﺍﻟﺰﻣﺎﻧﻲ