Safe BDD Minimization Using Dont Cares Author Youpyo

Safe BDD Minimization Using Don’t Cares Author Youpyo Hong , Peter A. Beerel , Jerry R. Burch , Kenneth L. Mc. Millan Publisher Proceedings of the 34 th annual conference on DAC , Pages: 208 -213 , 1997 Speaker 陳佳鴻 1

Outline n n Introduction Basic Compaction Leaf-identifying Compaction Experimental Results 2

Introduction (1/2) n Completely specified function: f dc = f on + f off = Tautology n Incompletely specified function: f dc≠ f on + f off ≠ Tautology 3

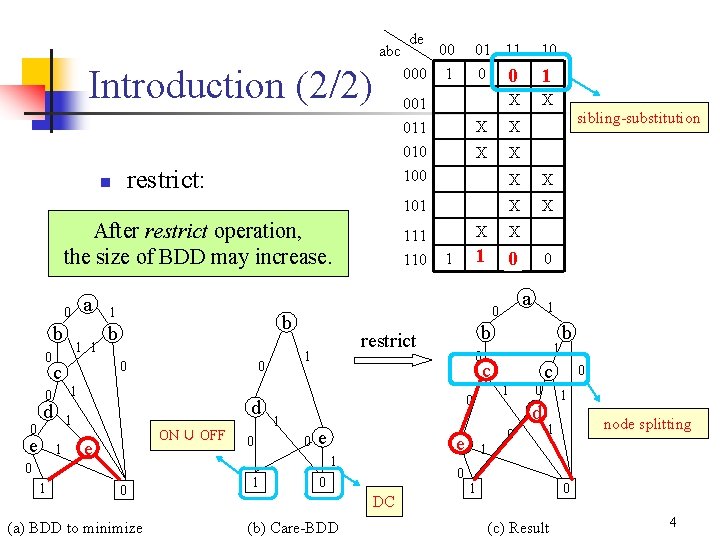

abc Introduction (2/2) 00 000 1 001 010 100 restrict: n de 01 11 0 0 X 10 1 X X X X 101 After restrict operation, the size of BDD may increase. a 0 b 0 c 0 0 d e 1 1 d 1 1 ON ∪ OFF e 0 (a) BDD to minimize 1 X X X 1 X 0 X 0 1 0 e ee 0 0 DC (b) Care-BDD 0 a 1 1 0 c 1 0 X b restrict 1 0 0 1 X 0 b b 111 110 X 1 1 b c 0 d 0 sibling-substitution 0 1 node splitting 1 1 0 (c) Result 4

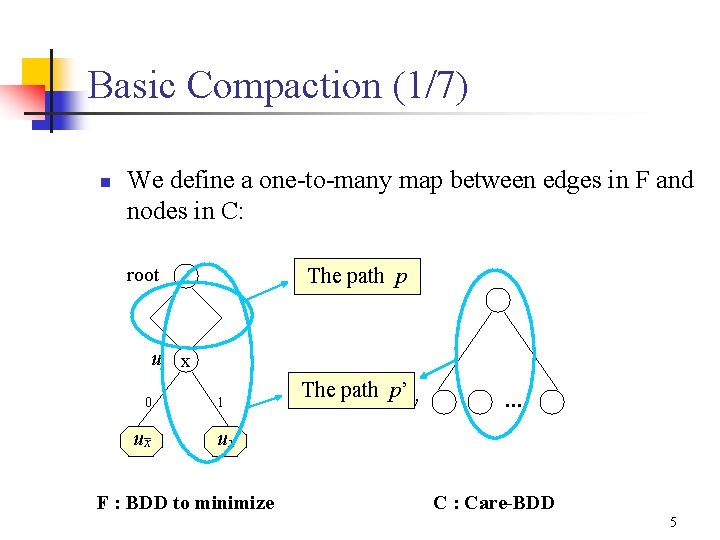

Basic Compaction (1/7) n We define a one-to-many map between edges in F and nodes in C: root The path p u x 0 ux 1 The path p’ v … ux F : BDD to minimize C : Care-BDD 5

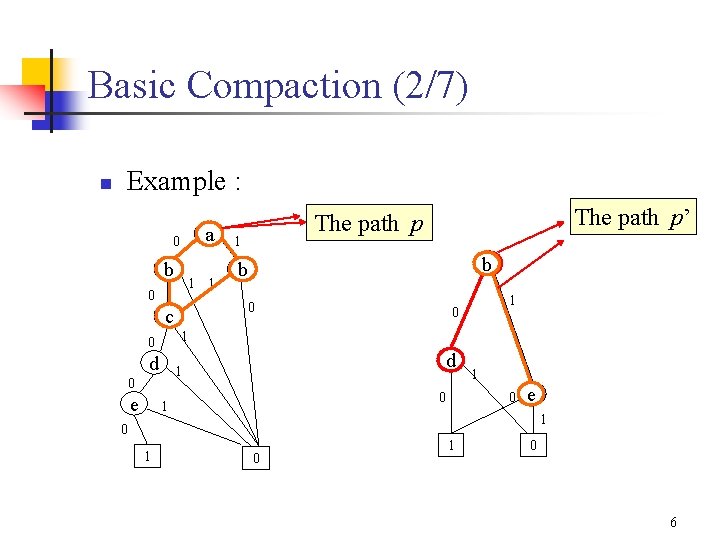

Basic Compaction (2/7) n Example : aa 0 bb 1 1 0 1 bb bb 0 cc 1 0 d d 1 0 e The path p’ The path p 0 1 1 0 ee 1 0 1 0 6

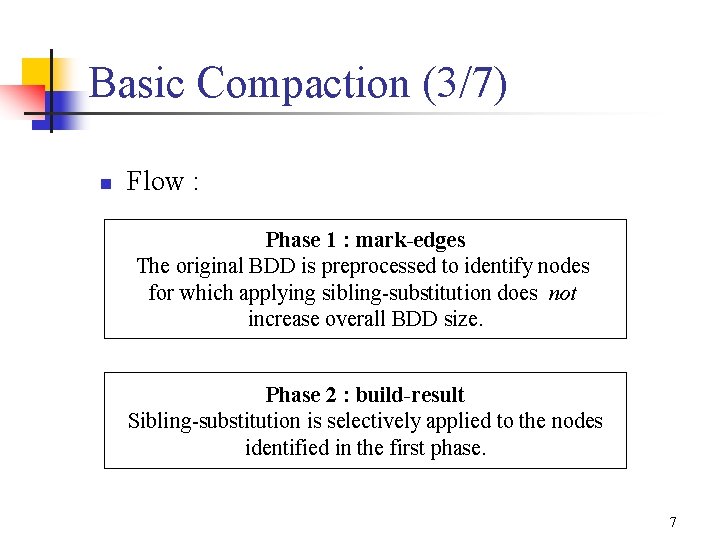

Basic Compaction (3/7) n Flow : Phase 1 : mark-edges The original BDD is preprocessed to identify nodes for which applying sibling-substitution does not increase overall BDD size. Phase 2 : build-result Sibling-substitution is selectively applied to the nodes identified in the first phase. 7

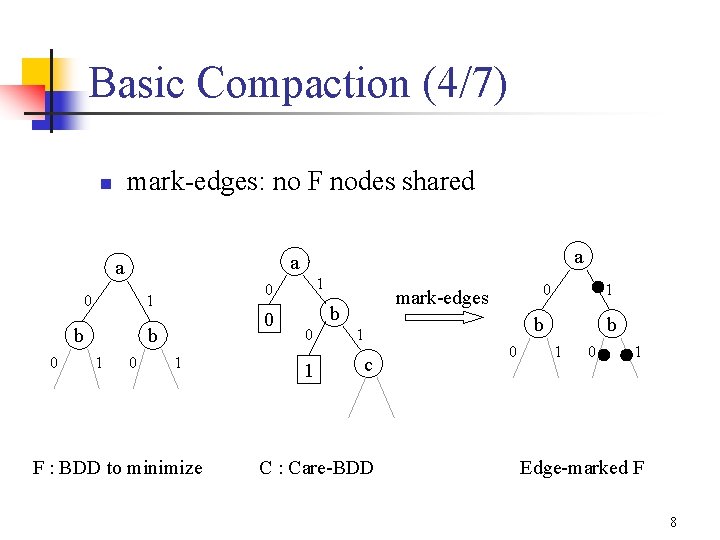

Basic Compaction (4/7) mark-edges: no F nodes shared n 0 0 b 1 0 1 b 0 a a a 1 F : BDD to minimize b 0 1 0 mark-edges 1 b 1 c C : Care-BDD 0 b 1 0 1 Edge-marked F 8

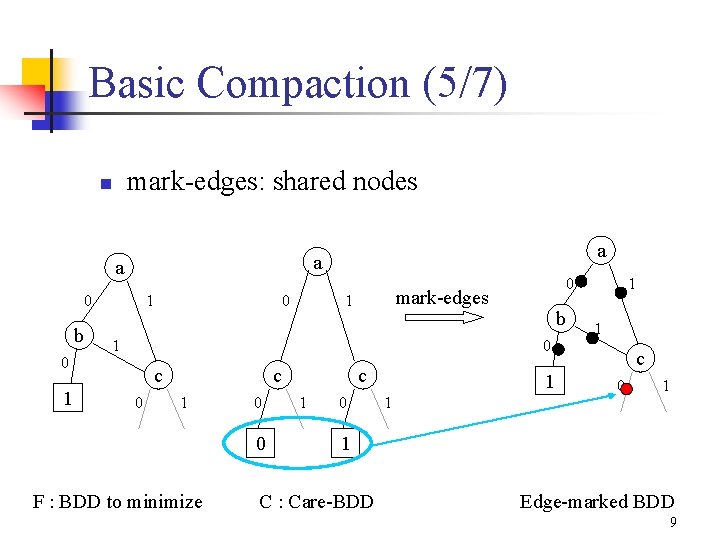

Basic Compaction (5/7) mark-edges: shared nodes n a 0 b 0 1 a a 1 0 0 mark-edges 1 1 b 0 c 1 0 0 F : BDD to minimize c 1 0 1 1 c 0 1 1 C : Care-BDD Edge-marked BDD 9

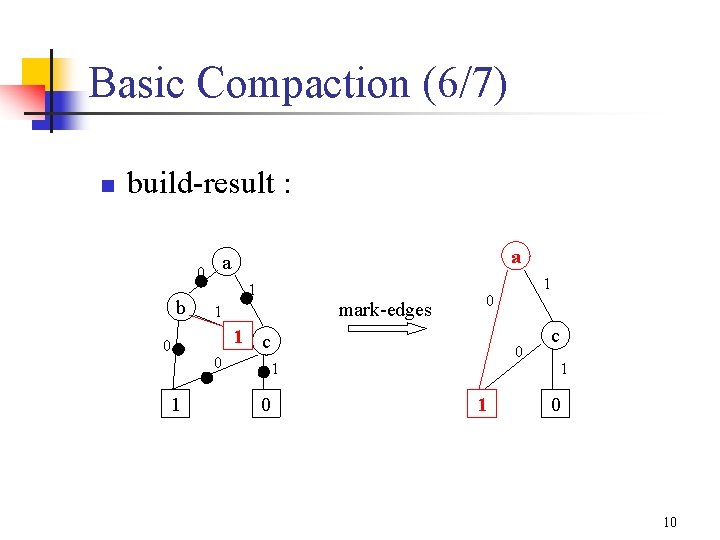

Basic Compaction (6/7) n build-result : 0 b 0 1 a a 1 mark-edges 1 0 1 c 0 0 1 1 c 1 0 10

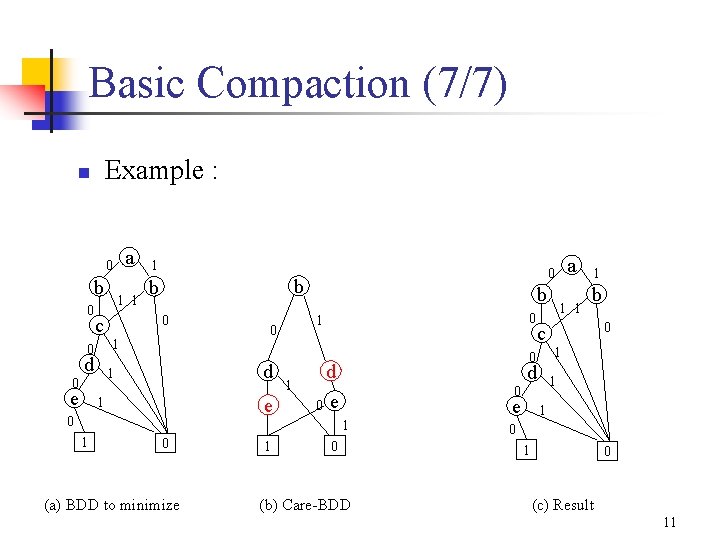

Basic Compaction (7/7) Example : n a 0 b 0 c 0 0 d e 1 1 1 b b 0 1 d 1 0 e 1 0 b 0 1 0 (a) BDD to minimize 1 c 0 d 0 e 0 d e 1 1 a 0 0 (b) Care-BDD 1 1 1 b 0 1 1 1 0 (c) Result 11

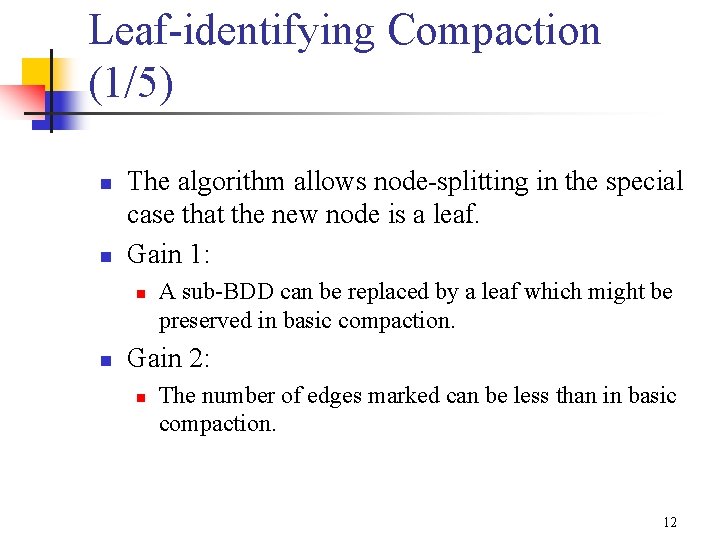

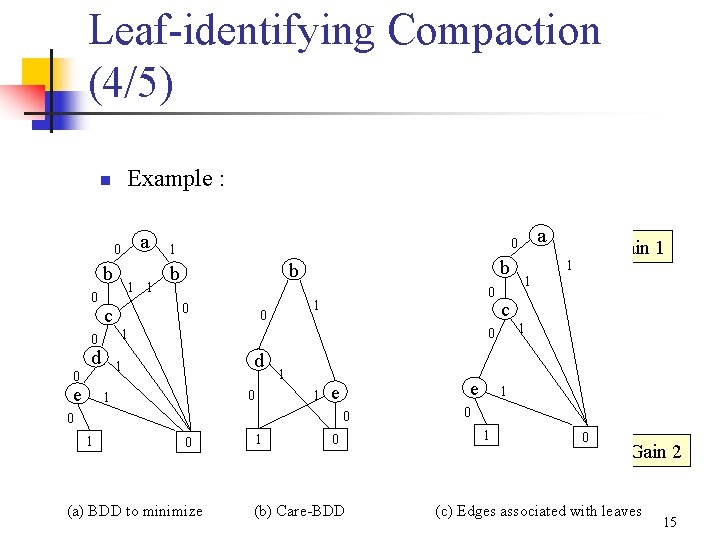

Leaf-identifying Compaction (1/5) n n The algorithm allows node-splitting in the special case that the new node is a leaf. Gain 1: n n A sub-BDD can be replaced by a leaf which might be preserved in basic compaction. Gain 2: n The number of edges marked can be less than in basic compaction. 12

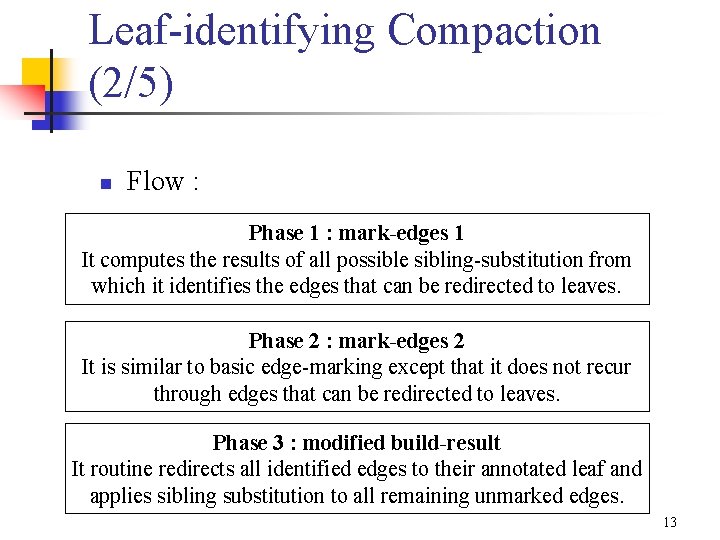

Leaf-identifying Compaction (2/5) n Flow : Phase 1 : mark-edges 1 It computes the results of all possible sibling-substitution from which it identifies the edges that can be redirected to leaves. Phase 2 : mark-edges 2 It is similar to basic edge-marking except that it does not recur through edges that can be redirected to leaves. Phase 3 : modified build-result It routine redirects all identified edges to their annotated leaf and applies sibling substitution to all remaining unmarked edges. 13

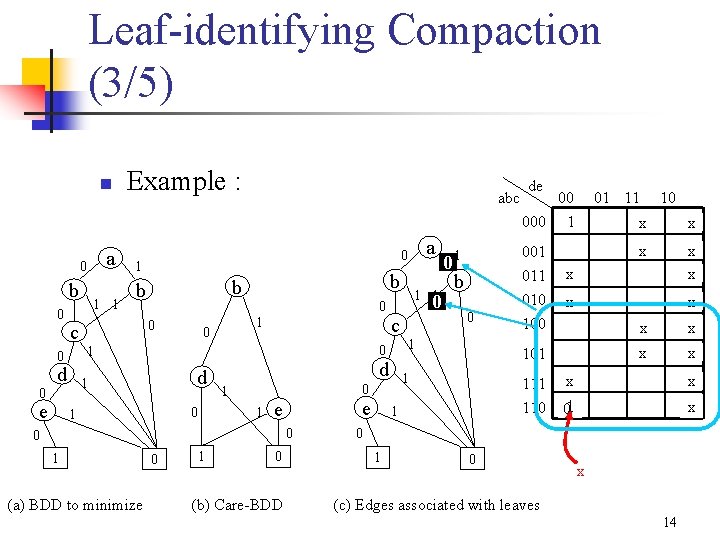

Leaf-identifying Compaction (3/5) n a 0 b 0 abc b b b 0 0 d 0 1 1 e e 0 (a) BDD to minimize 0 1 0 (b) Care-BDD 0 de 00 000 1 001 010 100 01 11 110 1 10 x x x x 101 1 01 b 1 d 0 1 0 c 1 0 1 d a 0 1 c 0 e 1 1 Example : x x x 101 x 0 1 0 x (c) Edges associated with leaves 14

Leaf-identifying Compaction (4/5) Example : n a 0 b b b 0 c 0 1 0 d d 1 0 0 1 d 1 1 0 ee e 0 0 1 cc 00 1 0 e 1 1 aa 00 1 0 (a) BDD to minimize 1 0 (b) Care-BDD 0 0 11 1 0 Gain 1 0 11 0 b 1 0 11 1 1 0 0 Gain 2 (c) Edges associated with leaves 15

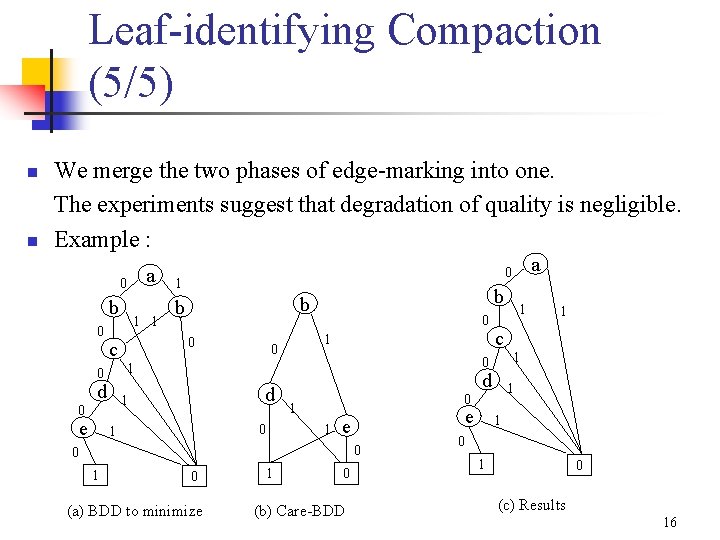

Leaf-identifying Compaction (5/5) n n We merge the two phases of edge-marking into one. The experiments suggest that degradation of quality is negligible. Example : a 0 b 0 1 bb b b 0 c 00 1 0 d d 1 0 0 1 00 1 1 0 0 (a) BDD to minimize 1 0 (b) Care-BDD dd ee e 0 1 cc 00 1 0 e 1 1 aa 00 0 0 01 b 11 1 1 0 0 11 11 1 1 0 0 (c) Results 16

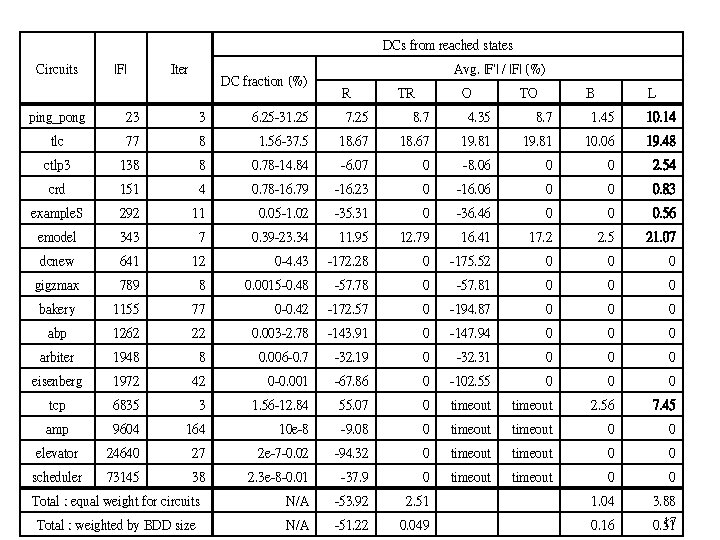

DCs from reached states Circuits |F| Iter DC fraction (%) Avg. |F'| / |F| (%) R TR O TO B L ping_pong 23 3 6. 25 -31. 25 7. 25 8. 7 4. 35 8. 7 1. 45 10. 14 tlc 77 8 1. 56 -37. 5 18. 67 19. 81 10. 06 19. 48 ctlp 3 138 8 0. 78 -14. 84 -6. 07 0 -8. 06 0 0 2. 54 crd 151 4 0. 78 -16. 79 -16. 23 0 -16. 06 0 0 0. 83 example. S 292 11 0. 05 -1. 02 -35. 31 0 -36. 46 0 0 0. 56 emodel 343 7 0. 39 -23. 34 11. 95 12. 79 16. 41 17. 2 2. 5 21. 07 dcnew 641 12 0 -4. 43 -172. 28 0 -175. 52 0 0 0 gigzmax 789 8 0. 0015 -0. 48 -57. 78 0 -57. 81 0 0 0 bakery 1155 77 0 -0. 42 -172. 57 0 -194. 87 0 0 0 abp 1262 22 0. 003 -2. 78 -143. 91 0 -147. 94 0 0 0 arbiter 1948 8 0. 006 -0. 7 -32. 19 0 -32. 31 0 0 0 eisenberg 1972 42 0 -0. 001 -67. 86 0 -102. 55 0 0 0 tcp 6835 3 1. 56 -12. 84 55. 07 0 timeout 2. 56 7. 45 amp 9604 164 10 e-8 -9. 08 0 timeout 0 0 elevator 24640 27 2 e-7 -0. 02 -94. 32 0 timeout 0 0 scheduler 73145 38 2. 3 e-8 -0. 01 -37. 9 0 timeout 0 0 Total : equal weight for circuits N/A -53. 92 2. 51 1. 04 3. 88 Total : weighted by BDD size N/A -51. 22 0. 049 0. 16 17 0. 51

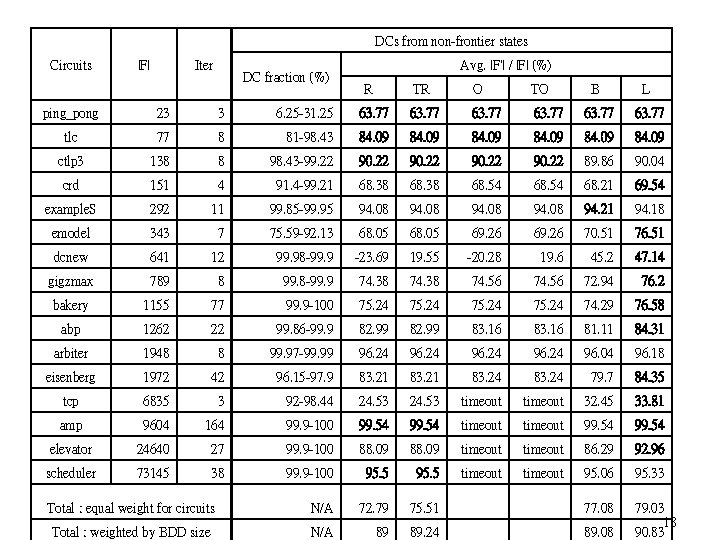

DCs from non-frontier states Circuits |F| Iter DC fraction (%) Avg. |F'| / |F| (%) R TR O TO B L ping_pong 23 3 6. 25 -31. 25 63. 77 tlc 77 8 81 -98. 43 84. 09 ctlp 3 138 8 98. 43 -99. 22 90. 22 89. 86 90. 04 crd 151 4 91. 4 -99. 21 68. 38 68. 54 68. 21 69. 54 example. S 292 11 99. 85 -99. 95 94. 08 94. 21 94. 18 emodel 343 7 75. 59 -92. 13 68. 05 69. 26 70. 51 76. 51 dcnew 641 12 99. 98 -99. 9 -23. 69 19. 55 -20. 28 19. 6 45. 2 47. 14 gigzmax 789 8 99. 8 -99. 9 74. 38 74. 56 72. 94 76. 2 bakery 1155 77 99. 9 -100 75. 24 74. 29 76. 58 abp 1262 22 99. 86 -99. 9 82. 99 83. 16 81. 11 84. 31 arbiter 1948 8 99. 97 -99. 99 96. 24 96. 04 96. 18 eisenberg 1972 42 96. 15 -97. 9 83. 21 83. 24 79. 7 84. 35 tcp 6835 3 92 -98. 44 24. 53 timeout 32. 45 33. 81 amp 9604 164 99. 9 -100 99. 54 timeout 99. 54 elevator 24640 27 99. 9 -100 88. 09 timeout 86. 29 92. 96 scheduler 73145 38 99. 9 -100 95. 5 timeout 95. 06 95. 33 Total : equal weight for circuits N/A 72. 79 75. 51 77. 08 Total : weighted by BDD size N/A 89 89. 24 89. 08 79. 03 18 90. 83

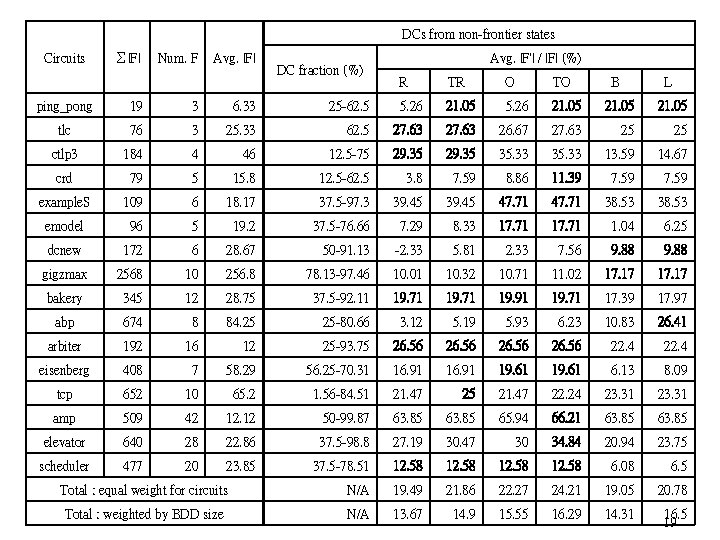

DCs from non-frontier states Circuits Σ|F| Num. F Avg. |F| DC fraction (%) Avg. |F'| / |F| (%) R TR O TO B L ping_pong 19 3 6. 33 25 -62. 5 5. 26 21. 05 tlc 76 3 25. 33 62. 5 27. 63 26. 67 27. 63 25 25 ctlp 3 184 4 46 12. 5 -75 29. 35 35. 33 13. 59 14. 67 crd 79 5 15. 8 12. 5 -62. 5 3. 8 7. 59 8. 86 11. 39 7. 59 example. S 109 6 18. 17 37. 5 -97. 3 39. 45 47. 71 38. 53 emodel 96 5 19. 2 37. 5 -76. 66 7. 29 8. 33 17. 71 1. 04 6. 25 dcnew 172 6 28. 67 50 -91. 13 -2. 33 5. 81 2. 33 7. 56 9. 88 gigzmax 2568 10 256. 8 78. 13 -97. 46 10. 01 10. 32 10. 71 11. 02 17. 17 bakery 345 12 28. 75 37. 5 -92. 11 19. 71 19. 91 19. 71 17. 39 17. 97 abp 674 8 84. 25 25 -80. 66 3. 12 5. 19 5. 93 6. 23 10. 83 26. 41 arbiter 192 16 12 25 -93. 75 26. 56 22. 4 eisenberg 408 7 58. 29 56. 25 -70. 31 16. 91 19. 61 6. 13 8. 09 tcp 652 10 65. 2 1. 56 -84. 51 21. 47 25 21. 47 22. 24 23. 31 amp 509 42 12. 12 50 -99. 87 63. 85 65. 94 66. 21 63. 85 elevator 640 28 22. 86 37. 5 -98. 8 27. 19 30. 47 30 34. 84 20. 94 23. 75 scheduler 477 20 23. 85 37. 5 -78. 51 12. 58 6. 08 6. 5 Total : equal weight for circuits N/A 19. 49 21. 86 22. 27 24. 21 19. 05 20. 78 Total : weighted by BDD size N/A 13. 67 14. 9 15. 55 16. 29 14. 31 16. 5 19

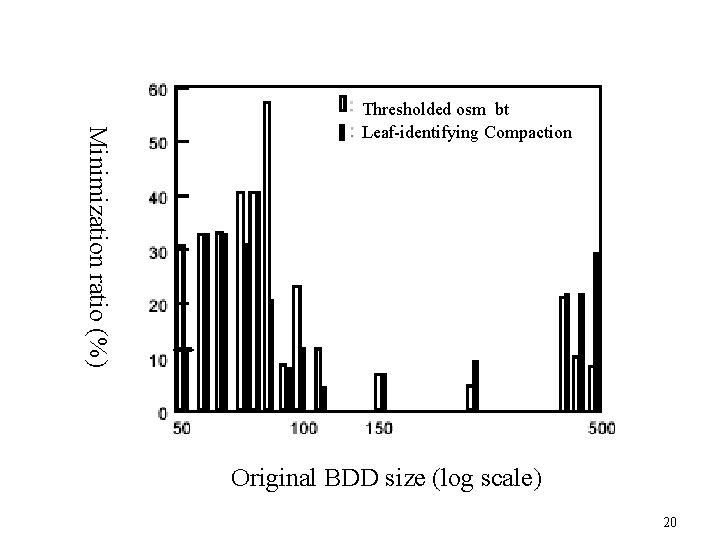

Minimization ratio (%) Thresholded osm_bt Leaf-identifying Compaction Original BDD size (log scale) 20

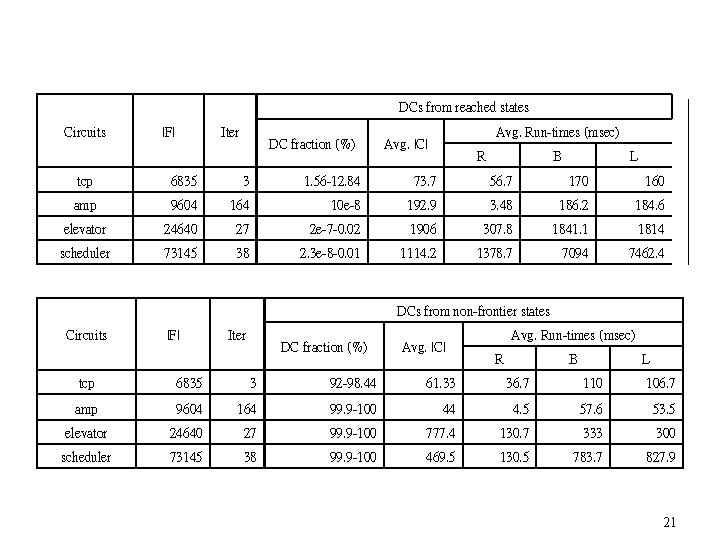

DCs from reached states Circuits |F| Iter DC fraction (%) Avg. Run-times (msec) Avg. |C| R B L tcp 6835 3 1. 56 -12. 84 73. 7 56. 7 170 160 amp 9604 164 10 e-8 192. 9 3. 48 186. 2 184. 6 elevator 24640 27 2 e-7 -0. 02 1906 307. 8 1841. 1 1814 scheduler 73145 38 2. 3 e-8 -0. 01 1114. 2 1378. 7 7094 7462. 4 DCs from non-frontier states Circuits |F| Iter DC fraction (%) Avg. |C| Avg. Run-times (msec) R B L tcp 6835 3 92 -98. 44 61. 33 36. 7 110 106. 7 amp 9604 164 99. 9 -100 44 4. 5 57. 6 53. 5 elevator 24640 27 99. 9 -100 777. 4 130. 7 333 300 scheduler 73145 38 99. 9 -100 469. 5 130. 5 783. 7 827. 9 21

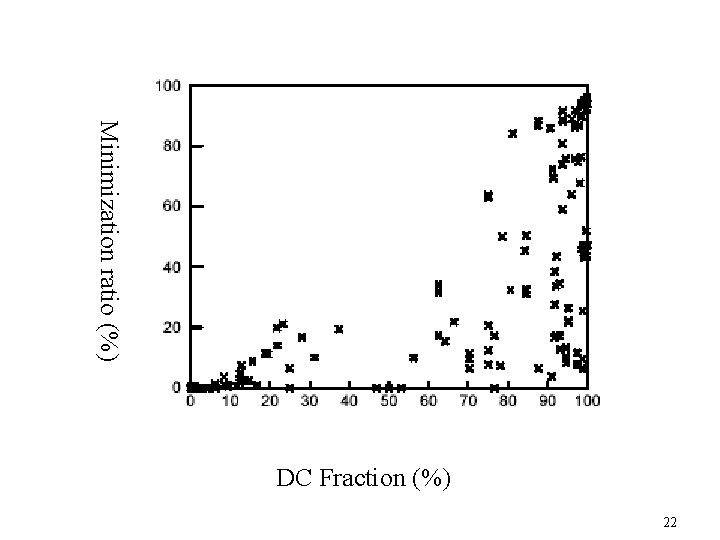

Minimization ratio (%) DC Fraction (%) 22

- Slides: 22