Realizing 3 D Smart Dust Particles Zeynep Dilli

![Photodiodes: Design Issues n n Photocurrent=Responsivity [A/W] x Incident Power Responsivity= Quantum efficiency x Photodiodes: Design Issues n n Photocurrent=Responsivity [A/W] x Incident Power Responsivity= Quantum efficiency x](https://slidetodoc.com/presentation_image_h2/ecef07f2420185881d3d26ca4de574d3/image-6.jpg)

- Slides: 16

Realizing 3 D Smart Dust Particles Zeynep Dilli

Introduction & Outline MIT Lincoln Laboratories FDSOI Process: Adapted to chip stacking n 3 D Run in April 2005 n Outline: n ¨ System Description ¨ Process information ¨ Photodiodes: Design and Layout ¨ Simulation Results ¨ Layouts

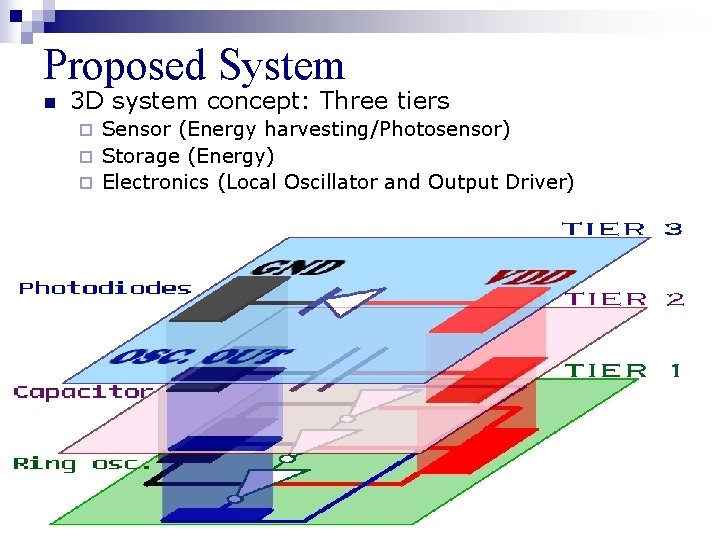

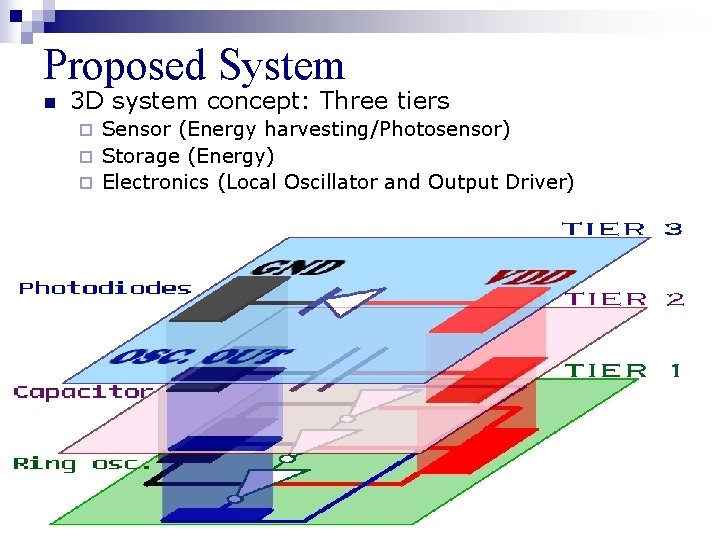

Proposed System n 3 D system concept: Three tiers Sensor (Energy harvesting/Photosensor) ¨ Storage (Energy) ¨ Electronics (Local Oscillator and Output Driver) ¨

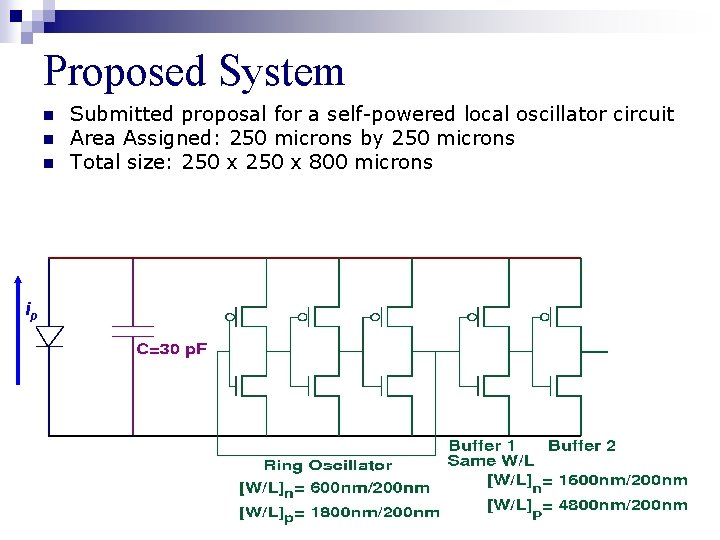

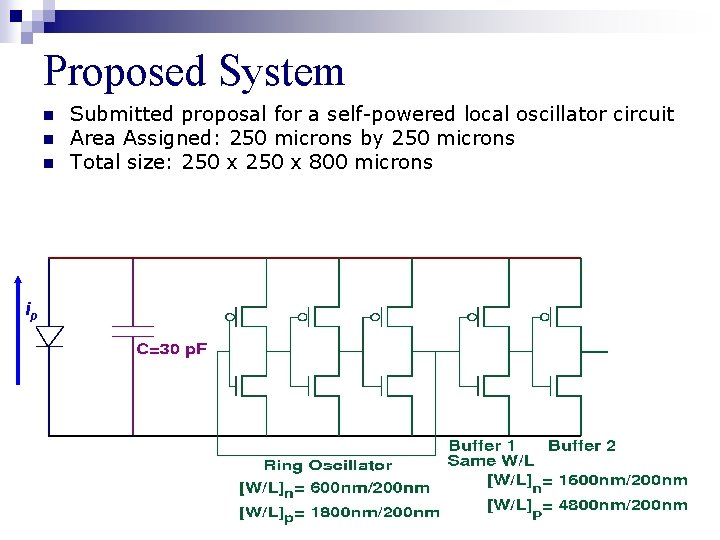

Proposed System n n n ip Submitted proposal for a self-powered local oscillator circuit Area Assigned: 250 microns by 250 microns Total size: 250 x 800 microns

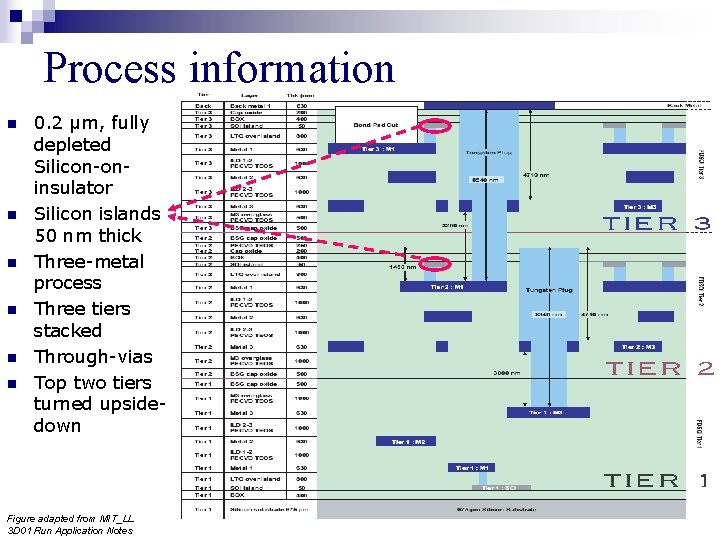

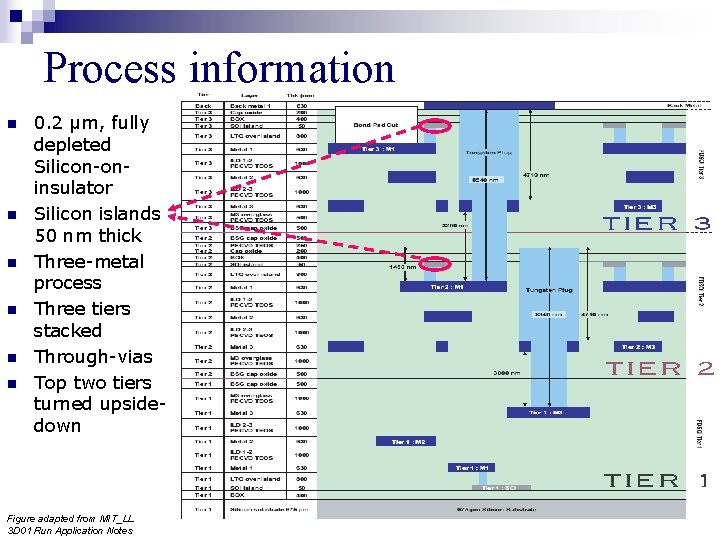

Process information n n n 0. 2 μm, fully depleted Silicon-oninsulator Silicon islands 50 nm thick Three-metal process Three tiers stacked Through-vias Top two tiers turned upsidedown Figure adapted from MIT_LL 3 D 01 Run Application Notes

![Photodiodes Design Issues n n PhotocurrentResponsivity AW x Incident Power Responsivity Quantum efficiency x Photodiodes: Design Issues n n Photocurrent=Responsivity [A/W] x Incident Power Responsivity= Quantum efficiency x](https://slidetodoc.com/presentation_image_h2/ecef07f2420185881d3d26ca4de574d3/image-6.jpg)

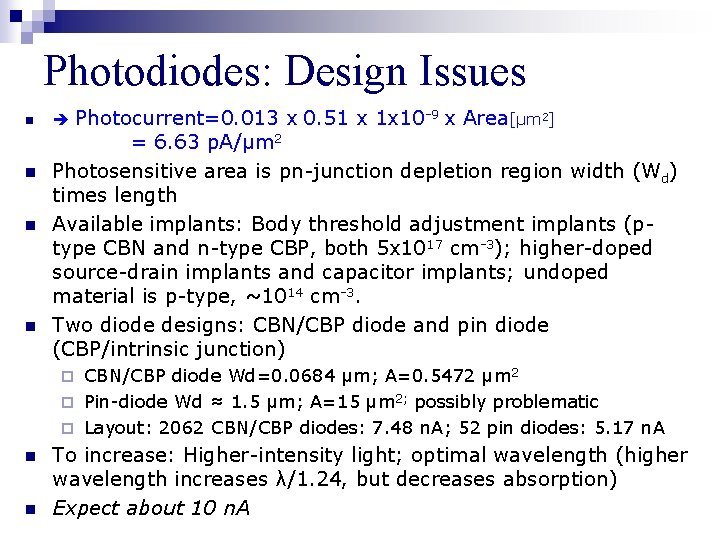

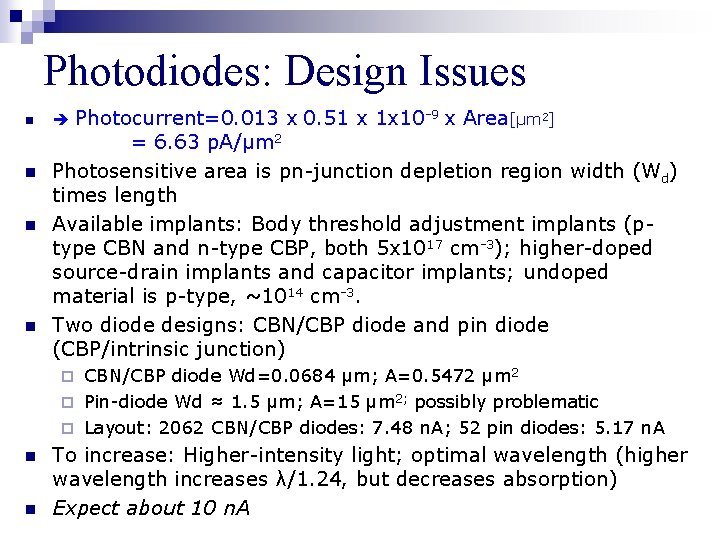

Photodiodes: Design Issues n n Photocurrent=Responsivity [A/W] x Incident Power Responsivity= Quantum efficiency x λ [μm] /1. 24 ¨ n [μm] /1. 24 = 0. 51 Incident Power = Intensity ¨ n For red light, λ [W/μm 2] x Area [μm 2] Sunlight intensity ≈ 1 x 10 -9 W/μm 2 Quantum Efficiency = [# electron-hole pairs]/ [# incident photons] Depends on reflectance, how many carrier pairs make it to the outer circuit, and absorption ¨ At 633 nm (red light), absorption coef. ≈3. 5 e-4 1/nm amount of photons absorbed in 50 nm depth is (1 -exp(-αd)) ≈ 0. 017 ¨ η = 0. 017 x reflectance x ratio of non-recombined pairs ≈ 0. 017 x 0. 75=0. 013 ¨ Photocurrent=0. 013 x 0. 51 x 1 x 10 -9 x Area[μm 2] = 6. 63 p. A/μm 2 n n Major problem: The material depth is very small

Photodiodes: Design Issues n n Photocurrent=0. 013 x 0. 51 x 1 x 10 -9 x Area[μm 2] = 6. 63 p. A/μm 2 Photosensitive area is pn-junction depletion region width (Wd) times length Available implants: Body threshold adjustment implants (ptype CBN and n-type CBP, both 5 x 1017 cm-3); higher-doped source-drain implants and capacitor implants; undoped material is p-type, ~1014 cm-3. Two diode designs: CBN/CBP diode and pin diode (CBP/intrinsic junction) CBN/CBP diode Wd=0. 0684 μm; A=0. 5472 μm 2 ¨ Pin-diode Wd ≈ 1. 5 μm; A=15 μm 2; possibly problematic ¨ Layout: 2062 CBN/CBP diodes: 7. 48 n. A; 52 pin diodes: 5. 17 n. A ¨ n n To increase: Higher-intensity light; optimal wavelength (higher wavelength increases λ/1. 24, but decreases absorption) Expect about 10 n. A

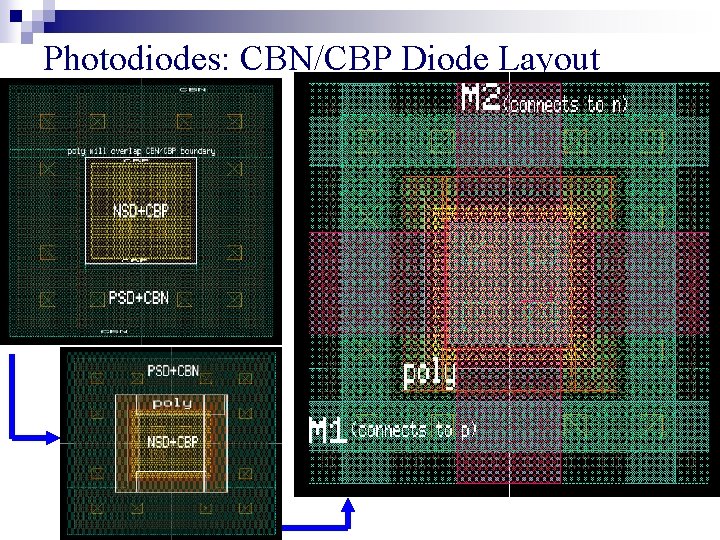

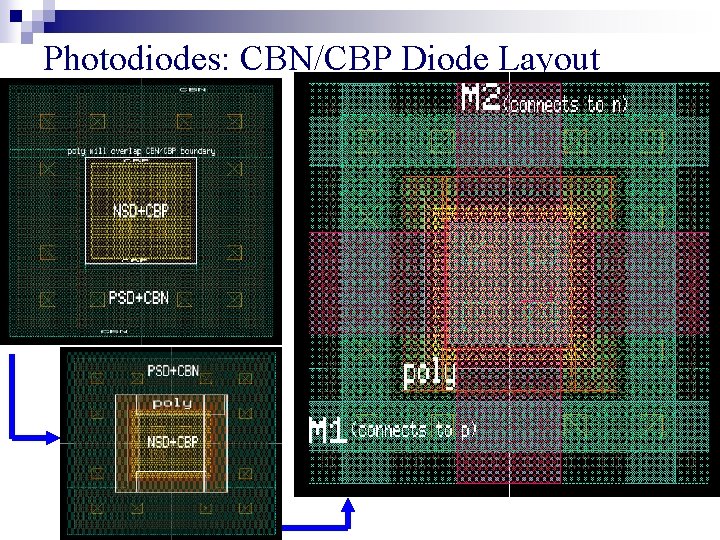

Photodiodes: CBN/CBP Diode Layout

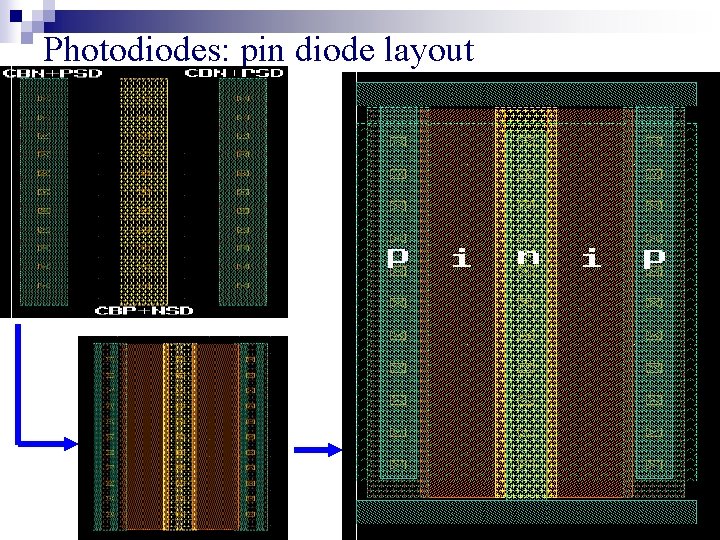

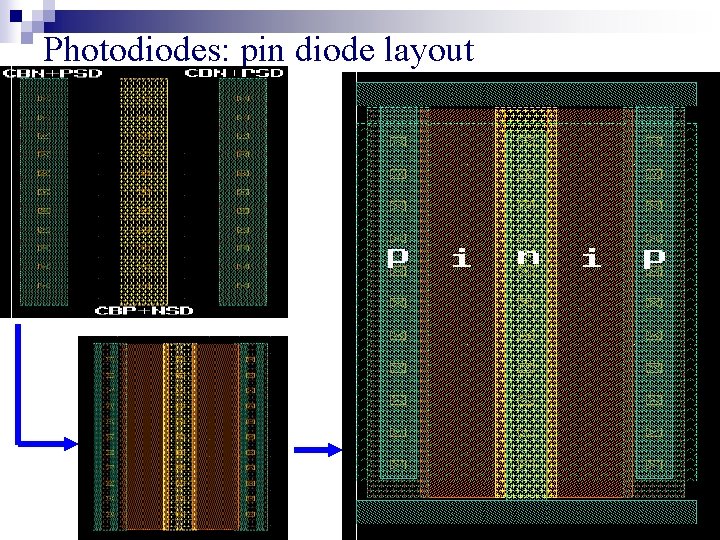

Photodiodes: pin diode layout

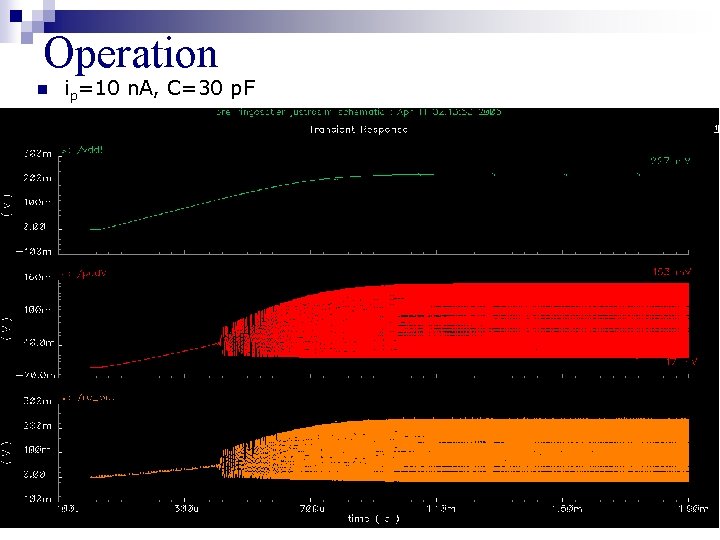

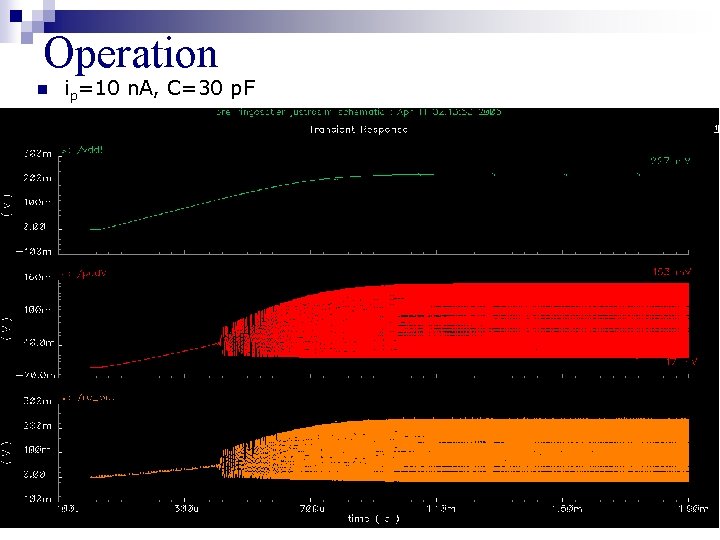

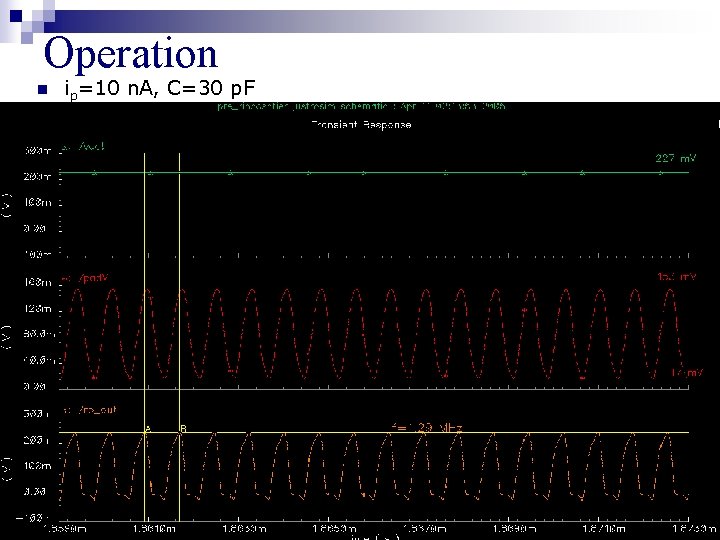

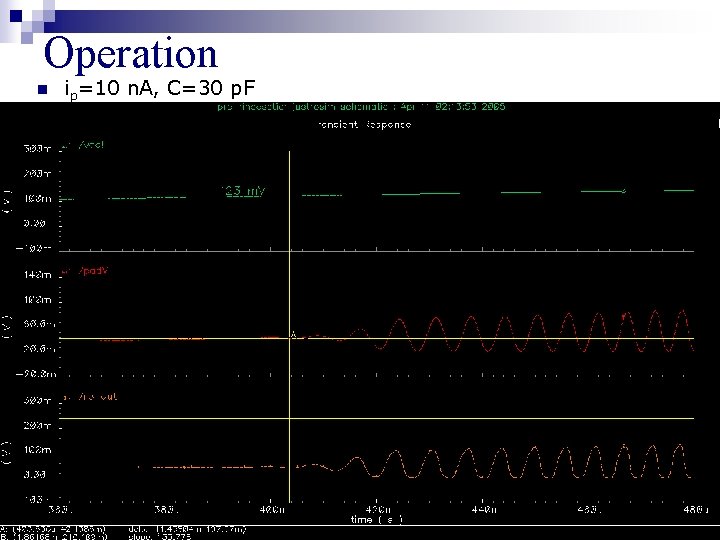

Operation n ip=10 n. A, C=30 p. F

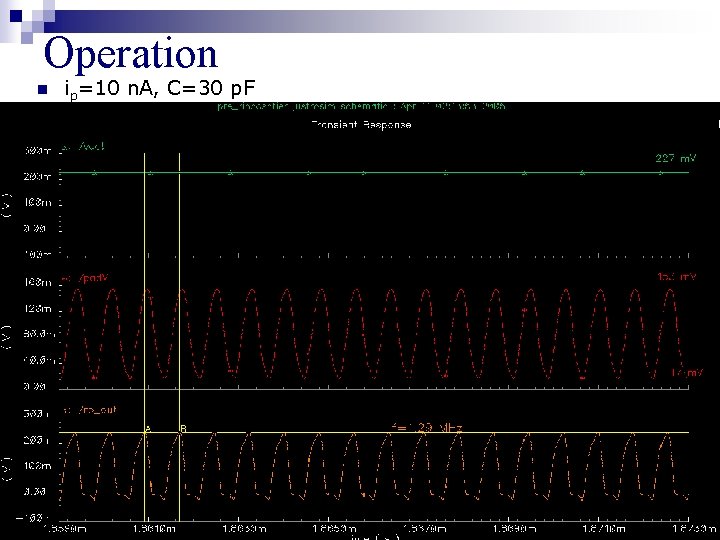

Operation n ip=10 n. A, C=30 p. F

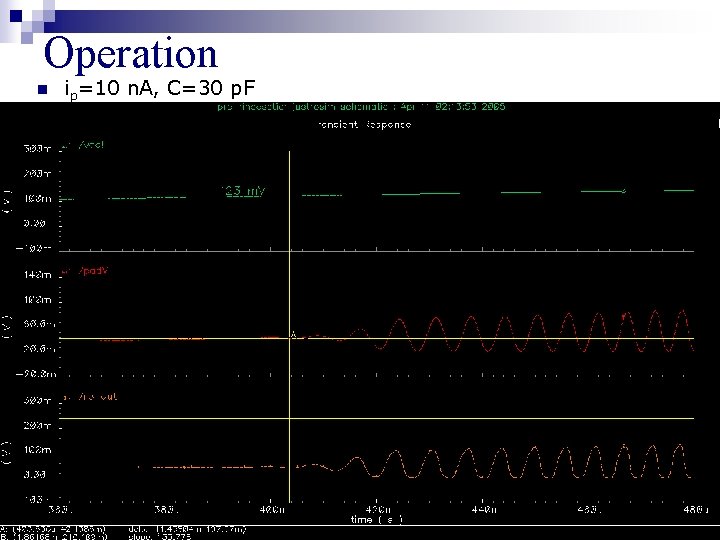

Operation n ip=10 n. A, C=30 p. F

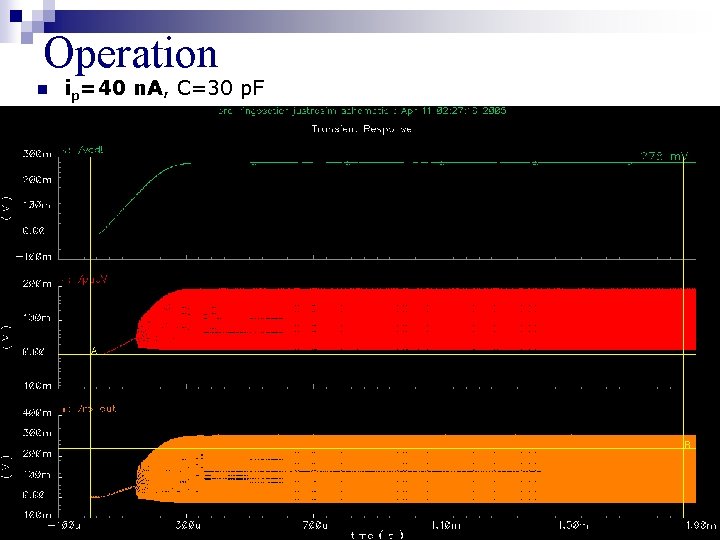

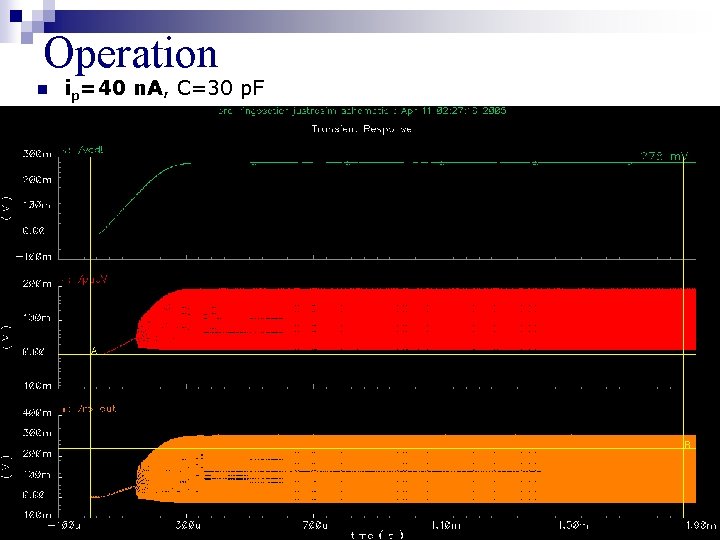

Operation n ip=40 n. A, C=30 p. F

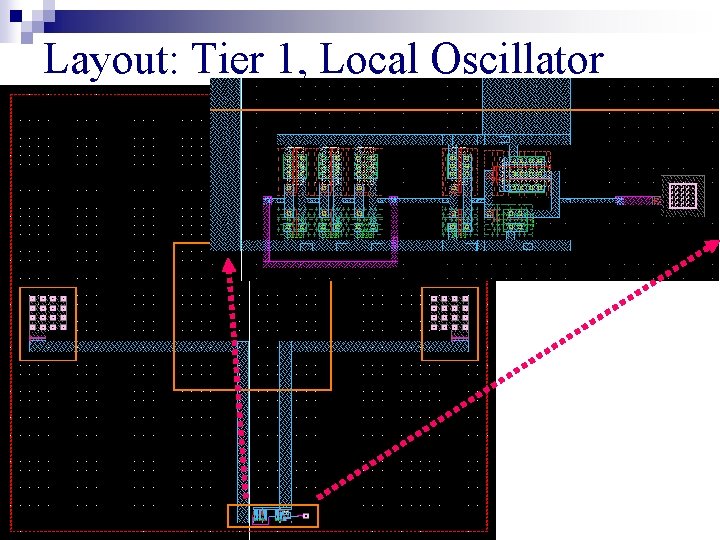

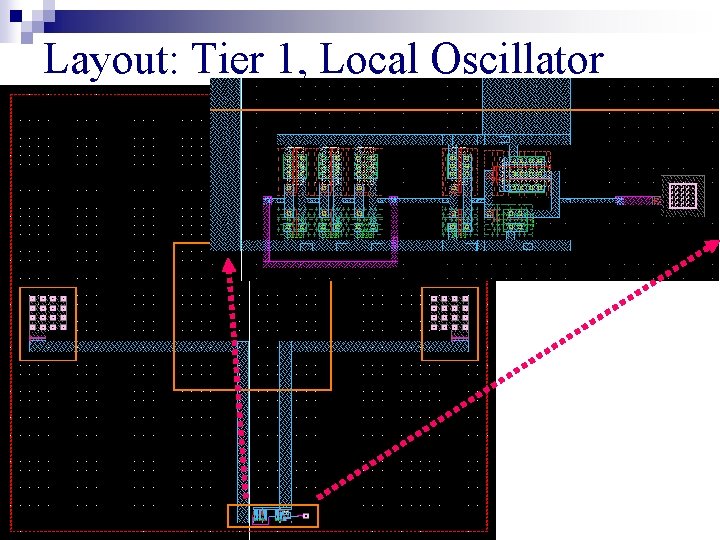

Layout: Tier 1, Local Oscillator

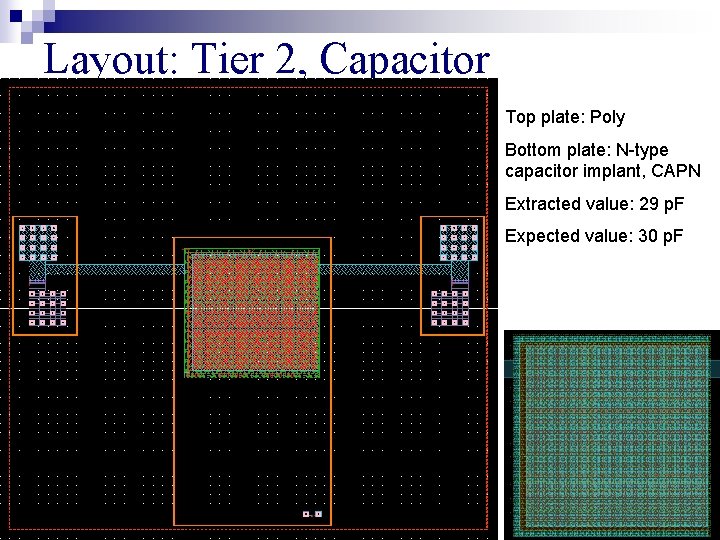

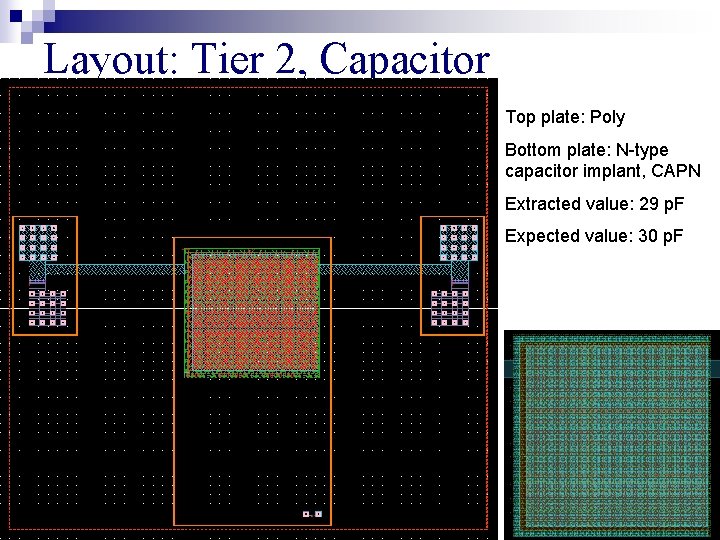

Layout: Tier 2, Capacitor Top plate: Poly Bottom plate: N-type capacitor implant, CAPN Extracted value: 29 p. F Expected value: 30 p. F

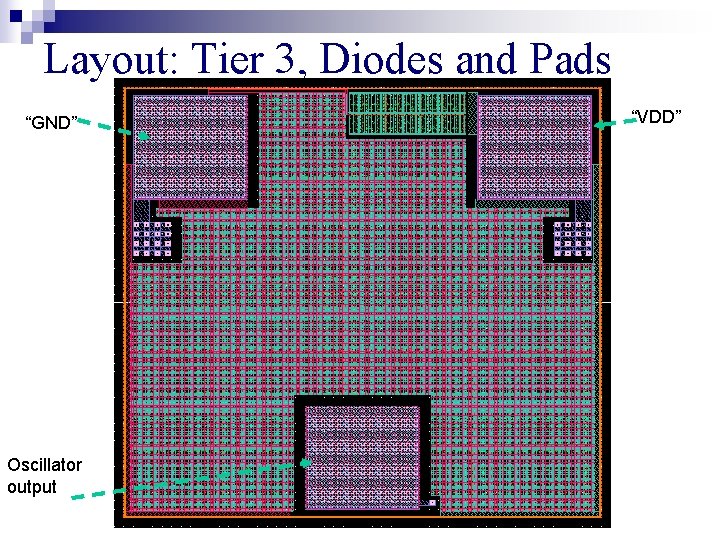

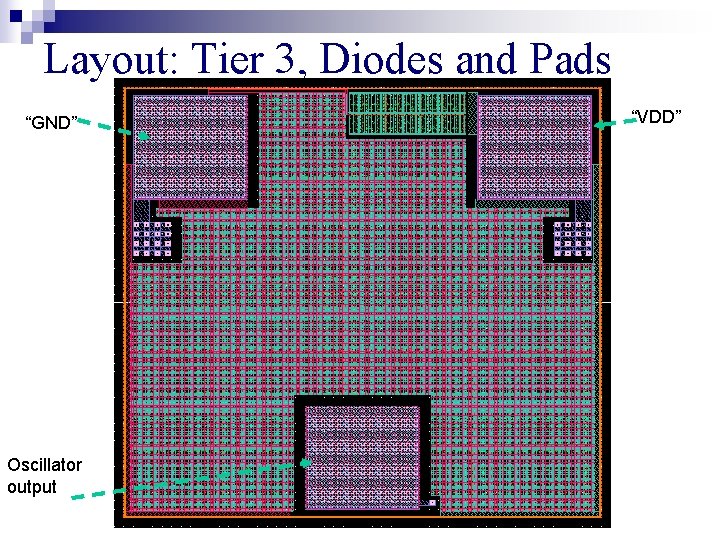

Layout: Tier 3, Diodes and Pads “GND” Oscillator output “VDD”