Proiectarea Microsistemelor Digitale Curs 6 1 Proiectarea Microsistemelor

- Slides: 26

Proiectarea Microsistemelor Digitale Curs 6 1

Proiectarea Microsistemelor Digitale 4. Conectarea porturilor de intrare/ ieşire n n Prin port de intrare/ ieşire sau, mai scurt, port, se înţelege un circuit, sau grup de circuite, care fac legătura între unitatea centrală a unui microsistem şi dispozitivele şi echipamentele periferice. Porturi + circuite de legătură între ele = interfaţă Există o gamă diversă de dipozitive şi echipamente periferice: led – uri, comutatoare, module de afişare cu segmente, module de afişare cu LCD, tastaturi, imprimante etc. Implementarea porturilor: q q Cu 1 sau puţine circuite: dacă UC se leagă la led – uri, comutatoare, module de afişare cu segmente, module de afişare cu LCD, tastaturi, bistabile cu funcţiuni speciale etc. Cu mai multe circuite, dacă UC se leagă la un echipament periferic, uneori nefăcându-se distincţia între port si interfaţă; ex. : microcalculatorul PC: porturile serial, paralel, USB; noţiunea de port este mai largă cuprinzând mai multe circuite, inclusiv un circuit specializat programabil sau o parte a unui circuit specializat programabil mai complex, precum şi elemente mecanice de conectare. 2

Proiectarea Microsistemelor Digitale 4. 1. Proiectarea unui decodificator de porturi n Similară proiectării unui decodificator de memorie; diferenţele care apar constau în: q q n Numărul de linii pe care apare adresa portului: la memorii adresele apar pe toată magistrala pe când la porturi adresele apar fie pe A 7 – 0 fie pe A 15 – 0; Semnalul de comandă care indică transferul cu porturile: fie este altul decât cel pentru transferurile cu memoria fie este acelaşi dar cealaltă valoare logică este cea activă. Exemplu: să se proiecteze decodificatorul corespunzător următoarei hărţi a porturilor: q q q P 1 cu adresa 20 H, P 2 cu adresa 21 H, P 3 cu adresa 30 H şi P 4 cu adresa 31 H; Porturile sunt pe 8 biţi, cu adrese pe 8 biţi. 3

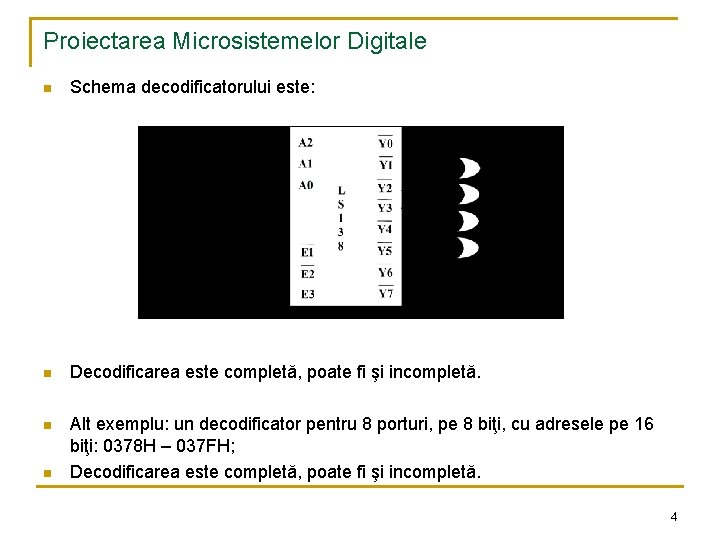

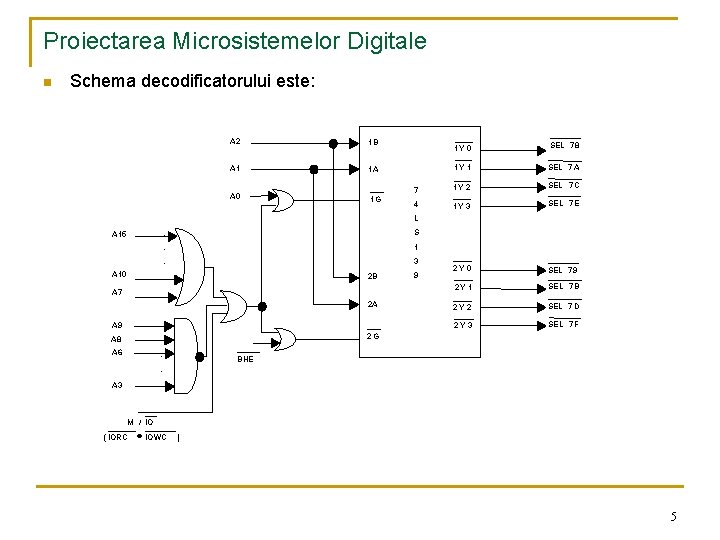

Proiectarea Microsistemelor Digitale n Schema decodificatorului este: n Decodificarea este completă, poate fi şi incompletă. n Alt exemplu: un decodificator pentru 8 porturi, pe 8 biţi, cu adresele pe 16 biţi: 0378 H – 037 FH; Decodificarea este completă, poate fi şi incompletă. n 4

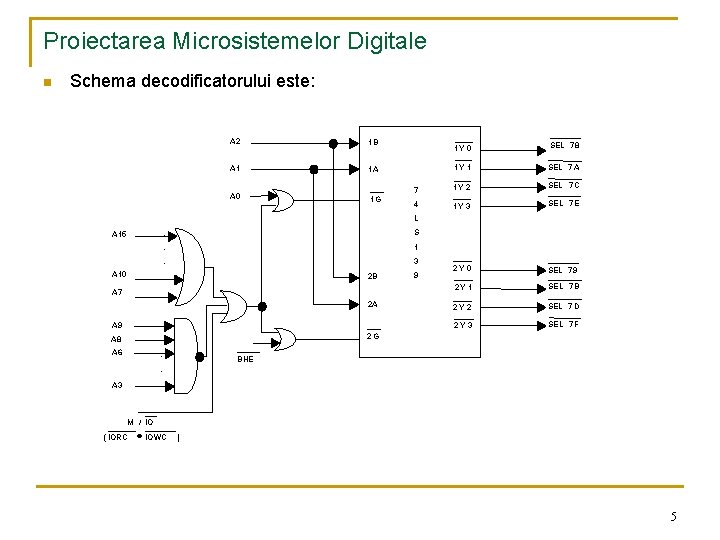

Proiectarea Microsistemelor Digitale n Schema decodificatorului este: A 2 1 B A 1 1 A A 0 1 G 1 Y 0 SEL 78 1 Y 1 SEL 7 A 7 1 Y 2 SEL 7 C 4 1 Y 3 SEL 7 E 2 Y 0 SEL 79 2 Y 1 SEL 7 B 2 Y 2 SEL 7 D 2 Y 3 SEL 7 F L A 15 . S . 1 . 3 A 10 2 B A 7 2 A A 9 9 2 G A 8 A 6 . BHE . A 3 M / IO ( IORC · IOWC ) 5

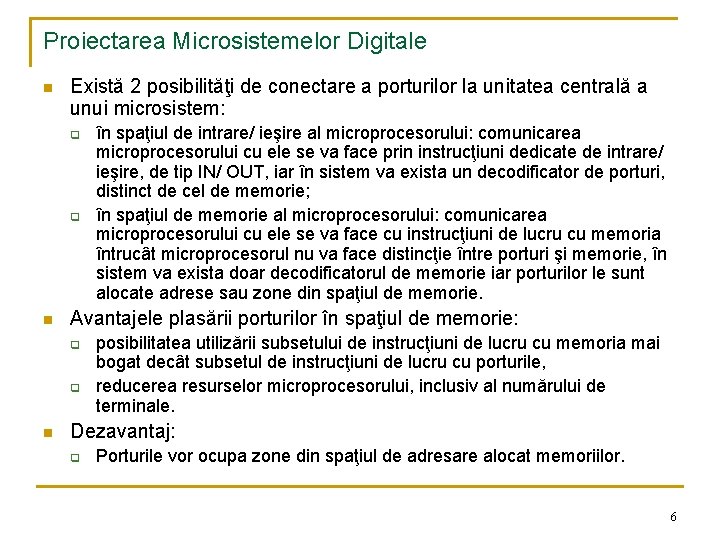

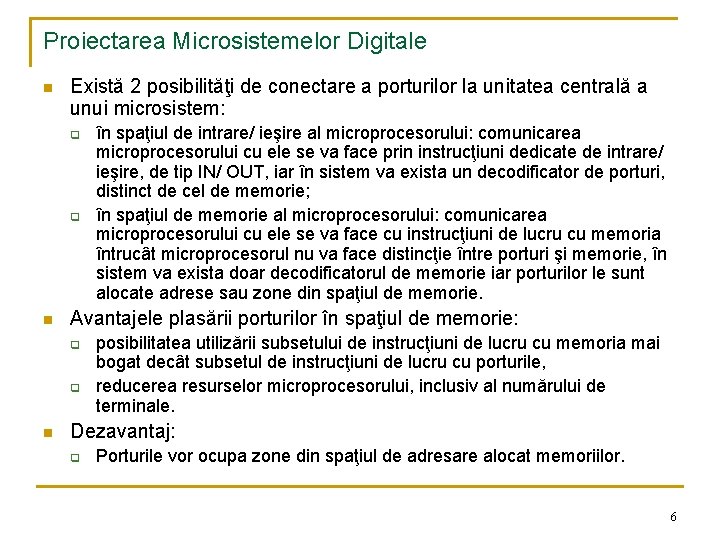

Proiectarea Microsistemelor Digitale n Există 2 posibilităţi de conectare a porturilor la unitatea centrală a unui microsistem: q q n Avantajele plasării porturilor în spaţiul de memorie: q q n în spaţiul de intrare/ ieşire al microprocesorului: comunicarea microprocesorului cu ele se va face prin instrucţiuni dedicate de intrare/ ieşire, de tip IN/ OUT, iar în sistem va exista un decodificator de porturi, distinct de cel de memorie; în spaţiul de memorie al microprocesorului: comunicarea microprocesorului cu ele se va face cu instrucţiuni de lucru cu memoria întrucât microprocesorul nu va face distincţie între porturi şi memorie, în sistem va exista doar decodificatorul de memorie iar porturilor le sunt alocate adrese sau zone din spaţiul de memorie. posibilitatea utilizării subsetului de instrucţiuni de lucru cu memoria mai bogat decât subsetul de instrucţiuni de lucru cu porturile, reducerea resurselor microprocesorului, inclusiv al numărului de terminale. Dezavantaj: q Porturile vor ocupa zone din spaţiul de adresare alocat memoriilor. 6

Proiectarea Microsistemelor Digitale 4. 2. Tipuri de porturi n Portul implementat cu porţi q q q Este folosită pentru porturile de intrare; Ieşirile porţilor se conectează la linii de date ale microprocesorului, ca urmare este necesar să aibă facilitatea de a 3 – a stare; Semnalele care se citesc se conectează la intrările de date ale porţilor; Intrările de validare ale porţilor sunt comandate de una sau mai multe ieşiri dintr - un decodificator de porturi; Semnalele care se citesc sunt generate din exterior şi se presupune că circuitul care le generează le şi memorează până când este necesar; în caz contrar sunt prevăzute bistabile; Citirea se face în timpul ciclului de intrare. 7

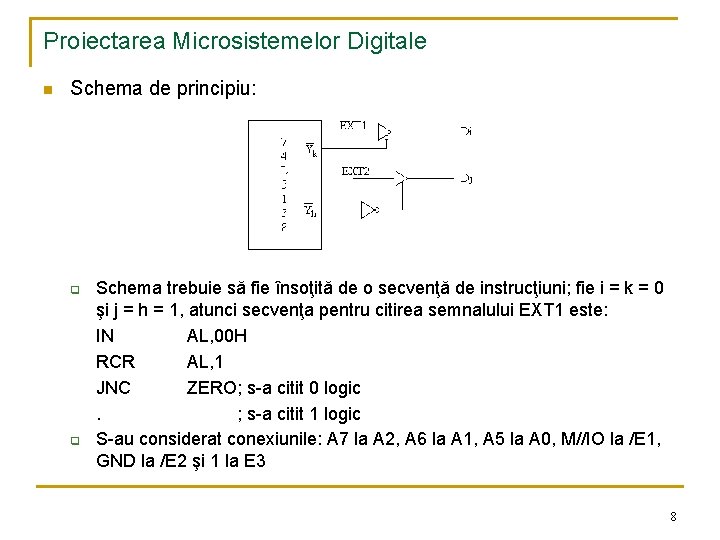

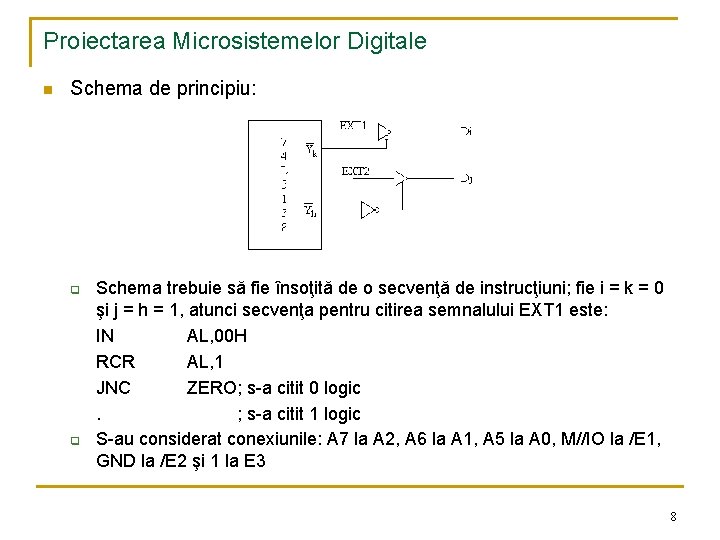

Proiectarea Microsistemelor Digitale n Schema de principiu: q q Schema trebuie să fie însoţită de o secvenţă de instrucţiuni; fie i = k = 0 şi j = h = 1, atunci secvenţa pentru citirea semnalului EXT 1 este: IN AL, 00 H RCR AL, 1 JNC ZERO; s-a citit 0 logic. ; s-a citit 1 logic S-au considerat conexiunile: A 7 la A 2, A 6 la A 1, A 5 la A 0, M//IO la /E 1, GND la /E 2 şi 1 la E 3 8

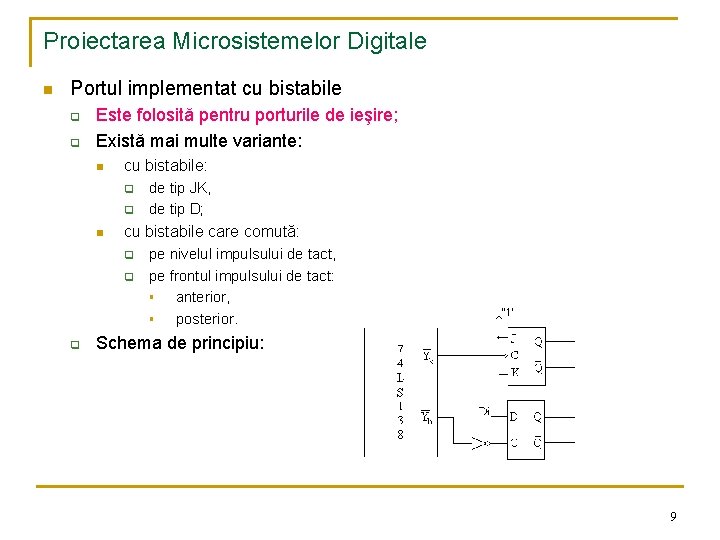

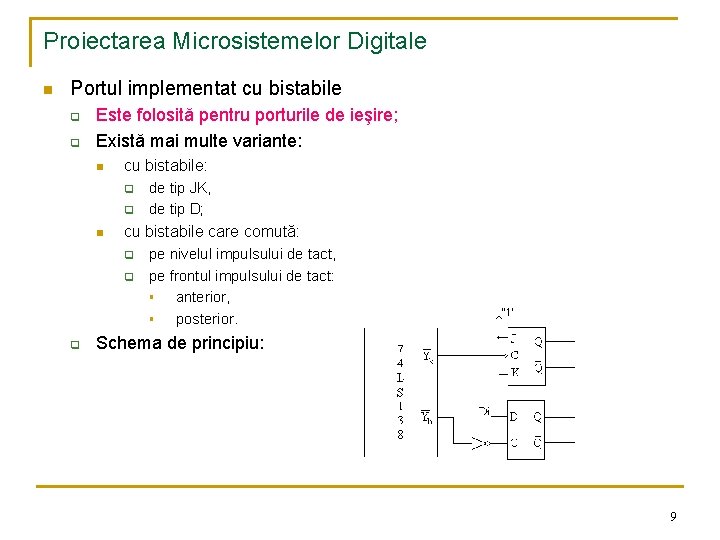

Proiectarea Microsistemelor Digitale n Portul implementat cu bistabile q q Este folosită pentru porturile de ieşire; Există mai multe variante: n cu bistabile: q q n cu bistabile care comută: q q q de tip JK, de tip D; pe nivelul impulsului de tact, pe frontul impulsului de tact: § anterior, § posterior. Schema de principiu: 9

Proiectarea Microsistemelor Digitale n Fie k = 0, h = 1 şi i = 7: q q q pentru modificarea ieşirii bistabilului de tip JK este suficientă execuţia instrucţiunii OUT 00 H, AL şi bistabilul va trece în starea complementară celeia în care a fost; utilizarea acestei soluţii are dezavantajul că trebuie cunoscută starea prezentă a bistabilului înainte de a lansa în execuţie instrucţiunea care îi modifică starea; Ieşirea bistabilului de tip D poate fi comandată fără a fi necesară cunoaşterea stării prezente întrucât are intrare de date; Următoarea secvenţă provoacă trecerea bistabilului în starea 1: MOV AL, 80 H OUT 20 H, AL Următoarea secvenţă provoacă trecerea bistabilului în starea 0: MOV AL, 00 H OUT 20 H, AL Modificarea stării bistabilelor se face în timpul ciclului de ieşire. 10

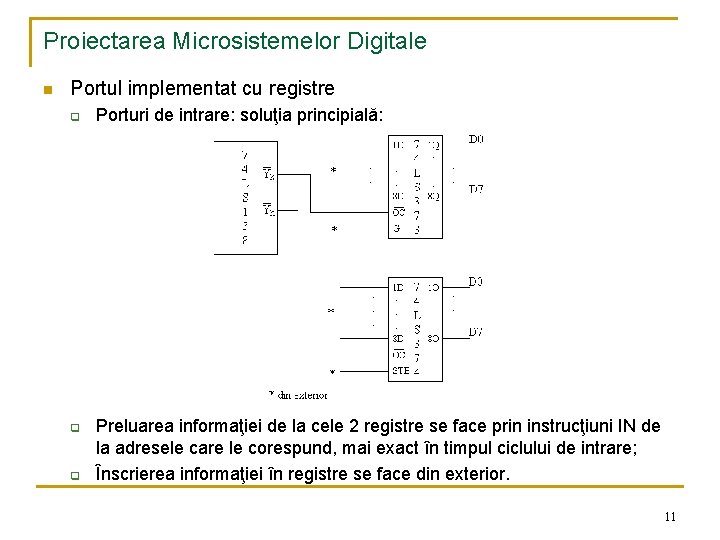

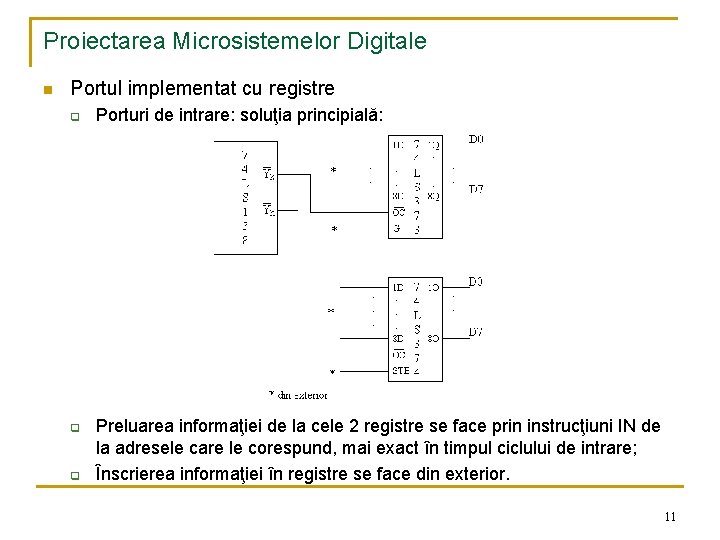

Proiectarea Microsistemelor Digitale n Portul implementat cu registre q q q Porturi de intrare: soluţia principială: Preluarea informaţiei de la cele 2 registre se face prin instrucţiuni IN de la adresele care le corespund, mai exact în timpul ciclului de intrare; Înscrierea informaţiei în registre se face din exterior. 11

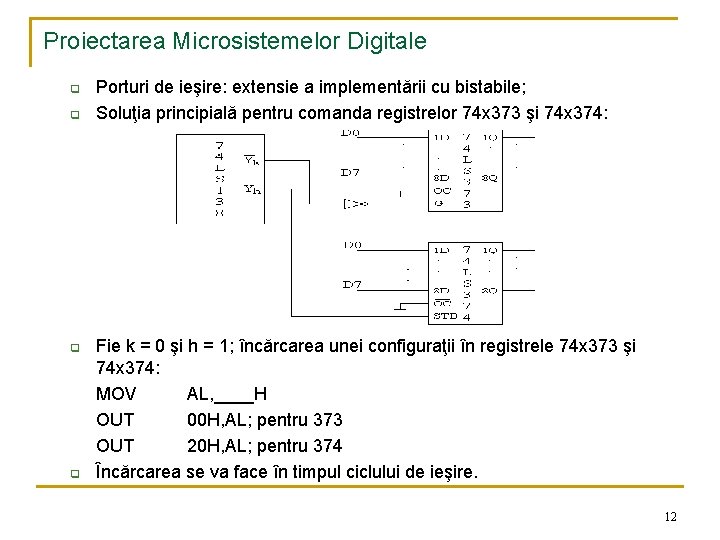

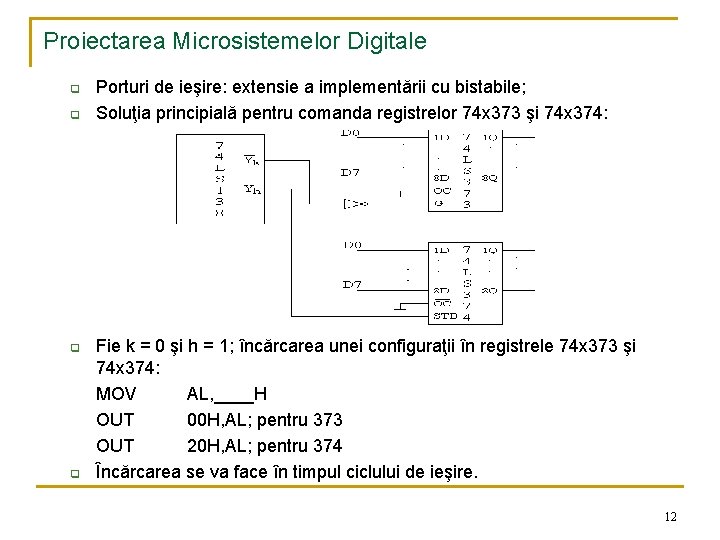

Proiectarea Microsistemelor Digitale q q Porturi de ieşire: extensie a implementării cu bistabile; Soluţia principială pentru comanda registrelor 74 x 373 şi 74 x 374: Fie k = 0 şi h = 1; încărcarea unei configuraţii în registrele 74 x 373 şi 74 x 374: MOV AL, ____H OUT 00 H, AL; pentru 373 OUT 20 H, AL; pentru 374 Încărcarea se va face în timpul ciclului de ieşire. 12

Proiectarea Microsistemelor Digitale n n Trebuie remarcat că, în toate exemplele prezentate, adresele de port s-au obţinut prin decodificare incompletă; Ca urmare pot fi utilizate şi alte valori pentru adresele de port 00 H şi 20 H, cu condiţia îndeplinirii următoarelor condiţii: q q A 7 = A 6 = A 5 = 0 pentru 00 H şi A 7 = A 6 = 0 şi A 5 = 1 pentru 20 H. 13

Proiectarea Microsistemelor Digitale n Portul implementat cu circuite specializate q q Există circuite programabile, specializate pe diferite tipuri de aplicaţii, de exemplu interfaţă serială, interfaţă paralelă etc. Datorită complexităţii sale, un asemenea circuit este comandat de microprocesor ca un grup de porturi ale căror adrese au un câmp comun şi un câmp variabil. Câmpul comun corespunde unei conexiuni făcute între o ieşire din decodificatorul de porturi şi intrarea de selecţie a circuitului specializat iar câmpul variabil corespunde legăturilor făcute între linii mai puţin semnificative din magistrala de adrese şi intrări specifice ale circuitului specializat. Circuitele specializate programabile, inclusiv toate problemele legate de conectarea lor la o unitate centrală cu microprocesorul 8086, vor fi prezentate pe larg în capitolele următoare. 14

Proiectarea Microsistemelor Digitale 4. 3. Comanda unui semnal prin program n Semnifică: q Citirea unui semnal din exteriorul microsistemului: soluţia este cea prezentată la citirea unui semnal prin intermediul unui port implementat cu o poartă: n n q Semnalul este legat la intrarea de date a unei porţi cu 3 stări; Intrarea de validare a porţii este comandată de o ieşire a unui decodificator de porturi; Ieşirea porţii este legată la o linie a magistralei de date a unităţii centrale; Citirea se face cu o instrucţiune IN şi apoi se face ramificarea. Poziţionarea unui semnal la 1 sau 0 logic: soluţia este cea prezentată la implementarea unui port cu un bistabil: n n Valoarea semnalului este transmisă la intrarea de date a unui bistabil prin intermediul unei linii a magistralei de date; Tactul bistabilului este comandat de o ieşire a unui decodificator de porturi; Iesirea bistabilului este semnalul care trebuie comandat; Poziţionarea semnalului se face cu o instrucţiune OUT. 15

Proiectarea Microsistemelor Digitale 4. 4. Aplicaţii 4. 4. 1. Extinderea spaţiului de memorie al unui microprocesor q q Prin suprapunerea mai multor blocuri fizice de memorie în aceeaşi zonă a spaţiului de adrese; Intrarea de selecţie a fiecărui bloc de memorie va avea 2 componente: n n q O componentă care rezultă din zona ocupată; este dată de o ieşire a decodificatorului de memorii, comună tuturor blocurilor; O componentă obţinută din ieşirea unui circuit comandat ca port: doar unul din aceste circuite va fi activ la un moment dat; prin program poate fi activat circuitul activ. 2 soluţii: n n Cu bistabile: fiecare bloc va fi comandat de 1 bistabil; pentru n blocuri sunt necesare n bistabile; Cu bistabile şi decodificator: pentru n blocuri sunt necesare log 2 n bistabile + decodificator. 16

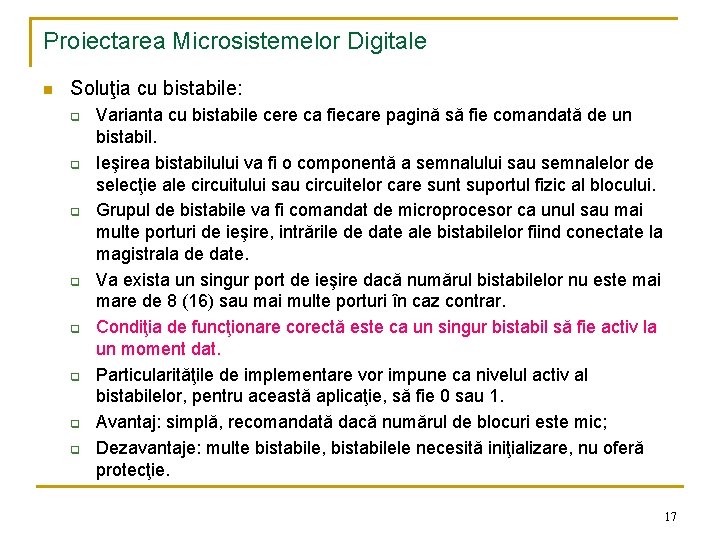

Proiectarea Microsistemelor Digitale n Soluţia cu bistabile: q q q q Varianta cu bistabile cere ca fiecare pagină să fie comandată de un bistabil. Ieşirea bistabilului va fi o componentă a semnalului sau semnalelor de selecţie ale circuitului sau circuitelor care sunt suportul fizic al blocului. Grupul de bistabile va fi comandat de microprocesor ca unul sau mai multe porturi de ieşire, intrările de date ale bistabilelor fiind conectate la magistrala de date. Va exista un singur port de ieşire dacă numărul bistabilelor nu este mai mare de 8 (16) sau mai multe porturi în caz contrar. Condiţia de funcţionare corectă este ca un singur bistabil să fie activ la un moment dat. Particularităţile de implementare vor impune ca nivelul activ al bistabilelor, pentru această aplicaţie, să fie 0 sau 1. Avantaj: simplă, recomandată dacă numărul de blocuri este mic; Dezavantaje: multe bistabile, bistabilele necesită iniţializare, nu oferă protecţie. 17

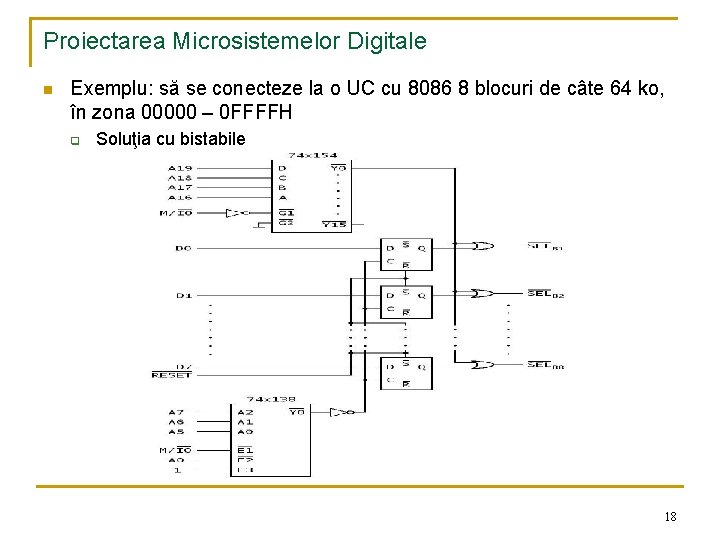

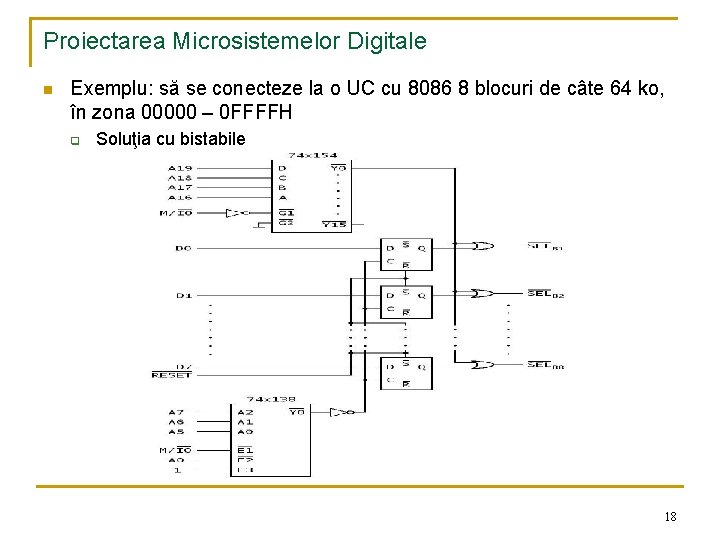

Proiectarea Microsistemelor Digitale n Exemplu: să se conecteze la o UC cu 8086 8 blocuri de câte 64 ko, în zona 00000 – 0 FFFFH q Soluţia cu bistabile 18

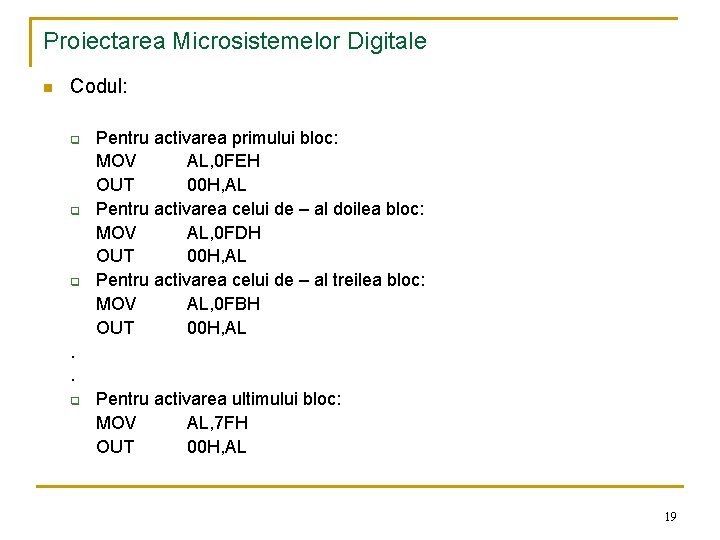

Proiectarea Microsistemelor Digitale n Codul: q q q Pentru activarea primului bloc: MOV AL, 0 FEH OUT 00 H, AL Pentru activarea celui de – al doilea bloc: MOV AL, 0 FDH OUT 00 H, AL Pentru activarea celui de – al treilea bloc: MOV AL, 0 FBH OUT 00 H, AL . . q Pentru activarea ultimului bloc: MOV AL, 7 FH OUT 00 H, AL 19

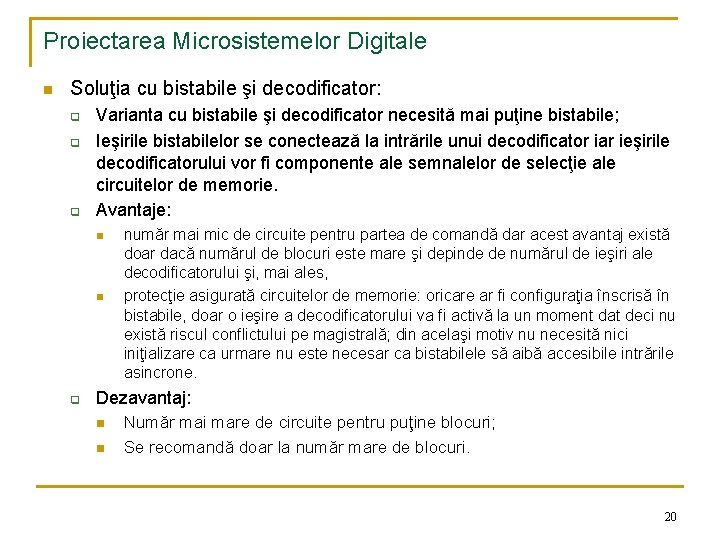

Proiectarea Microsistemelor Digitale n Soluţia cu bistabile şi decodificator: q q q Varianta cu bistabile şi decodificator necesită mai puţine bistabile; Ieşirile bistabilelor se conectează la intrările unui decodificator iar ieşirile decodificatorului vor fi componente ale semnalelor de selecţie ale circuitelor de memorie. Avantaje: n n q număr mai mic de circuite pentru partea de comandă dar acest avantaj există doar dacă numărul de blocuri este mare şi depinde de numărul de ieşiri ale decodificatorului şi, mai ales, protecţie asigurată circuitelor de memorie: oricare ar fi configuraţia înscrisă în bistabile, doar o ieşire a decodificatorului va fi activă la un moment dat deci nu există riscul conflictului pe magistrală; din acelaşi motiv nu necesită nici iniţializare ca urmare nu este necesar ca bistabilele să aibă accesibile intrările asincrone. Dezavantaj: n n Număr mai mare de circuite pentru puţine blocuri; Se recomandă doar la număr mare de blocuri. 20

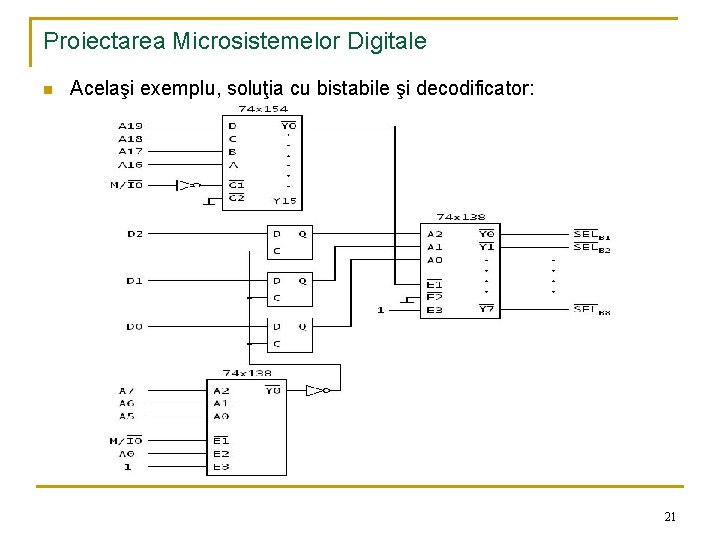

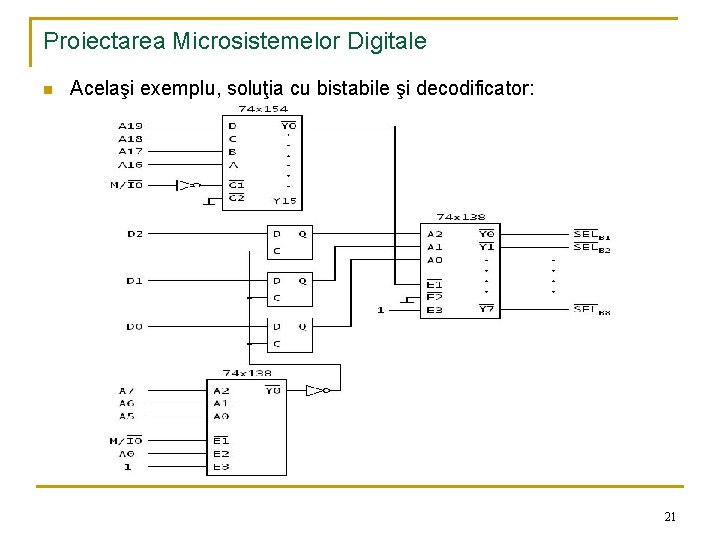

Proiectarea Microsistemelor Digitale n Acelaşi exemplu, soluţia cu bistabile şi decodificator: 21

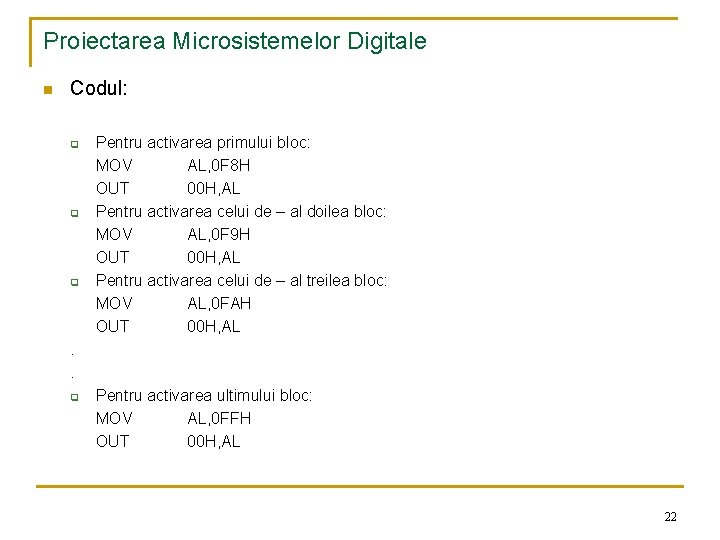

Proiectarea Microsistemelor Digitale n Codul: q q q Pentru activarea primului bloc: MOV AL, 0 F 8 H OUT 00 H, AL Pentru activarea celui de – al doilea bloc: MOV AL, 0 F 9 H OUT 00 H, AL Pentru activarea celui de – al treilea bloc: MOV AL, 0 FAH OUT 00 H, AL . . q Pentru activarea ultimului bloc: MOV AL, 0 FFH OUT 00 H, AL 22

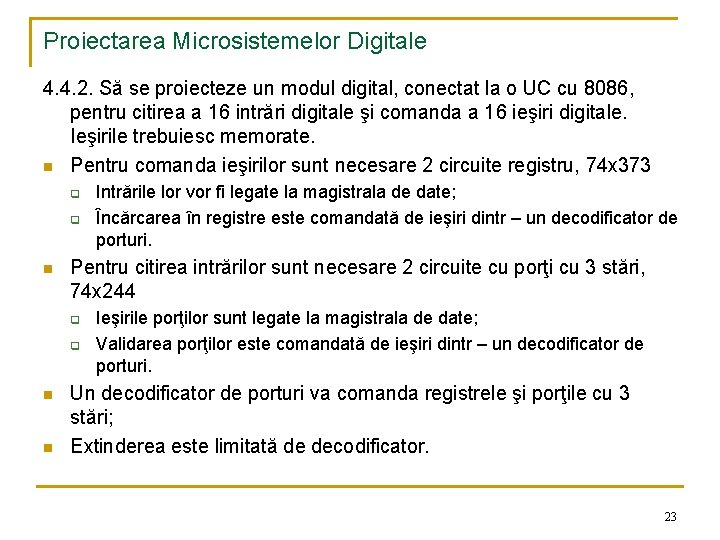

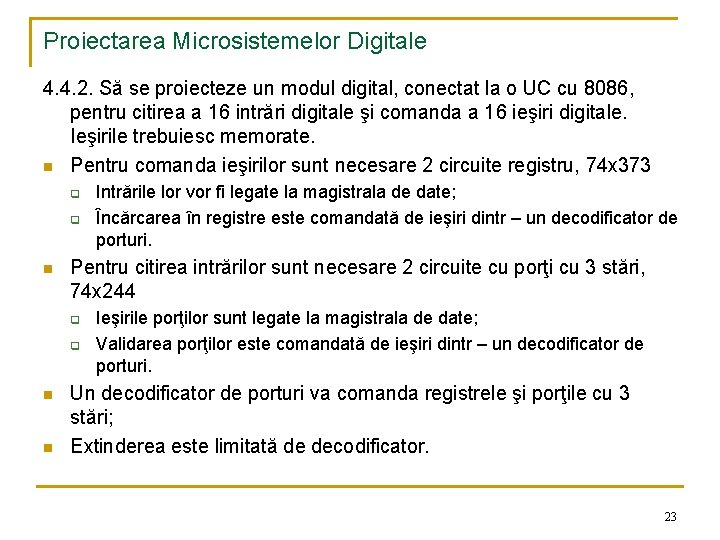

Proiectarea Microsistemelor Digitale 4. 4. 2. Să se proiecteze un modul digital, conectat la o UC cu 8086, pentru citirea a 16 intrări digitale şi comanda a 16 ieşiri digitale. Ieşirile trebuiesc memorate. n Pentru comanda ieşirilor sunt necesare 2 circuite registru, 74 x 373 q q n Pentru citirea intrărilor sunt necesare 2 circuite cu porţi cu 3 stări, 74 x 244 q q n n Intrările lor vor fi legate la magistrala de date; Încărcarea în registre este comandată de ieşiri dintr – un decodificator de porturi. Ieşirile porţilor sunt legate la magistrala de date; Validarea porţilor este comandată de ieşiri dintr – un decodificator de porturi. Un decodificator de porturi va comanda registrele şi porţile cu 3 stări; Extinderea este limitată de decodificator. 23

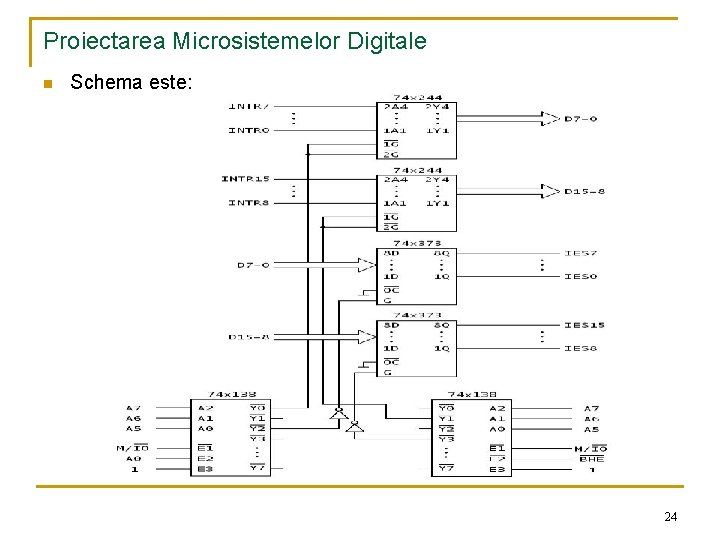

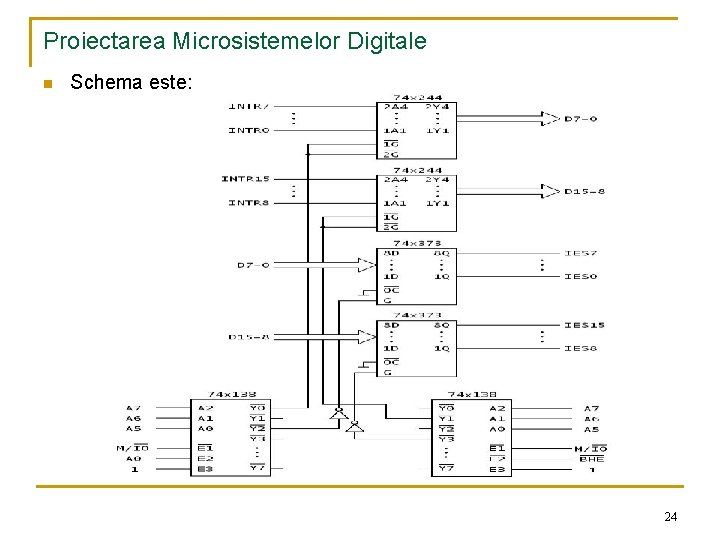

Proiectarea Microsistemelor Digitale n Schema este: 24

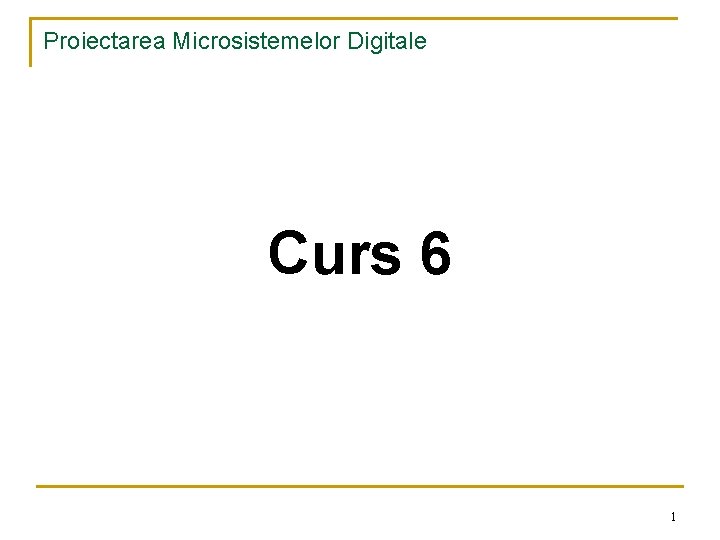

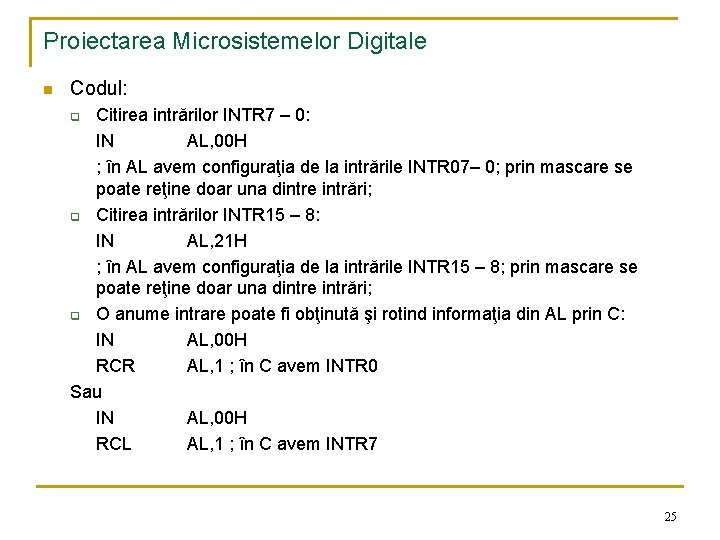

Proiectarea Microsistemelor Digitale n Codul: Citirea intrărilor INTR 7 – 0: IN AL, 00 H ; în AL avem configuraţia de la intrările INTR 07– 0; prin mascare se poate reţine doar una dintre intrări; q Citirea intrărilor INTR 15 – 8: IN AL, 21 H ; în AL avem configuraţia de la intrările INTR 15 – 8; prin mascare se poate reţine doar una dintre intrări; q O anume intrare poate fi obţinută şi rotind informaţia din AL prin C: IN AL, 00 H RCR AL, 1 ; în C avem INTR 0 Sau IN AL, 00 H RCL AL, 1 ; în C avem INTR 7 q 25

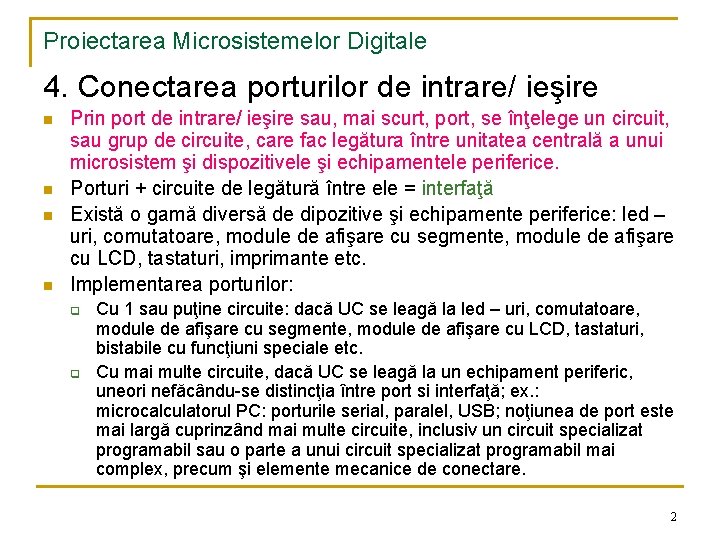

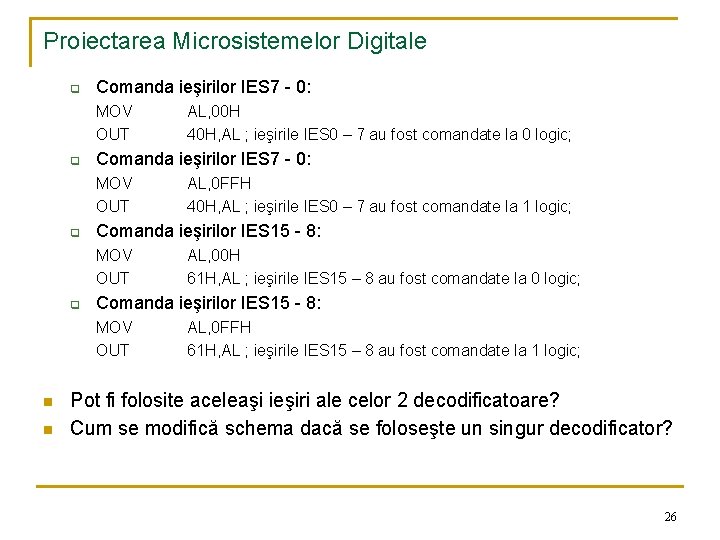

Proiectarea Microsistemelor Digitale q Comanda ieşirilor IES 7 - 0: MOV OUT q n AL, 00 H 61 H, AL ; ieşirile IES 15 – 8 au fost comandate la 0 logic; Comanda ieşirilor IES 15 - 8: MOV OUT n AL, 0 FFH 40 H, AL ; ieşirile IES 0 – 7 au fost comandate la 1 logic; Comanda ieşirilor IES 15 - 8: MOV OUT q AL, 00 H 40 H, AL ; ieşirile IES 0 – 7 au fost comandate la 0 logic; AL, 0 FFH 61 H, AL ; ieşirile IES 15 – 8 au fost comandate la 1 logic; Pot fi folosite aceleaşi ieşiri ale celor 2 decodificatoare? Cum se modifică schema dacă se foloseşte un singur decodificator? 26