Presentation 3 Smart Cart 525 Idongesit Ebong 1

Presentation #3: Smart Cart 525 Idongesit Ebong (1 -1) Jenna Fu (1 -2) Bowei Gai (1 -3) Syed Hussain (1 -4) Jonathan Lee (1 -5) Design Manager: Myron Kwai Stage III: 2 Feb. 2005 Size estimates/floorplan Overall Project Objective: Design a chip as part of a system that accommodates the growing demand for radio frequency identification (RFID) technology while creating a quicker, more convenient shopping experience.

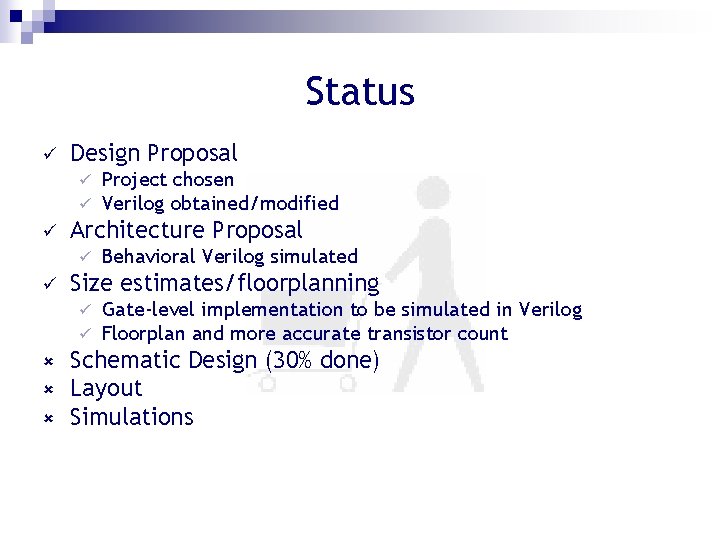

Status ü Design Proposal ü ü ü Architecture Proposal ü ü û û Behavioral Verilog simulated Size estimates/floorplanning ü ü û Project chosen Verilog obtained/modified Gate-level implementation to be simulated in Verilog Floorplan and more accurate transistor count Schematic Design (30% done) Layout Simulations

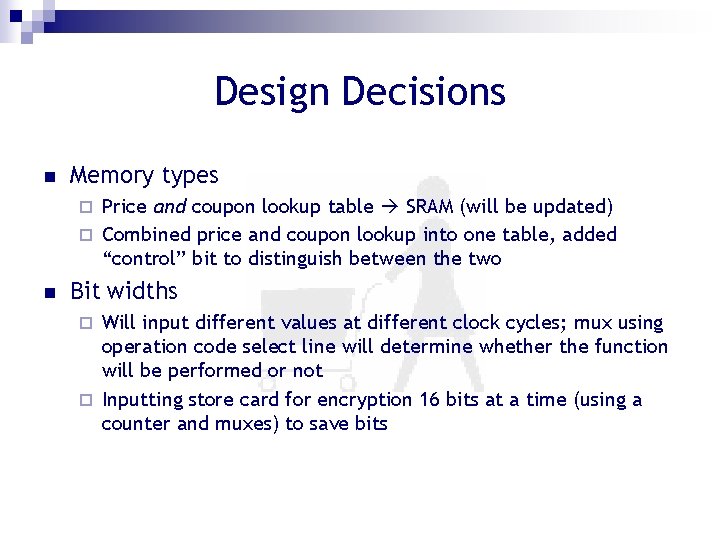

Design Decisions n Memory types Price and coupon lookup table SRAM (will be updated) ¨ Combined price and coupon lookup into one table, added “control” bit to distinguish between the two ¨ n Bit widths Will input different values at different clock cycles; mux using operation code select line will determine whether the function will be performed or not ¨ Inputting store card for encryption 16 bits at a time (using a counter and muxes) to save bits ¨

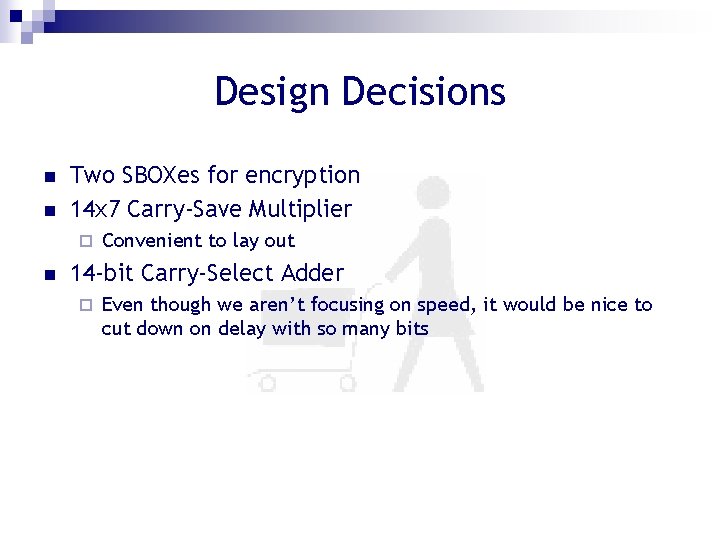

Design Decisions n n Two SBOXes for encryption 14 x 7 Carry-Save Multiplier ¨ n Convenient to lay out 14 -bit Carry-Select Adder ¨ Even though we aren’t focusing on speed, it would be nice to cut down on delay with so many bits

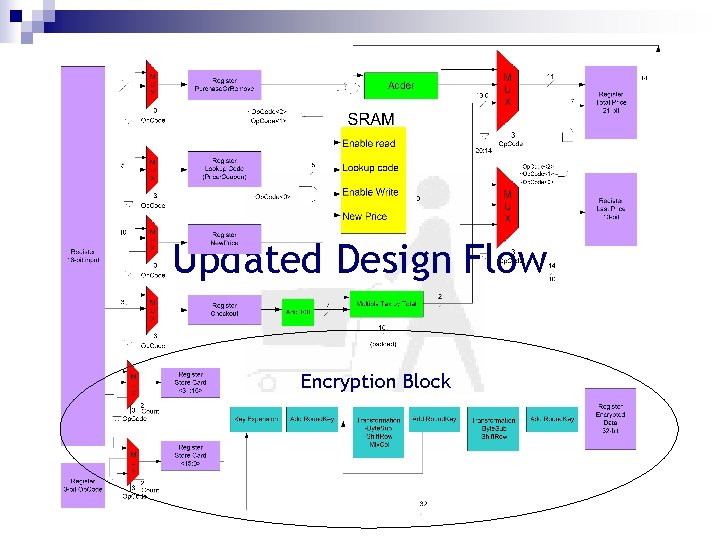

Updated Design Flow Encryption Block

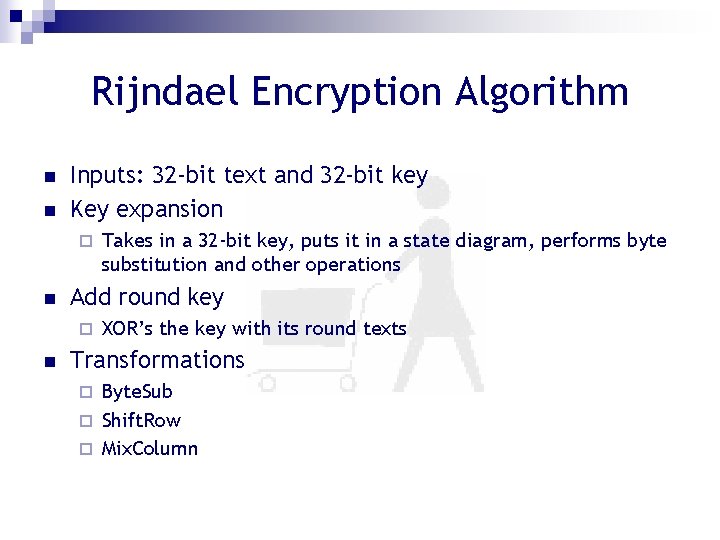

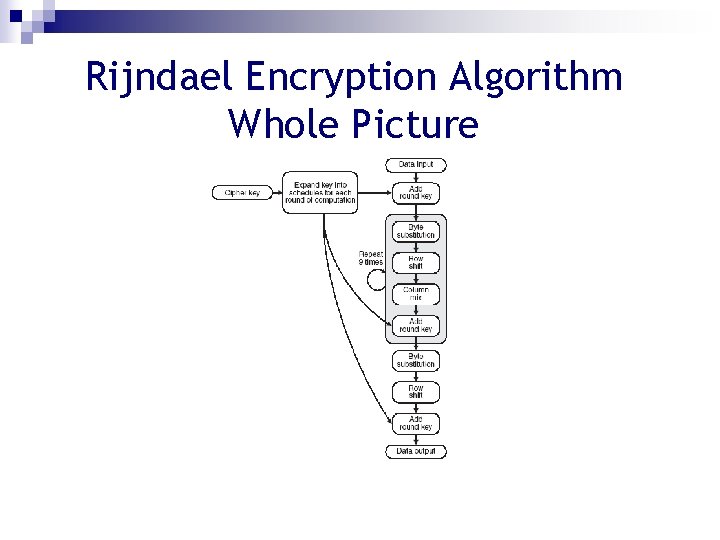

Rijndael Encryption Algorithm n n Inputs: 32 -bit text and 32 -bit key Key expansion ¨ n Add round key ¨ n Takes in a 32 -bit key, puts it in a state diagram, performs byte substitution and other operations XOR’s the key with its round texts Transformations Byte. Sub ¨ Shift. Row ¨ Mix. Column ¨

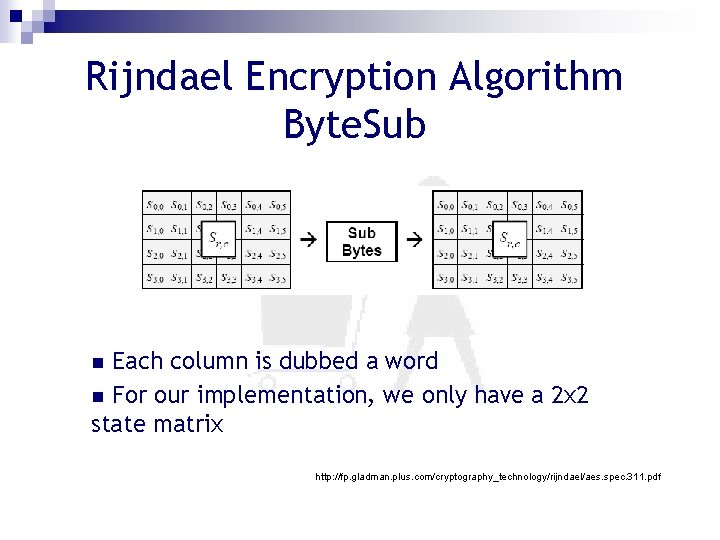

Rijndael Encryption Algorithm Byte. Sub Each column is dubbed a word n For our implementation, we only have a 2 x 2 state matrix n http: //fp. gladman. plus. com/cryptography_technology/rijndael/aes. spec. 311. pdf

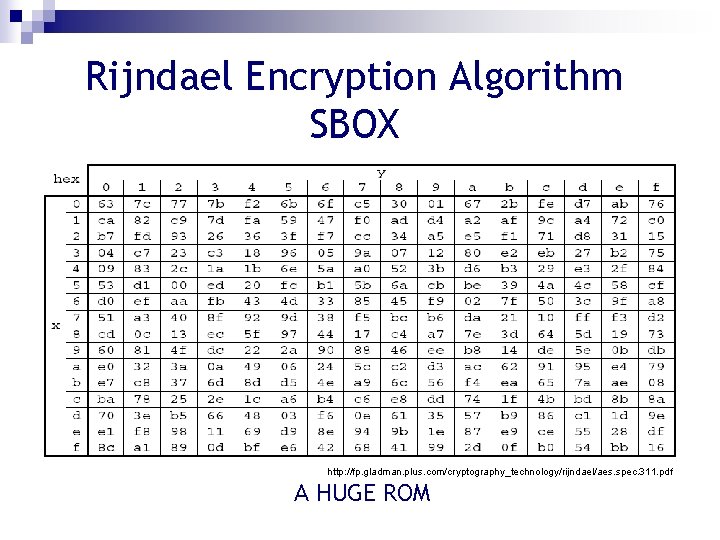

Rijndael Encryption Algorithm SBOX http: //fp. gladman. plus. com/cryptography_technology/rijndael/aes. spec. 311. pdf A HUGE ROM

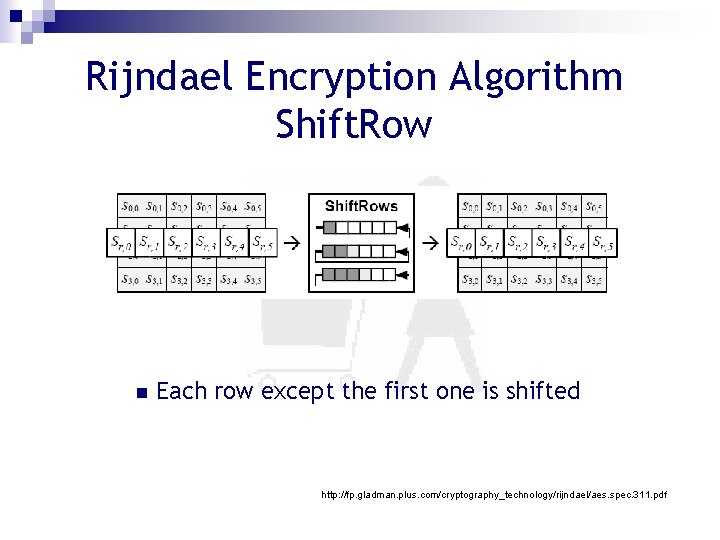

Rijndael Encryption Algorithm Shift. Row n Each row except the first one is shifted http: //fp. gladman. plus. com/cryptography_technology/rijndael/aes. spec. 311. pdf

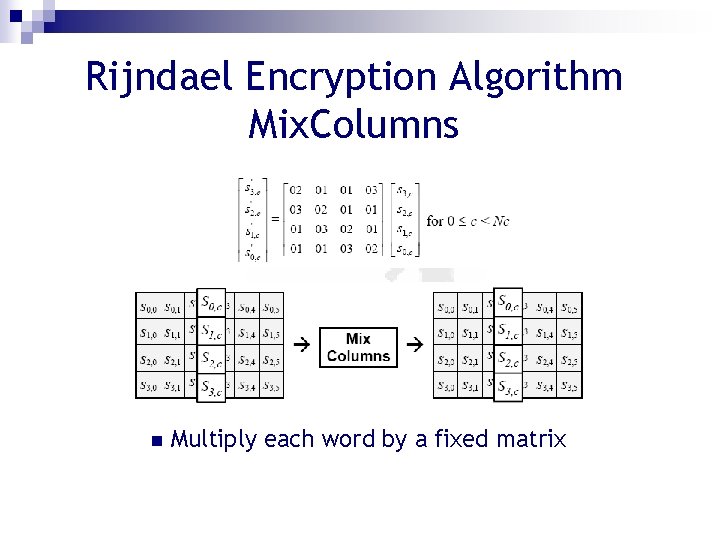

Rijndael Encryption Algorithm Mix. Columns n Multiply each word by a fixed matrix

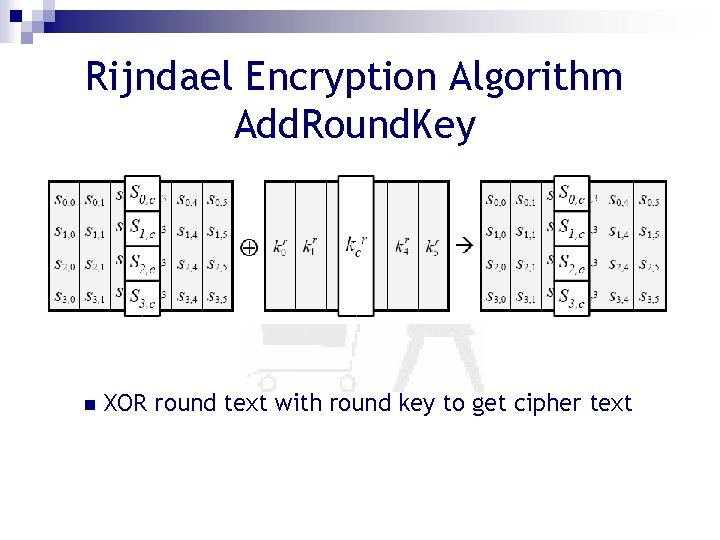

Rijndael Encryption Algorithm Add. Round. Key n XOR round text with round key to get cipher text

Rijndael Encryption Algorithm Key Expansion n Takes each word in the previous round key state diagram and performs certain operations ¨ If the word subscript is a multiple of 4 then the word becomes the (previous word shifted down once and byte substituted)^(the previous 4 th multiple)^(RCN-1) n n ¨ Where N=current round and we’re given RC 1=2 RCN-1 is padded with zeros to make its size the length of each word If the word is not a multiple of 4 then the word becomes (previous round’s corresponding column)^(previous word) Ex: W 4=W 0^Byte. Sub(Shift. Down. One(W 3))^(00_00_00_02) ¨ Ex: W 5=W 1^W 4 ¨

Rijndael Encryption Algorithm Whole Picture

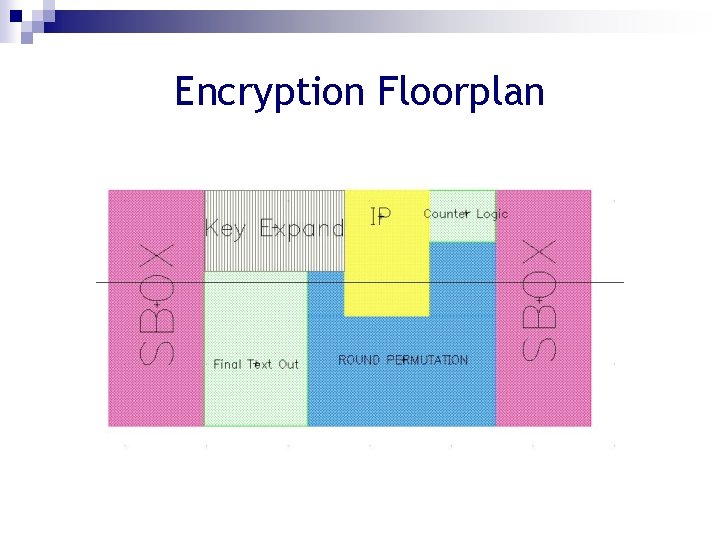

Encryption Floorplan

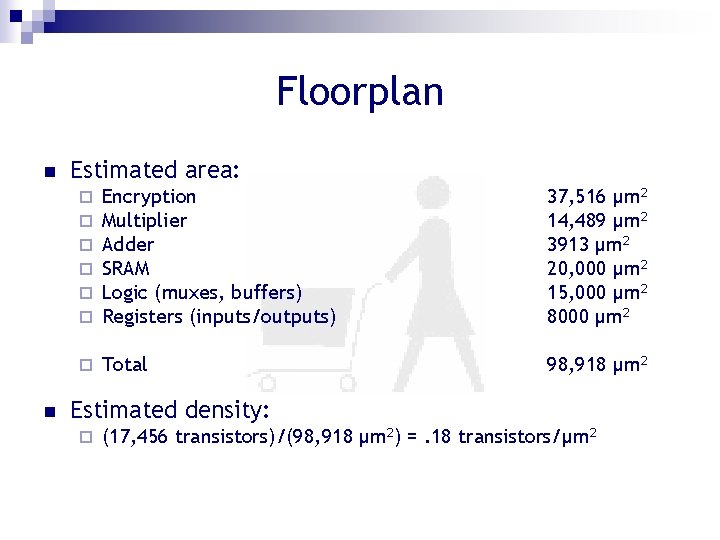

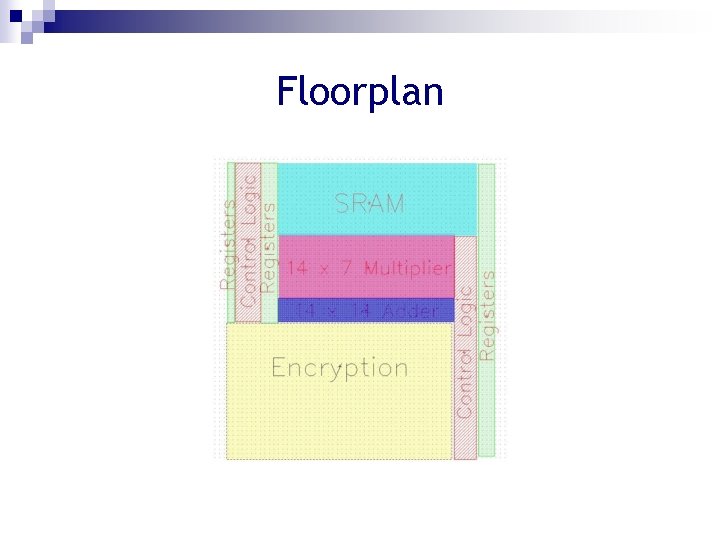

Floorplan n n Estimated area: ¨ ¨ ¨ Encryption Multiplier Adder SRAM Logic (muxes, buffers) Registers (inputs/outputs) 37, 516 μm 2 14, 489 μm 2 3913 μm 2 20, 000 μm 2 15, 000 μm 2 8000 μm 2 ¨ Total 98, 918 μm 2 Estimated density: ¨ (17, 456 transistors)/(98, 918 μm 2) =. 18 transistors/μm 2

Floorplan

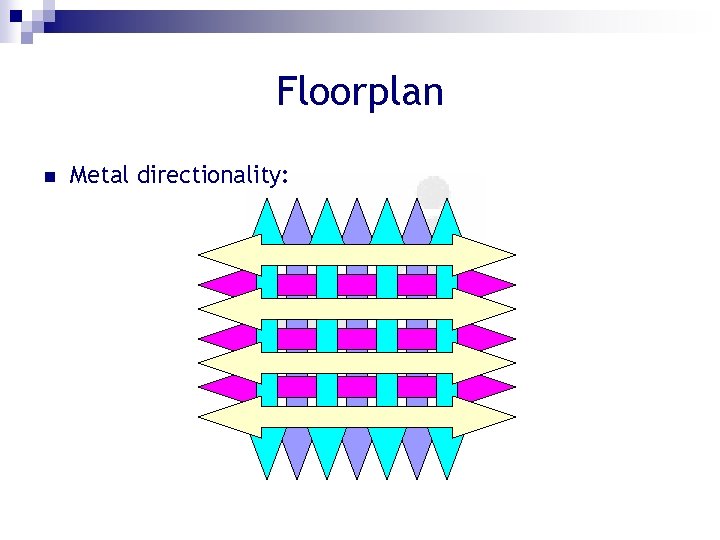

Floorplan n Metal directionality:

Floorplan n Interconnect Metal 1 & Metal 2: Vdd, Gnd, local interconnect ¨ Metal 3 & Metal 4: Clk, reset, global interconnect ¨

Problems & Questions n Most efficient implementation of top-level design Decided to share inputs since we would have otherwise gone way over the 100 -pin limit ¨ Power consumption ¨ n n Newest implementation of top-level more efficient and saves power by “disabling” other blocks when not needed Floating point or not? ? ? ¨ Toooooo late

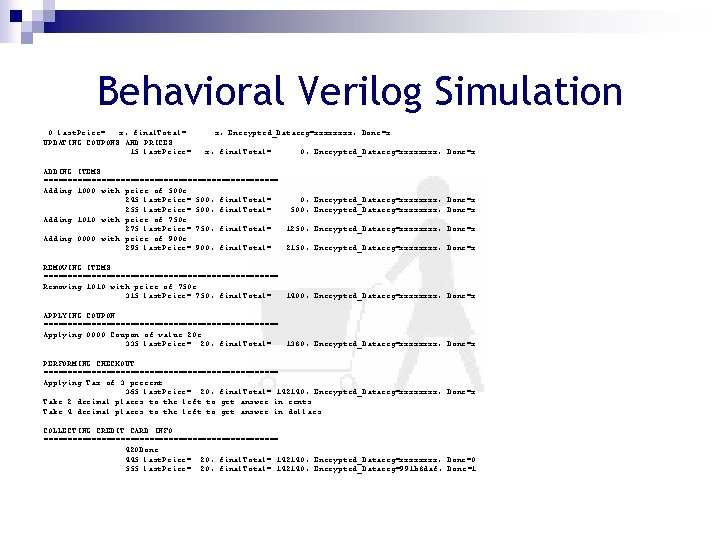

Behavioral Verilog Simulation 0 last. Price= x, final. Total= UPDATING COUPONS AND PRICES 15 last. Price= x, Encrypted_Datareg=xxxx, Done=x x, final. Total= 0, Encrypted_Datareg=xxxx, Done=x ADDING ITEMS ========================= Adding 1000 with price of 500 c 245 last. Price= 500, final. Total= 0, Encrypted_Datareg=xxxx, 255 last. Price= 500, final. Total= 500, Encrypted_Datareg=xxxx, Adding 1010 with price of 750 c 275 last. Price= 750, final. Total= 1250, Encrypted_Datareg=xxxx, Adding 0000 with price of 900 c 295 last. Price= 900, final. Total= 2150, Encrypted_Datareg=xxxx, Done=x REMOVING ITEMS ========================= Removing 1010 with price of 750 c 315 last. Price= 750, final. Total= 1400, Encrypted_Datareg=xxxx, Done=x APPLYING COUPON ========================= Applying 0000 Coupon of value 20 c 335 last. Price= 20, final. Total= 1380, Encrypted_Datareg=xxxx, Done=x PERFORMING CHECKOUT ========================= Applying Tax of 3 percent 365 last. Price= 20, final. Total= 142140, Encrypted_Datareg=xxxx, Done=x Take 2 decimal places to the left to get answer in cents Take 4 decimal places to the left to get answer in dollars COLLECTING CREDIT CARD INFO ========================= 420 Done 445 last. Price= 20, final. Total= 142140, Encrypted_Datareg=xxxx, Done=0 555 last. Price= 20, final. Total= 142140, Encrypted_Datareg=991 b 8 daf, Done=1

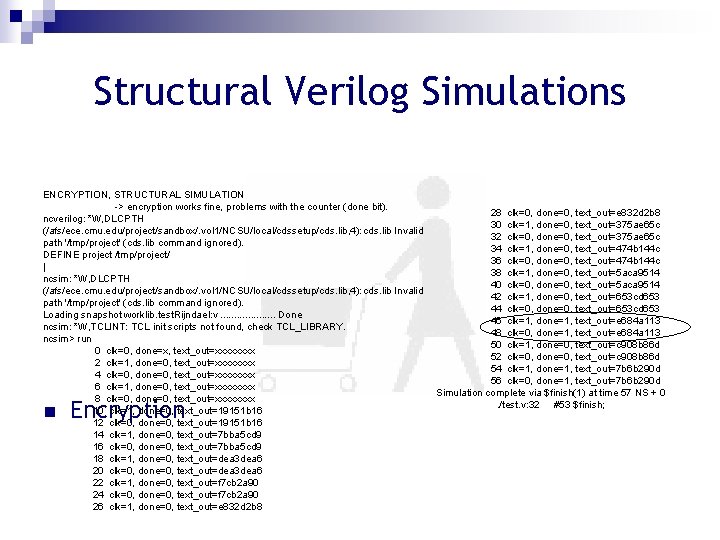

Structural Verilog Simulations ENCRYPTION, STRUCTURAL SIMULATION -> encryption works fine, problems with the counter (done bit). ncverilog: *W, DLCPTH (/afs/ece. cmu. edu/project/sandbox/. vol 1/NCSU/local/cdssetup/cds. lib, 4): cds. lib Invalid path '/tmp/project' (cds. lib command ignored). DEFINE project /tmp/project/ | ncsim: *W, DLCPTH (/afs/ece. cmu. edu/project/sandbox/. vol 1/NCSU/local/cdssetup/cds. lib, 4): cds. lib Invalid path '/tmp/project' (cds. lib command ignored). Loading snapshot worklib. test. Rijndael: v. . . . . Done ncsim: *W, TCLINT: TCL init scripts not found, check TCL_LIBRARY. ncsim> run 0 clk=0, done=x, text_out=xxxx 2 clk=1, done=0, text_out=xxxx 4 clk=0, done=0, text_out=xxxx 6 clk=1, done=0, text_out=xxxx 8 clk=0, done=0, text_out=xxxx 10 clk=1, done=0, text_out=19151 b 16 12 clk=0, done=0, text_out=19151 b 16 14 clk=1, done=0, text_out=7 bba 5 cd 9 16 clk=0, done=0, text_out=7 bba 5 cd 9 18 clk=1, done=0, text_out=dea 3 dea 6 20 clk=0, done=0, text_out=dea 3 dea 6 22 clk=1, done=0, text_out=f 7 cb 2 a 90 24 clk=0, done=0, text_out=f 7 cb 2 a 90 26 clk=1, done=0, text_out=e 832 d 2 b 8 n Encryption 28 clk=0, done=0, text_out=e 832 d 2 b 8 30 clk=1, done=0, text_out=375 ae 65 c 32 clk=0, done=0, text_out=375 ae 65 c 34 clk=1, done=0, text_out=474 b 144 c 36 clk=0, done=0, text_out=474 b 144 c 38 clk=1, done=0, text_out=5 aca 9514 40 clk=0, done=0, text_out=5 aca 9514 42 clk=1, done=0, text_out=653 cd 653 44 clk=0, done=0, text_out=653 cd 653 46 clk=1, done=1, text_out=e 684 a 113 48 clk=0, done=1, text_out=e 684 a 113 50 clk=1, done=0, text_out=c 908 b 86 d 52 clk=0, done=0, text_out=c 908 b 86 d 54 clk=1, done=1, text_out=7 b 6 b 290 d 56 clk=0, done=1, text_out=7 b 6 b 290 d Simulation complete via $finish(1) at time 57 NS + 0. /test. v: 32 #53 $finish;

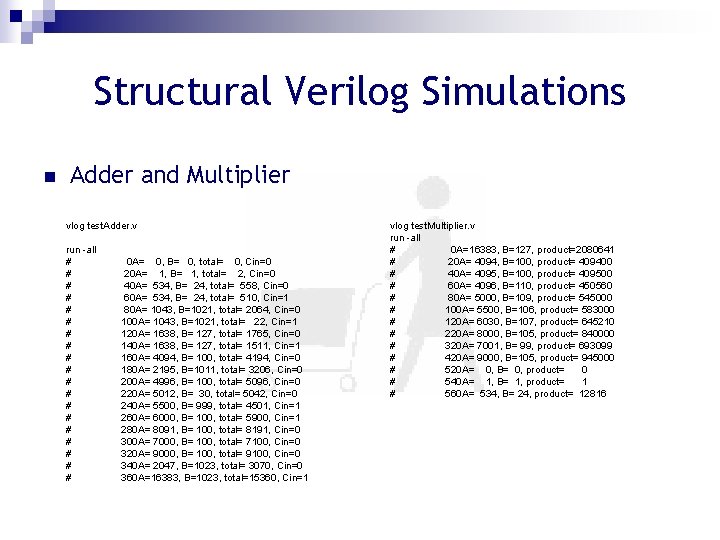

Structural Verilog Simulations n Adder and Multiplier vlog test. Adder. v run -all # # # # # 0 A= 0, B= 0, total= 0, Cin=0 20 A= 1, B= 1, total= 2, Cin=0 40 A= 534, B= 24, total= 558, Cin=0 60 A= 534, B= 24, total= 510, Cin=1 80 A= 1043, B=1021, total= 2064, Cin=0 100 A= 1043, B=1021, total= 22, Cin=1 120 A= 1638, B= 127, total= 1765, Cin=0 140 A= 1638, B= 127, total= 1511, Cin=1 160 A= 4094, B= 100, total= 4194, Cin=0 180 A= 2195, B=1011, total= 3206, Cin=0 200 A= 4996, B= 100, total= 5096, Cin=0 220 A= 5012, B= 30, total= 5042, Cin=0 240 A= 5500, B= 999, total= 4501, Cin=1 260 A= 6000, B= 100, total= 5900, Cin=1 280 A= 8091, B= 100, total= 8191, Cin=0 300 A= 7000, B= 100, total= 7100, Cin=0 320 A= 9000, B= 100, total= 9100, Cin=0 340 A= 2047, B=1023, total= 3070, Cin=0 360 A=16383, B=1023, total=15360, Cin=1 vlog test. Multiplier. v run -all # 0 A=16383, B=127, product=2080641 # 20 A= 4094, B=100, product= 409400 # 40 A= 4095, B=100, product= 409500 # 60 A= 4096, B=110, product= 450560 # 80 A= 5000, B=109, product= 545000 # 100 A= 5500, B=106, product= 583000 # 120 A= 6030, B=107, product= 645210 # 220 A= 8000, B=105, product= 840000 # 320 A= 7001, B= 99, product= 693099 # 420 A= 9000, B=105, product= 945000 # 520 A= 0, B= 0, product= 0 # 540 A= 1, B= 1, product= 1 # 560 A= 534, B= 24, product= 12816

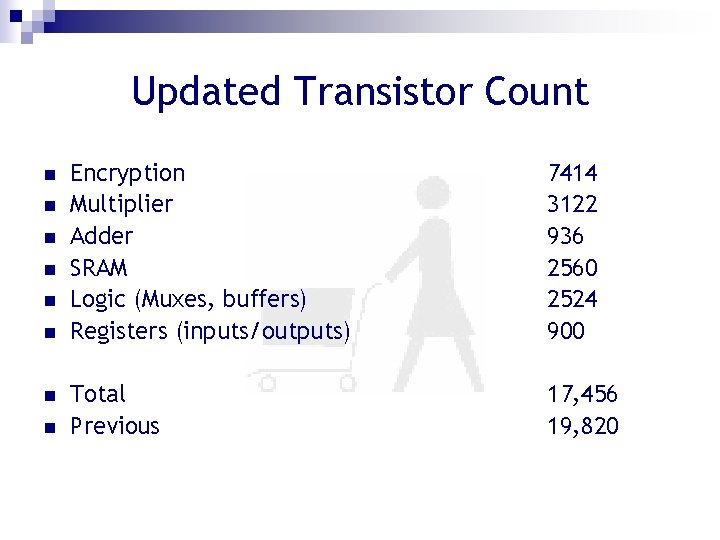

Updated Transistor Count n n n n Encryption Multiplier Adder SRAM Logic (Muxes, buffers) Registers (inputs/outputs) 7414 3122 936 2560 2524 900 Total Previous 17, 456 19, 820

The Real “Floorplan…”

Sweet layouts A“butt”ment Metal 5 Interconnect

- Slides: 25