NEXT CHIP PALPIDE 3 021214 gianluca aglieri rinellacern

- Slides: 10

NEXT CHIP: PALPIDE 3 02/12/14 gianluca. aglieri. rinella@cern. ch 1

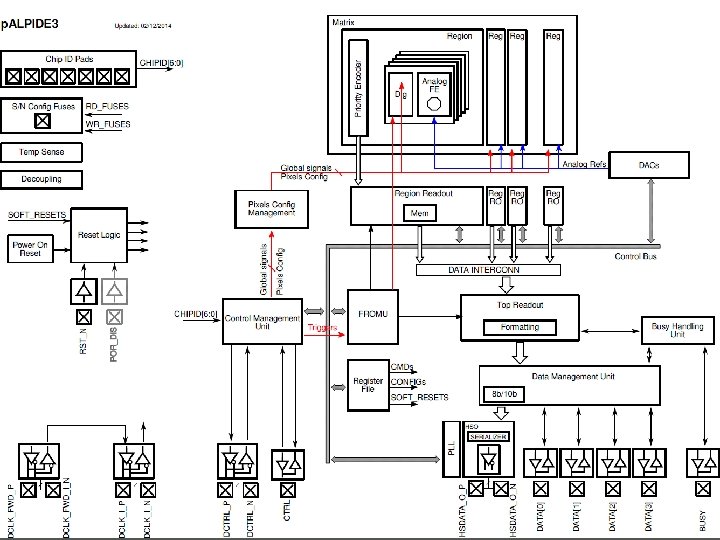

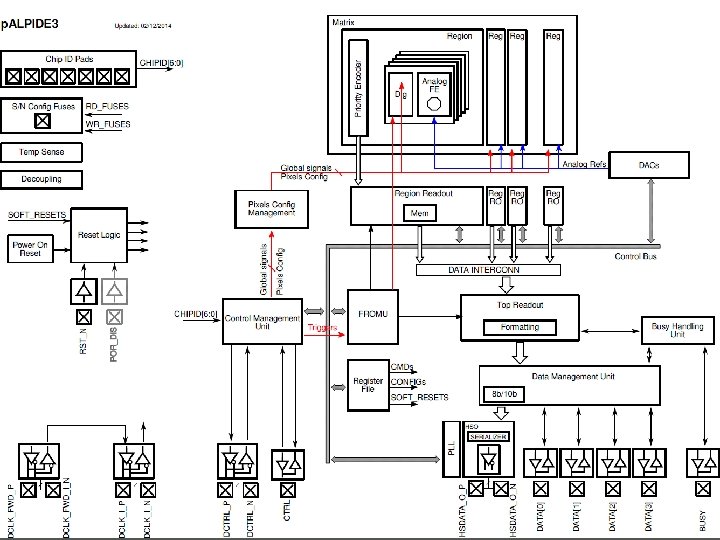

p. ALPIDE 3 Requirements for p. ALPIDE 3 (ALPIDE fs prototype 3) • Matrix implementation • • • Final floorplan (30 mm × 15 mm) Final pads location Final pixel pitch and size In-pixel Multi Event hit storage (depth 3 MEB) Std cell based Priority Encoder Revised digital and analog routing • Analog biasing and monitoring • Digital periphery • New module handling trigger management and MEB • Revision of data path, re-factoring of Data Management Unit, optimization of data protocol • Interfaces • Data Transmission Unit (1. 2 Gbps and 400 Mbps) • Clocking distribution for OB module integration 02/12/14 gianluca. aglieri. rinella@cern. ch 2

DIGITAL PERIPHERY AND INTERFACES DESIGN ITEMS 02/12/14 gianluca. aglieri. rinella@cern. ch 3

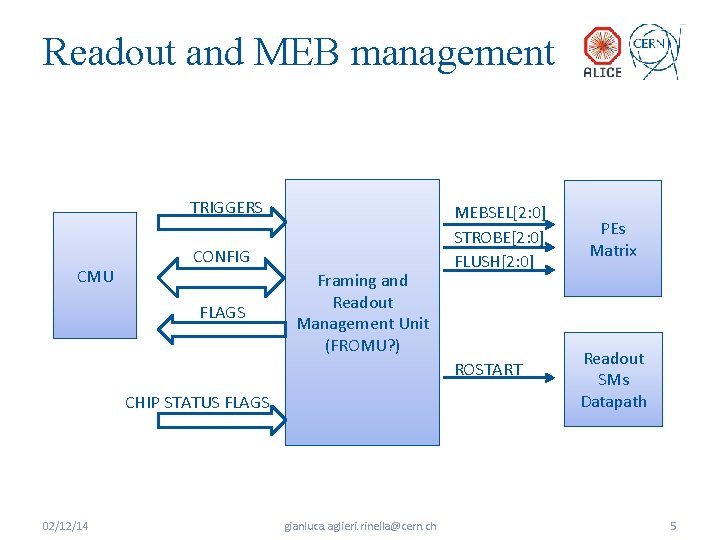

Matrix readout interfaces will change Digital steering of pixel MEBs • Priority Encoder interface remains similar • Additions • MEBSEL[2: 0] – MEB selection • STROBE[2: 0] – Frame strobing • FLUSH[2: 0] – Frame reset 02/12/14 gianluca. aglieri. rinella@cern. ch 4

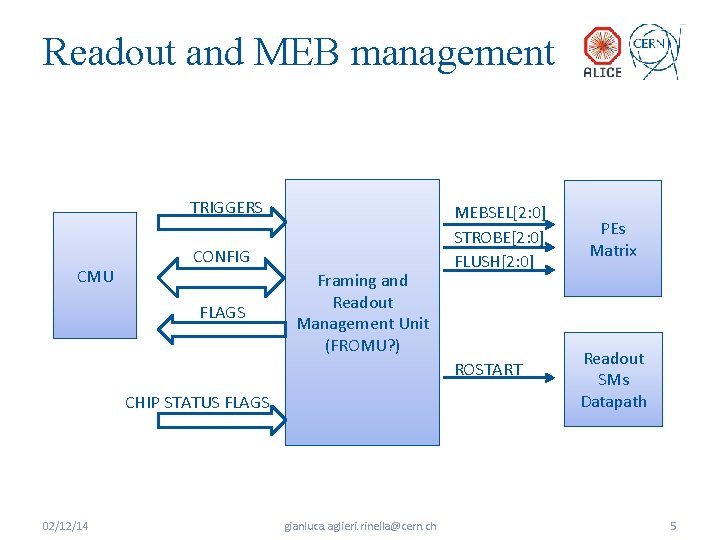

Readout and MEB management TRIGGERS CMU CONFIG FLAGS Framing and Readout Management Unit (FROMU? ) MEBSEL[2: 0] STROBE[2: 0] FLUSH[2: 0] ROSTART CHIP STATUS FLAGS 02/12/14 gianluca. aglieri. rinella@cern. ch PEs Matrix Readout SMs Datapath 5

Framing and Readout Management Unit • New digital module (FROMU ? ? ) • Purposes • • Sequence frames strobe and readout phases Multi-event Memory selection, reset, readout coordination Programmable readout modes Triggered frames Continuous framing Frame duration control Time stamping of frames Monitors of running states and error conditions • Proposal • • 02/12/14 Specification: CERN + IRFU Design and standalone verification: IRFU Integrated verification: CERN Implementation (digital P&R): CERN gianluca. aglieri. rinella@cern. ch 6

Revision and refactoring of DMU Data Management Unit • • Strongly coupled with ALPIDE Top Readout Unit (TRU) Revision needed for the full data rate capability Re-factoring of module code to isolate it from TRU Addition of 8 b/10 b Encoder module (+verification) • Proposal • • 02/12/14 Specification: CERN+ INFN Cagliari Re-Design and standalone verification: INFN Cagliari Integrated verification: CERN Implementation (digital P&R): CERN gianluca. aglieri. rinella@cern. ch 7

Data Transmission Unit Final Data Trasmission Unit • PLL finalization: INFN Torino • High speed line driver: INFN Torino • Serializer finalization: INFN Torino + CERN • 8 b/10 b encoder verification and implementation: INFN Torino + CERN 02/12/14 gianluca. aglieri. rinella@cern. ch 8

New OB module clock tree Revision of clock distribution for OB module Proposal • Differential clock signaling on the module • Remove single ended clock forwarding ports • Add on-chip programmable termination feature to MLVDS transceiver: INFN Torino • Add a second MLVDS receiver dedicated exclusively to clock forwarding in the OB Module master 02/12/14 gianluca. aglieri. rinella@cern. ch 9

02/12/14 gianluca. aglieri. rinella@cern. ch 10