Memory Management Background Logical versus Physical Address Space

Memory Management • • • Background Logical versus Physical Address Space Contiguous Allocation Paging Segmentation with Paging

Basics • For execution a program must be brought into memory. • Input queue – consists of collection of processes on the disk that are waiting to be brought into memory for execution. • Physical Addresses - These are the addresses assigned by the manufacturer; these cannot be changed by the programmer. The range of these addresses constitutes physical address space. • Logical addresses These addresses are generated by the compiler. A compiler can generates absolutes or re-locatable addresses. The range of these addresses constitutes logical address space.

• Binding of a logical addresses of instruction or Data to physical address is called address translation it can happen at three different stages. – At compile time If memory location is known in advance absolute code can be generated; must recompile code if starting location changes. – At load time – Must generate relocatable code if memory location is not known at compile time. – Execution time – Binding is delayed until run time if the process can be moved during its execution from one part to another part of the memory. Hardware support is required for address maps (e. g. , base and limit registers).

Address Translation • Binding of a logical address of instruction or data to physical address is called address translation it can happen at three different stages. o At compile time § If memory location is known in advance absolute code can be generated; must recompile code if starting location changes. o At load time § Must generate relocatable code if memory location is not known at compile time. o Execution time § Binding is delayed until run time if the process can be moved during its execution from one part to another part of the memory. Hardware support is required for address maps (e. g. , base and limit registers).

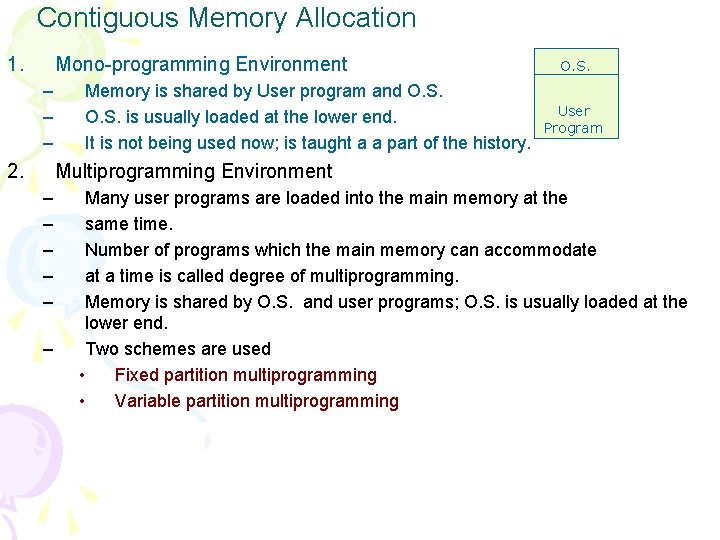

Contiguous Memory Allocation 1. Mono-programming Environment – – – 2. Memory is shared by User program and O. S. is usually loaded at the lower end. It is not being used now; is taught a a part of the history. O. S. User Program Multiprogramming Environment – – – Many user programs are loaded into the main memory at the same time. Number of programs which the main memory can accommodate at a time is called degree of multiprogramming. Memory is shared by O. S. and user programs; O. S. is usually loaded at the lower end. Two schemes are used • Fixed partition multiprogramming • Variable partition multiprogramming

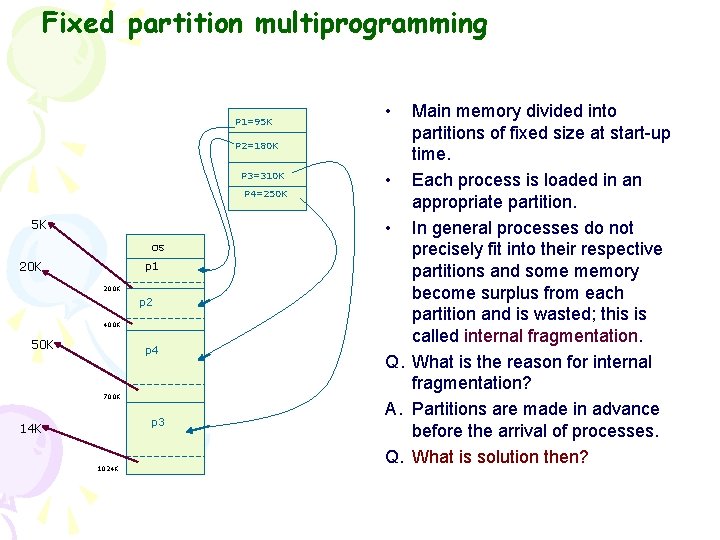

Fixed partition multiprogramming P 1=95 K P 2=180 K P 3=310 K P 4=250 K 5 K OS 20 K p 1 200 K 100 K p 2 400 K 50 K p 4 700 K p 3 14 K 1024 K • Main memory divided into partitions of fixed size at start-up time. • Each process is loaded in an appropriate partition. • In general processes do not precisely fit into their respective partitions and some memory become surplus from each partition and is wasted; this is called internal fragmentation. Q. What is the reason for internal fragmentation? A. Partitions are made in advance before the arrival of processes. Q. What is solution then?

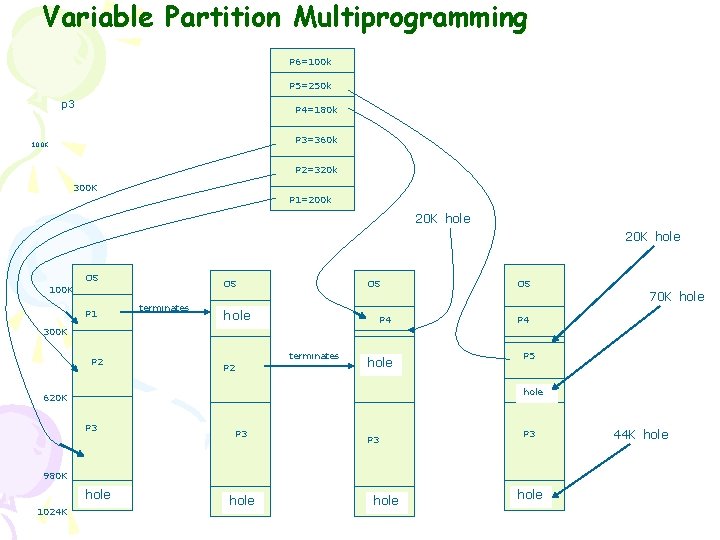

Variable Partition Multiprogramming p 2 P 6=100 k P 5=250 k p 3 P 4=180 k P 3=360 k 100 K P 2=320 k 300 K P 1=200 k 20 K hole OS OS 100 K P 1 terminates OS OS 70 K hole P 4 300 K P 2 terminates P 2 hole P 5 hole 620 K P 3 P 3 980 K hole 1024 K hole 44 K hole

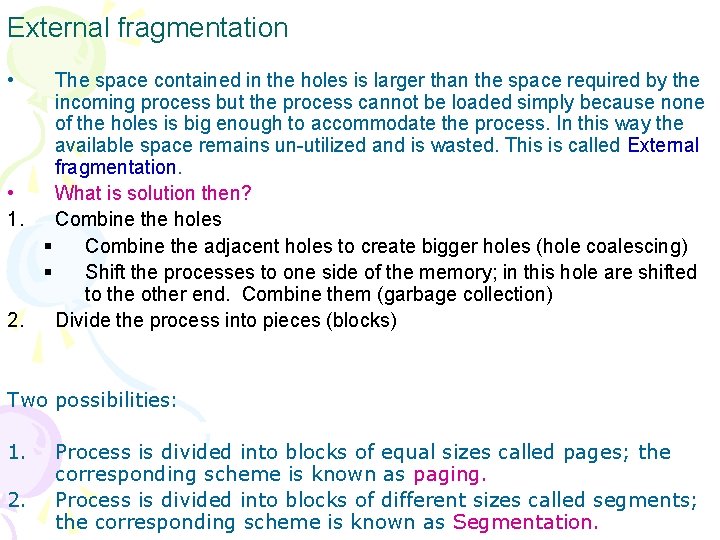

External fragmentation • The space contained in the holes is larger than the space required by the incoming process but the process cannot be loaded simply because none of the holes is big enough to accommodate the process. In this way the available space remains un-utilized and is wasted. This is called External fragmentation. • What is solution then? 1. Combine the holes § Combine the adjacent holes to create bigger holes (hole coalescing) § Shift the processes to one side of the memory; in this hole are shifted to the other end. Combine them (garbage collection) 2. Divide the process into pieces (blocks) Two possibilities: 1. 2. Process is divided into blocks of equal sizes called pages; the corresponding scheme is known as paging. Process is divided into blocks of different sizes called segments; the corresponding scheme is known as Segmentation.

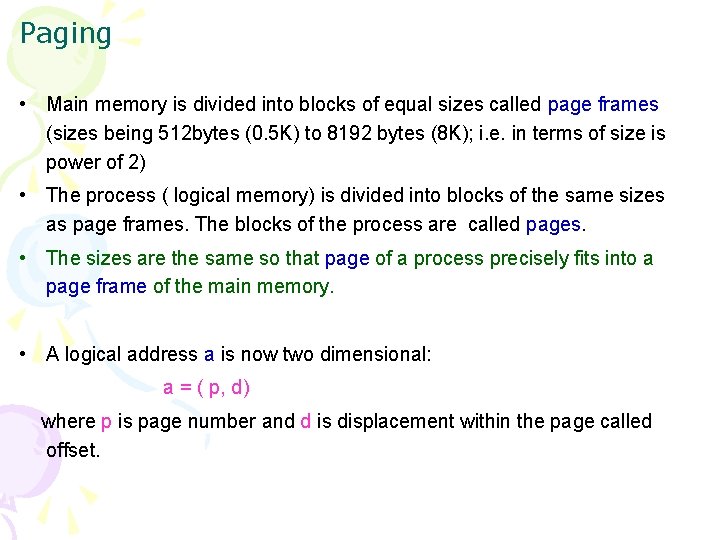

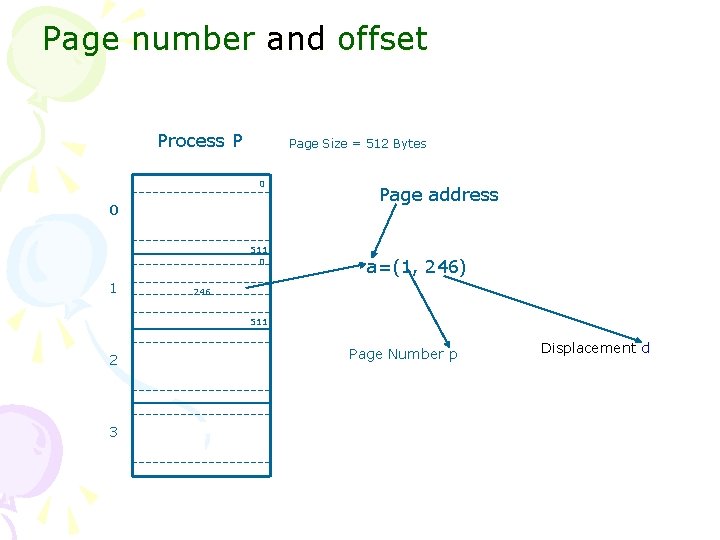

Paging • Main memory is divided into blocks of equal sizes called page frames (sizes being 512 bytes (0. 5 K) to 8192 bytes (8 K); i. e. in terms of size is power of 2) • The process ( logical memory) is divided into blocks of the same sizes as page frames. The blocks of the process are called pages. • The sizes are the same so that page of a process precisely fits into a page frame of the main memory. • A logical address a is now two dimensional: a = ( p, d) where p is page number and d is displacement within the page called offset.

Page number and offset Process P Page Size = 512 Bytes 0 0 511 0 1 Page address a=(1, 246) 246 511 2 3 Page Number p Displacement d

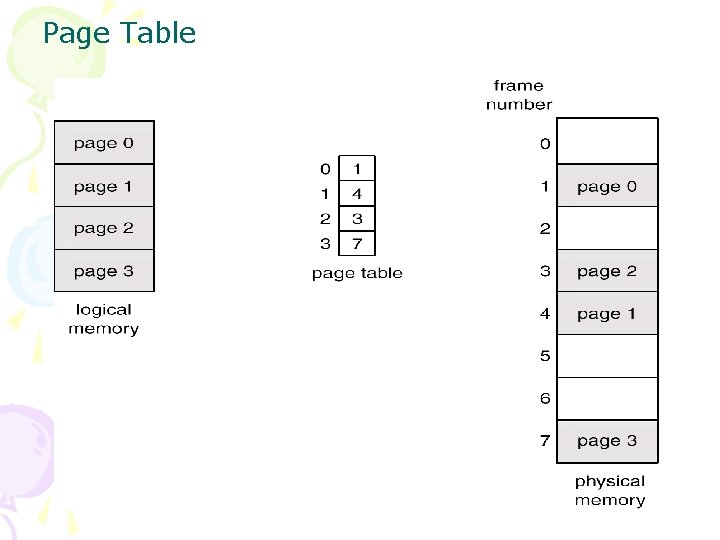

Page Table

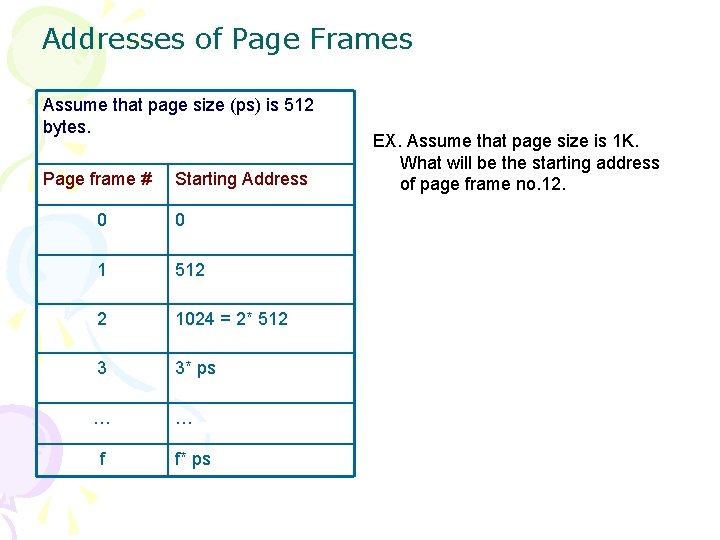

Addresses of Page Frames Assume that page size (ps) is 512 bytes. Page frame # Starting Address 0 0 1 512 2 1024 = 2* 512 3 3* ps … … f f* ps EX. Assume that page size is 1 K. What will be the starting address of page frame no. 12.

Paging (cont) • If a system uses x bit addresses and page size is 2 n then lower n bit are used for displacement (offset) and higher x-n bits are used to represent the page number. • Example: Suppose a computer uses 16 bit address and page size is 1 K. Find maximum number of pages and convert the following page address into (p, d) form: 0010100000101011 Page size = 1 K = 1024 = 210, therefore, n = 10 out of 16 bits, the lower 10 bits are used for the displacement d and higher 6 bits represent the page numbers; maximum number of pages = 26 = 64. The given address 0010100000101011 in (p, d) d form will be: (10, 43)p • Ex. A computer uses 16 bit address and page size is 2 K. Find maximum number of pages and convert the following page address into (p, d) form: 0010100000101011

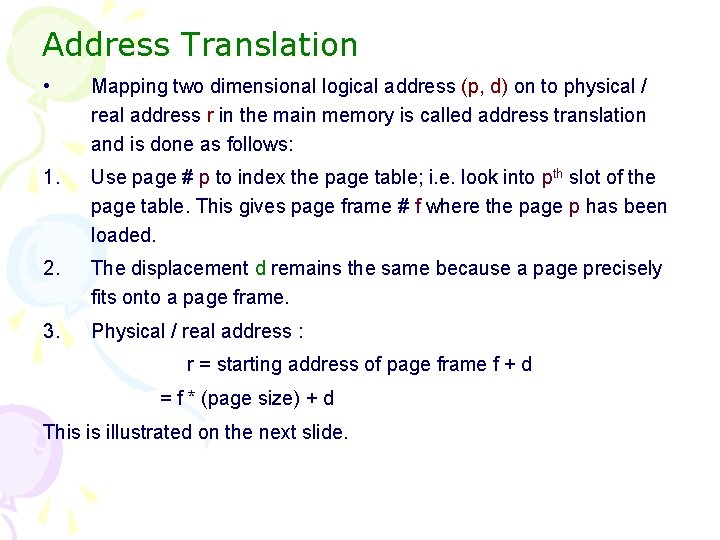

Address Translation • Mapping two dimensional logical address (p, d) on to physical / real address r in the main memory is called address translation and is done as follows: 1. Use page # p to index the page table; i. e. look into pth slot of the page table. This gives page frame # f where the page p has been loaded. 2. The displacement d remains the same because a page precisely fits onto a page frame. 3. Physical / real address : r = starting address of page frame f + d = f * (page size) + d This is illustrated on the next slide.

Address Translation (contd. )

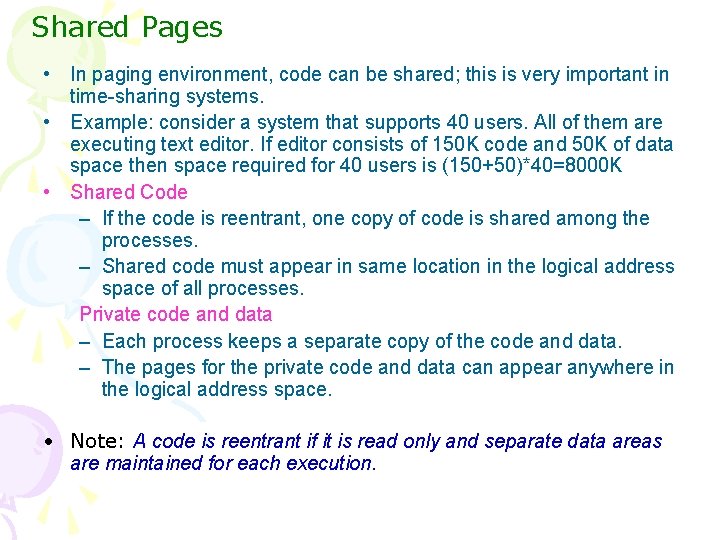

Shared Pages • In paging environment, code can be shared; this is very important in time-sharing systems. • Example: consider a system that supports 40 users. All of them are executing text editor. If editor consists of 150 K code and 50 K of data space then space required for 40 users is (150+50)*40=8000 K • Shared Code – If the code is reentrant, one copy of code is shared among the processes. – Shared code must appear in same location in the logical address space of all processes. Private code and data – Each process keeps a separate copy of the code and data. – The pages for the private code and data can appear anywhere in the logical address space. • Note: A code is reentrant if it is read only and separate data areas are maintained for each execution.

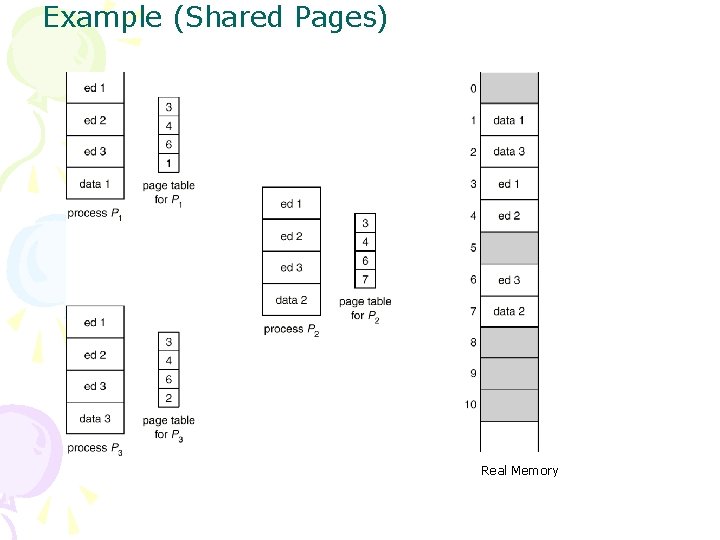

Example (Shared Pages) Real Memory

Shared Pages (cont) • In page sharing only one copy of the editor is placed in the main memory. • Page table of each user maps to the same page frames of the editor. • Data pages map to the different page frames. • With shared pages, total space required to support 40 users is 150 + 40*50 =2150 K instead of 8000 K • All the heavily used programs are shared; these includes text editors, compilers, window systems, etc.

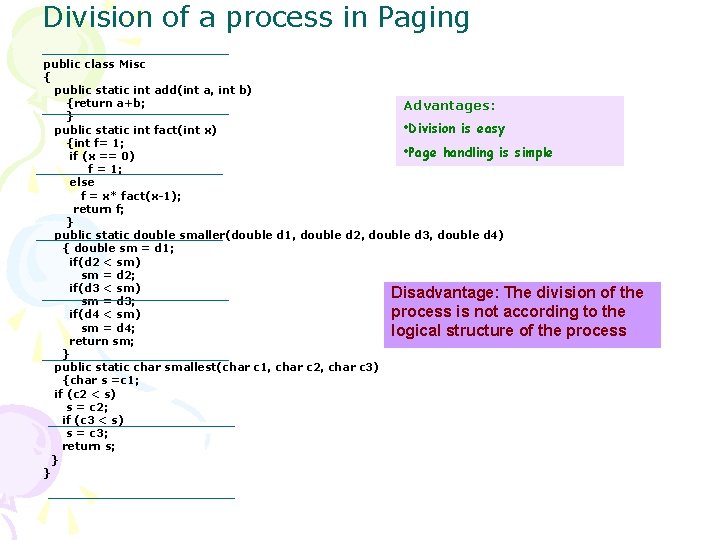

Division of a process in Paging public class Misc { public static int add(int a, int b) {return a+b; Advantages: } • Division is easy public static int fact(int x) {int f= 1; • Page handling is simple if (x == 0) f = 1; else f = x* fact(x-1); return f; } public static double smaller(double d 1, double d 2, double d 3, double d 4) { double sm = d 1; if(d 2 < sm) sm = d 2; if(d 3 < sm) Disadvantage: The division of the sm = d 3; process is not according to the if(d 4 < sm) sm = d 4; logical structure of the process return sm; } public static char smallest(char c 1, char c 2, char c 3) {char s =c 1; if (c 2 < s) s = c 2; if (c 3 < s) s = c 3; return s; } }

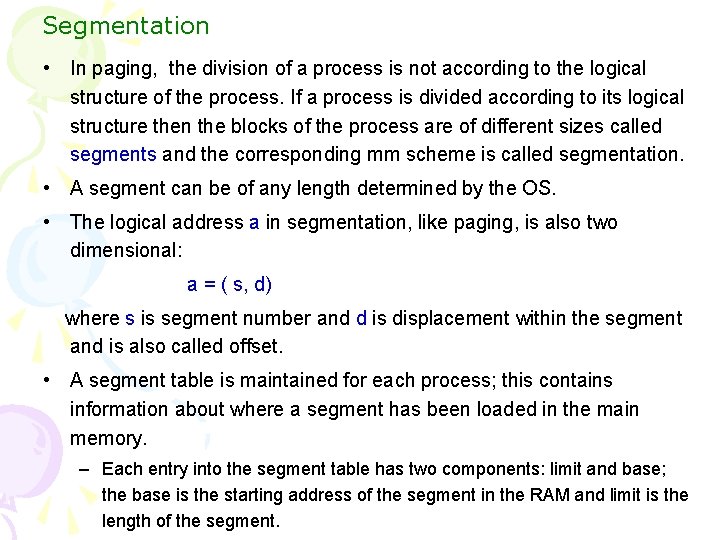

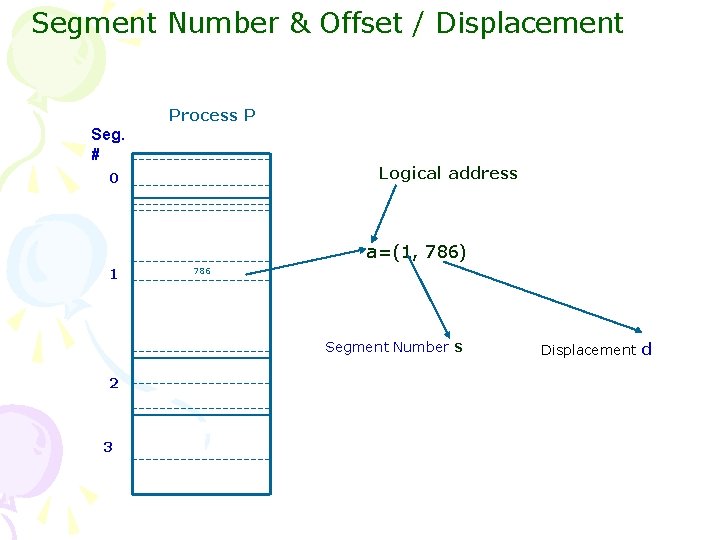

Segmentation • In paging, the division of a process is not according to the logical structure of the process. If a process is divided according to its logical structure then the blocks of the process are of different sizes called segments and the corresponding mm scheme is called segmentation. • A segment can be of any length determined by the OS. • The logical address a in segmentation, like paging, is also two dimensional: a = ( s, d) where s is segment number and d is displacement within the segment and is also called offset. • A segment table is maintained for each process; this contains information about where a segment has been loaded in the main memory. – Each entry into the segment table has two components: limit and base; the base is the starting address of the segment in the RAM and limit is the length of the segment.

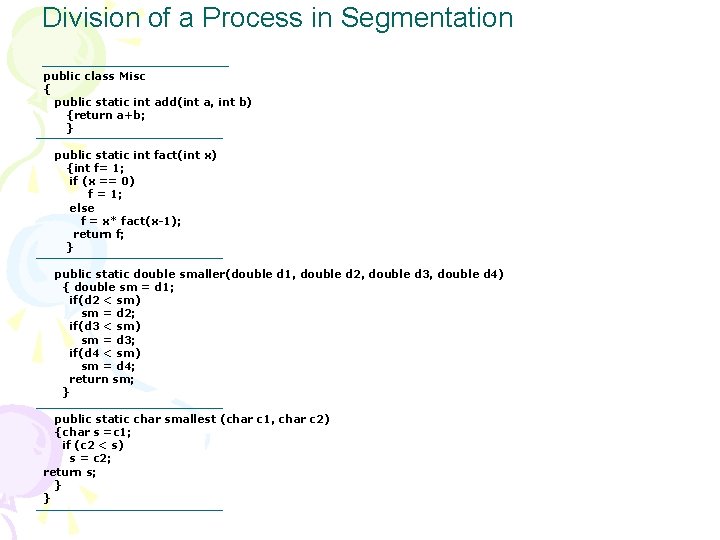

Division of a Process in Segmentation public class Misc { public static int add(int a, int b) {return a+b; } public static int fact(int x) {int f= 1; if (x == 0) f = 1; else f = x* fact(x-1); return f; } public static double smaller(double d 1, double d 2, double d 3, double d 4) { double sm = d 1; if(d 2 < sm) sm = d 2; if(d 3 < sm) sm = d 3; if(d 4 < sm) sm = d 4; return sm; } public static char smallest (char c 1, char c 2) {char s =c 1; if (c 2 < s) s = c 2; return s; } }

Segment Number & Offset / Displacement Process P Seg. # Logical address 0 a=(1, 786) 1 786 Segment Number s 2 3 Displacement d

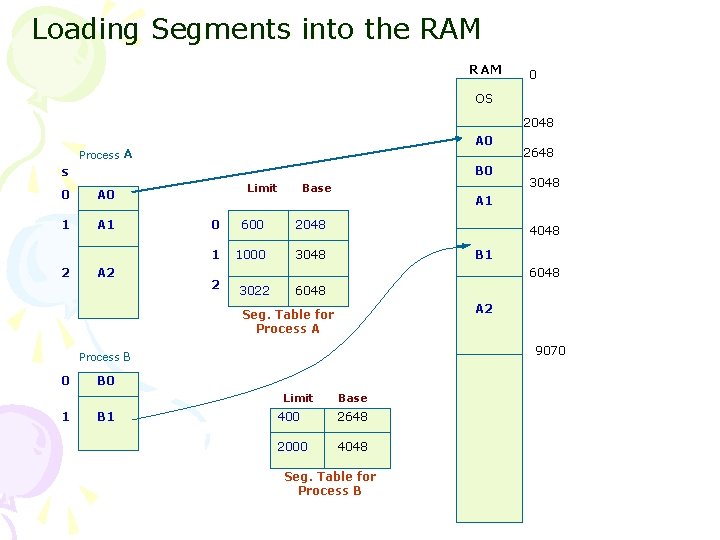

Loading Segments into the RAM 0 OS 2048 Process A 0 A s B 0 0 A 0 1 A 1 2 A 2 Limit Base 0 600 2048 1 1000 3048 2 4048 B 1 6048 3022 6048 A 2 9070 Process B B 0 Limit 1 B 1 3048 A 1 Seg. Table for Process A 0 2648 Base 400 2648 2000 4048 Seg. Table for Process B

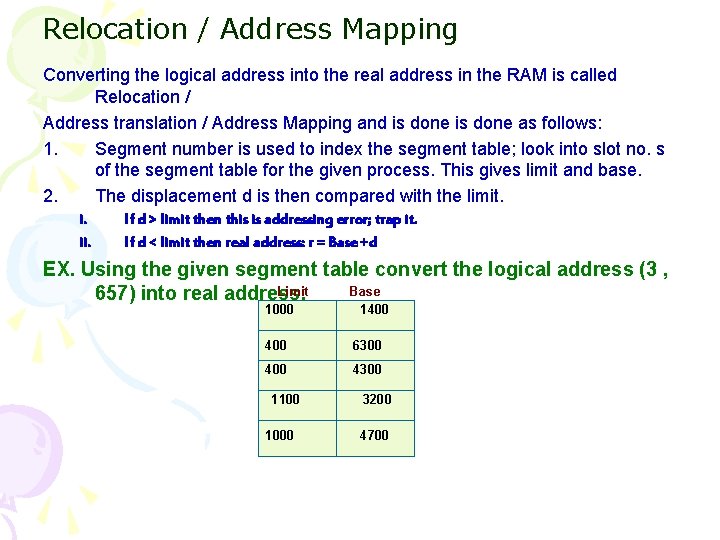

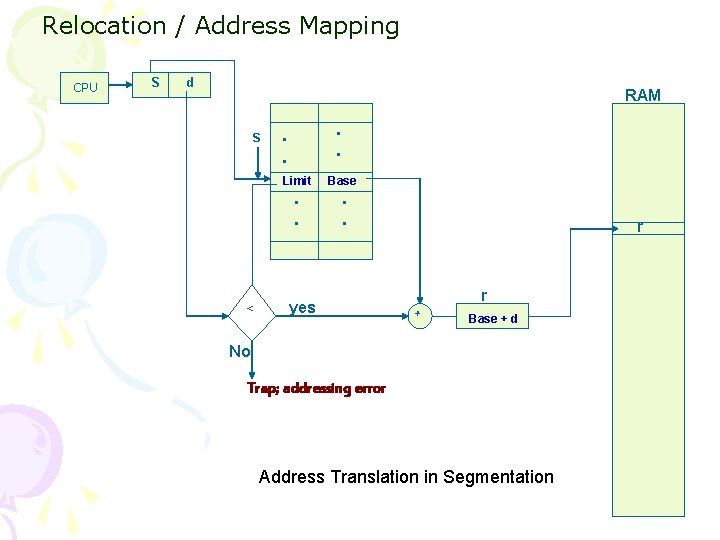

Relocation / Address Mapping Converting the logical address into the real address in the RAM is called Relocation / Address translation / Address Mapping and is done as follows: 1. Segment number is used to index the segment table; look into slot no. s of the segment table for the given process. This gives limit and base. 2. The displacement d is then compared with the limit. i. ii. If d > limit then this is addressing error; trap it. If d < limit then real address: r = Base +d EX. Using the given segment table convert the logical address (3 , Limit Base 657) into real address. 1000 1400 6300 4300 1100 1000 3200 4700

Relocation / Address Mapping CPU S d RAM S . . < Limit Base . . yes r r + Base + d No Trap; addressing error Address Translation in Segmentation

Combined Paging & Segmentation • The respective advantages of paging segmentation are combined into a paged segmented system. In this system: • Main memory is divided into blocks of equal sizes called page frames (sizes being 512 bytes (0. 5 K) to 8192 bytes (8 K). • The process is divided into segments. • The segments are divided into pages. • A logical address a is now three dimensional: a = ( s, p, d) where s is segment number p is page number within segment s d is offset within page p and d is displacement within the page called offset.

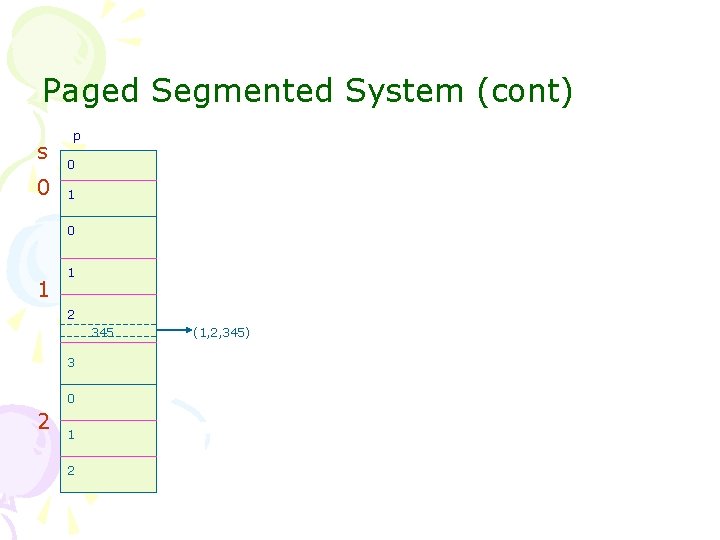

Paged Segmented System (cont) s 0 p 0 1 1 2 345 3 0 2 1 2 (1, 2, 345)

- Slides: 27