Memories 1 Flash Memory Reprogrammable program Flash memory

Memories

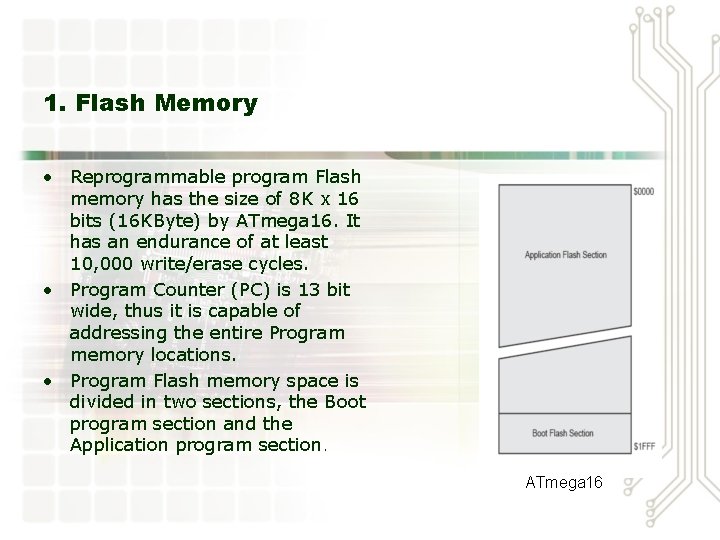

1. Flash Memory • Reprogrammable program Flash memory has the size of 8 K x 16 bits (16 KByte) by ATmega 16. It has an endurance of at least 10, 000 write/erase cycles. • Program Counter (PC) is 13 bit wide, thus it is capable of addressing the entire Program memory locations. • Program Flash memory space is divided in two sections, the Boot program section and the Application program section. ATmega 16

• Boot Memory Size is programmable thr’ fuses (128 -1024 words(16 bit)). • Boot Memory allows downloading and uploading program code by the μC itself. This feature allows flexible application software updates using a Flash-resident Boot Loader program.

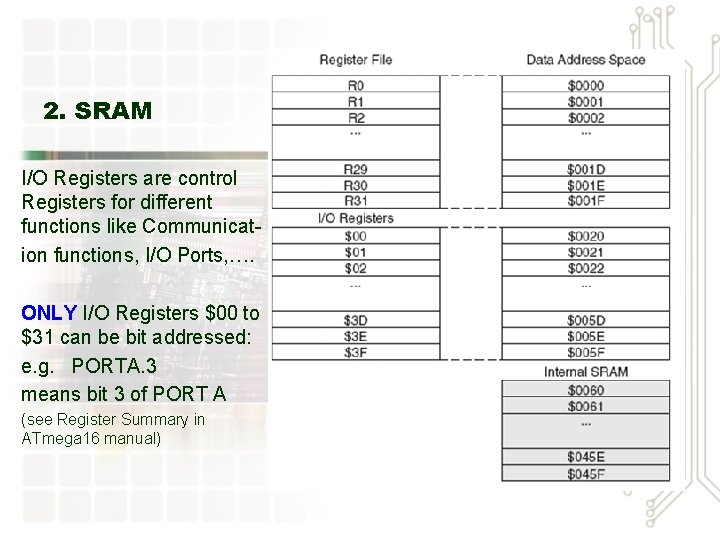

2. SRAM I/O Registers are control Registers for different functions like Communication functions, I/O Ports, …. ONLY I/O Registers $00 to $31 can be bit addressed: e. g. PORTA. 3 means bit 3 of PORT A (see Register Summary in ATmega 16 manual)

3. EEPROM • • 512 byte having an endurance of at least 100, 000 write/erase cycles. Write access time ≈ 8. 5 ms. • • While read CPU halted for 4 clock cycles While write CPU halted for 2 clock cycles

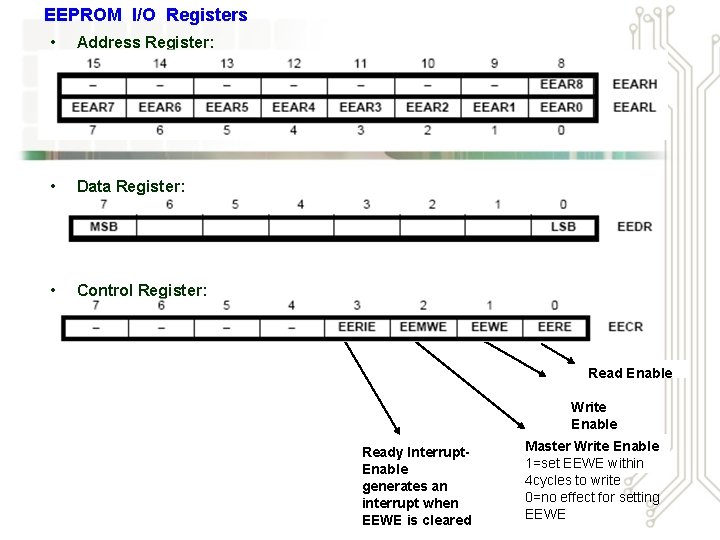

EEPROM I/O Registers • Address Register: • Data Register: • Control Register: Read Enable Write Enable Ready Interrupt. Enable generates an interrupt when EEWE is cleared Master Write Enable 1=set EEWE within 4 cycles to write 0=no effect for setting EEWE

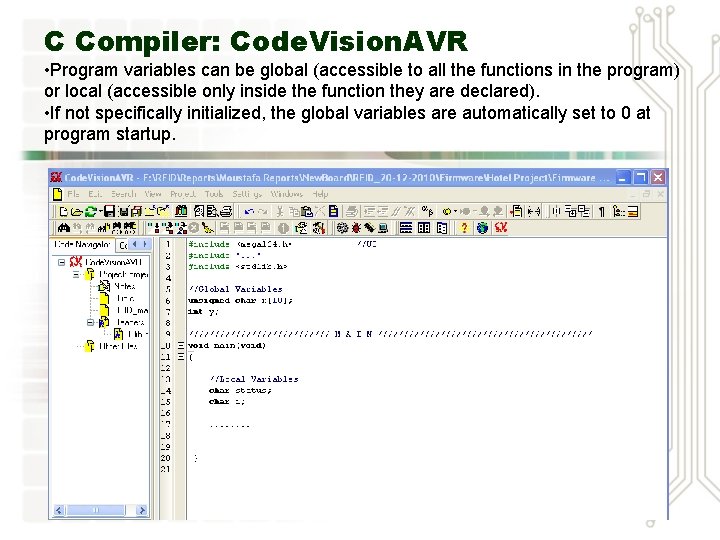

C Compiler: Code. Vision. AVR • Program variables can be global (accessible to all the functions in the program) or local (accessible only inside the function they are declared). • If not specifically initialized, the global variables are automatically set to 0 at program startup.

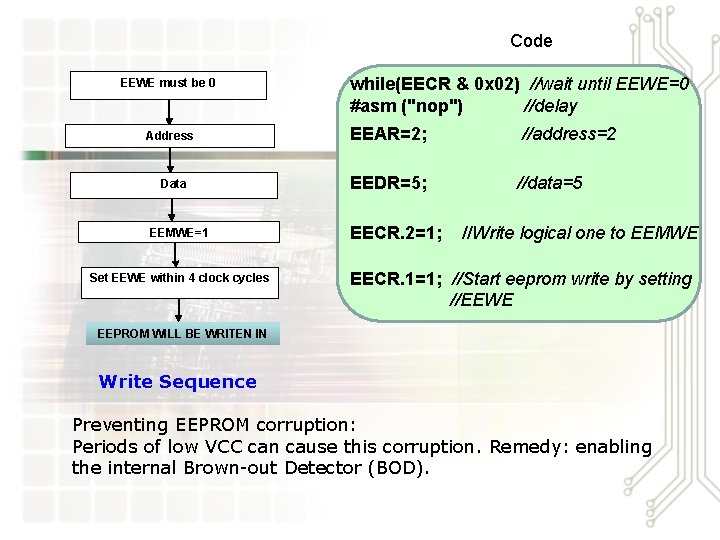

Code EEWE must be 0 Address Data EEMWE=1 Set EEWE within 4 clock cycles while(EECR & 0 x 02) //wait until EEWE=0 #asm ("nop") //delay EEAR=2; //address=2 EEDR=5; //data=5 EECR. 2=1; //Write logical one to EEMWE EECR. 1=1; //Start eeprom write by setting //EEWE EEPROM WILL BE WRITEN IN Write Sequence Preventing EEPROM corruption: Periods of low VCC can cause this corruption. Remedy: enabling the internal Brown-out Detector (BOD).

Specifying the EEPROM Storage Address for Global Variables • To store the integer variable "a“ in EEPROM at address 10 h: eeprom int a @0 x 10;

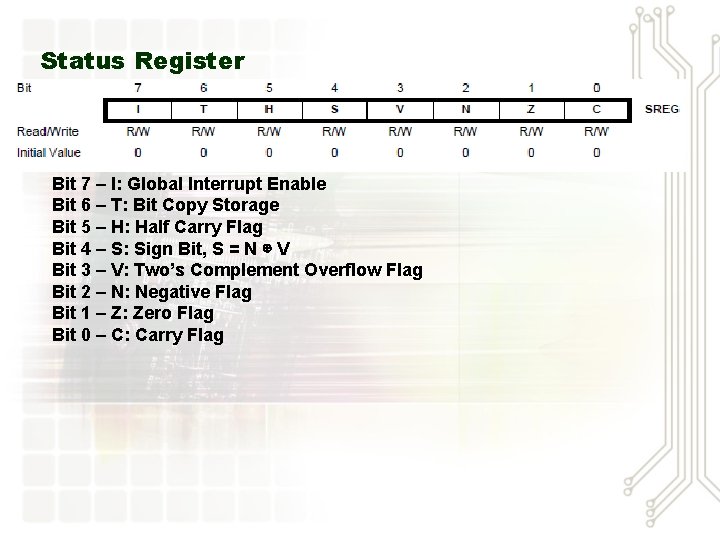

Status Register Bit 7 – I: Global Interrupt Enable Bit 6 – T: Bit Copy Storage Bit 5 – H: Half Carry Flag Bit 4 – S: Sign Bit, S = N ⊕ V Bit 3 – V: Two’s Complement Overflow Flag Bit 2 – N: Negative Flag Bit 1 – Z: Zero Flag Bit 0 – C: Carry Flag

Program Counter • The Program Counter keeps track of the location in flash program memory of the next instruction to be executed. • When the u. C is reset, the Program Counter resets to 000000. • Every instruction fetched causes the Program Counter to increment by the number of bytes of this instruction. • Only by program jumps (conditional, unconditional and interrupts) the contents of the Program Counter are changed. • Also by interrupts, the Program Counter content is stored on the Stack(? ) and a new program location is fetched, and on returning from interrupt the Program Counter regains its value.

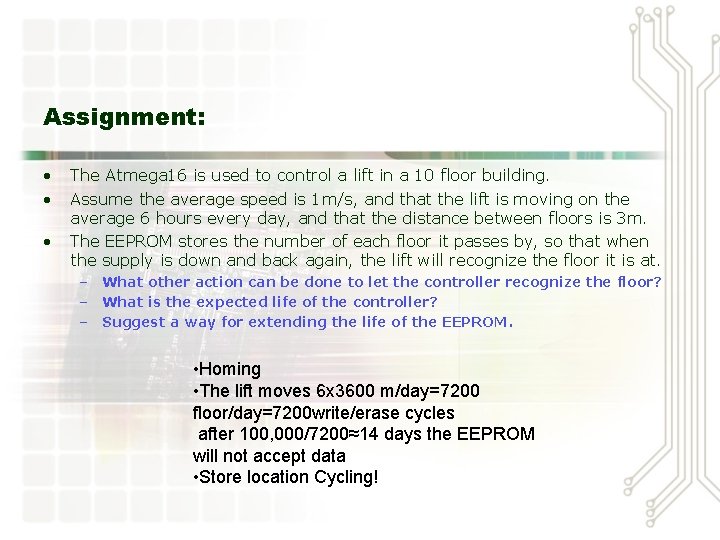

Assignment: • • • The Atmega 16 is used to control a lift in a 10 floor building. Assume the average speed is 1 m/s, and that the lift is moving on the average 6 hours every day, and that the distance between floors is 3 m. The EEPROM stores the number of each floor it passes by, so that when the supply is down and back again, the lift will recognize the floor it is at. – What other action can be done to let the controller recognize the floor? – What is the expected life of the controller? – Suggest a way for extending the life of the EEPROM. • Homing • The lift moves 6 x 3600 m/day=7200 floor/day=7200 write/erase cycles after 100, 000/7200≈14 days the EEPROM will not accept data • Store location Cycling!

- Slides: 12