Jordan University of Science Technology Faculty of Computer

- Slides: 42

Jordan University of Science & Technology Faculty of Computer & Information Technology Computer Engineering Department An Introduction to PIC Microcontrollers Rami Mohammad Al-Sheikh Fady Ahmad Ghanim Supervised by : Dr. Lo’ai Tawalbeh

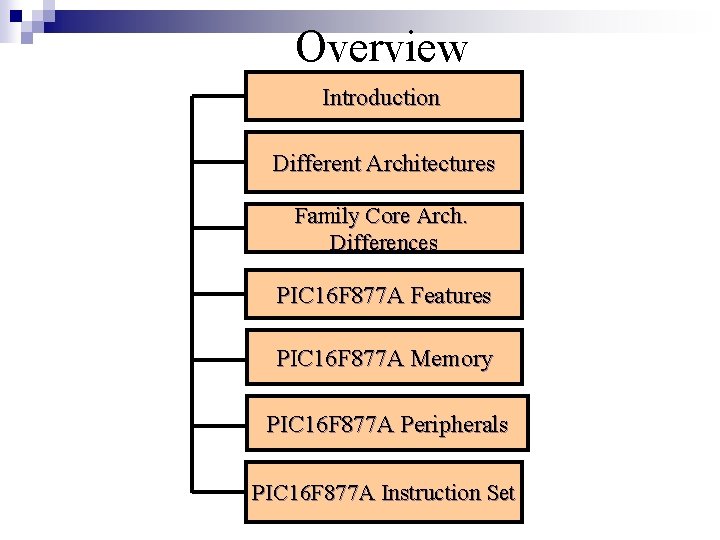

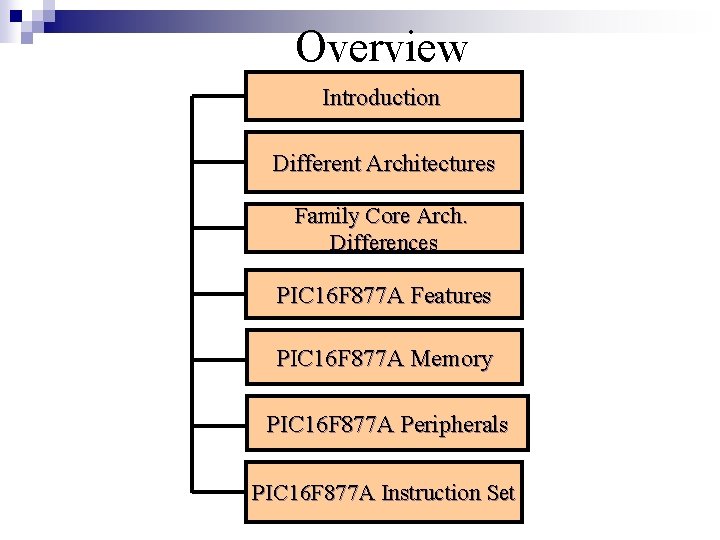

Overview Introduction Different Architectures Family Core Arch. Differences PIC 16 F 877 A Features PIC 16 F 877 A Memory PIC 16 F 877 A Peripherals PIC 16 F 877 A Instruction Set

Introduction n What is PIC? - A family of Harvard architecture microcontrollers made by Microchip Technology - Derived from the PIC 1650 originally developed by General Instrument Microelectronics Division. - The name PIC was originally an acronym for "Programmable Intelligent Computer".

Introduction n Why PIC is popular? ¨ low cost , wide availability with high clock speed ¨ availability of low cost or free development tools ¨ Only 37 instructions to remember ¨ serial programming and re-programming with flash memory capability ¨ Its code is extremely efficient, allowing the PIC to run with typically less program memory than its larger competitors ¨ PIC is very small and easy to implement for noncomplex problems and usually accompanies to the microprocessors as an interface

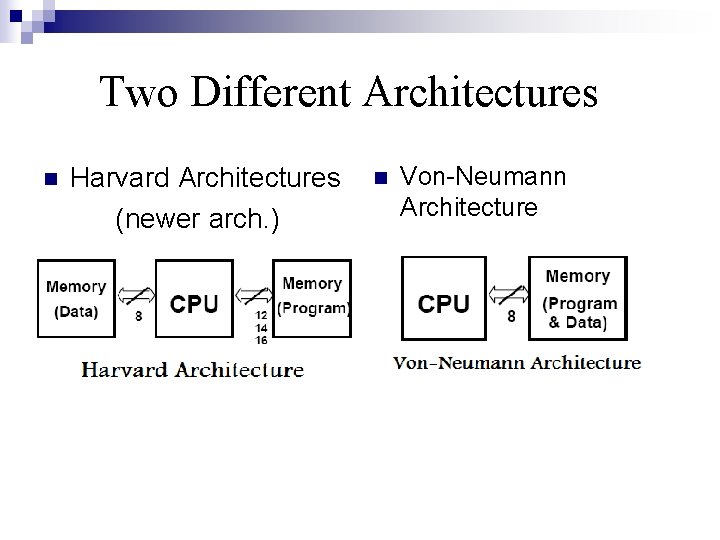

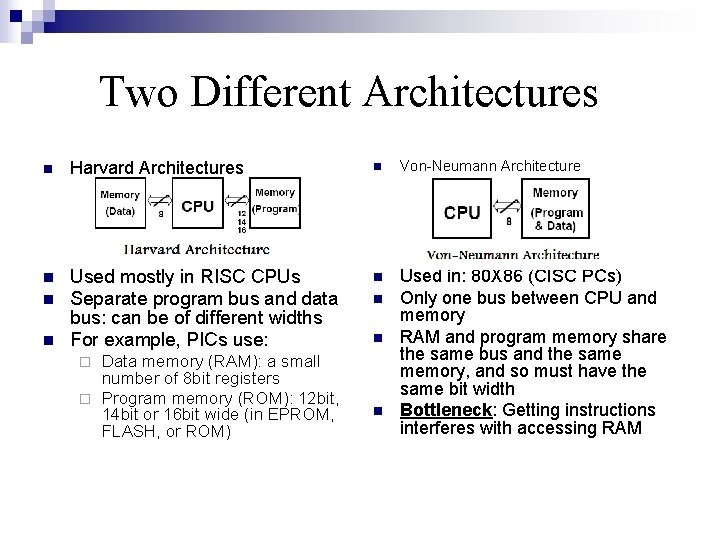

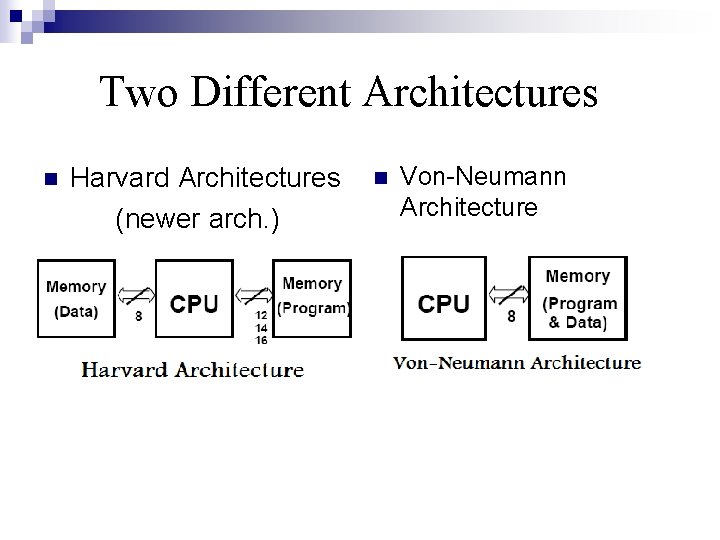

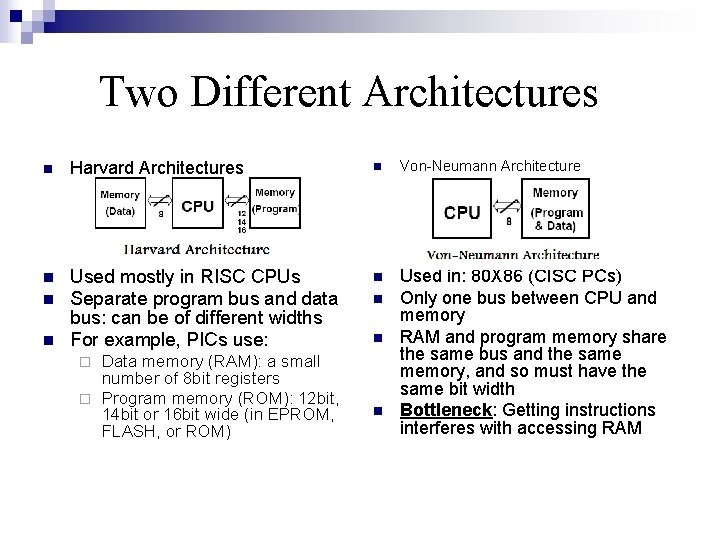

Two Different Architectures n Harvard Architectures (newer arch. ) n Von-Neumann Architecture

Two Different Architectures n Harvard Architectures n Von-Neumann Architecture n Used mostly in RISC CPUs Separate program bus and data bus: can be of different widths For example, PICs use: n Used in: 80 X 86 (CISC PCs) Only one bus between CPU and memory RAM and program memory share the same bus and the same memory, and so must have the same bit width Bottleneck: Getting instructions interferes with accessing RAM n n Data memory (RAM): a small number of 8 bit registers ¨ Program memory (ROM): 12 bit, 14 bit or 16 bit wide (in EPROM, FLASH, or ROM) n n ¨ n

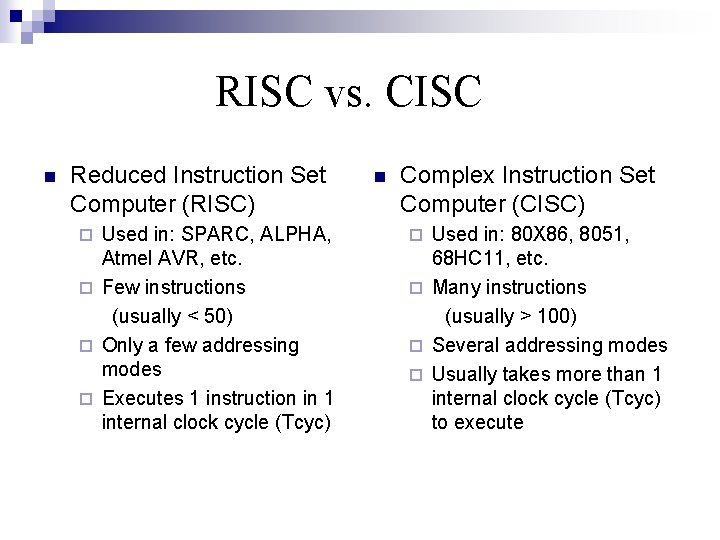

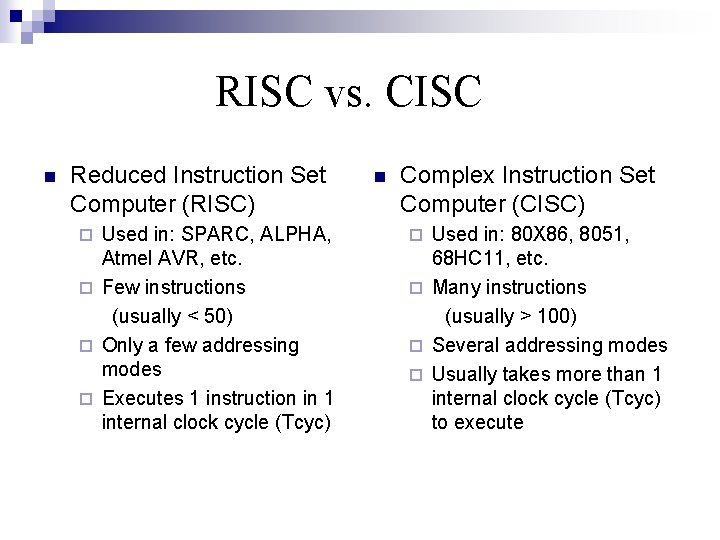

RISC vs. CISC n Reduced Instruction Set Computer (RISC) Used in: SPARC, ALPHA, Atmel AVR, etc. ¨ Few instructions (usually < 50) ¨ Only a few addressing modes ¨ Executes 1 instruction in 1 internal clock cycle (Tcyc) ¨ n Complex Instruction Set Computer (CISC) Used in: 80 X 86, 8051, 68 HC 11, etc. ¨ Many instructions (usually > 100) ¨ Several addressing modes ¨ Usually takes more than 1 internal clock cycle (Tcyc) to execute ¨

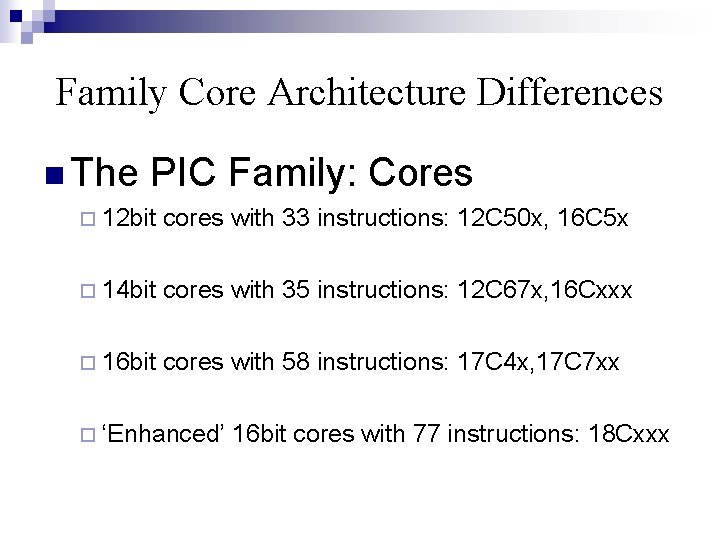

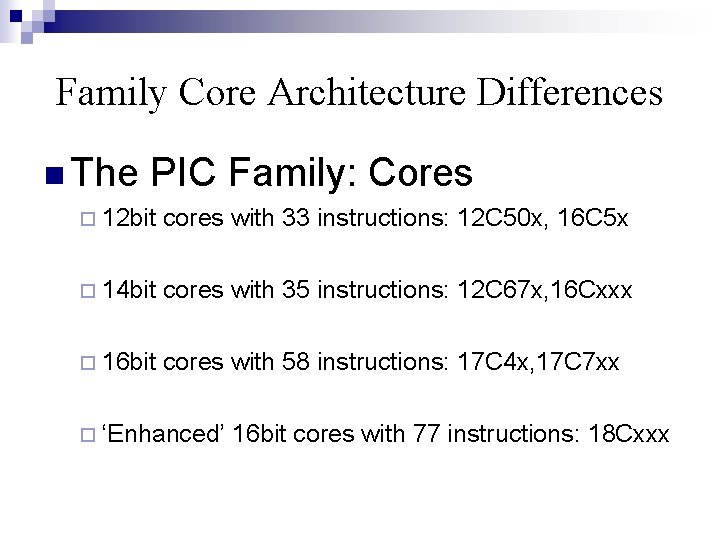

Family Core Architecture Differences n The PIC Family: Cores ¨ 12 bit cores with 33 instructions: 12 C 50 x, 16 C 5 x ¨ 14 bit cores with 35 instructions: 12 C 67 x, 16 Cxxx ¨ 16 bit cores with 58 instructions: 17 C 4 x, 17 C 7 xx ¨ ‘Enhanced’ 16 bit cores with 77 instructions: 18 Cxxx

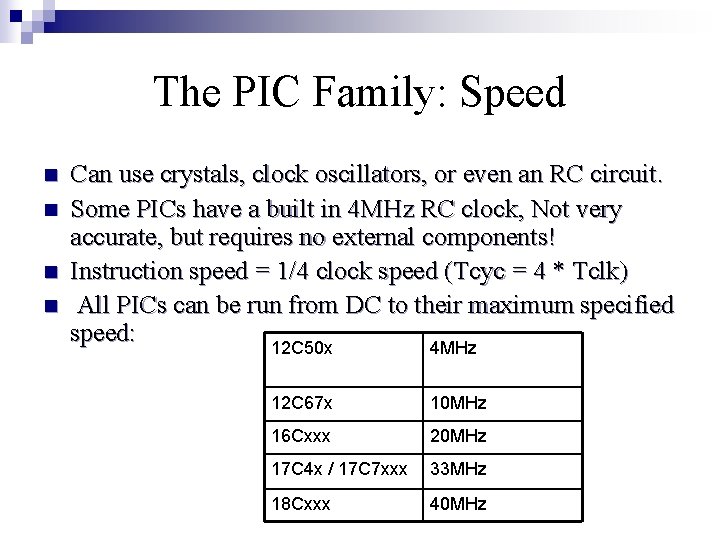

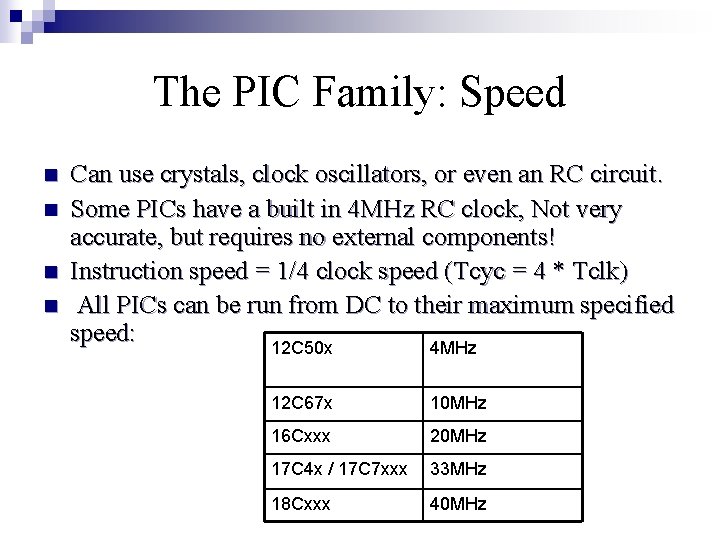

The PIC Family: Speed n n Can use crystals, clock oscillators, or even an RC circuit. Some PICs have a built in 4 MHz RC clock, Not very accurate, but requires no external components! Instruction speed = 1/4 clock speed (Tcyc = 4 * Tclk) All PICs can be run from DC to their maximum specified speed: 12 C 50 x 4 MHz 12 C 67 x 10 MHz 16 Cxxx 20 MHz 17 C 4 x / 17 C 7 xxx 33 MHz 18 Cxxx 40 MHz

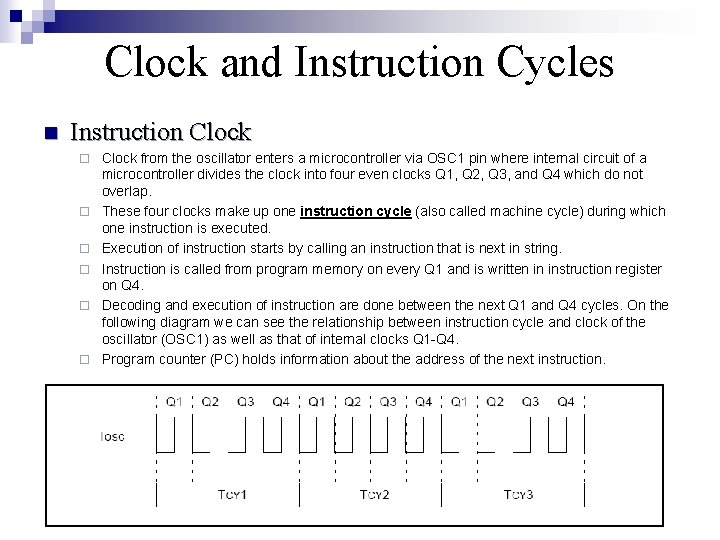

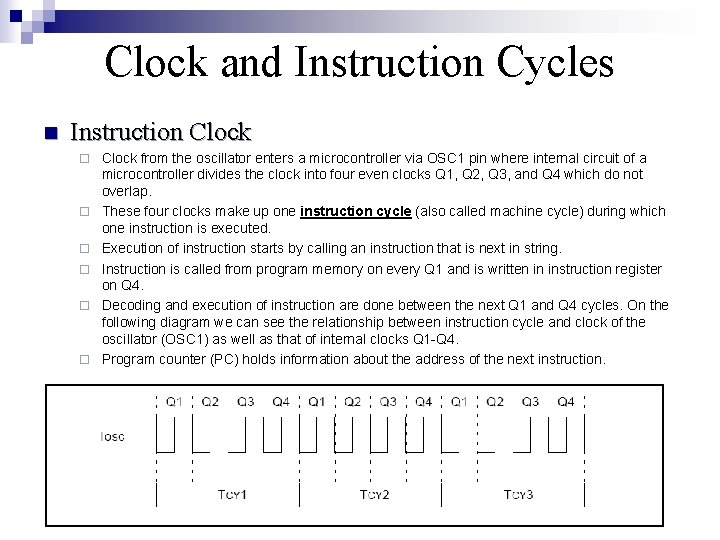

Clock and Instruction Cycles n Instruction Clock ¨ ¨ ¨ Clock from the oscillator enters a microcontroller via OSC 1 pin where internal circuit of a microcontroller divides the clock into four even clocks Q 1, Q 2, Q 3, and Q 4 which do not overlap. These four clocks make up one instruction cycle (also called machine cycle) during which one instruction is executed. Execution of instruction starts by calling an instruction that is next in string. Instruction is called from program memory on every Q 1 and is written in instruction register on Q 4. Decoding and execution of instruction are done between the next Q 1 and Q 4 cycles. On the following diagram we can see the relationship between instruction cycle and clock of the oscillator (OSC 1) as well as that of internal clocks Q 1 -Q 4. Program counter (PC) holds information about the address of the next instruction.

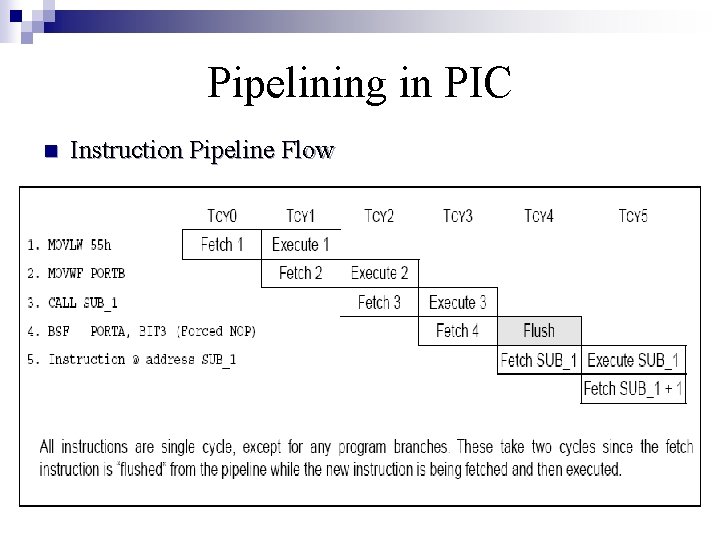

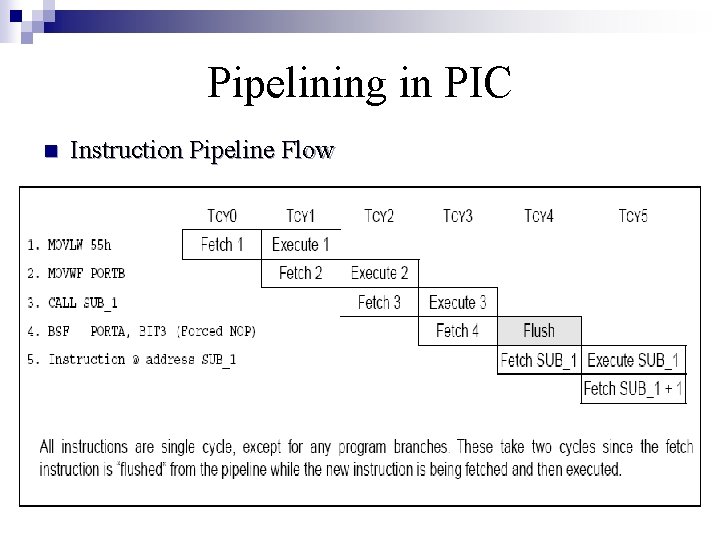

Pipelining in PIC n Instruction Pipeline Flow

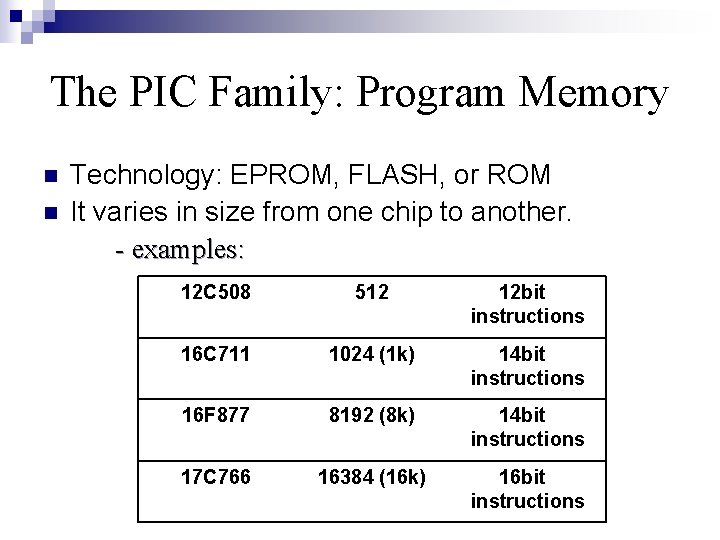

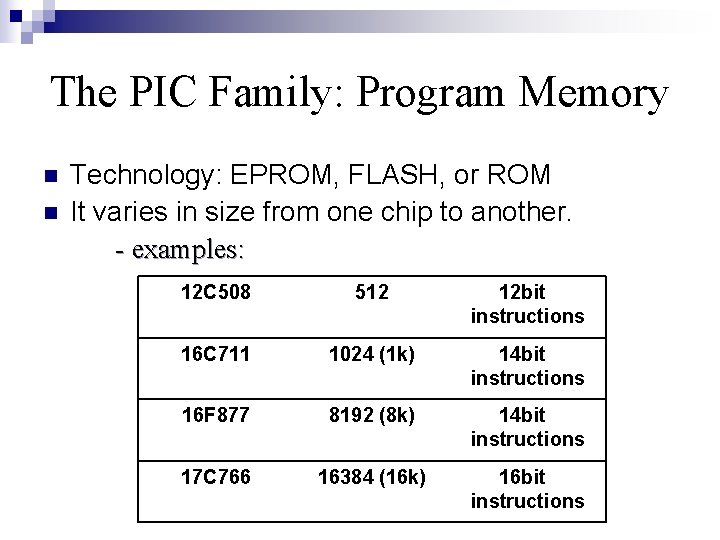

The PIC Family: Program Memory n n Technology: EPROM, FLASH, or ROM It varies in size from one chip to another. - examples: 12 C 508 512 12 bit instructions 16 C 711 1024 (1 k) 14 bit instructions 16 F 877 8192 (8 k) 14 bit instructions 17 C 766 16384 (16 k) 16 bit instructions

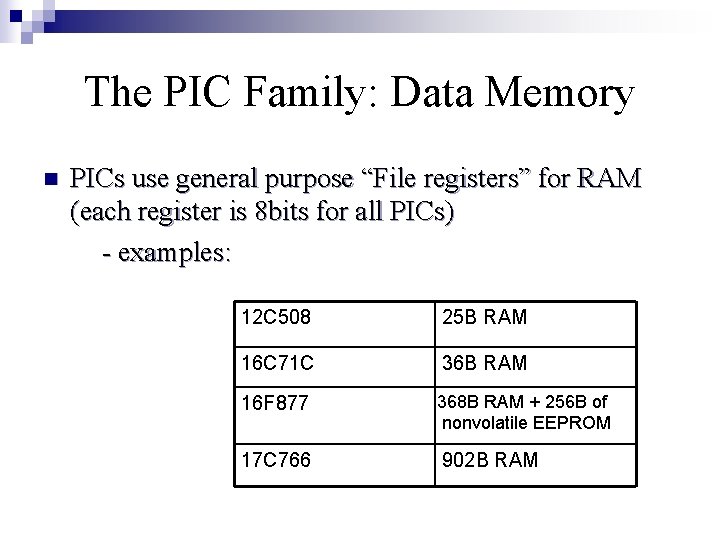

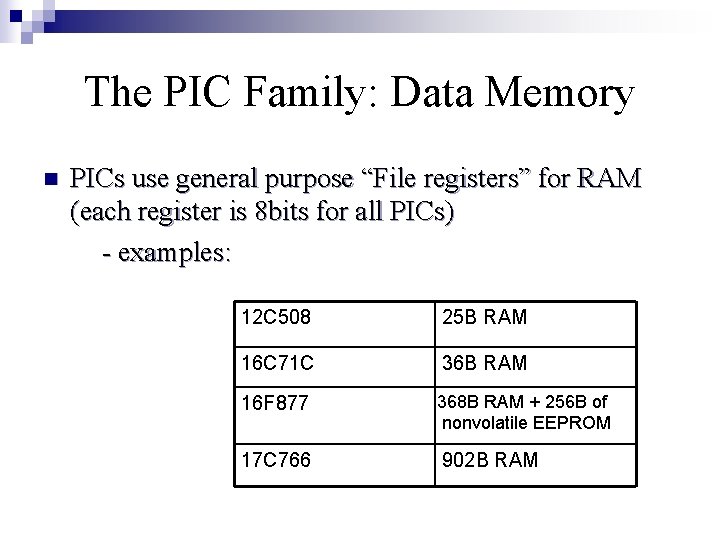

The PIC Family: Data Memory n PICs use general purpose “File registers” for RAM (each register is 8 bits for all PICs) - examples: 12 C 508 25 B RAM 16 C 71 C 36 B RAM 16 F 877 368 B RAM + 256 B of nonvolatile EEPROM 17 C 766 902 B RAM

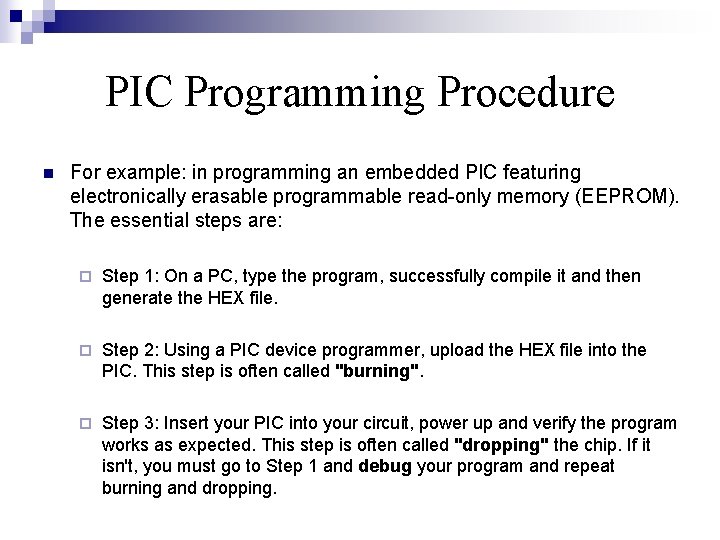

PIC Programming Procedure n For example: in programming an embedded PIC featuring electronically erasable programmable read-only memory (EEPROM). The essential steps are: ¨ Step 1: On a PC, type the program, successfully compile it and then generate the HEX file. ¨ Step 2: Using a PIC device programmer, upload the HEX file into the PIC. This step is often called "burning". ¨ Step 3: Insert your PIC into your circuit, power up and verify the program works as expected. This step is often called "dropping" the chip. If it isn't, you must go to Step 1 and debug your program and repeat burning and dropping.

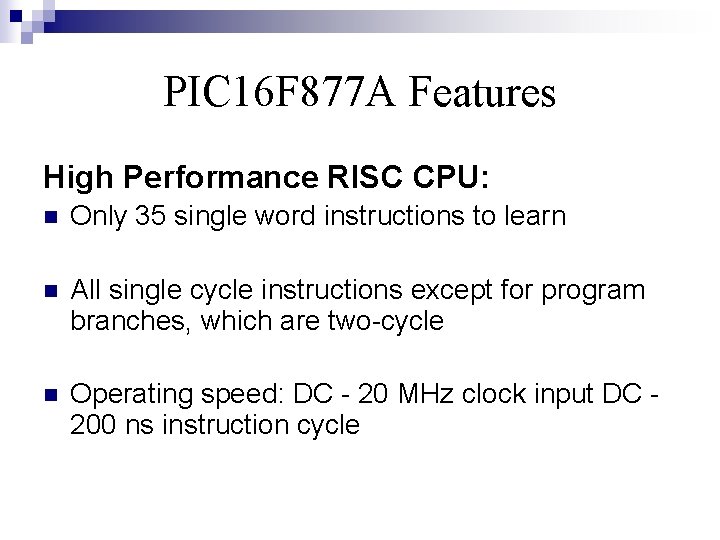

PIC 16 F 877 A Features High Performance RISC CPU: n Only 35 single word instructions to learn n All single cycle instructions except for program branches, which are two-cycle n Operating speed: DC - 20 MHz clock input DC 200 ns instruction cycle

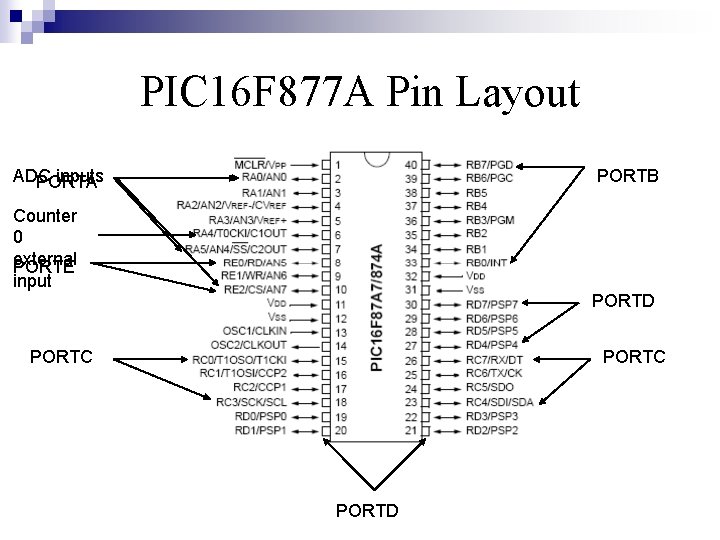

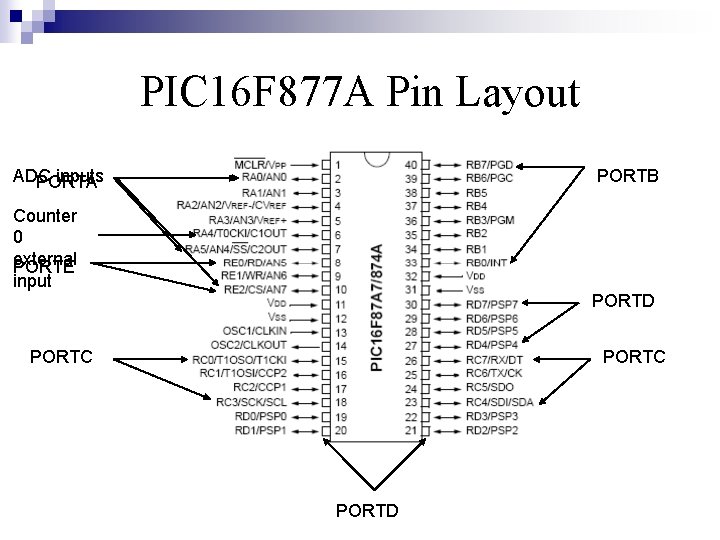

PIC 16 F 877 A Pin Layout ADC inputs PORTA PORTB Counter 0 external PORTE input PORTD PORTC PORTD

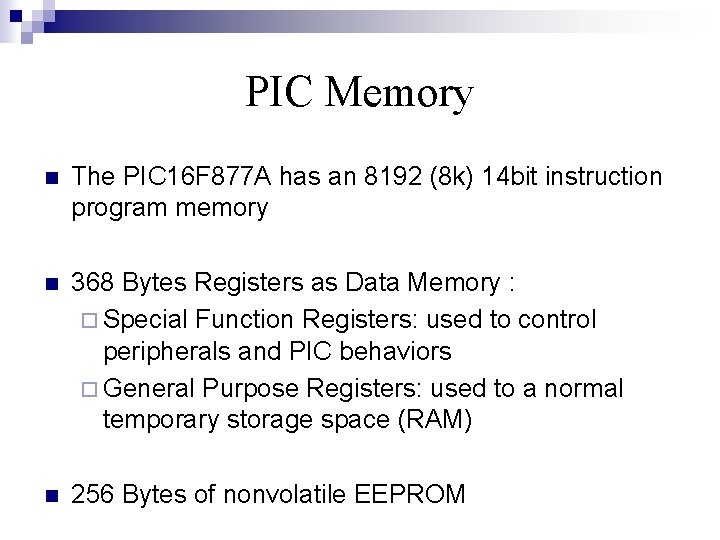

PIC Memory n The PIC 16 F 877 A has an 8192 (8 k) 14 bit instruction program memory n 368 Bytes Registers as Data Memory : ¨ Special Function Registers: used to control peripherals and PIC behaviors ¨ General Purpose Registers: used to a normal temporary storage space (RAM) n 256 Bytes of nonvolatile EEPROM

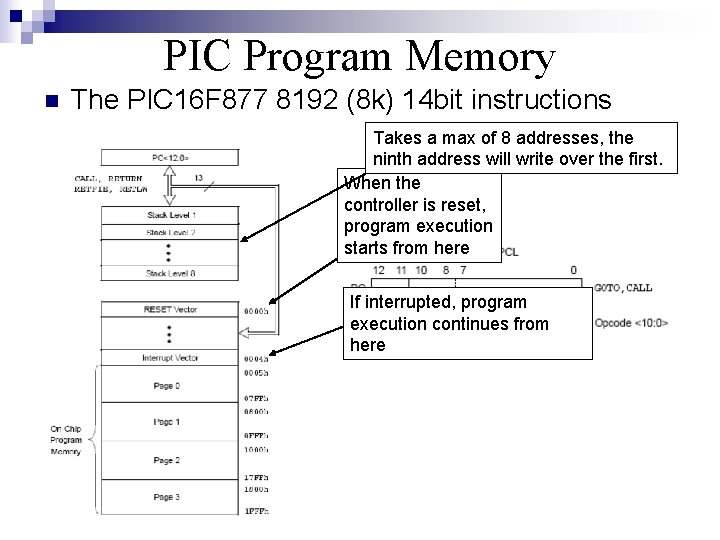

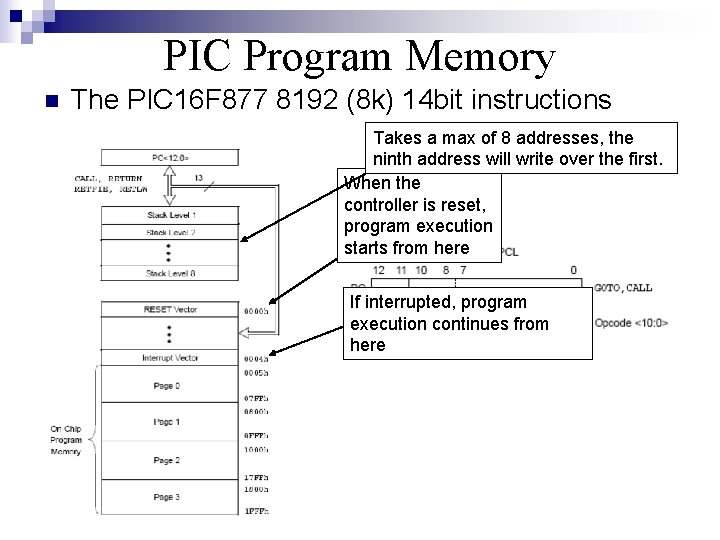

PIC Program Memory n The PIC 16 F 877 8192 (8 k) 14 bit instructions Takes a max of 8 addresses, the ninth address will write over the first. When the controller is reset, program execution starts from here If interrupted, program execution continues from here

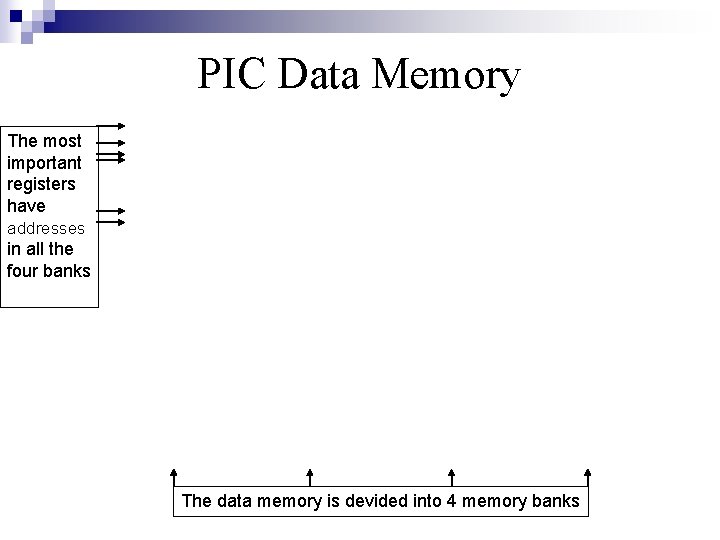

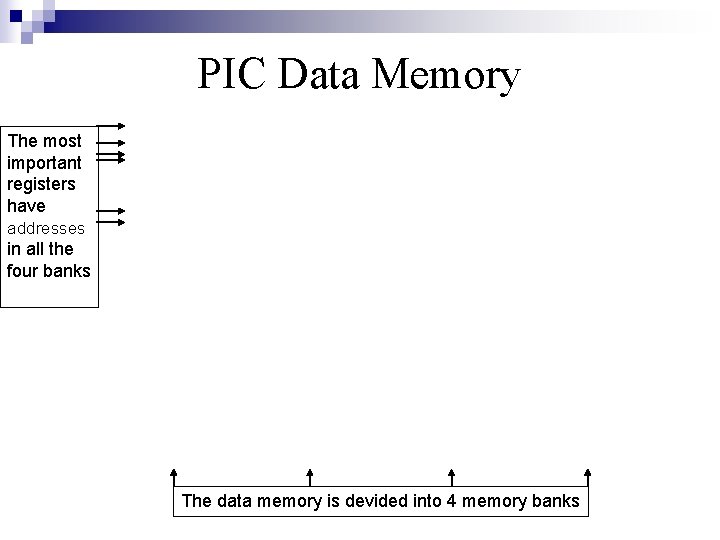

PIC Data Memory The most important registers have addresses in all the four banks The data memory is devided into 4 memory banks

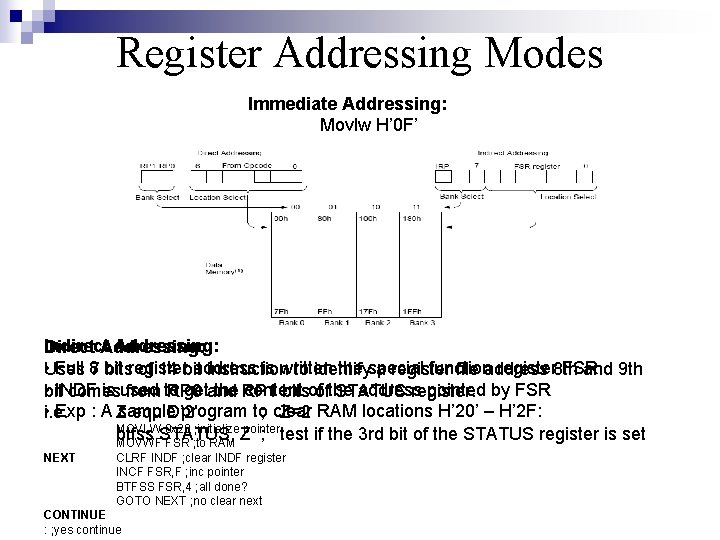

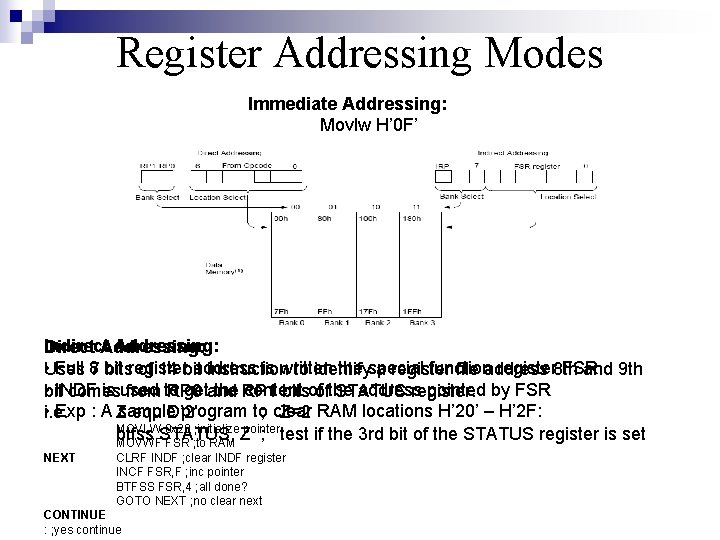

Register Addressing Modes Immediate Addressing: Movlw H’ 0 F’ Indirect. Addressing: Direct • Full 8 is written the special function register 8 th FSR Uses 7 bitsregister of 14 bitaddress instruction to identify a register file address and 9 th • bit. INDF is used getand the RP 1 content address pointed by FSR comes from to RP 0 bitsofofthe STATUS register. • Exp : A Zsample program to; clear i. e. equ D’ 2’ Z=2 RAM locations H’ 20’ – H’ 2 F: MOVLW 0 x 20 ; initialize pointer btfss STATUS, Z ; test if the 3 rd bit of the STATUS register is set MOVWF FSR ; to RAM NEXT CLRF INDF ; clear INDF register INCF FSR, F ; inc pointer BTFSS FSR, 4 ; all done? GOTO NEXT ; no clear next CONTINUE : ; yes continue

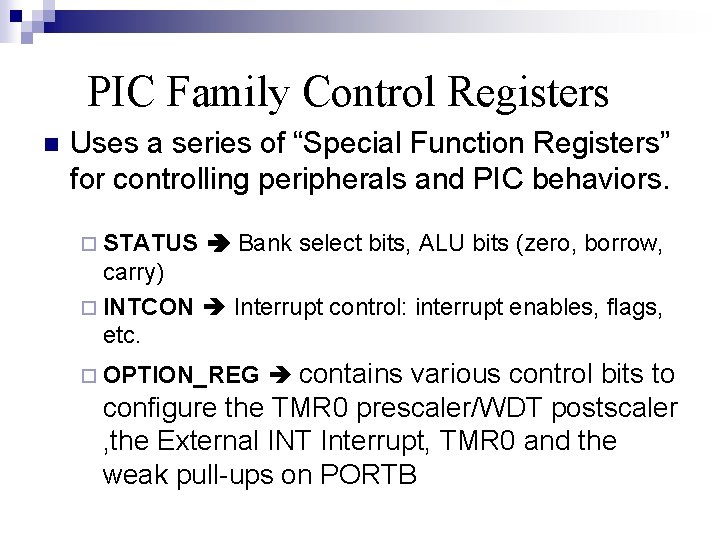

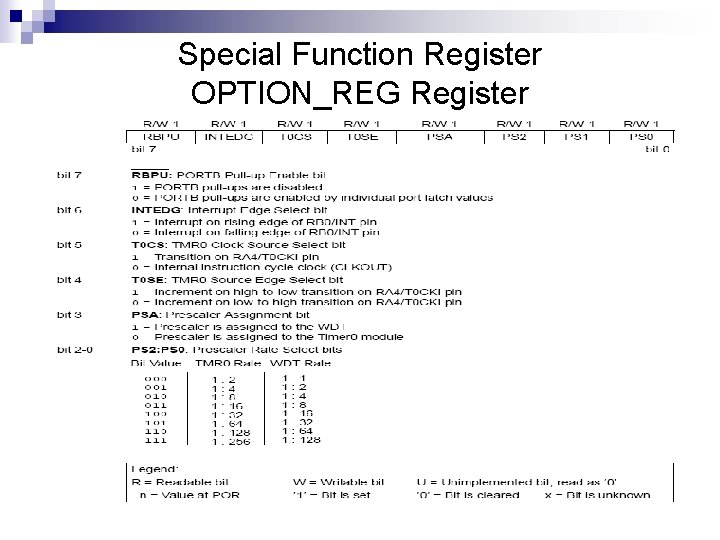

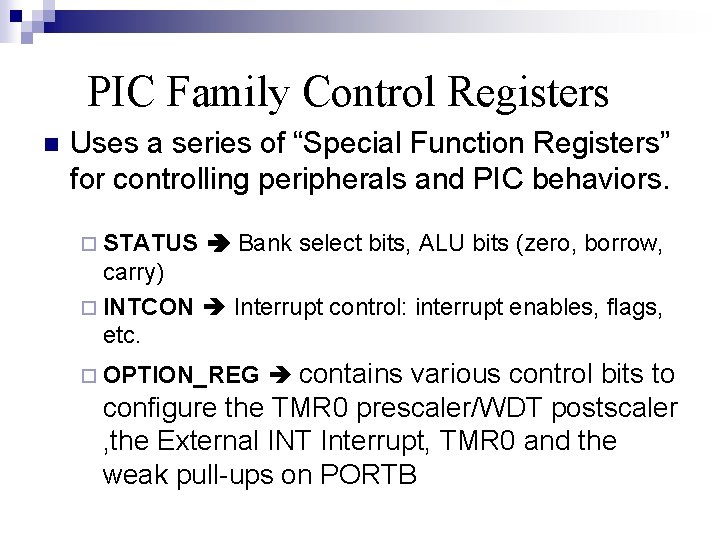

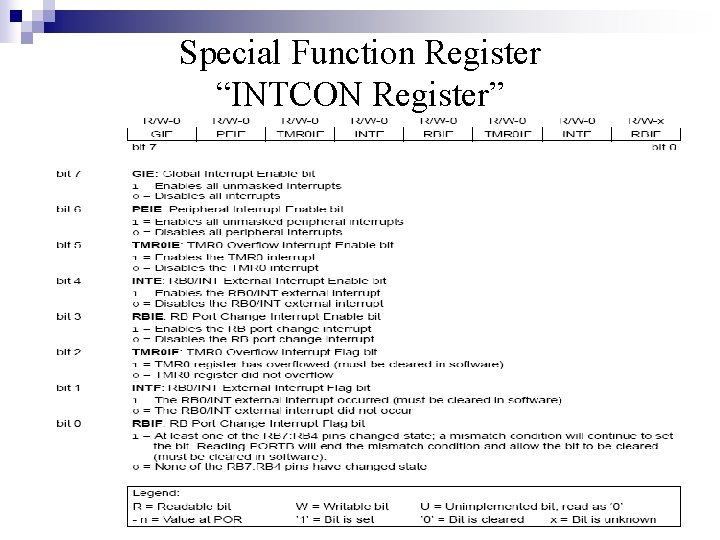

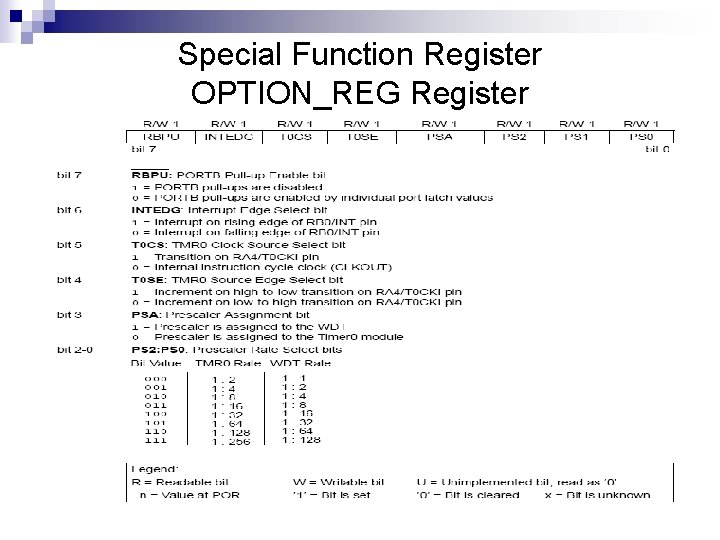

PIC Family Control Registers n Uses a series of “Special Function Registers” for controlling peripherals and PIC behaviors. ¨ STATUS Bank select bits, ALU bits (zero, borrow, carry) ¨ INTCON Interrupt control: interrupt enables, flags, etc. ¨ OPTION_REG contains various control bits to configure the TMR 0 prescaler/WDT postscaler , the External INT Interrupt, TMR 0 and the weak pull-ups on PORTB

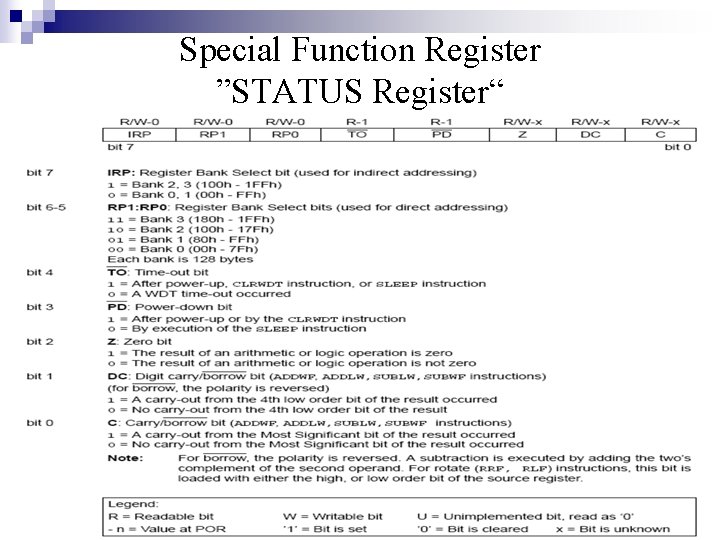

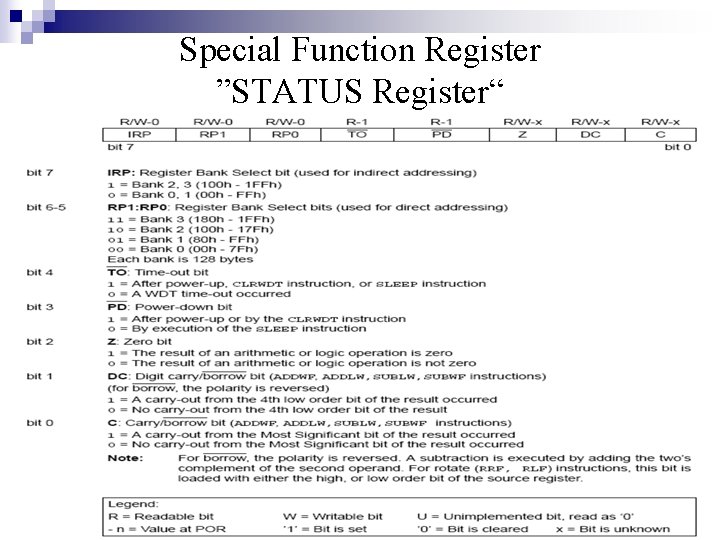

Special Function Register ”STATUS Register“

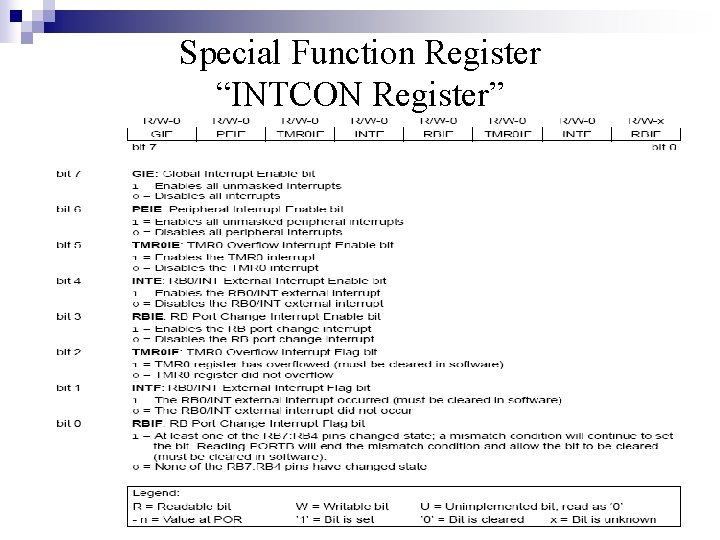

Special Function Register “INTCON Register”

PIC Peripherals n Each peripheral has a set of SFRs to control its operation. n Different PICs have different on-board peripherals

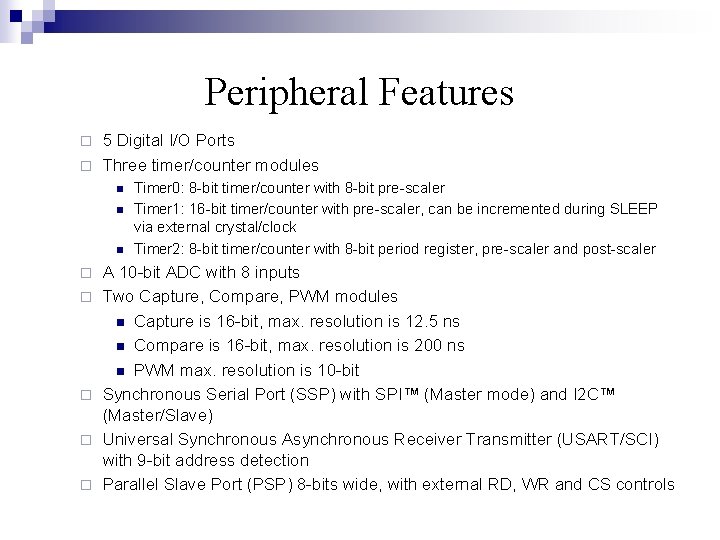

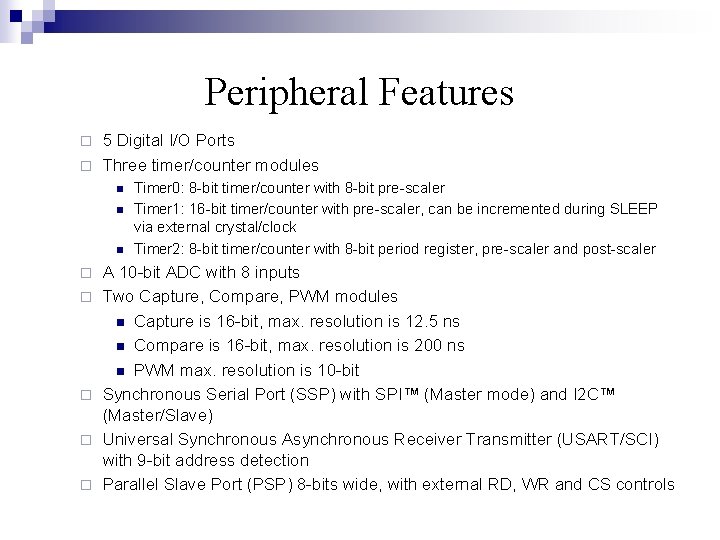

Peripheral Features 5 Digital I/O Ports ¨ Three timer/counter modules ¨ n n n ¨ ¨ ¨ Timer 0: 8 -bit timer/counter with 8 -bit pre-scaler Timer 1: 16 -bit timer/counter with pre-scaler, can be incremented during SLEEP via external crystal/clock Timer 2: 8 -bit timer/counter with 8 -bit period register, pre-scaler and post-scaler A 10 -bit ADC with 8 inputs Two Capture, Compare, PWM modules n Capture is 16 -bit, max. resolution is 12. 5 ns n Compare is 16 -bit, max. resolution is 200 ns n PWM max. resolution is 10 -bit Synchronous Serial Port (SSP) with SPI™ (Master mode) and I 2 C™ (Master/Slave) Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI) with 9 -bit address detection Parallel Slave Port (PSP) 8 -bits wide, with external RD, WR and CS controls

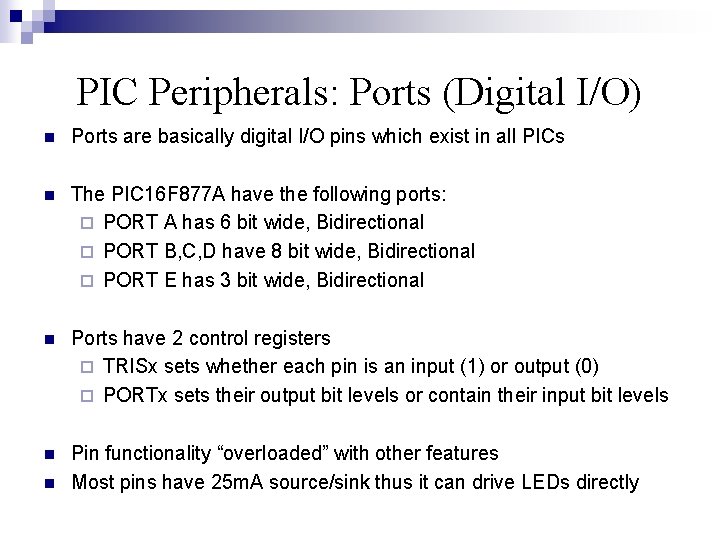

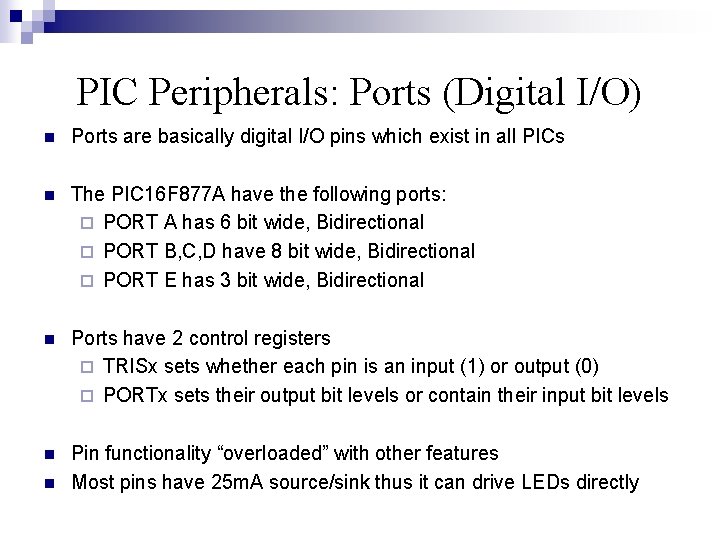

PIC Peripherals: Ports (Digital I/O) n Ports are basically digital I/O pins which exist in all PICs n The PIC 16 F 877 A have the following ports: ¨ PORT A has 6 bit wide, Bidirectional ¨ PORT B, C, D have 8 bit wide, Bidirectional ¨ PORT E has 3 bit wide, Bidirectional n Ports have 2 control registers ¨ TRISx sets whether each pin is an input (1) or output (0) ¨ PORTx sets their output bit levels or contain their input bit levels n Pin functionality “overloaded” with other features Most pins have 25 m. A source/sink thus it can drive LEDs directly n

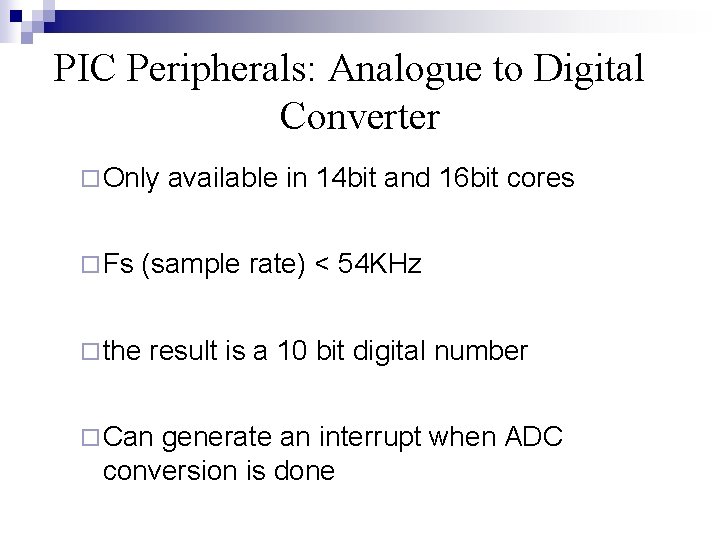

PIC Peripherals: Analogue to Digital Converter ¨ Only ¨ Fs available in 14 bit and 16 bit cores (sample rate) < 54 KHz ¨ the result is a 10 bit digital number ¨ Can generate an interrupt when ADC conversion is done

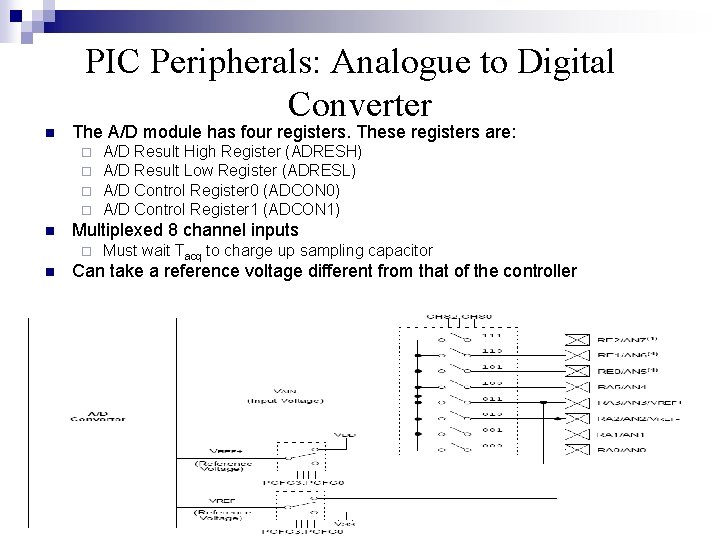

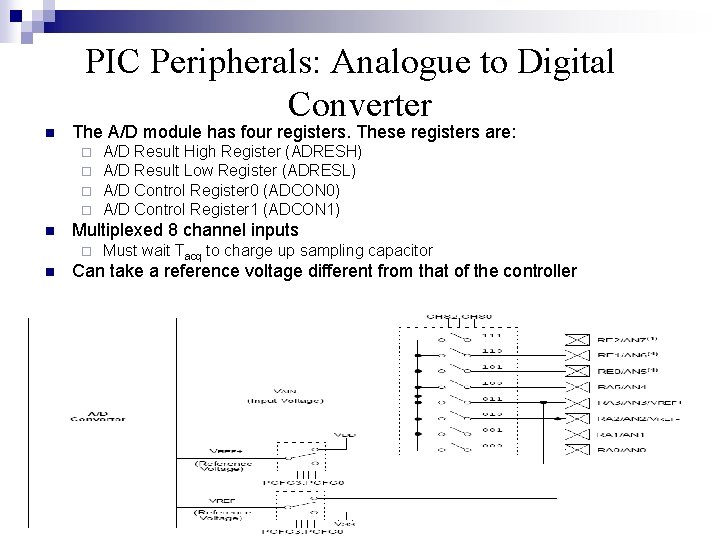

PIC Peripherals: Analogue to Digital Converter n The A/D module has four registers. These registers are: ¨ ¨ n Multiplexed 8 channel inputs ¨ n A/D Result High Register (ADRESH) A/D Result Low Register (ADRESL) A/D Control Register 0 (ADCON 0) A/D Control Register 1 (ADCON 1) Must wait Tacq to charge up sampling capacitor Can take a reference voltage different from that of the controller

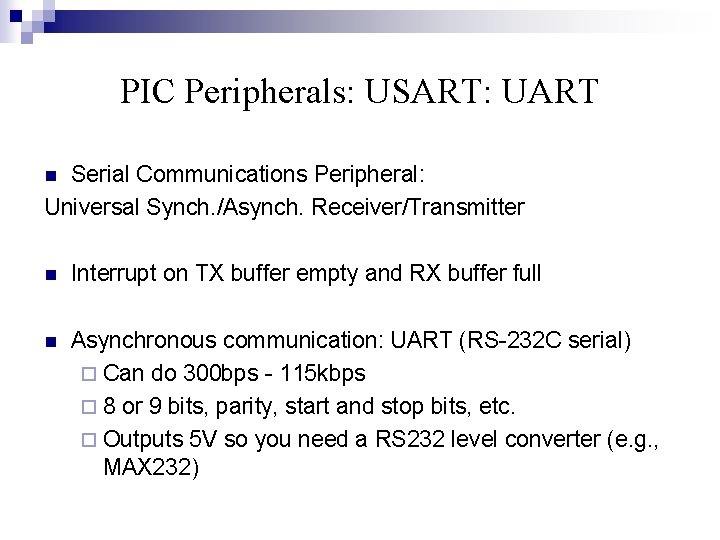

PIC Peripherals: USART: UART Serial Communications Peripheral: Universal Synch. /Asynch. Receiver/Transmitter n n Interrupt on TX buffer empty and RX buffer full n Asynchronous communication: UART (RS-232 C serial) ¨ Can do 300 bps - 115 kbps ¨ 8 or 9 bits, parity, start and stop bits, etc. ¨ Outputs 5 V so you need a RS 232 level converter (e. g. , MAX 232)

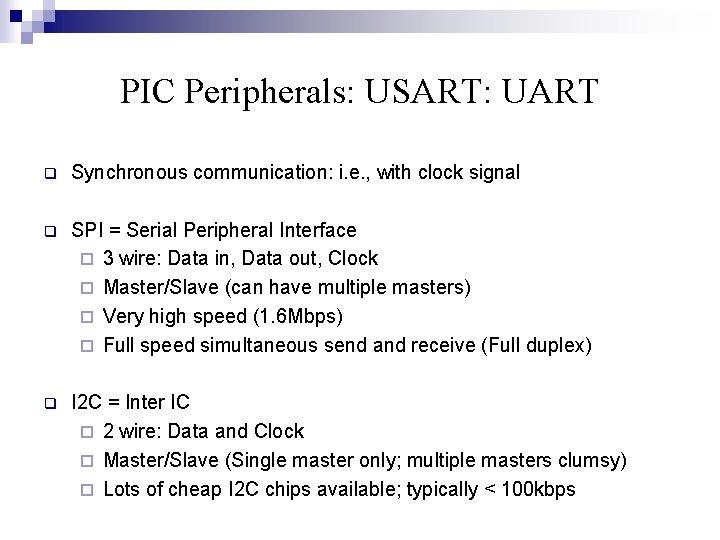

PIC Peripherals: USART: UART q Synchronous communication: i. e. , with clock signal q SPI = Serial Peripheral Interface ¨ 3 wire: Data in, Data out, Clock ¨ Master/Slave (can have multiple masters) ¨ Very high speed (1. 6 Mbps) ¨ Full speed simultaneous send and receive (Full duplex) q I 2 C = Inter IC ¨ 2 wire: Data and Clock ¨ Master/Slave (Single master only; multiple masters clumsy) ¨ Lots of cheap I 2 C chips available; typically < 100 kbps

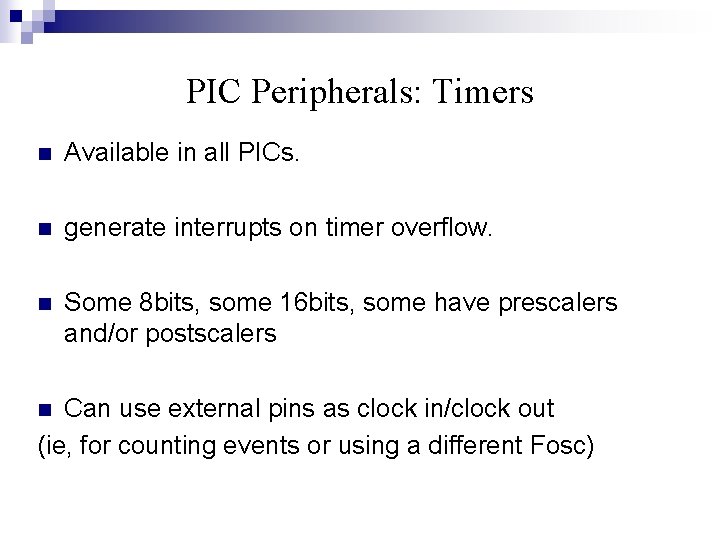

PIC Peripherals: Timers n Available in all PICs. n generate interrupts on timer overflow. n Some 8 bits, some 16 bits, some have prescalers and/or postscalers Can use external pins as clock in/clock out (ie, for counting events or using a different Fosc) n

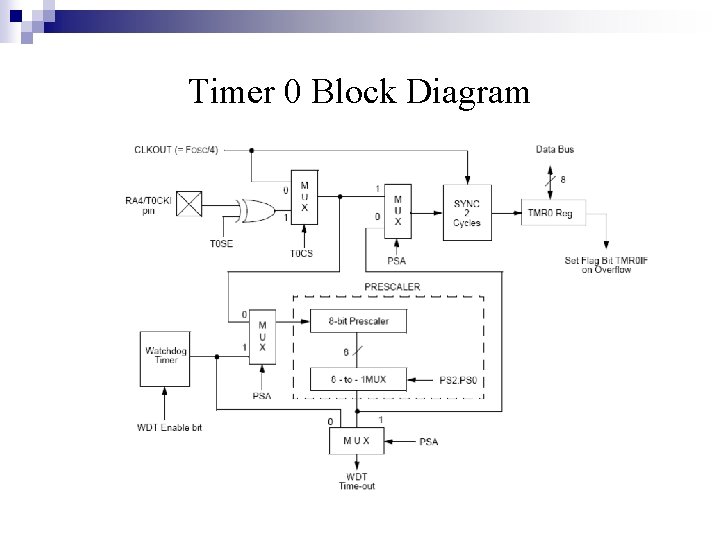

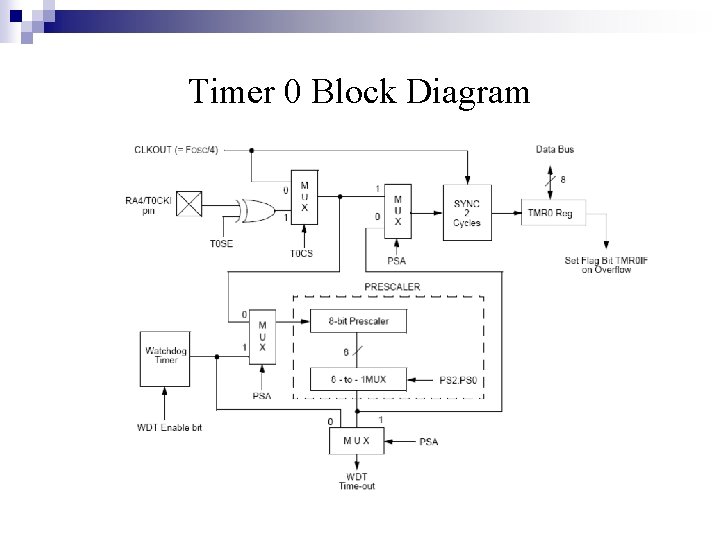

Timer 0 Block Diagram

Special Function Register OPTION_REG Register

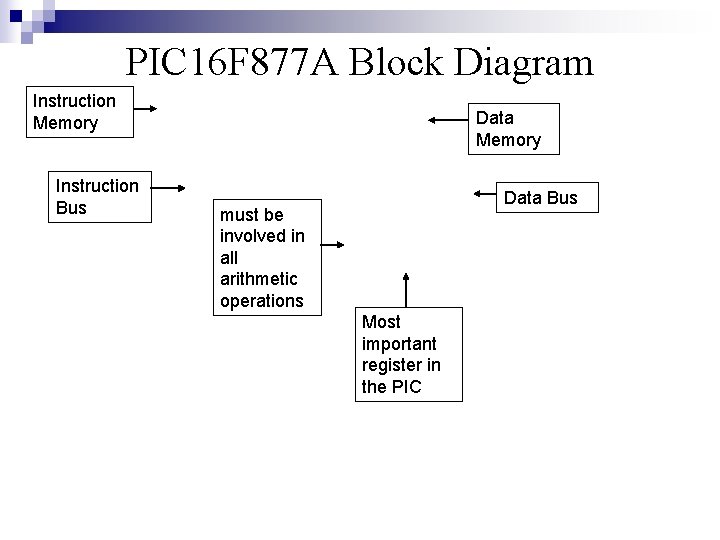

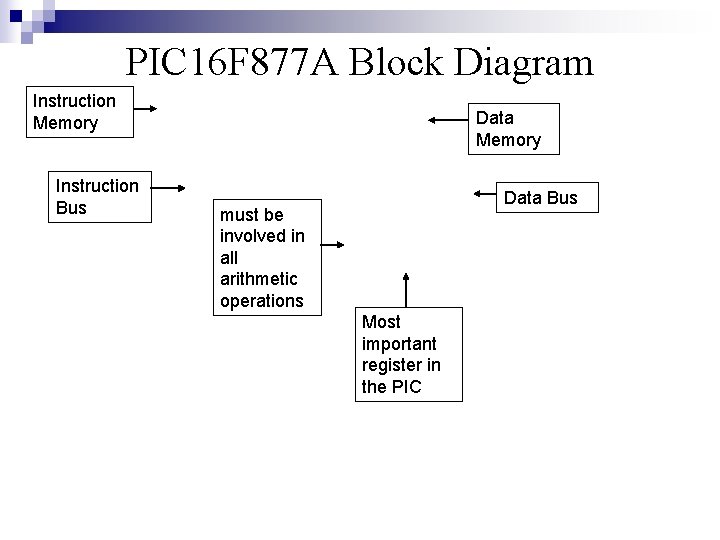

PIC 16 F 877 A Block Diagram Instruction Memory Instruction Bus Data Memory Data Bus must be involved in all arithmetic operations Most important register in the PIC

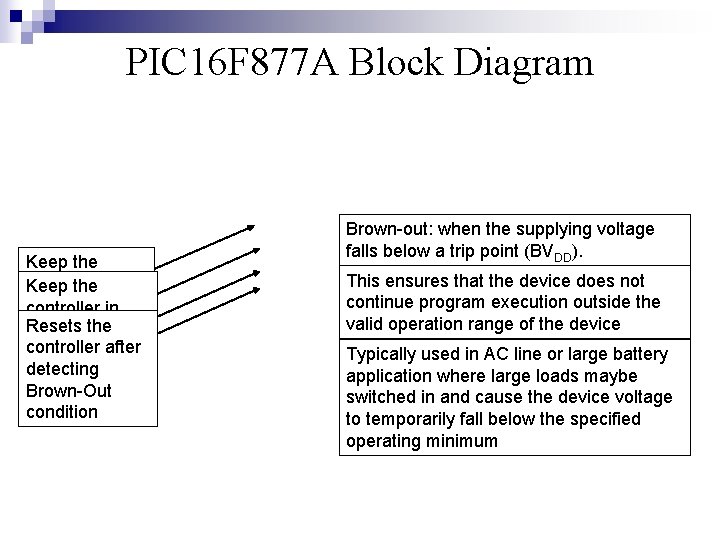

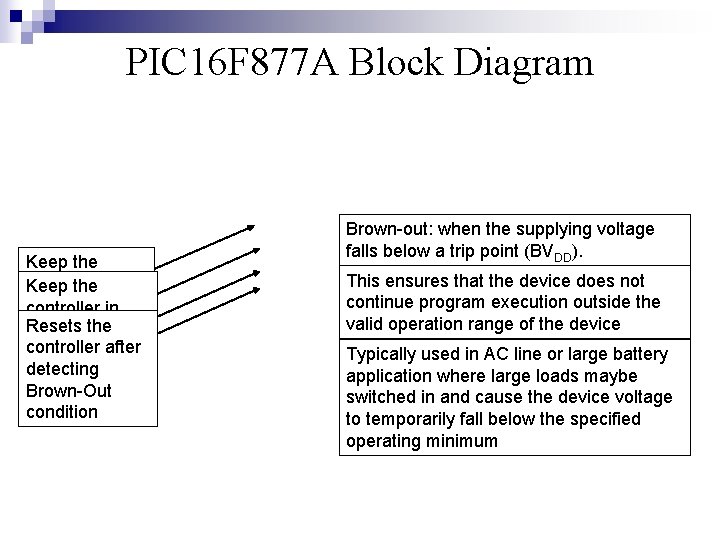

PIC 16 F 877 A Block Diagram Keep the controller Keep the in reset state controller Resets theinuntil Resets theafter powerstate reaches reset until controller after anspecified acceptable the oscillator is a time detecting level & steady started & stable Brown-Out condition Brown-out: when the supplying voltage falls below a trip point (BVDD). This ensures that the device does not continue program execution outside the valid operation range of the device Typically used in AC line or large battery application where large loads maybe switched in and cause the device voltage to temporarily fall below the specified operating minimum

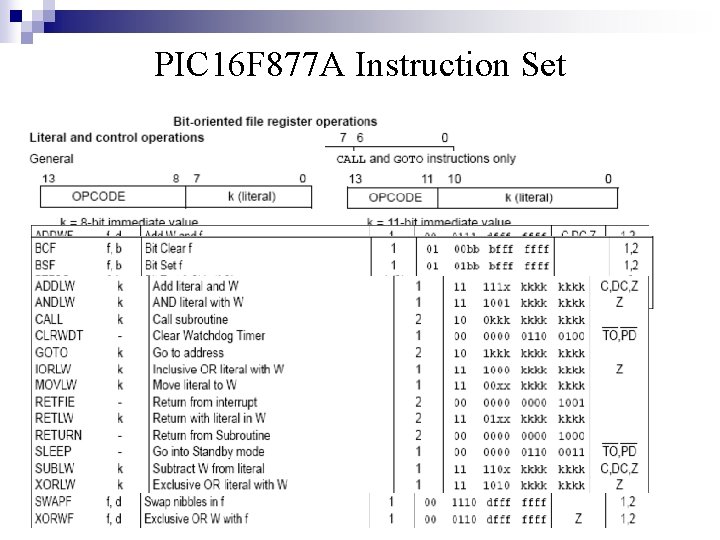

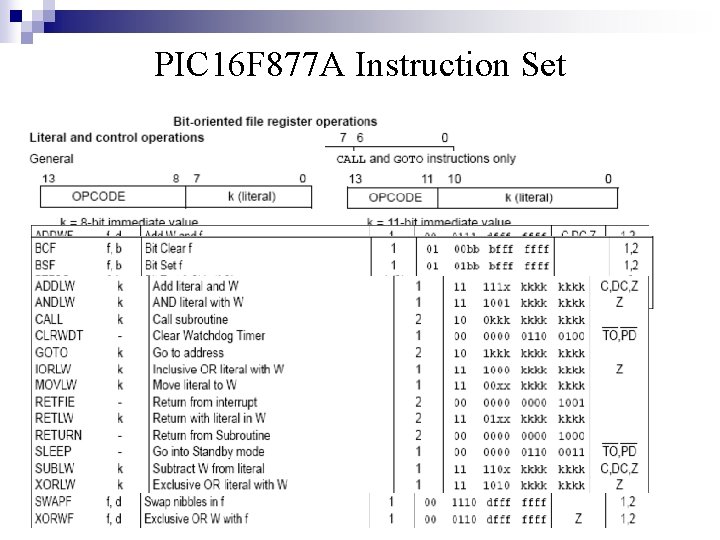

PIC 16 F 877 A Instruction Set

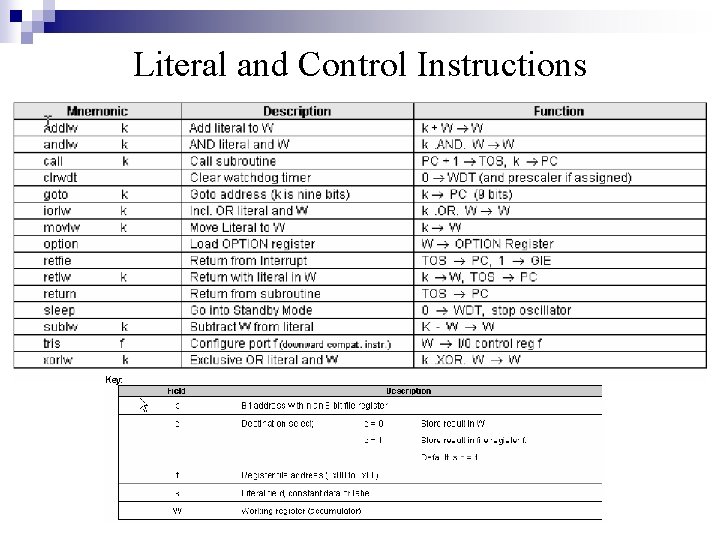

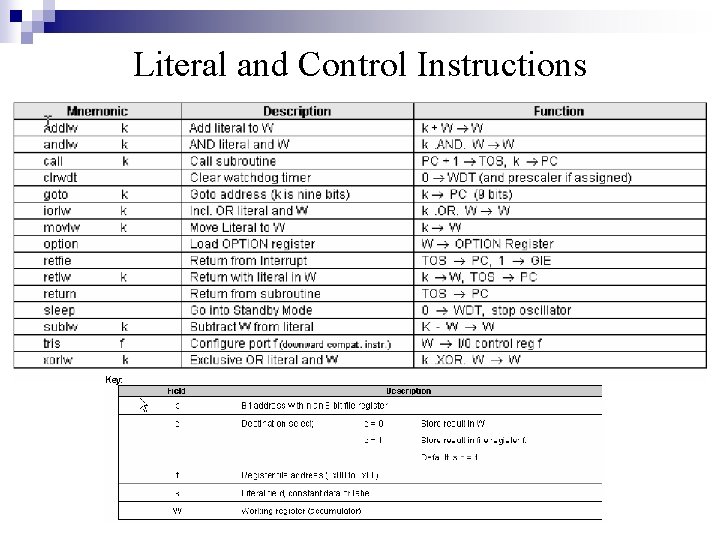

Literal and Control Instructions

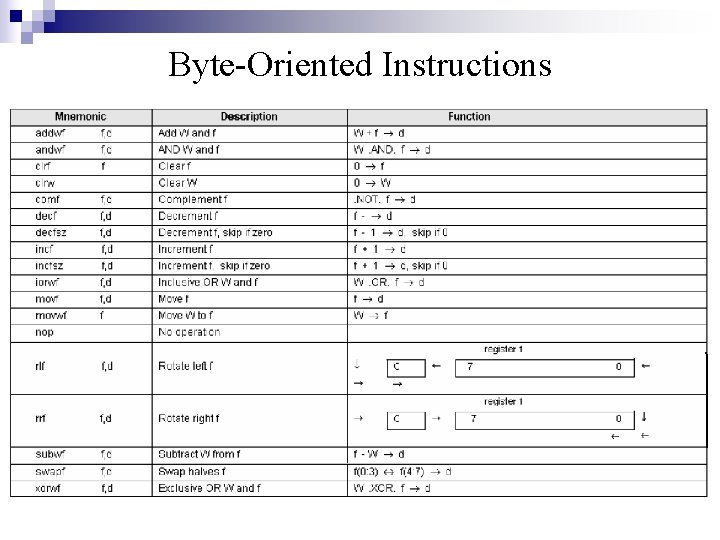

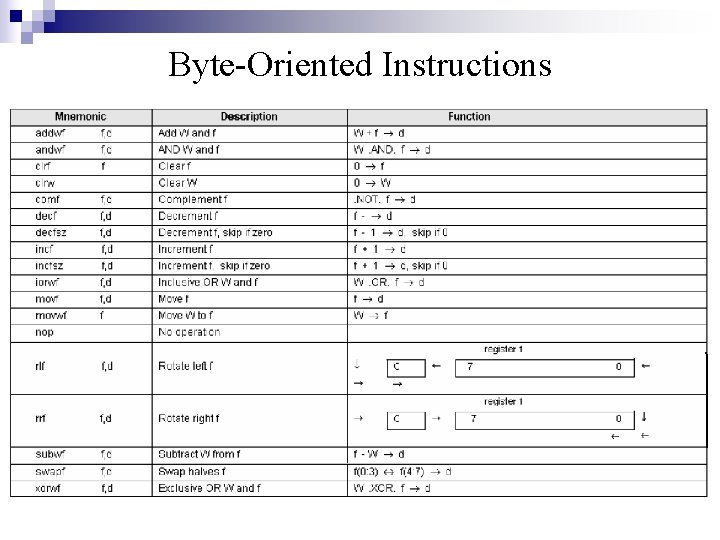

Byte-Oriented Instructions

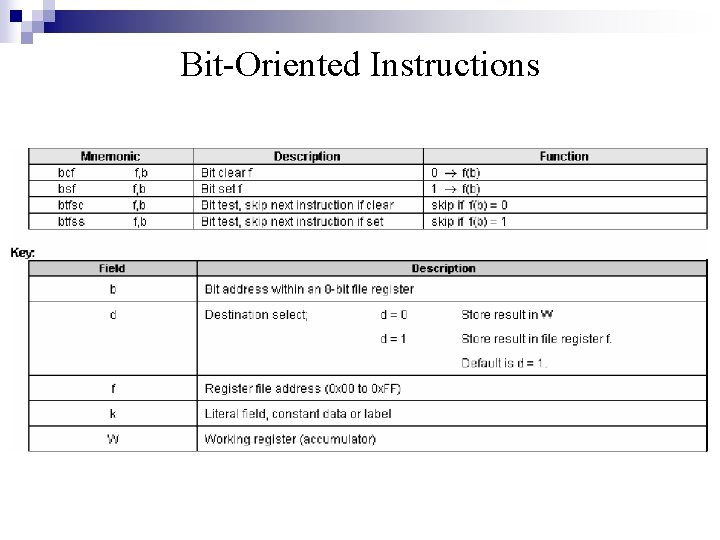

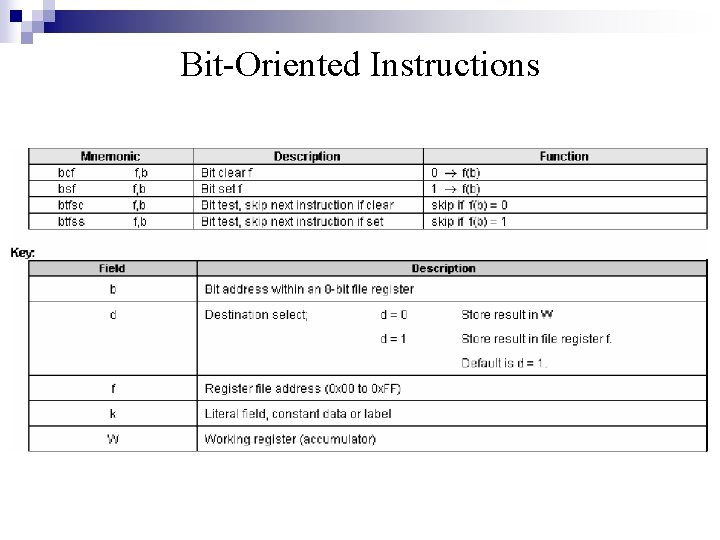

Bit-Oriented Instructions

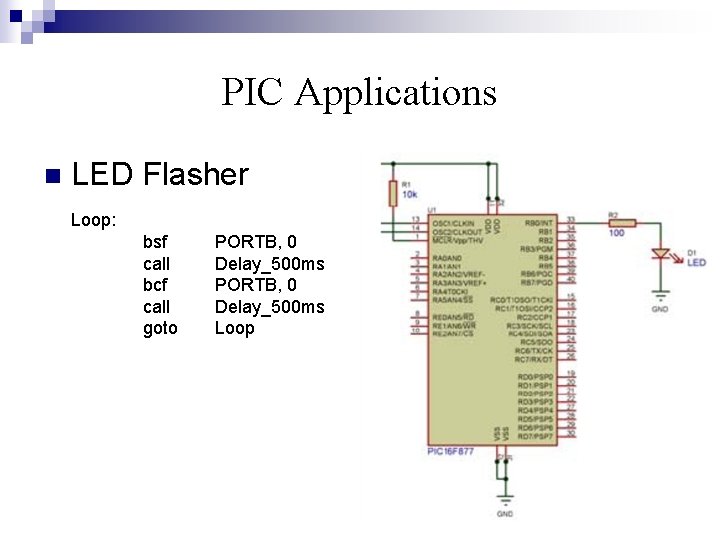

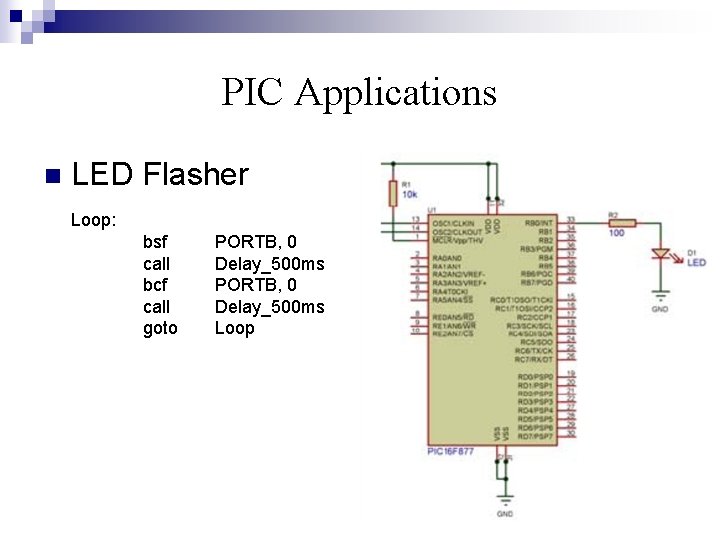

PIC Applications n LED Flasher Loop: bsf call bcf call goto PORTB, 0 Delay_500 ms Loop

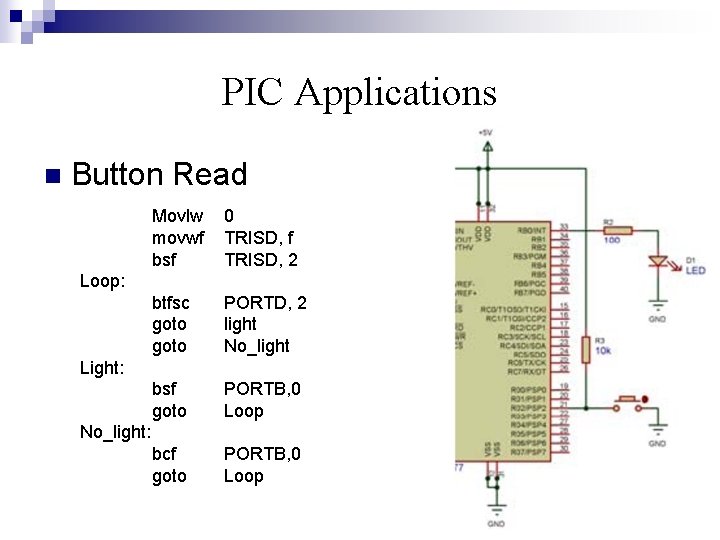

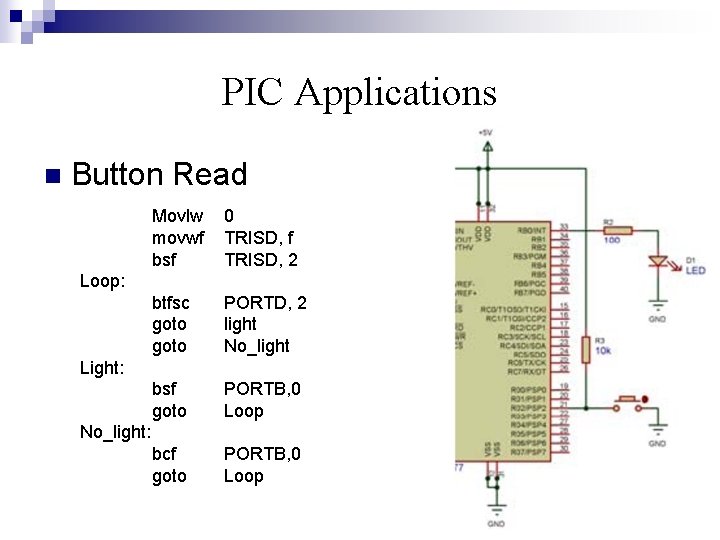

PIC Applications n Button Read Movlw movwf bsf 0 TRISD, f TRISD, 2 btfsc goto PORTD, 2 light No_light bsf goto PORTB, 0 Loop bcf goto PORTB, 0 Loop: Light: No_light:

References and Further Readings n http: //www. microchip. com Thank You For n http: //en. wikipedia. org/wiki/PIC_microcontroller Your Attendance. n 16 F 87 x n Mid Data Sheet Range Manual