Investigating latchup in the PXL detector Outline l

- Slides: 19

Investigating latchup in the PXL detector Outline: l What is latchup? – the consequences and sources of latchup – techniques to reduce latchup sensitivity l l l Other single event effects Latchup tests at BNL Latchup tests at 88” cyclotron Latchup tests at STAR Radiation environment at STAR Summary

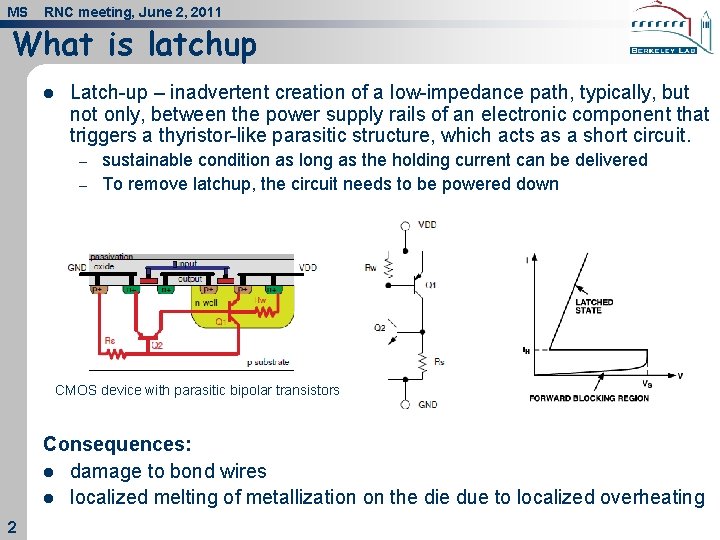

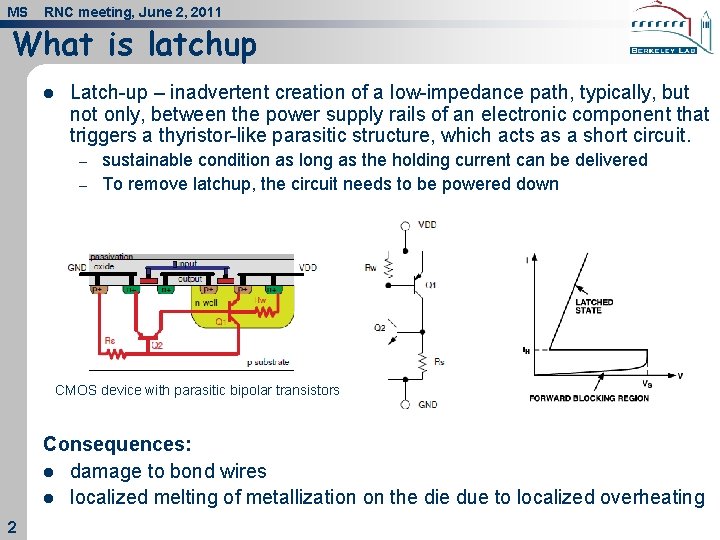

MS RNC meeting, June 2, 2011 What is latchup Latch-up – inadvertent creation of a low-impedance path, typically, but not only, between the power supply rails of an electronic component that triggers a thyristor-like parasitic structure, which acts as a short circuit. l – – sustainable condition as long as the holding current can be delivered To remove latchup, the circuit needs to be powered down CMOS device with parasitic bipolar transistors Consequences: l damage to bond wires l localized melting of metallization on the die due to localized overheating 2 2

MS RNC meeting, June 2, 2011 Sources of latchup l Supply voltages exceeding the absolute maximum ratings. l input/output pin voltage exceeding either supply rail by more than a diode drop. l incorrect power sequencing. l Various spikes and transients l Energetic particles (Single Event Latchup - SEL) Increasing density and circuit complexity in modern VLSI CMOS devices makes them more susceptible to latchup. 3 3

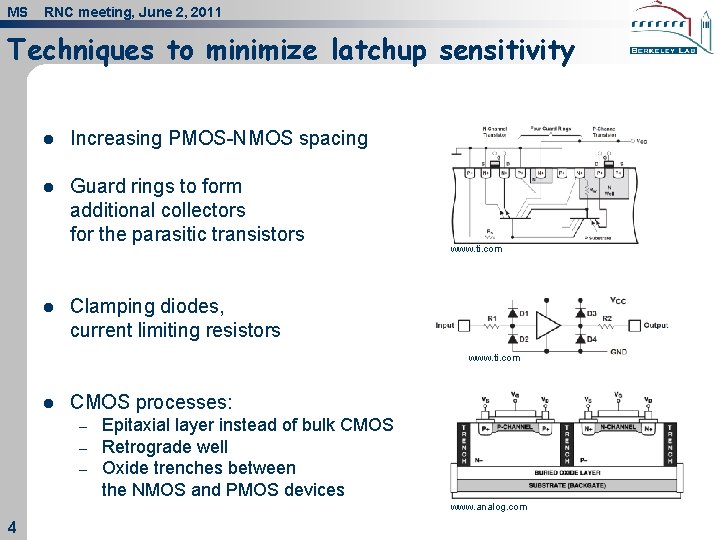

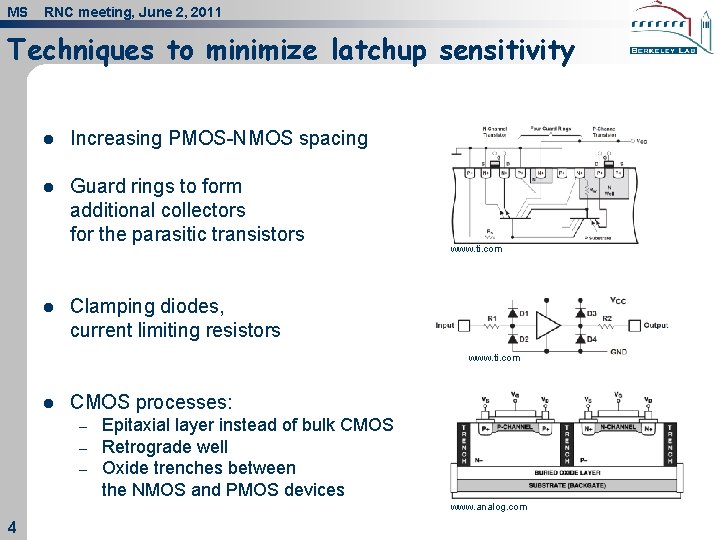

MS RNC meeting, June 2, 2011 Techniques to minimize latchup sensitivity l Increasing PMOS-NMOS spacing l Guard rings to form additional collectors for the parasitic transistors www. ti. com Clamping diodes, current limiting resistors l www. ti. com CMOS processes: l – – – Epitaxial layer instead of bulk CMOS Retrograde well Oxide trenches between the NMOS and PMOS devices www. analog. com 4 4

MS RNC meeting, June 2, 2011 What do we do for the PXL detector? We know that latchup can happen in MAPS (see later slides) l At IPHC – l At LBL – 5 5 On-going redesign of the standard digital cells for increased spacing between NMOS and PMOS transistors Building power supply modules for PXL ladders with over-current monitoring and automated shut down

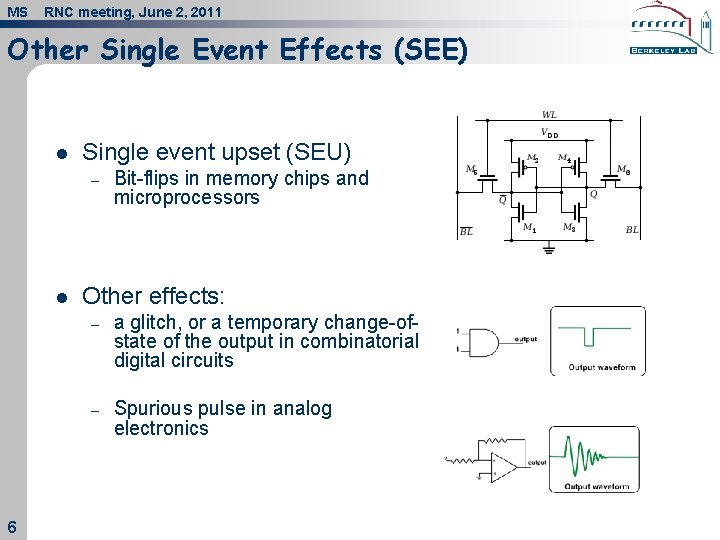

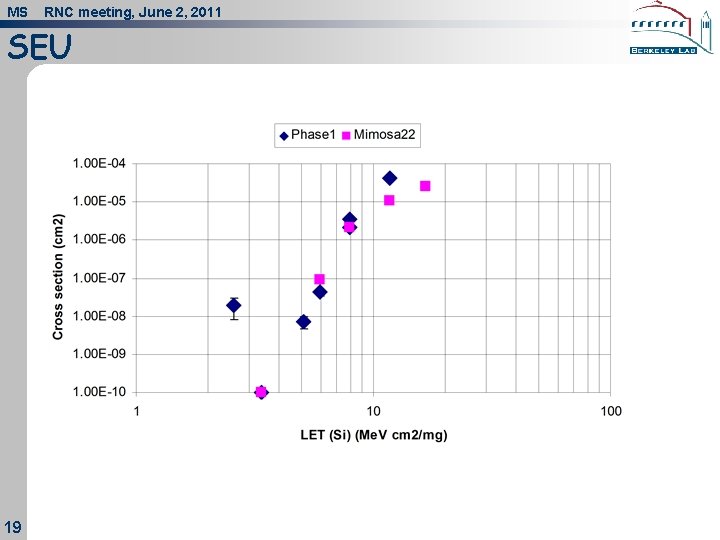

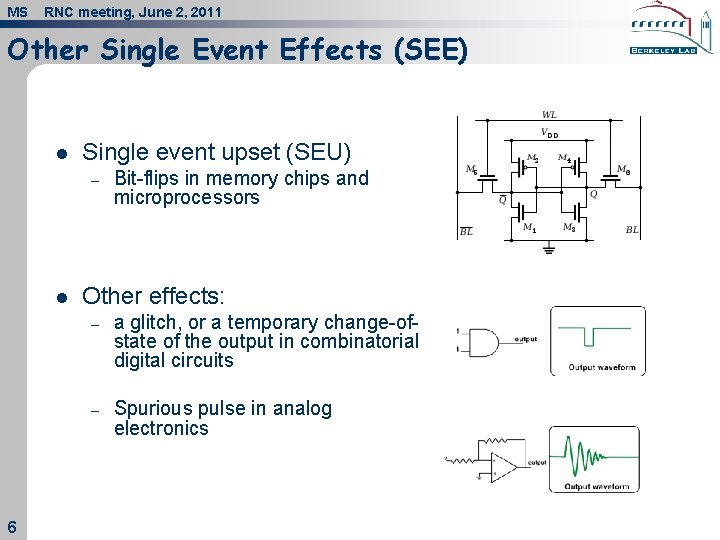

MS RNC meeting, June 2, 2011 Other Single Event Effects (SEE) l Single event upset (SEU) – l 6 6 Bit-flips in memory chips and microprocessors Other effects: – a glitch, or a temporary change-ofstate of the output in combinatorial digital circuits – Spurious pulse in analog electronics

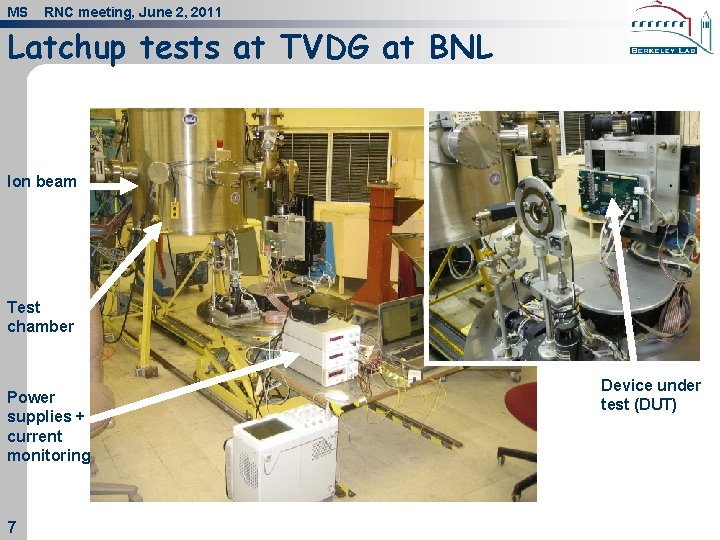

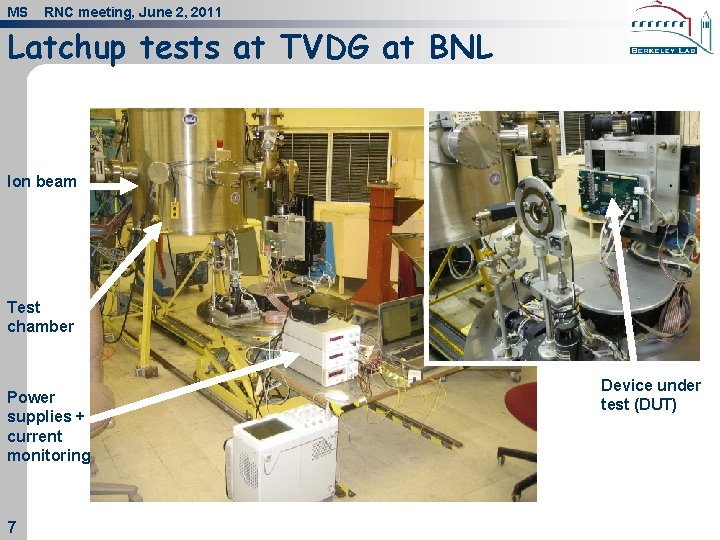

MS RNC meeting, June 2, 2011 Latchup tests at TVDG at BNL Ion beam Test chamber Power supplies + current monitoring 7 7 Device under test (DUT)

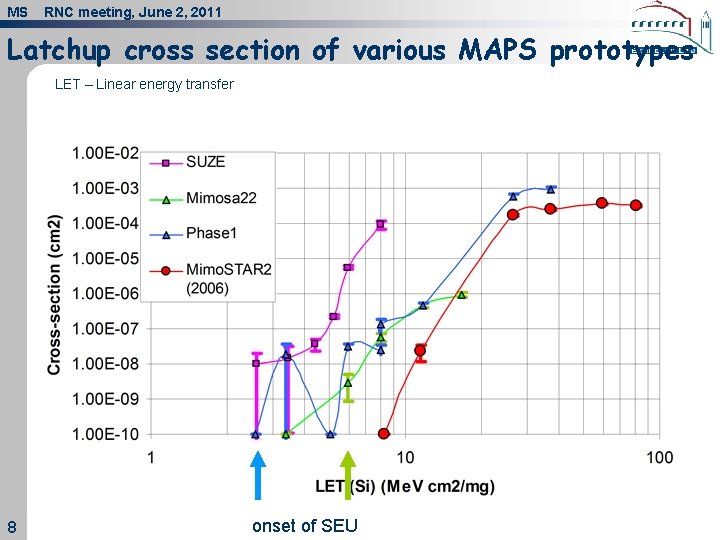

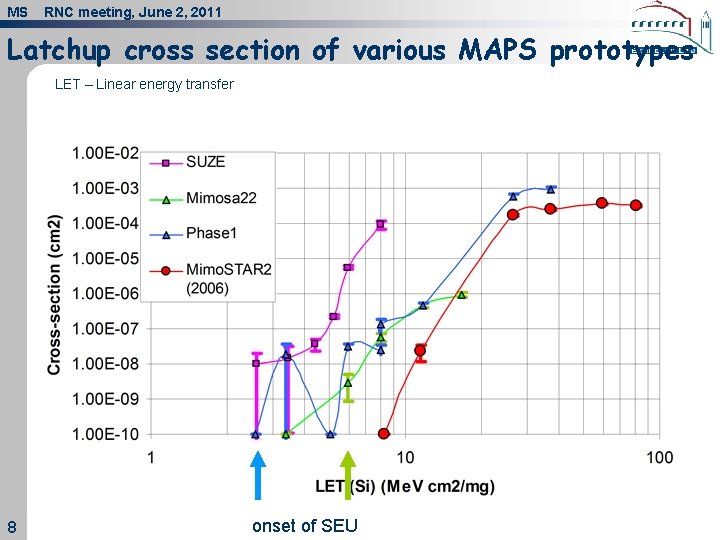

MS RNC meeting, June 2, 2011 Latchup cross section of various MAPS prototypes LET – Linear energy transfer 8 8 onset of SEU

MS RNC meeting, June 2, 2011 LU and SEU at 88” • • 9 Test chamber Readout system Test PCB Milled down IC package 9

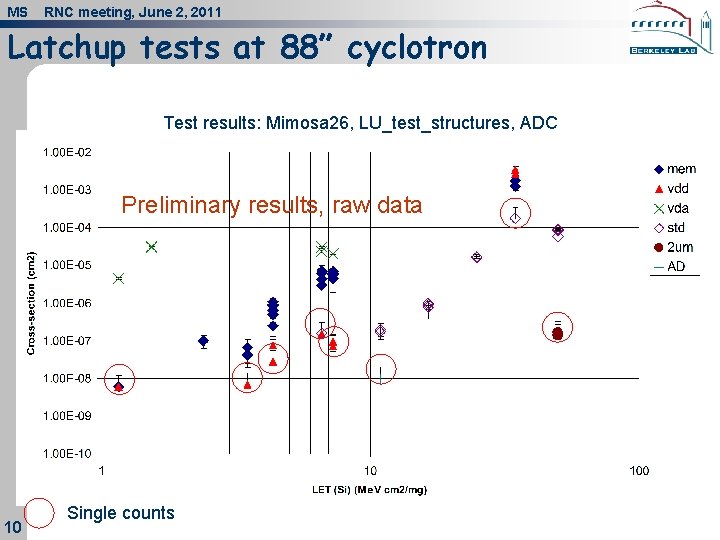

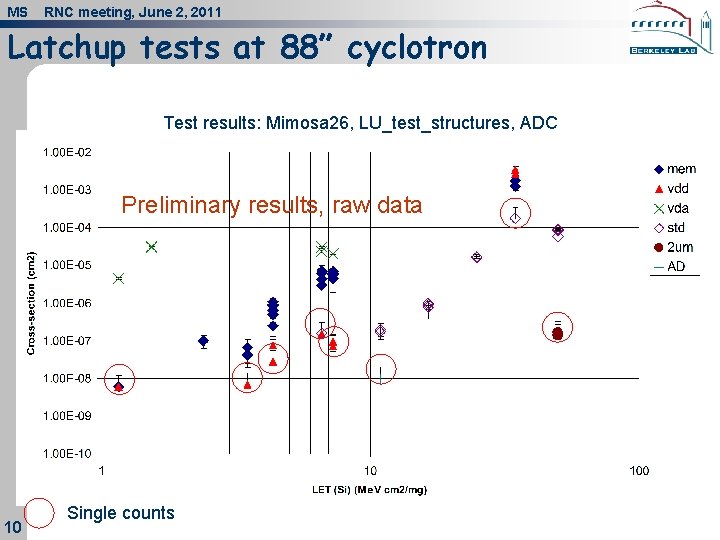

MS RNC meeting, June 2, 2011 Latchup tests at 88” cyclotron Test results: Mimosa 26, LU_test_structures, ADC Preliminary results, raw data 10 Single counts 10

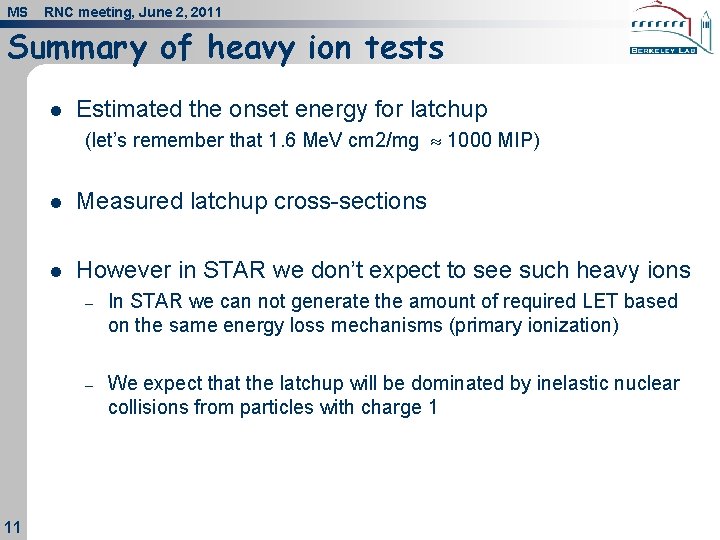

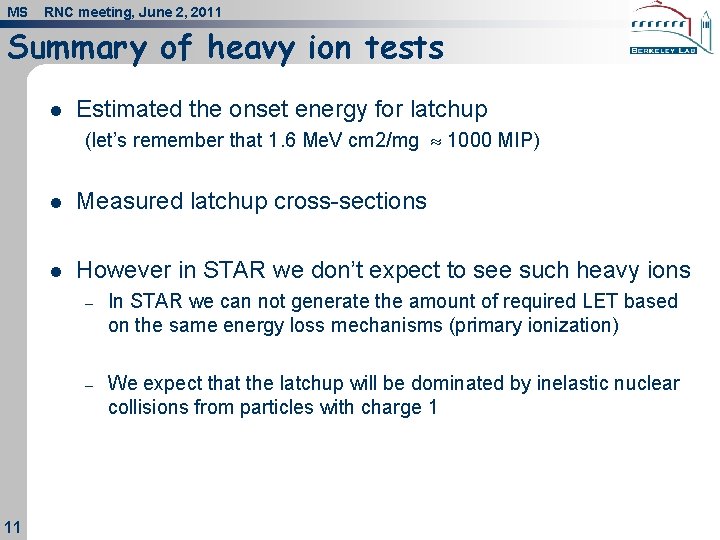

MS RNC meeting, June 2, 2011 Summary of heavy ion tests l Estimated the onset energy for latchup (let’s remember that 1. 6 Me. V cm 2/mg 1000 MIP) 11 l Measured latchup cross-sections l However in STAR we don’t expect to see such heavy ions 11 – In STAR we can not generate the amount of required LET based on the same energy loss mechanisms (primary ionization) – We expect that the latchup will be dominated by inelastic nuclear collisions from particles with charge 1

MS RNC meeting, June 2, 2011 Latchup tests at STAR l 2 x Mimosa 26 chips – l VDA, VDD, VMEM 1 voltage regulator Mimosa 26 – predecessor of PXL sensor (Ultimate) includes on-chip zero suppression 12 12 Mimosa 26 – ½ reticle size, PXL sensor – full reticle size, memory 4 × 600 × 16 bits memory 4 × 2048 × 16 bits

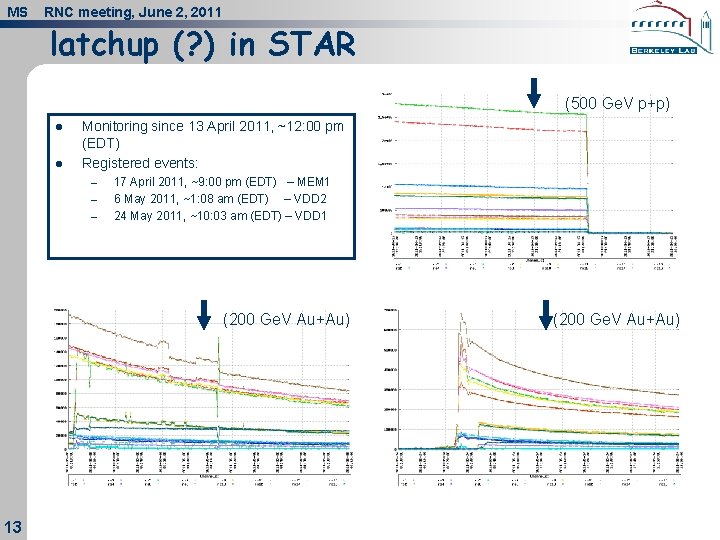

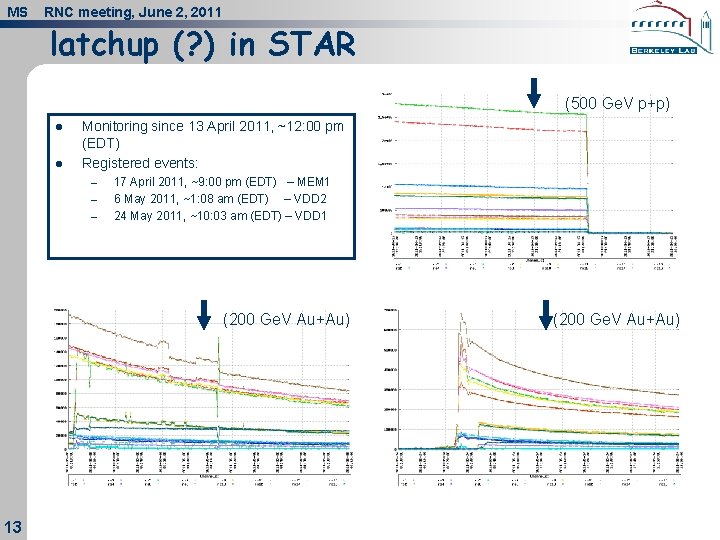

MS RNC meeting, June 2, 2011 latchup (? ) in STAR (500 Ge. V p+p) l l Monitoring since 13 April 2011, ~12: 00 pm (EDT) Registered events: – – – 17 April 2011, ~9: 00 pm (EDT) – MEM 1 6 May 2011, ~1: 08 am (EDT) – VDD 2 24 May 2011, ~10: 03 am (EDT) – VDD 1 (200 Ge. V Au+Au) 13 13 (200 Ge. V Au+Au)

MS RNC meeting, June 2, 2011 latchup in STAR 14 l Assuming that the mechanisms behind the observed event rates scale with the charged particle density, l and therefore, with the integrated dose (next 2 slides) l We can try to make predictions for latchup rates in the PXL detector 14

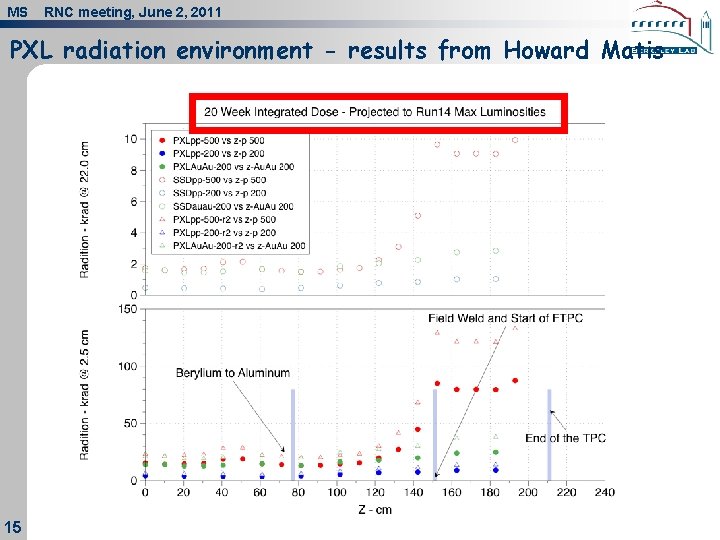

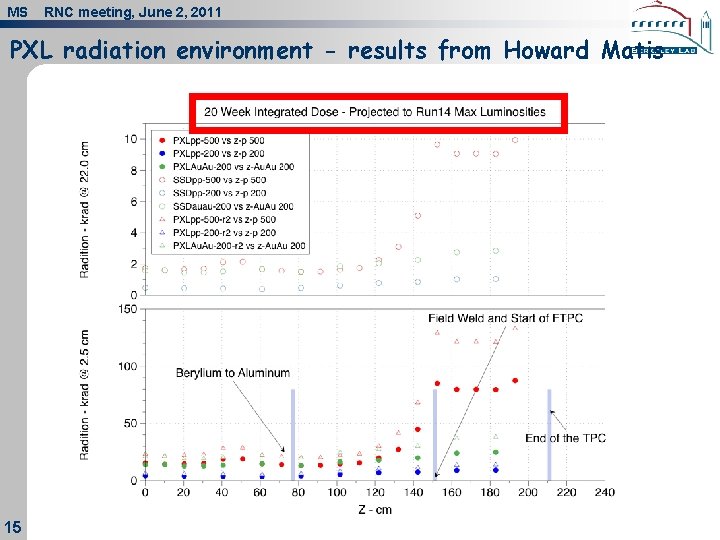

MS RNC meeting, June 2, 2011 PXL radiation environment - results from Howard Matis 15 15

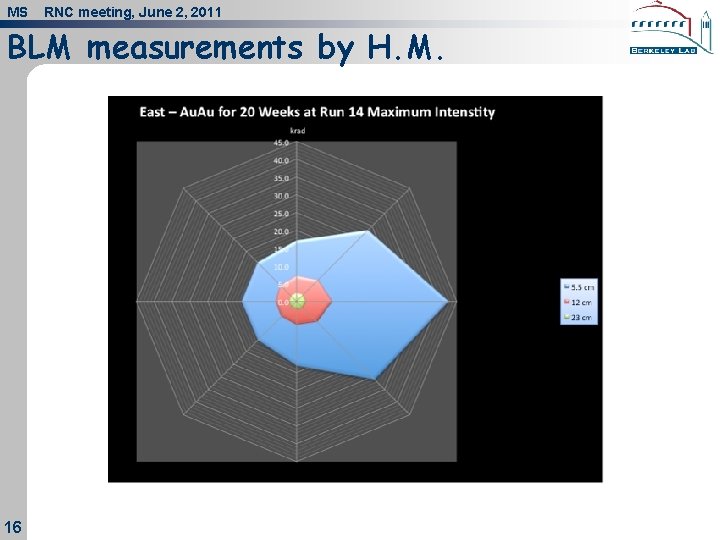

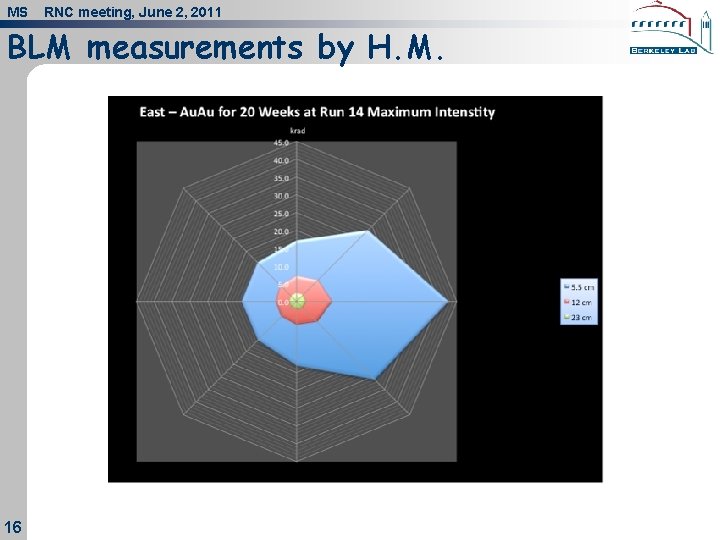

MS RNC meeting, June 2, 2011 BLM measurements by H. M. 16 16

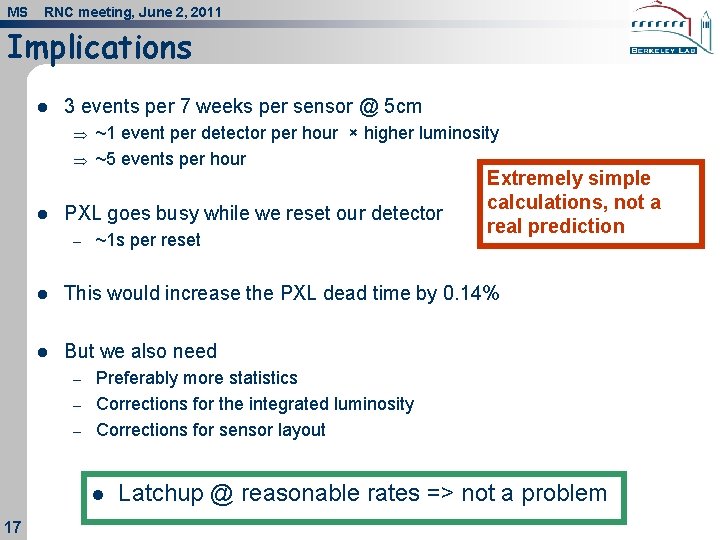

MS RNC meeting, June 2, 2011 Implications l 3 events per 7 weeks per sensor @ 5 cm Þ Þ l ~1 event per detector per hour × higher luminosity ~5 events per hour PXL goes busy while we reset our detector – ~1 s per reset l This would increase the PXL dead time by 0. 14% l But we also need – – – Preferably more statistics Corrections for the integrated luminosity Corrections for sensor layout l 17 Extremely simple calculations, not a real prediction 17 Latchup @ reasonable rates => not a problem

MS RNC meeting, June 2, 2011 Backup slides 18 18

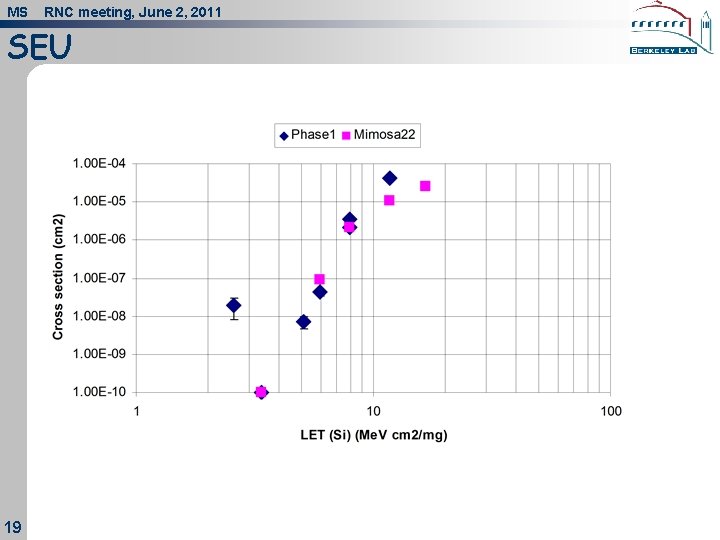

MS RNC meeting, June 2, 2011 SEU 19 19