Introduction CPU Overview 1 CPU performance factors Instruction

- Slides: 18

Introduction CPU Overview 1 CPU performance factors – Instruction count n – Determined by ISA and compiler CPI and Cycle time n Determined by CPU hardware We will examine two MIPS implementations – – A simplified version A more realistic pipelined version Simple subset, shows most aspects – – – Memory reference: lw, sw Arithmetic/logical: add, sub, and, or, slt Control transfer: beq, j CS@VT February 2009 Computer Organization II © 2006 -09 Mc. Quain & Ribbens

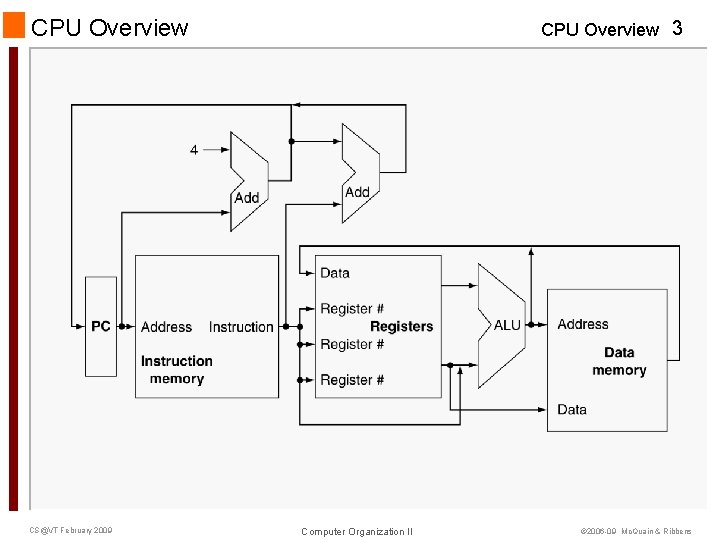

Instruction Execution CPU Overview 2 PC instruction memory, fetch instruction Register numbers register file, read registers Depending on instruction class – Use ALU to calculate n n n – – Arithmetic result Memory address for load/store Branch target address Access data memory for load/store PC target address or PC + 4 CS@VT February 2009 Computer Organization II © 2006 -09 Mc. Quain & Ribbens

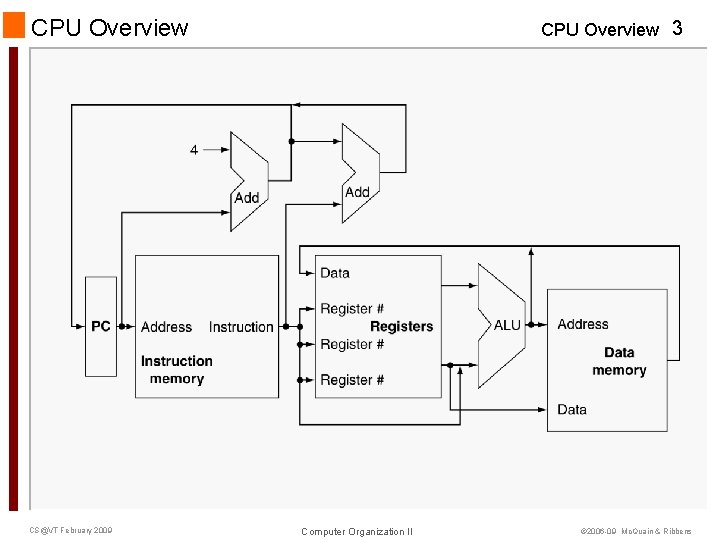

CPU Overview CS@VT February 2009 CPU Overview 3 Computer Organization II © 2006 -09 Mc. Quain & Ribbens

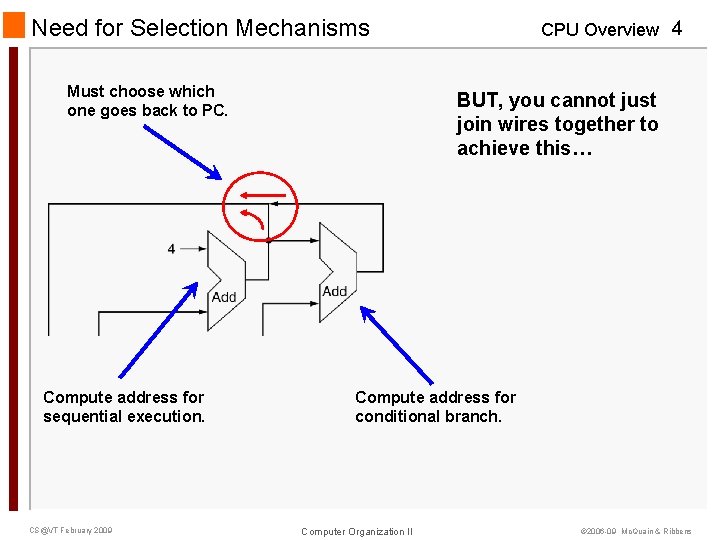

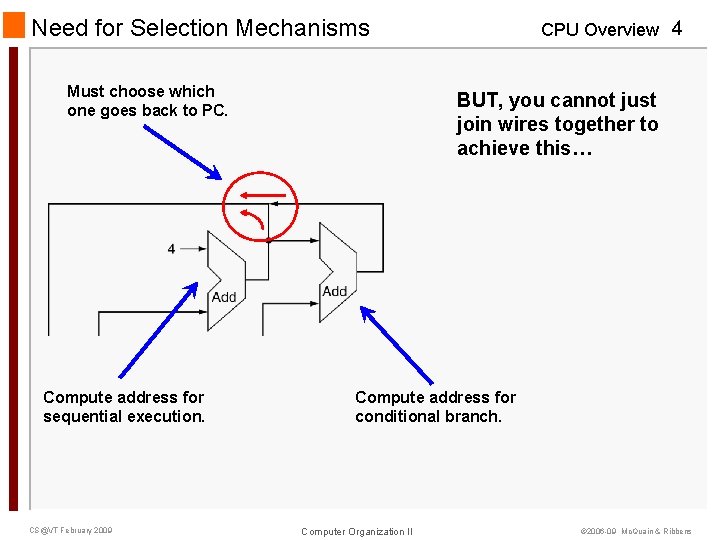

Need for Selection Mechanisms Must choose which one goes back to PC. Compute address for sequential execution. CS@VT February 2009 CPU Overview 4 BUT, you cannot just join wires together to achieve this… Compute address for conditional branch. Computer Organization II © 2006 -09 Mc. Quain & Ribbens

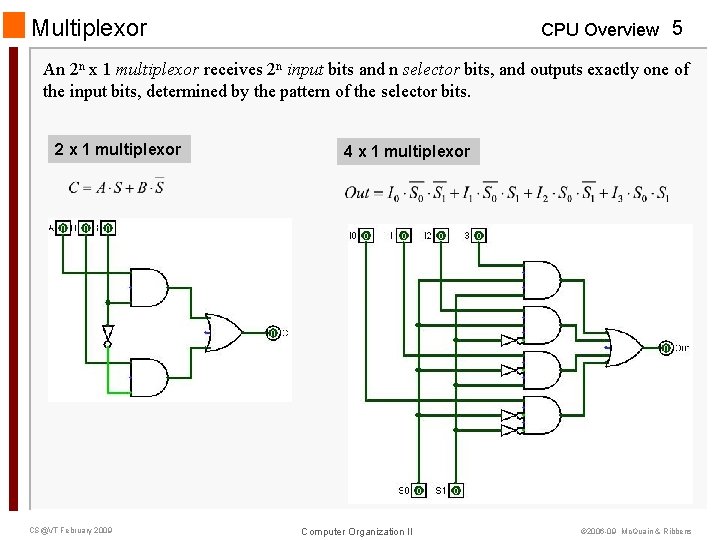

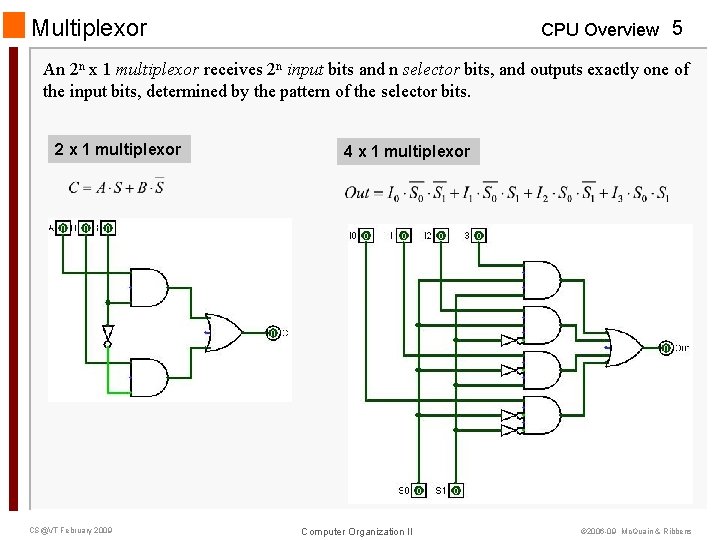

Multiplexor CPU Overview 5 An 2 n x 1 multiplexor receives 2 n input bits and n selector bits, and outputs exactly one of the input bits, determined by the pattern of the selector bits. 2 x 1 multiplexor CS@VT February 2009 4 x 1 multiplexor Computer Organization II © 2006 -09 Mc. Quain & Ribbens

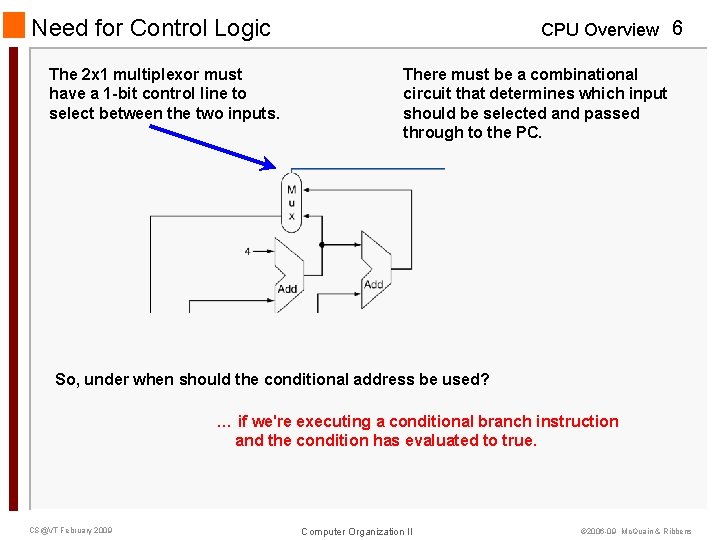

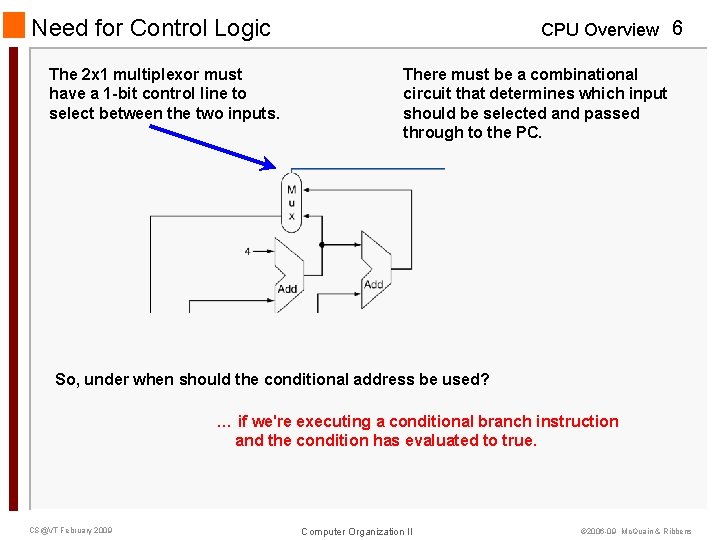

Need for Control Logic The 2 x 1 multiplexor must have a 1 -bit control line to select between the two inputs. CPU Overview 6 There must be a combinational circuit that determines which input should be selected and passed through to the PC. So, under when should the conditional address be used? … if we're executing a conditional branch instruction and the condition has evaluated to true. CS@VT February 2009 Computer Organization II © 2006 -09 Mc. Quain & Ribbens

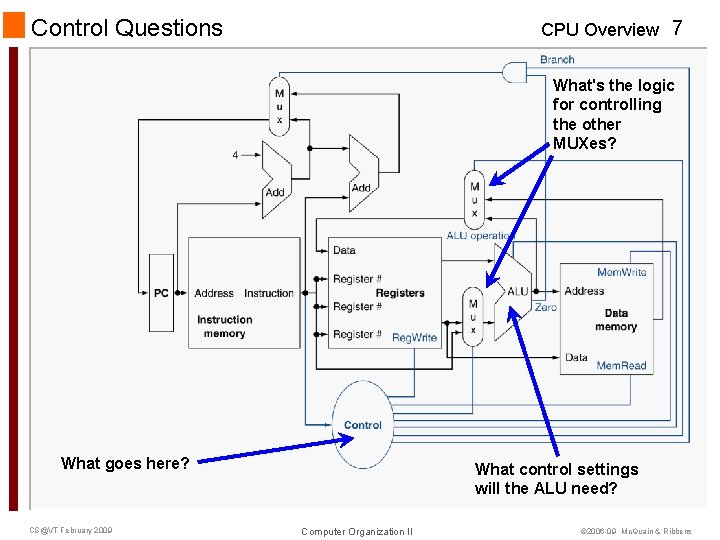

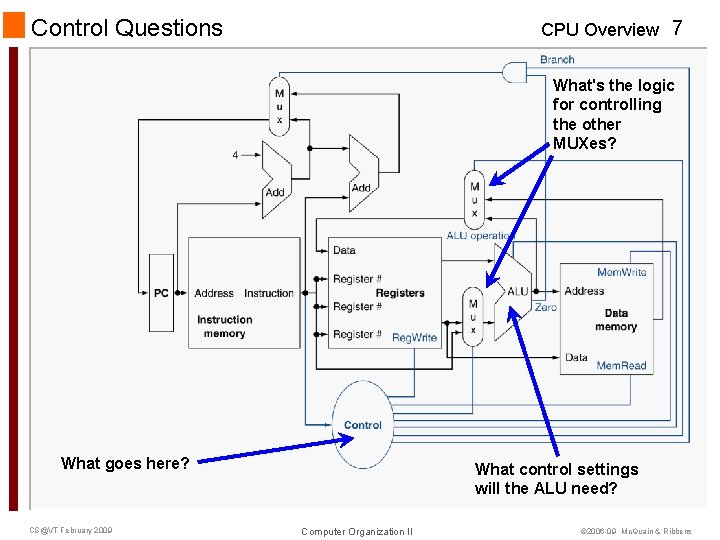

Control Questions CPU Overview 7 What's the logic for controlling the other MUXes? What goes here? CS@VT February 2009 What control settings will the ALU need? Computer Organization II © 2006 -09 Mc. Quain & Ribbens

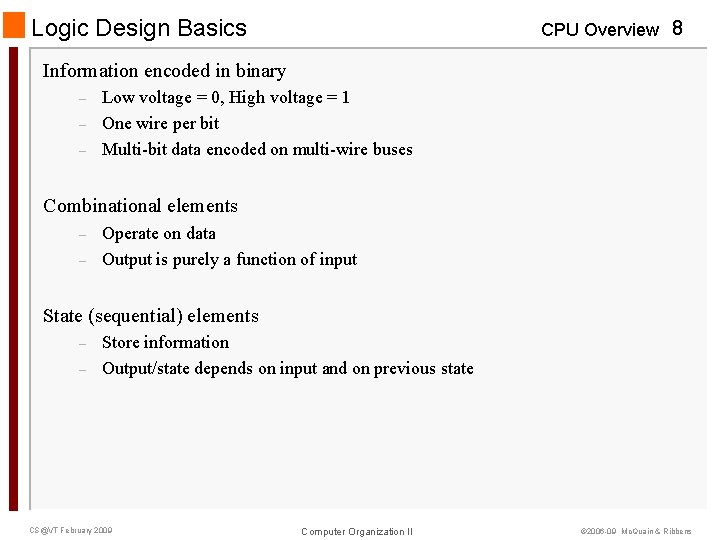

Logic Design Basics CPU Overview 8 Information encoded in binary – – – Low voltage = 0, High voltage = 1 One wire per bit Multi-bit data encoded on multi-wire buses Combinational elements – – Operate on data Output is purely a function of input State (sequential) elements – – Store information Output/state depends on input and on previous state CS@VT February 2009 Computer Organization II © 2006 -09 Mc. Quain & Ribbens

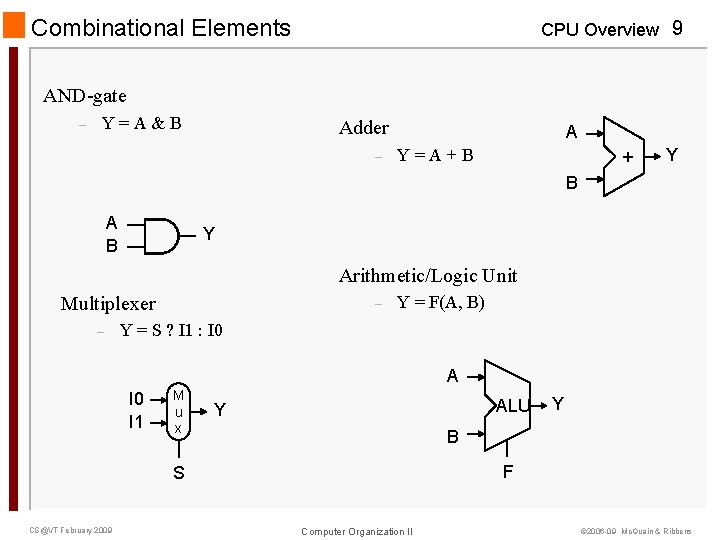

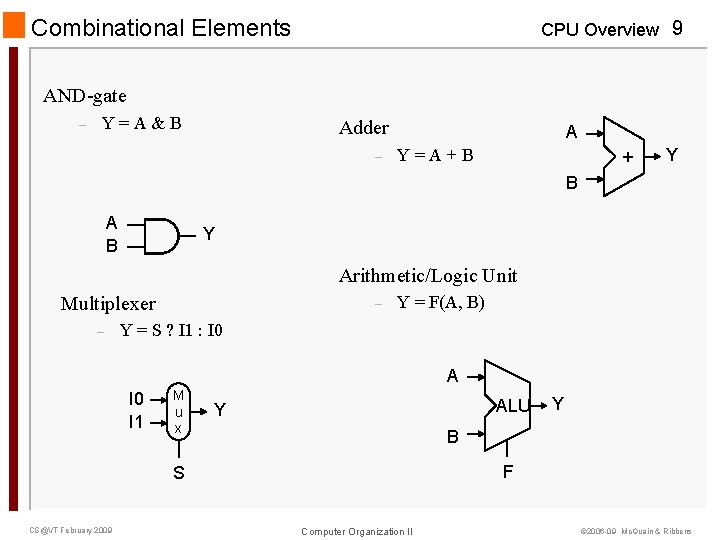

Combinational Elements CPU Overview 9 AND-gate – Y=A&B Adder – A Y=A+B + Y B A B Y Arithmetic/Logic Unit Multiplexer – – Y = F(A, B) Y = S ? I 1 : I 0 A I 0 I 1 M u x ALU Y B F S CS@VT February 2009 Y Computer Organization II © 2006 -09 Mc. Quain & Ribbens

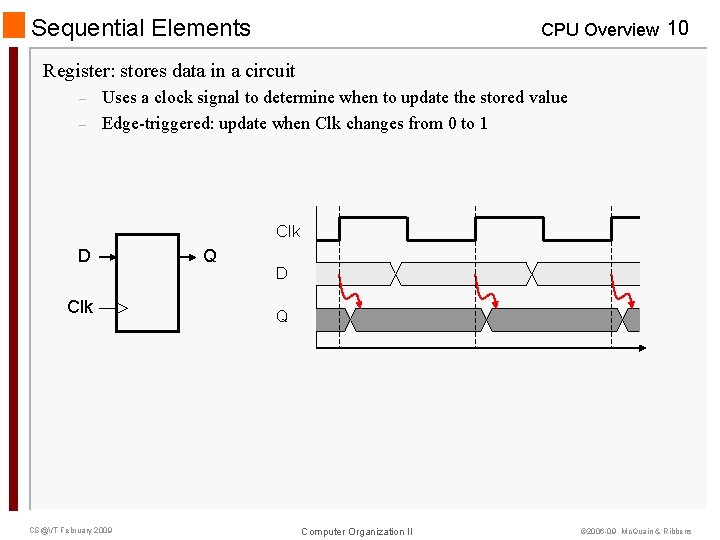

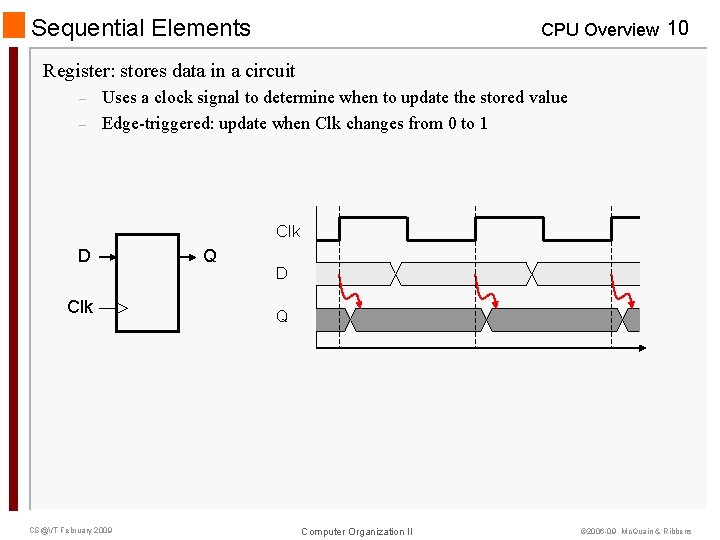

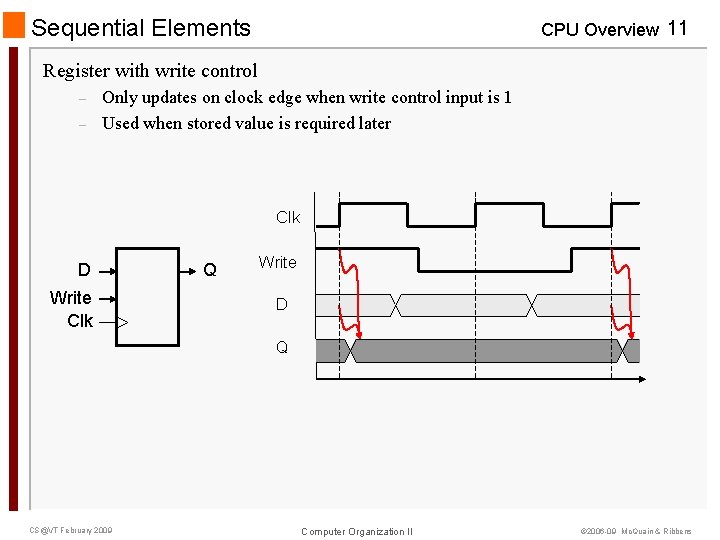

Sequential Elements CPU Overview 10 Register: stores data in a circuit – – Uses a clock signal to determine when to update the stored value Edge-triggered: update when Clk changes from 0 to 1 Clk D Clk CS@VT February 2009 Q D Q Computer Organization II © 2006 -09 Mc. Quain & Ribbens

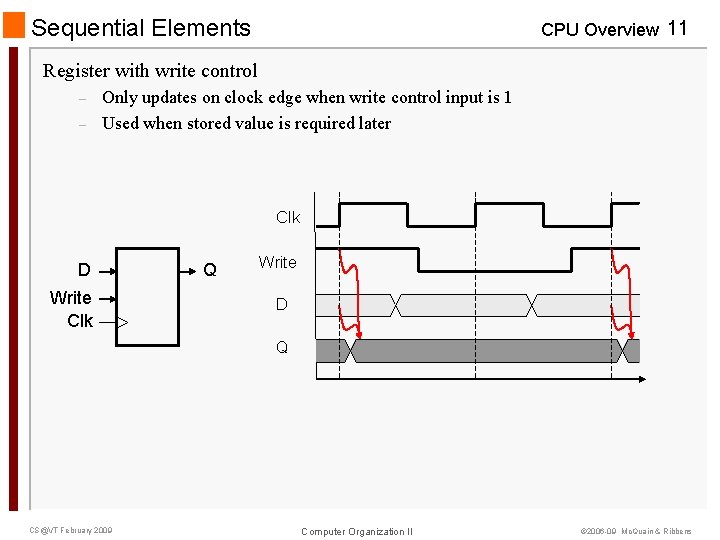

Sequential Elements CPU Overview 11 Register with write control – – Only updates on clock edge when write control input is 1 Used when stored value is required later Clk D Write Clk Q Write D Q CS@VT February 2009 Computer Organization II © 2006 -09 Mc. Quain & Ribbens

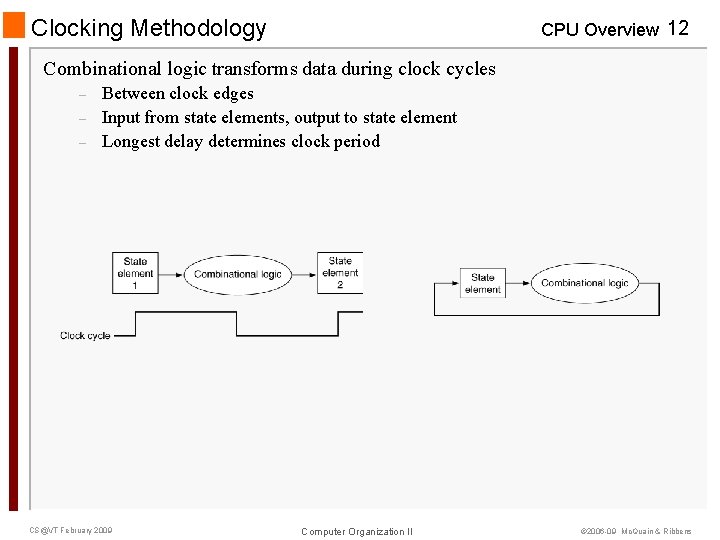

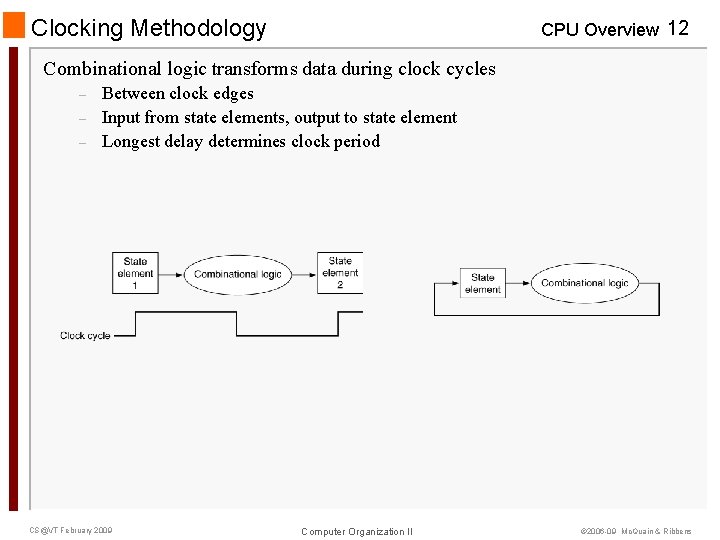

Clocking Methodology CPU Overview 12 Combinational logic transforms data during clock cycles – – – Between clock edges Input from state elements, output to state element Longest delay determines clock period CS@VT February 2009 Computer Organization II © 2006 -09 Mc. Quain & Ribbens

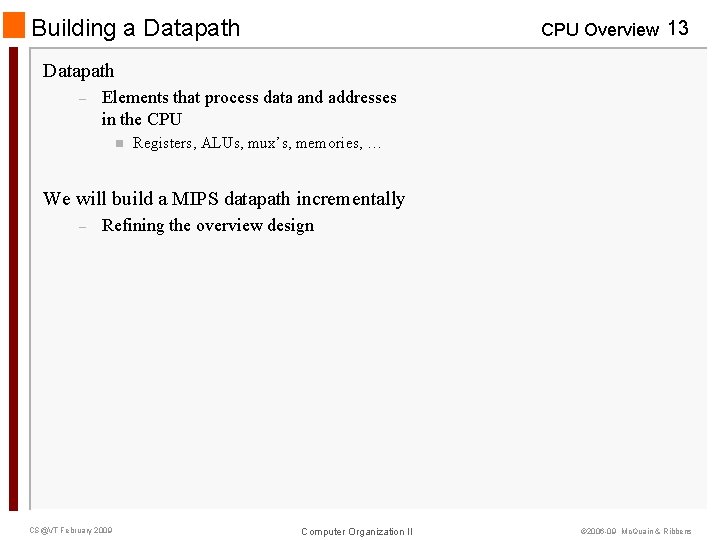

Building a Datapath CPU Overview 13 Datapath – Elements that process data and addresses in the CPU n Registers, ALUs, mux’s, memories, … We will build a MIPS datapath incrementally – Refining the overview design CS@VT February 2009 Computer Organization II © 2006 -09 Mc. Quain & Ribbens

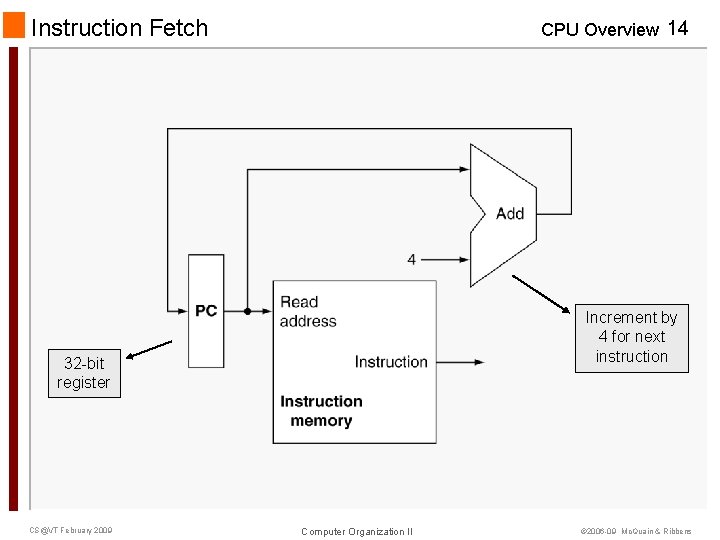

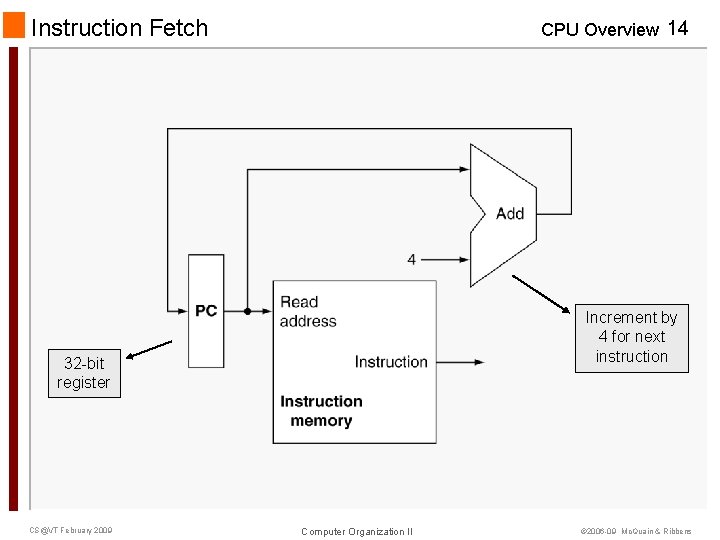

Instruction Fetch CPU Overview 14 Increment by 4 for next instruction 32 -bit register CS@VT February 2009 Computer Organization II © 2006 -09 Mc. Quain & Ribbens

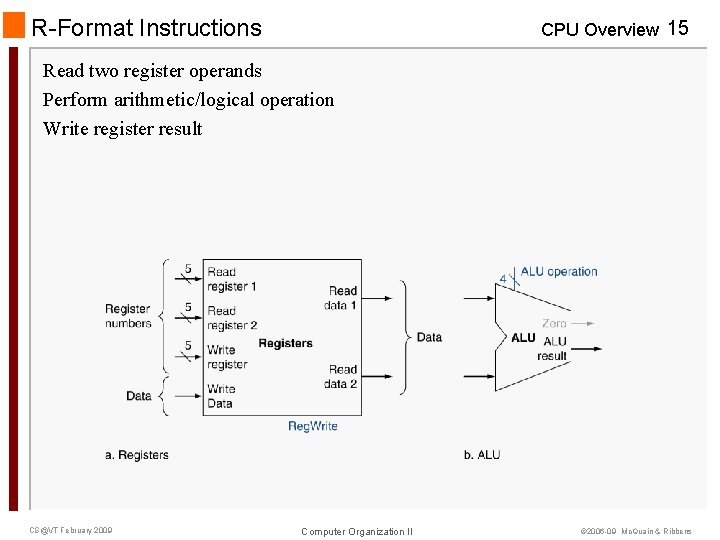

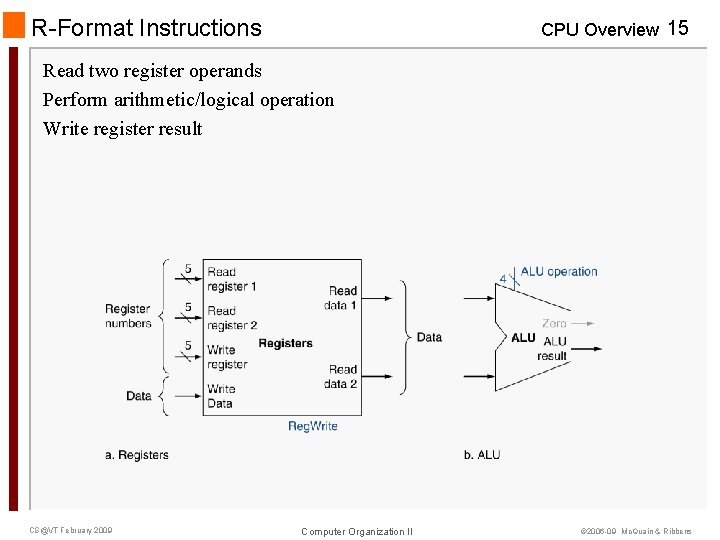

R-Format Instructions CPU Overview 15 Read two register operands Perform arithmetic/logical operation Write register result CS@VT February 2009 Computer Organization II © 2006 -09 Mc. Quain & Ribbens

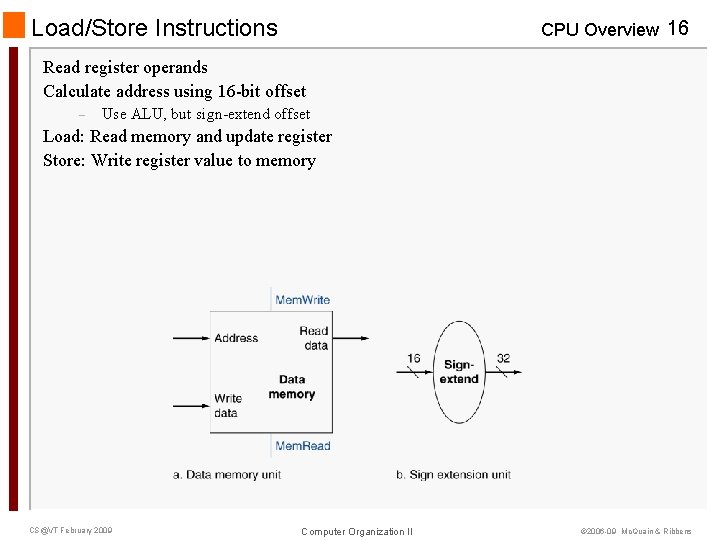

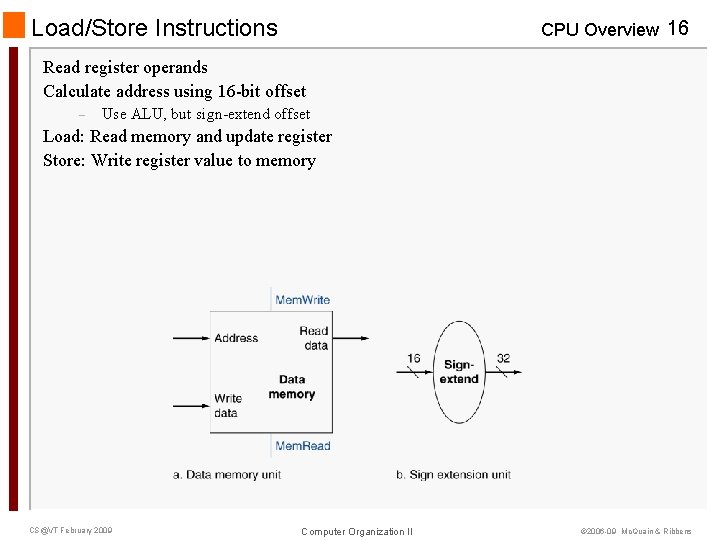

Load/Store Instructions CPU Overview 16 Read register operands Calculate address using 16 -bit offset – Use ALU, but sign-extend offset Load: Read memory and update register Store: Write register value to memory CS@VT February 2009 Computer Organization II © 2006 -09 Mc. Quain & Ribbens

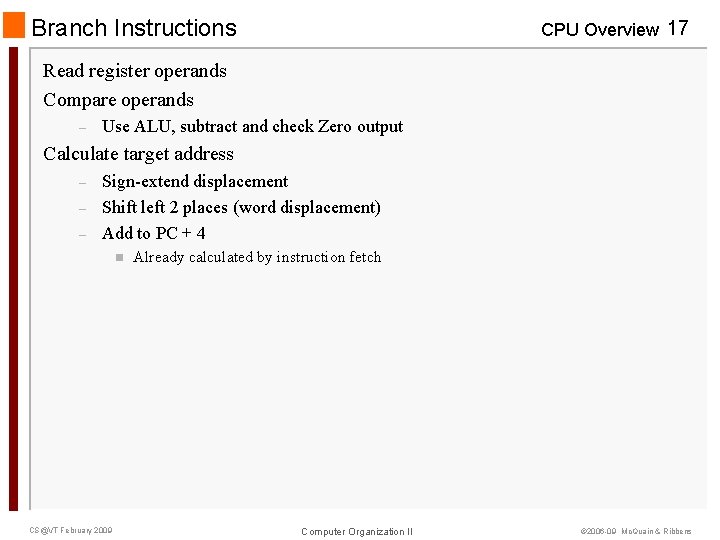

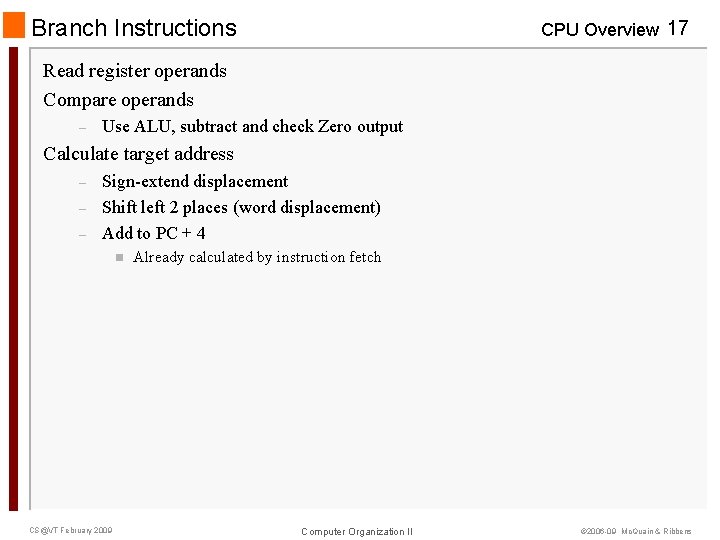

Branch Instructions CPU Overview 17 Read register operands Compare operands – Use ALU, subtract and check Zero output Calculate target address – – – Sign-extend displacement Shift left 2 places (word displacement) Add to PC + 4 n CS@VT February 2009 Already calculated by instruction fetch Computer Organization II © 2006 -09 Mc. Quain & Ribbens

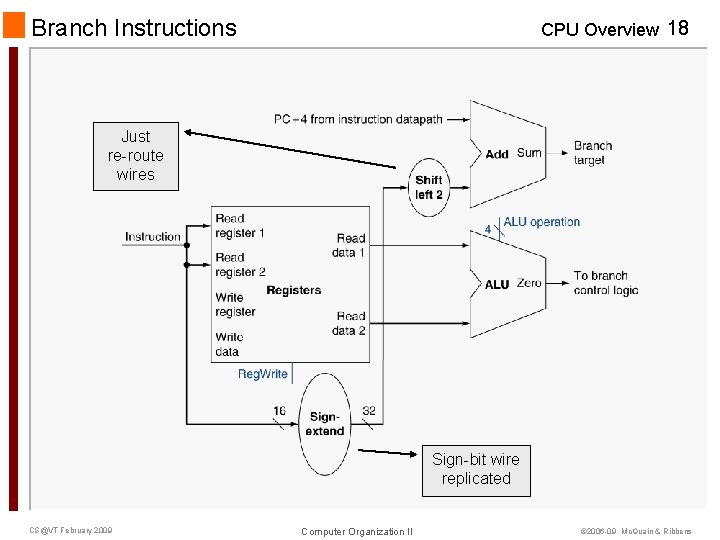

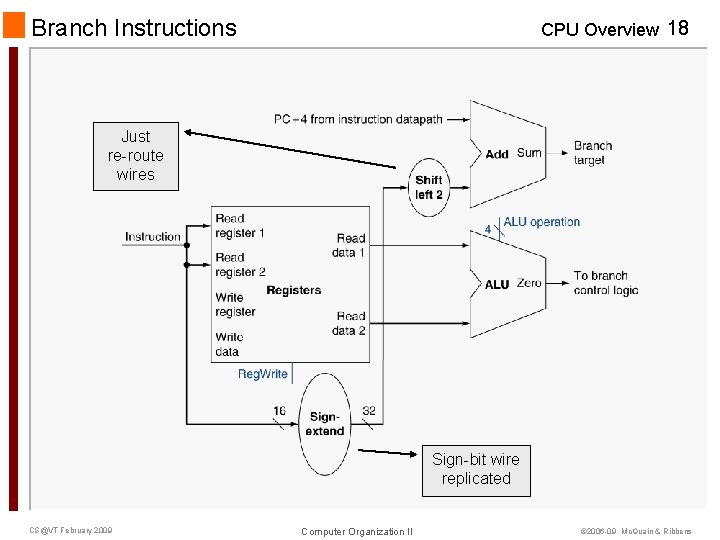

Branch Instructions CPU Overview 18 Just re-route wires Sign-bit wire replicated CS@VT February 2009 Computer Organization II © 2006 -09 Mc. Quain & Ribbens