Implementation RISC vs CISC concept Concept of pipeline

- Slides: 19

Implementation RISC vs. CISC concept Concept of pipeline An implementation of Mips Pipeline’s problems Pirouz Bazargan Sabet December 2003

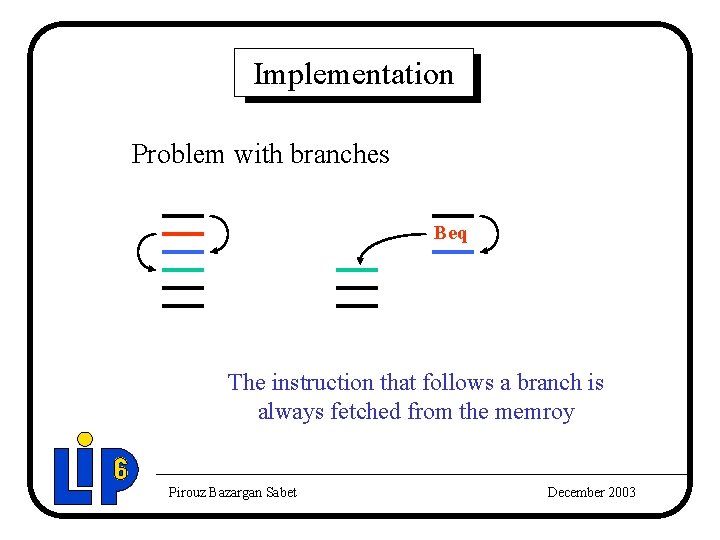

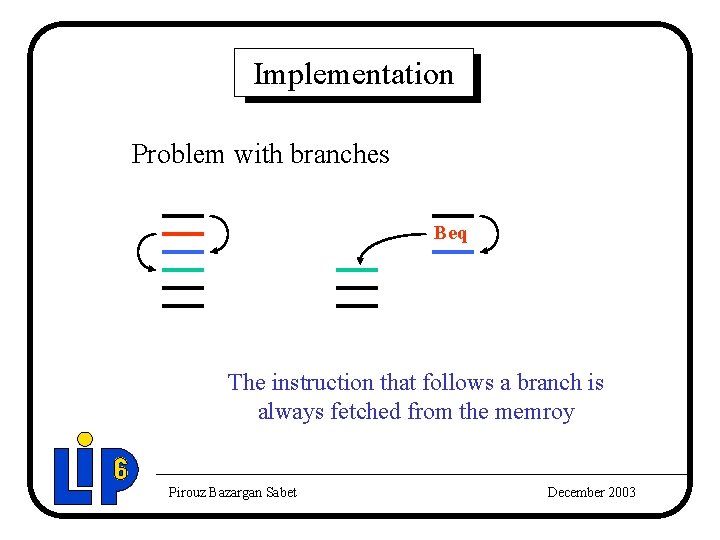

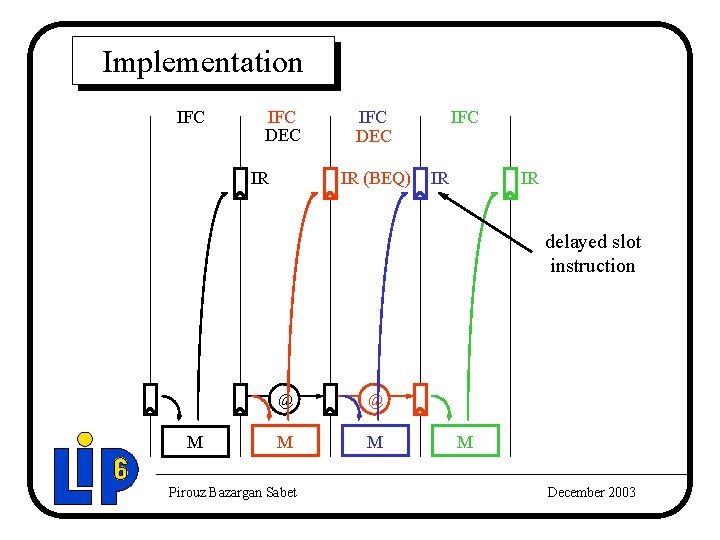

Implementation Problem with branches Beq The instruction that follows a branch is always fetched from the memroy Pirouz Bazargan Sabet December 2003

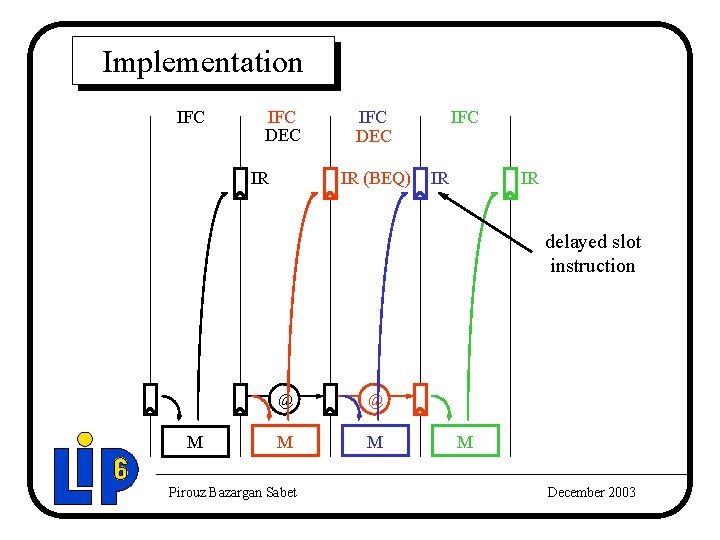

Implementation IFC DEC IR (BEQ) IFC IR IR delayed slot instruction M @ @ M M Pirouz Bazargan Sabet M December 2003

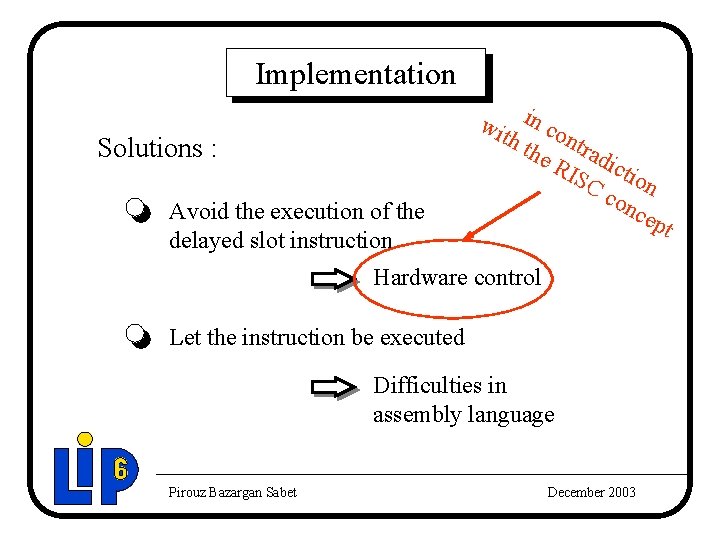

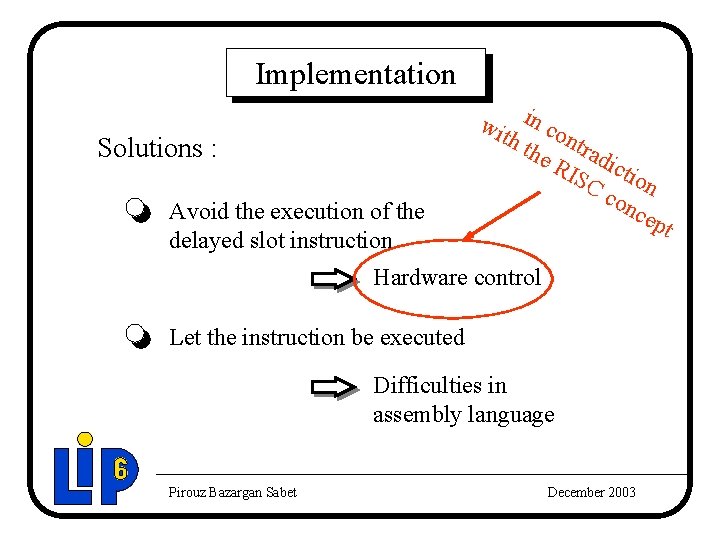

Implementation Solutions : Avoid the execution of the delayed slot instruction wit in co ht n he trad RIS icti C c on on cep t Hardware control Let the instruction be executed Difficulties in assembly language Pirouz Bazargan Sabet December 2003

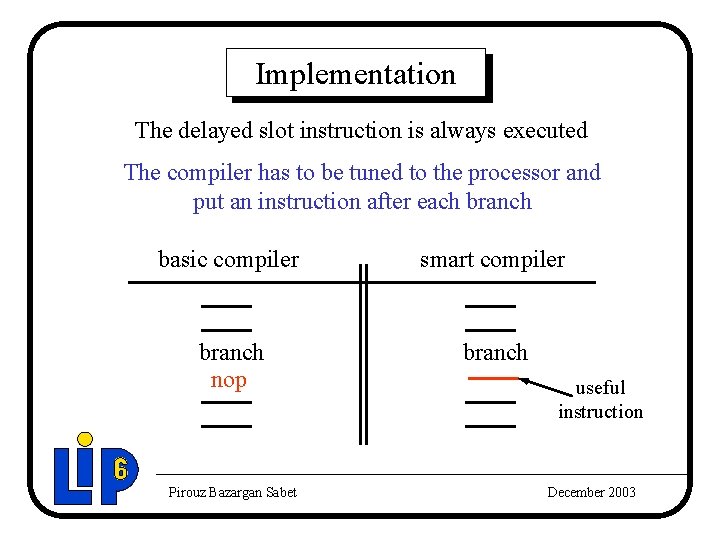

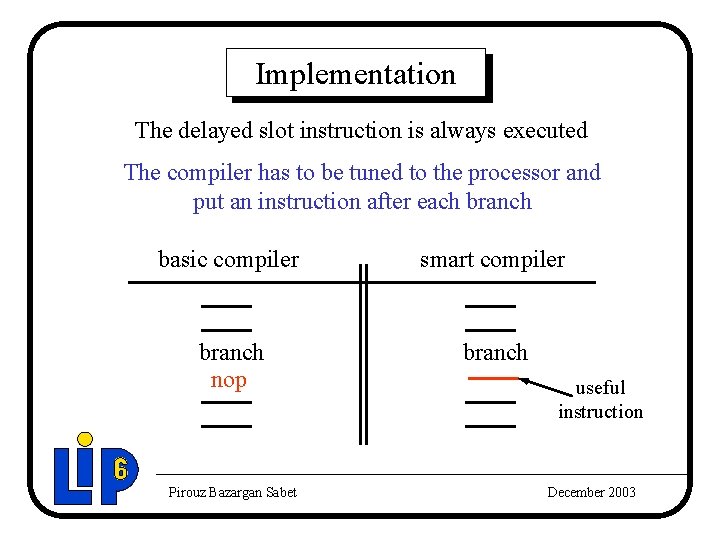

Implementation The delayed slot instruction is always executed The compiler has to be tuned to the processor and put an instruction after each branch basic compiler smart compiler branch nop branch Pirouz Bazargan Sabet useful instruction December 2003

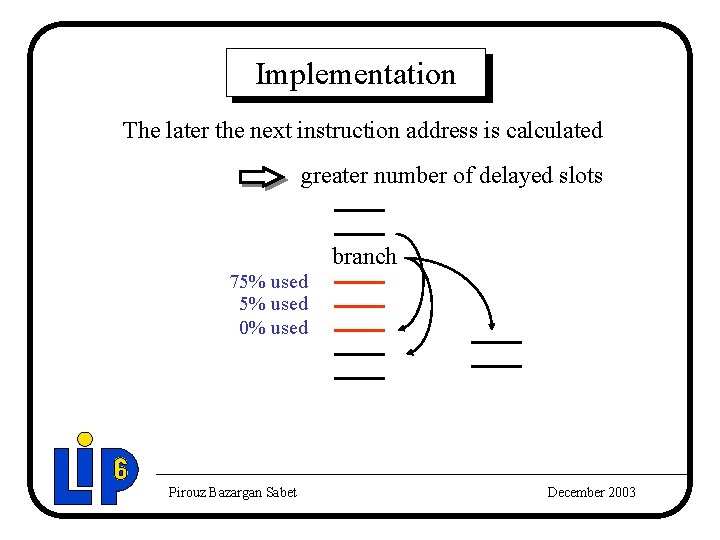

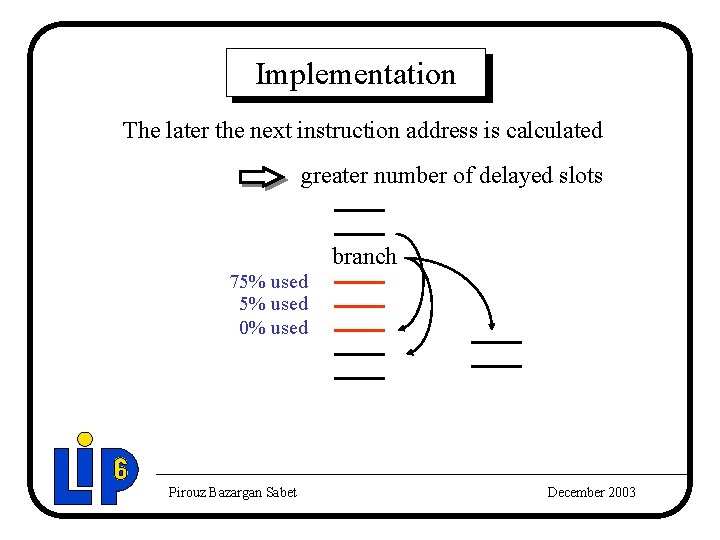

Implementation The later the next instruction address is calculated greater number of delayed slots branch hard 75% used to 5% fillused 0% used Pirouz Bazargan Sabet December 2003

Implementation The problem of data dependency Pirouz Bazargan Sabet December 2003

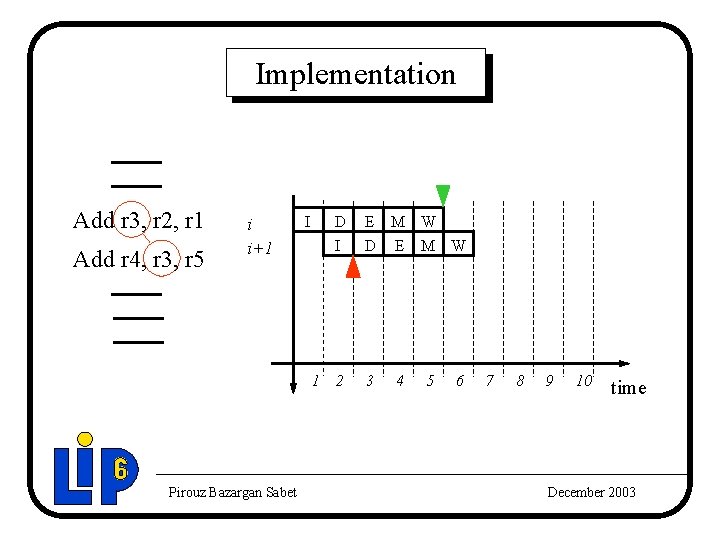

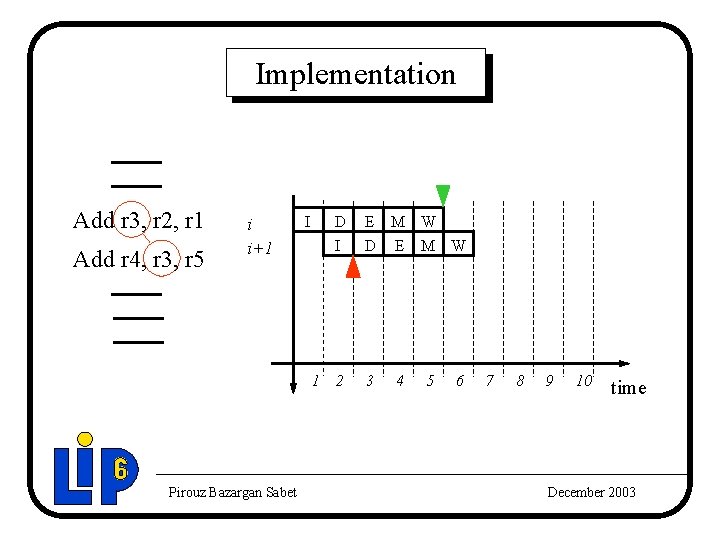

Implementation Add r 3, r 2, r 1 Add r 4, r 3, r 5 i i+1 I 1 Pirouz Bazargan Sabet D I E M W D E M W 2 3 4 5 6 7 8 9 10 time December 2003

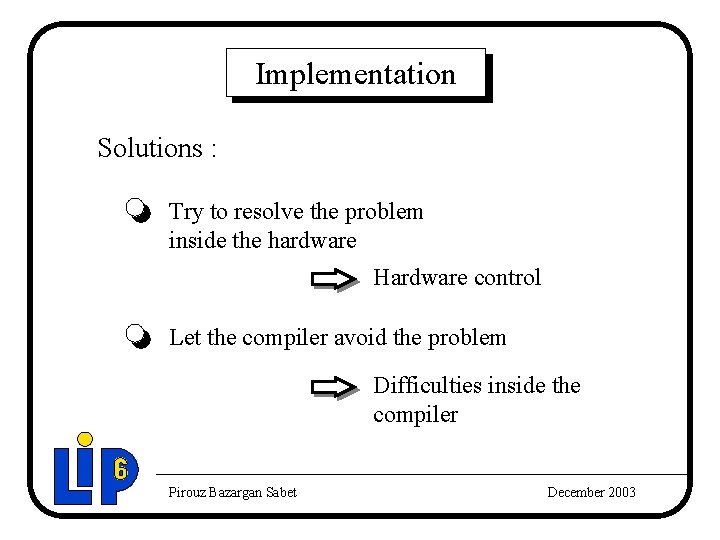

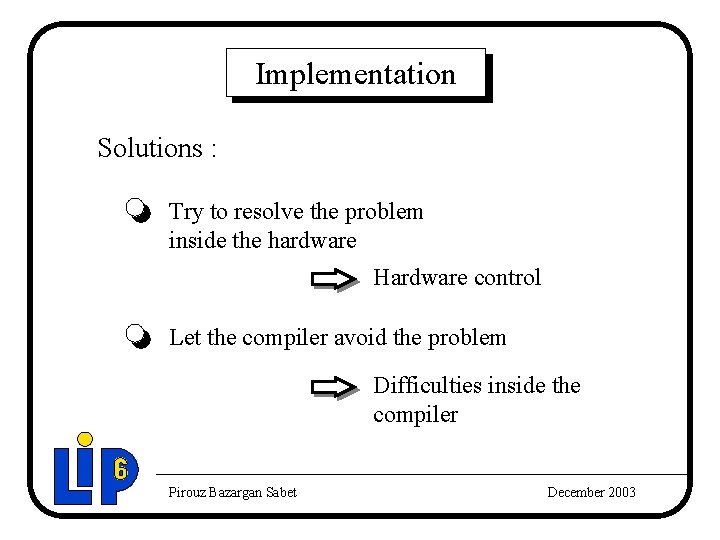

Implementation Solutions : Try to resolve the problem inside the hardware Hardware control Let the compiler avoid the problem Difficulties inside the compiler Pirouz Bazargan Sabet December 2003

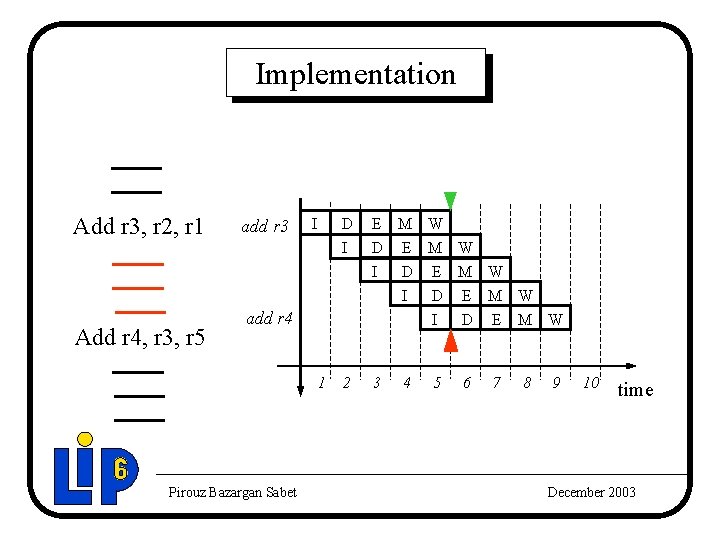

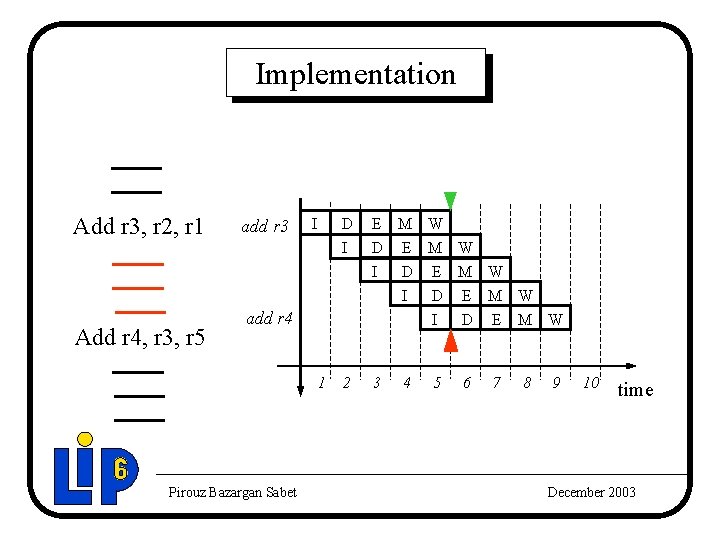

Implementation Add r 3, r 2, r 1 add r 3 I Add r 4, r 3, r 5 D I E M W D E M W I D E M W 2 3 add r 4 1 Pirouz Bazargan Sabet 4 5 6 7 8 9 10 time December 2003

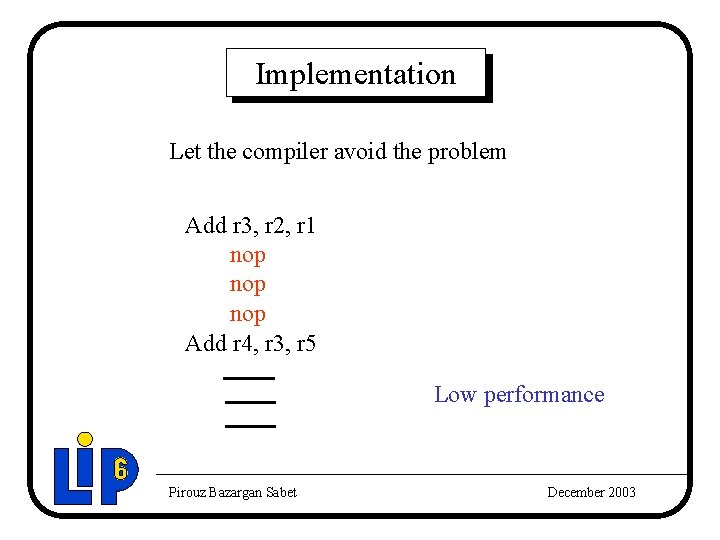

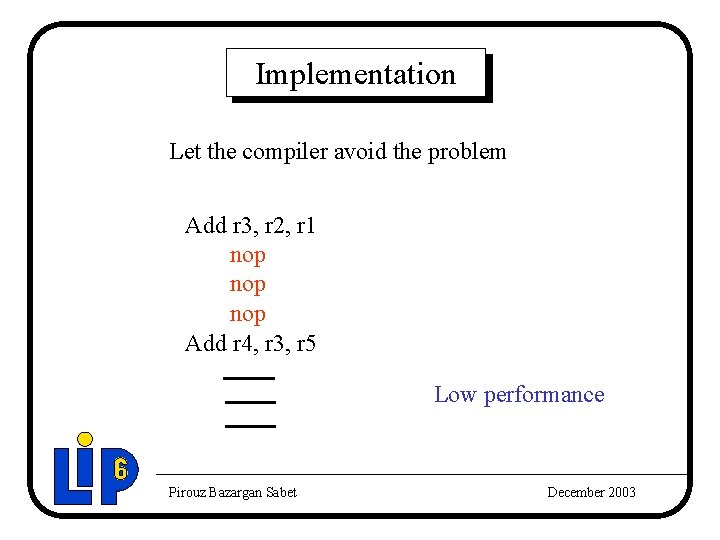

Implementation Let the compiler avoid the problem Add r 3, r 2, r 1 nop nop Add r 4, r 3, r 5 Low performance Pirouz Bazargan Sabet December 2003

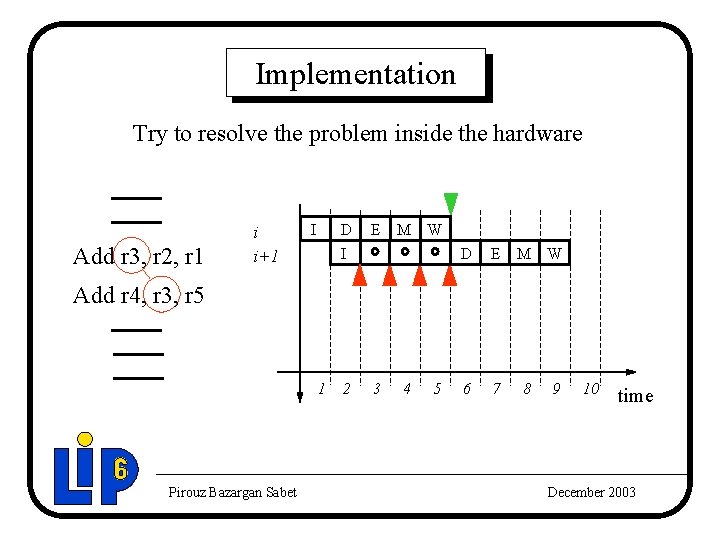

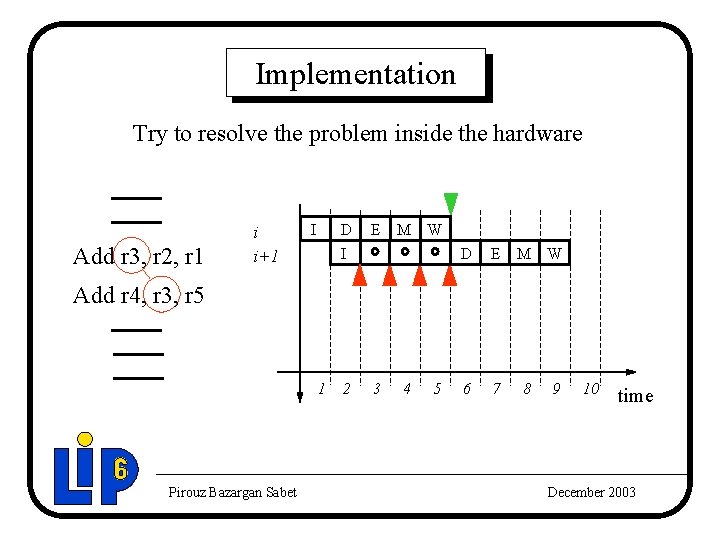

Implementation Try to resolve the problem inside the hardware Add r 3, r 2, r 1 i i+1 I D I E M W D D E 2 3 6 7 M W Add r 4, r 3, r 5 1 Pirouz Bazargan Sabet 4 5 8 9 10 time December 2003

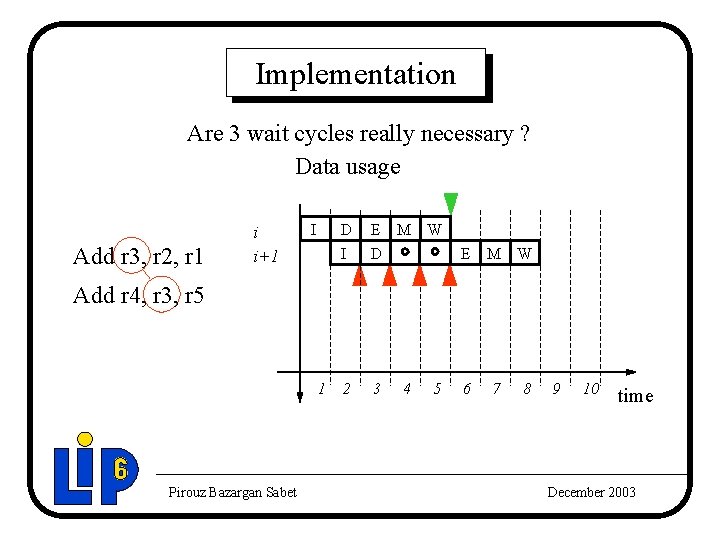

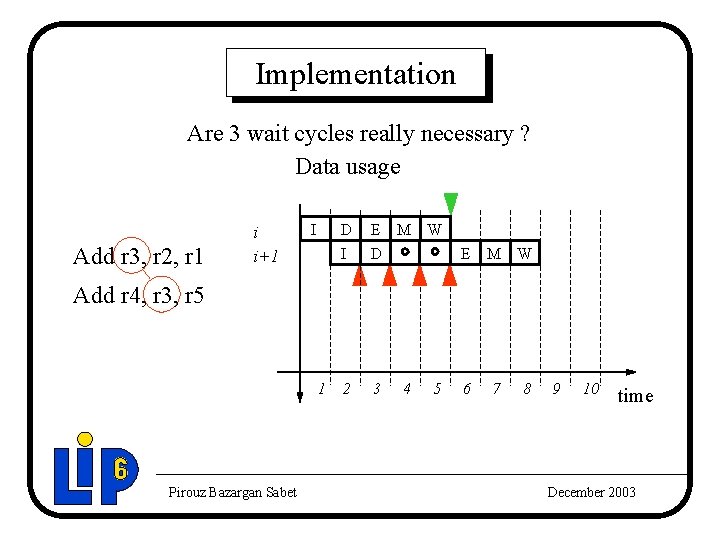

Implementation Are 3 wait cycles really necessary ? Data usage Add r 3, r 2, r 1 i i+1 I D I E M W D E E E 2 3 6 M W Add r 4, r 3, r 5 1 Pirouz Bazargan Sabet 4 5 7 8 9 10 time December 2003

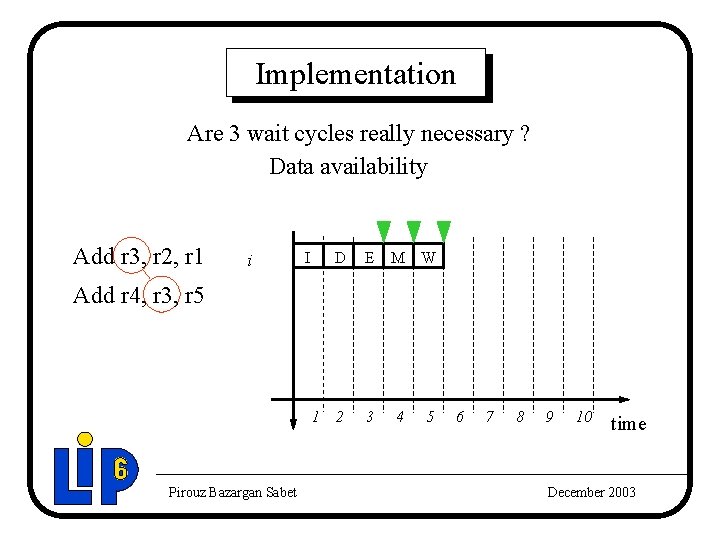

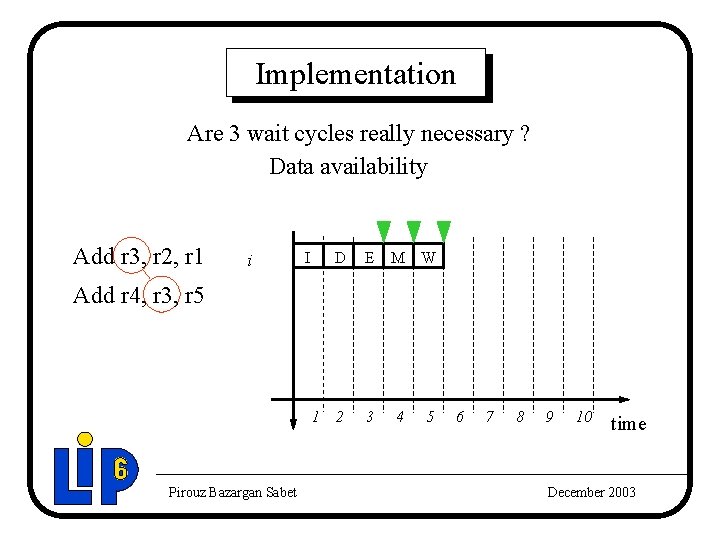

Implementation Are 3 wait cycles really necessary ? Data availability Add r 3, r 2, r 1 i I D E 2 3 M W Add r 4, r 3, r 5 1 Pirouz Bazargan Sabet 4 5 6 7 8 9 10 time December 2003

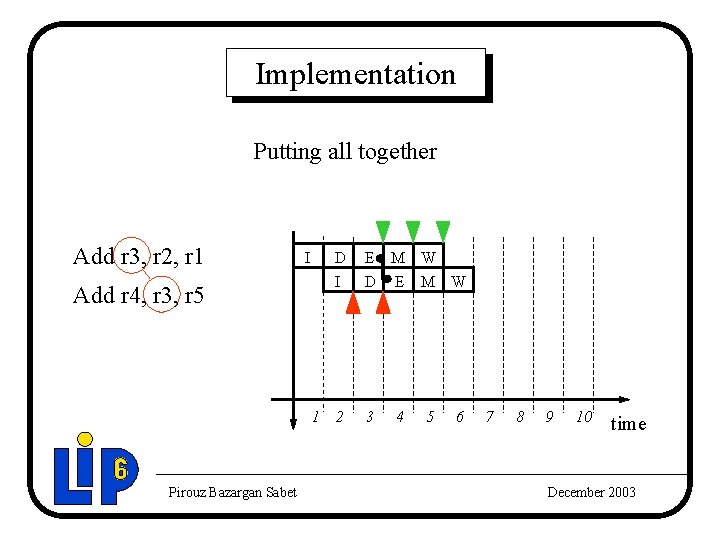

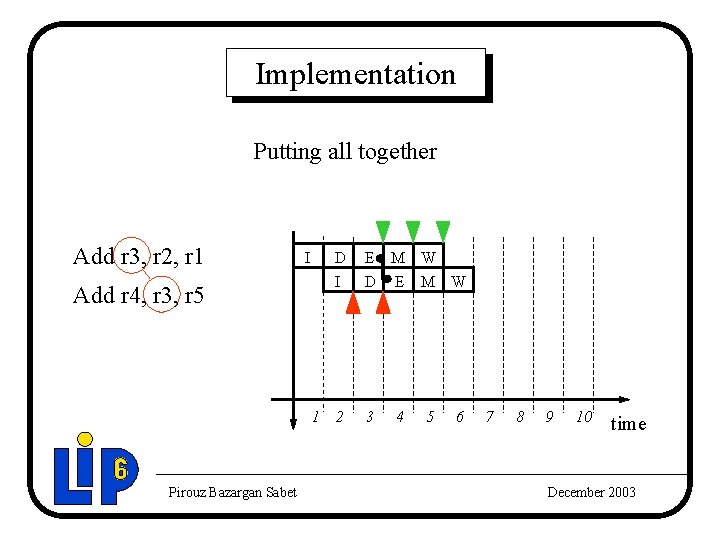

Implementation Putting all together Add r 3, r 2, r 1 I Add r 4, r 3, r 5 1 Pirouz Bazargan Sabet D I E M W D E M W 2 3 4 5 6 7 8 9 10 time December 2003

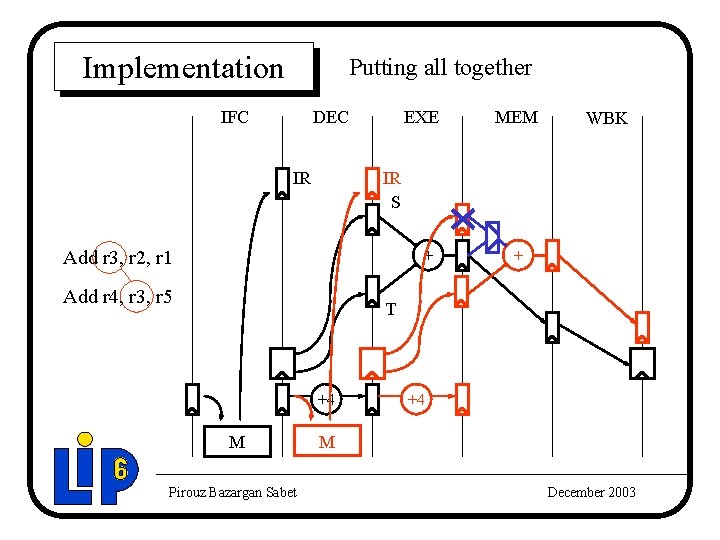

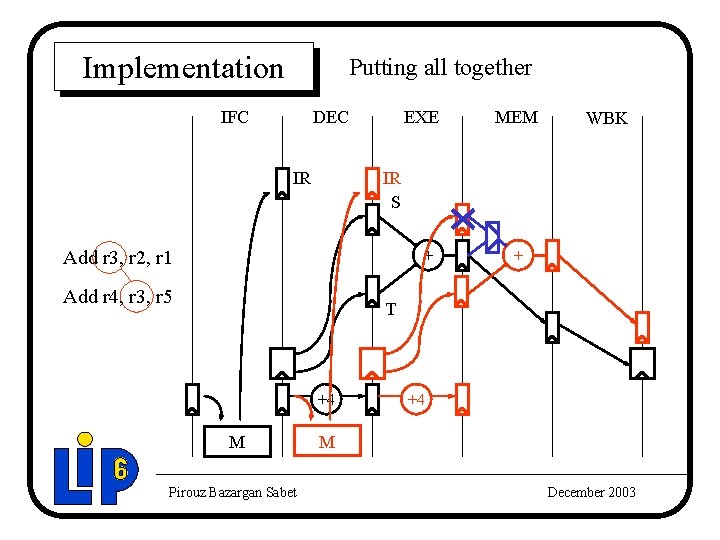

Implementation Putting all together IFC DEC IR EXE MEM WBK IR S Add r 3, r 2, r 1 + Add r 4, r 3, r 5 + T +4 M Pirouz Bazargan Sabet +4 M December 2003

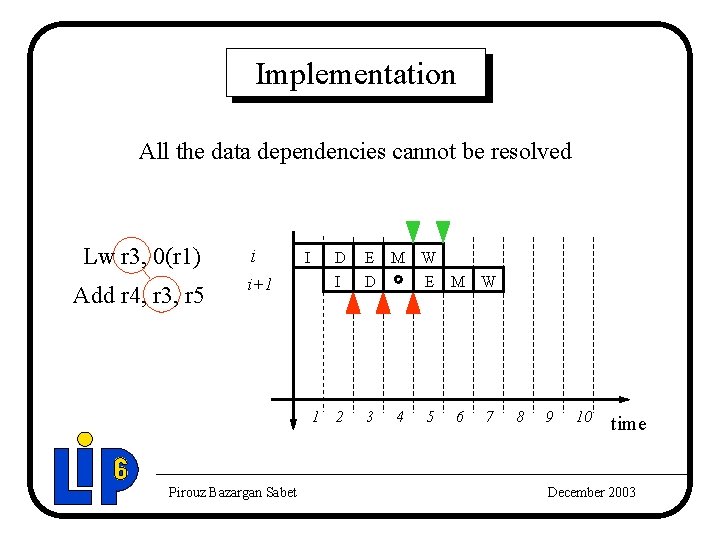

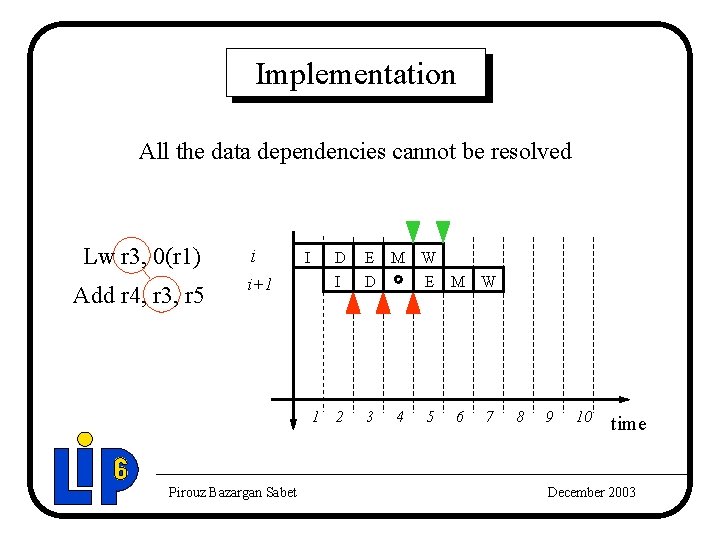

Implementation All the data dependencies cannot be resolved Lw r 3, 0(r 1) Add r 4, r 3, r 5 i I D i+1 1 Pirouz Bazargan Sabet E I M W D E E M W 2 3 4 5 6 7 8 9 10 time December 2003

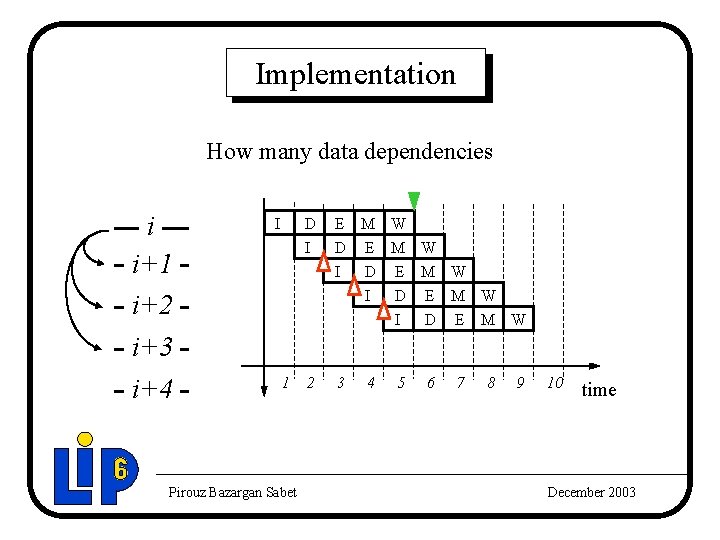

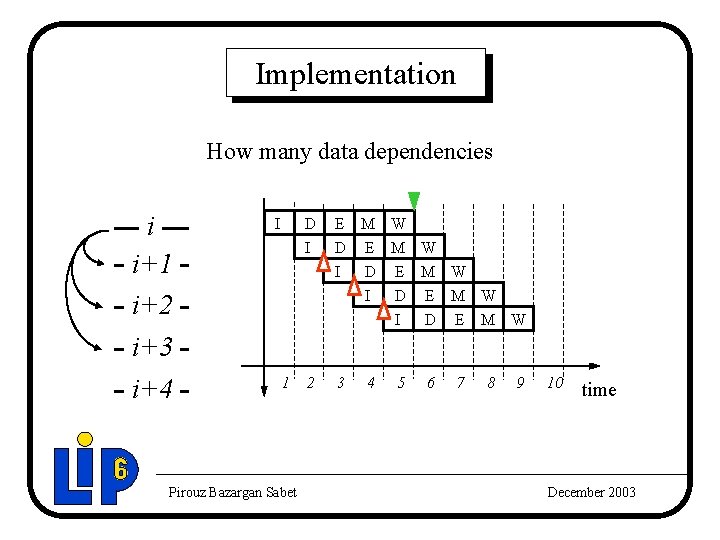

Implementation How many data dependencies i i+1 i+2 i+3 i+4 I D I 1 Pirouz Bazargan Sabet 2 E M W D E M W I D I E M W D E M W I D E M W 3 4 5 6 7 8 9 10 time December 2003

Implementation Is there any limitation to deep pipelines ? 2 limitations NO ! great number of delayed slots deep pipeline Pirouz Bazargan Sabet complex hardware control due to data dependencies December 2003