Hardware description languages introduction intellectual property IP introduction

- Slides: 33

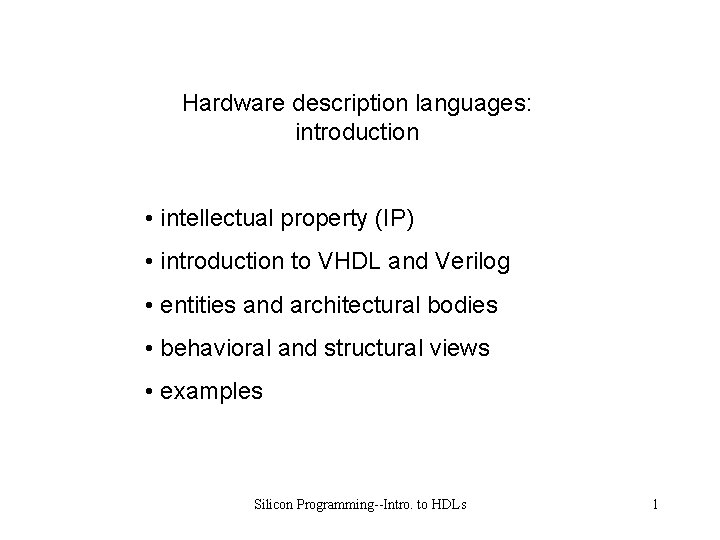

Hardware description languages: introduction • intellectual property (IP) • introduction to VHDL and Verilog • entities and architectural bodies • behavioral and structural views • examples Silicon Programming--Intro. to HDLs 1

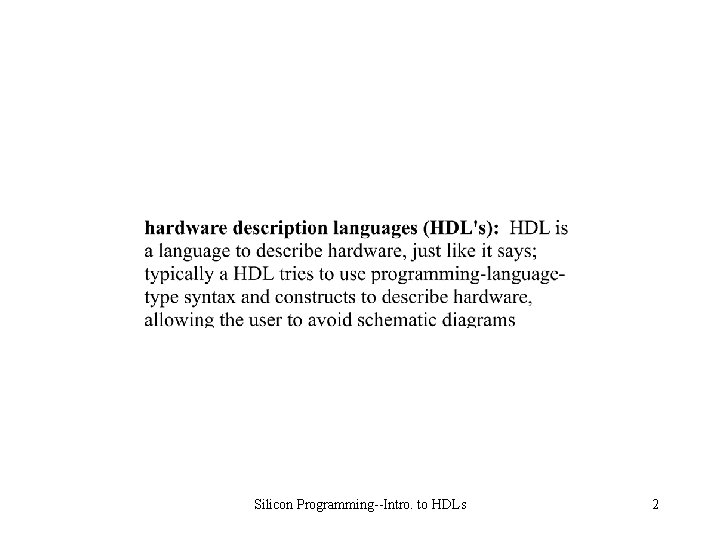

Silicon Programming--Intro. to HDLs 2

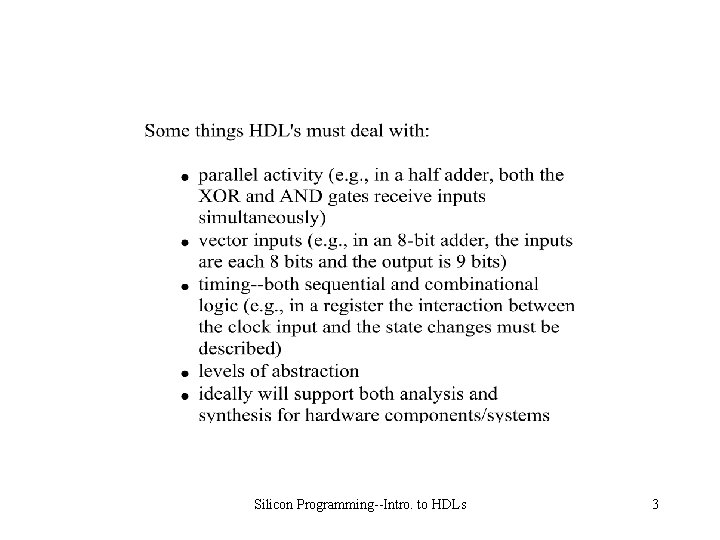

Silicon Programming--Intro. to HDLs 3

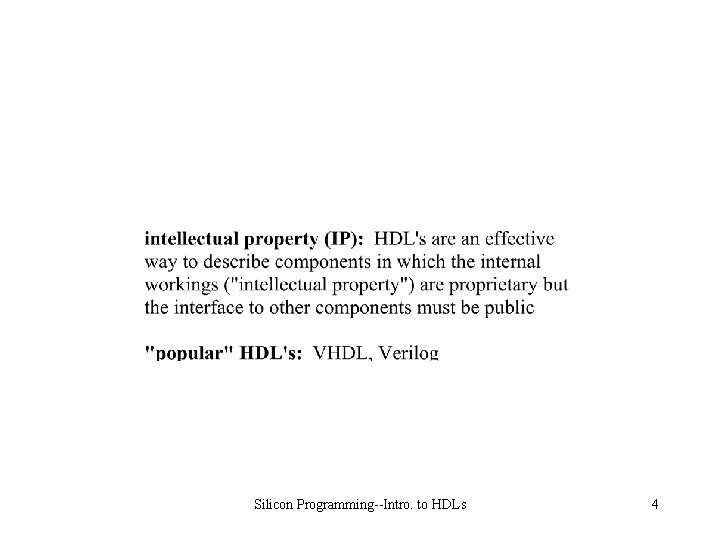

Silicon Programming--Intro. to HDLs 4

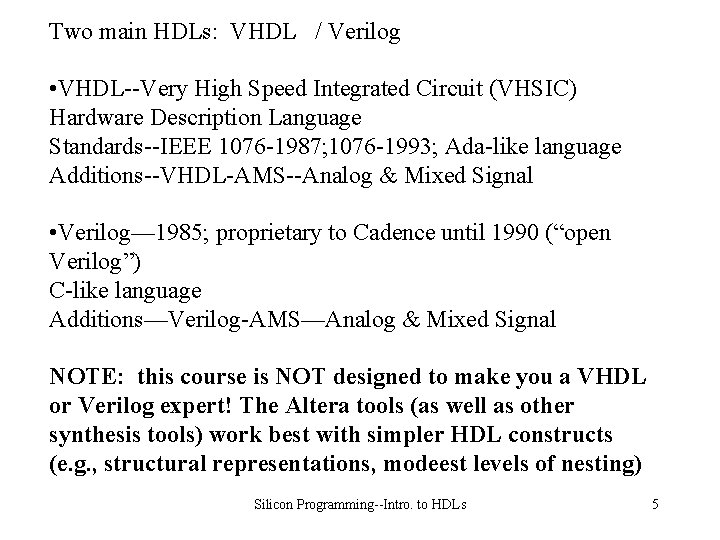

Two main HDLs: VHDL / Verilog • VHDL--Very High Speed Integrated Circuit (VHSIC) Hardware Description Language Standards--IEEE 1076 -1987; 1076 -1993; Ada-like language Additions--VHDL-AMS--Analog & Mixed Signal • Verilog— 1985; proprietary to Cadence until 1990 (“open Verilog”) C-like language Additions—Verilog-AMS—Analog & Mixed Signal NOTE: this course is NOT designed to make you a VHDL or Verilog expert! The Altera tools (as well as other synthesis tools) work best with simpler HDL constructs (e. g. , structural representations, modeest levels of nesting) Silicon Programming--Intro. to HDLs 5

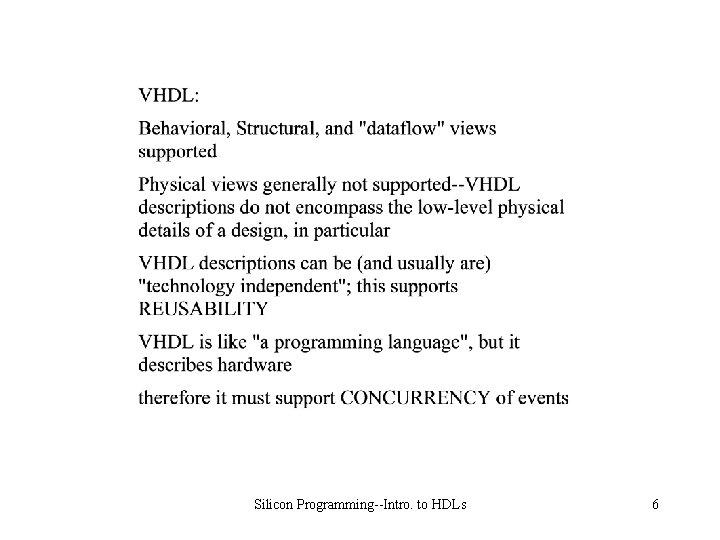

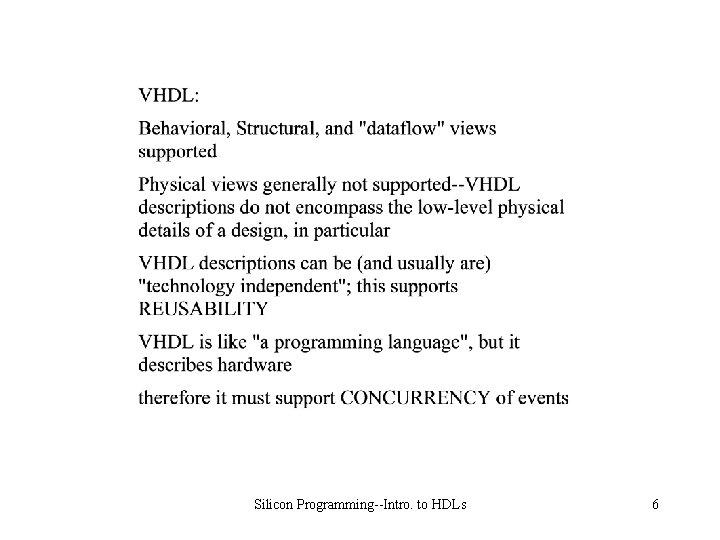

Silicon Programming--Intro. to HDLs 6

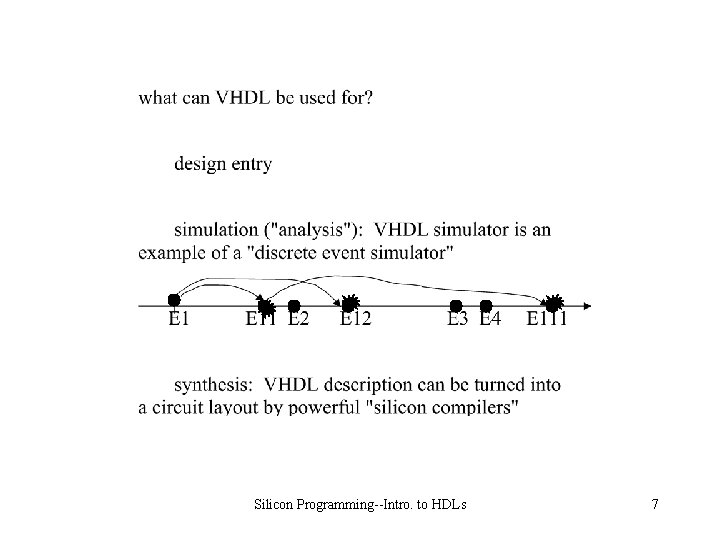

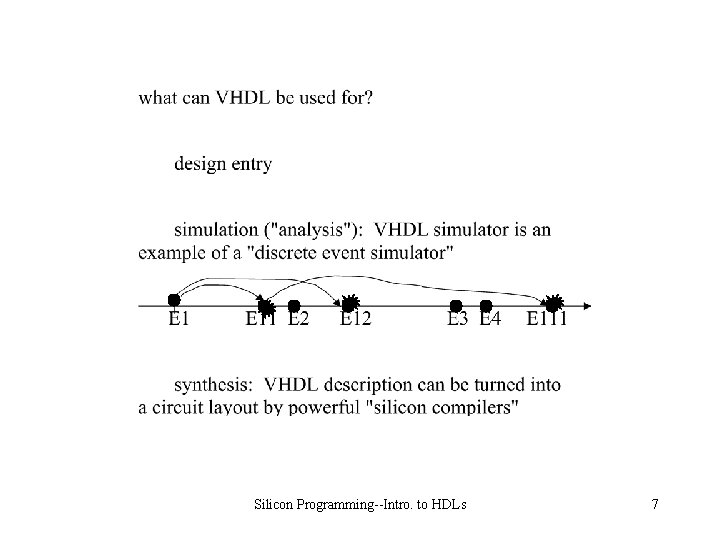

Silicon Programming--Intro. to HDLs 7

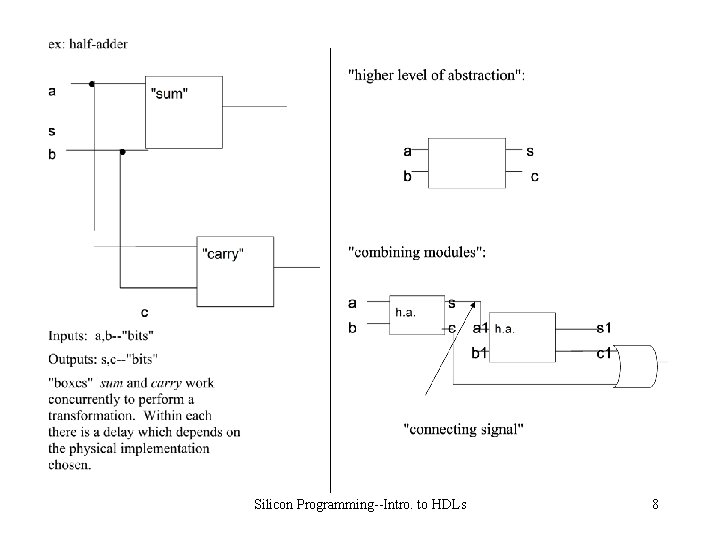

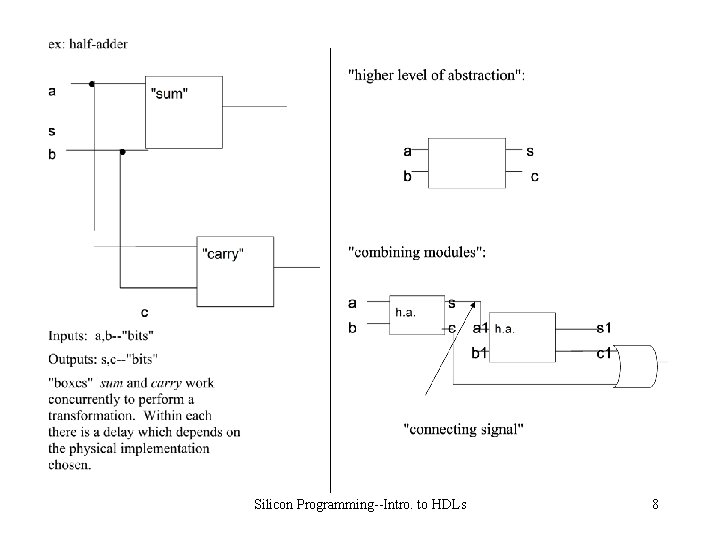

Silicon Programming--Intro. to HDLs 8

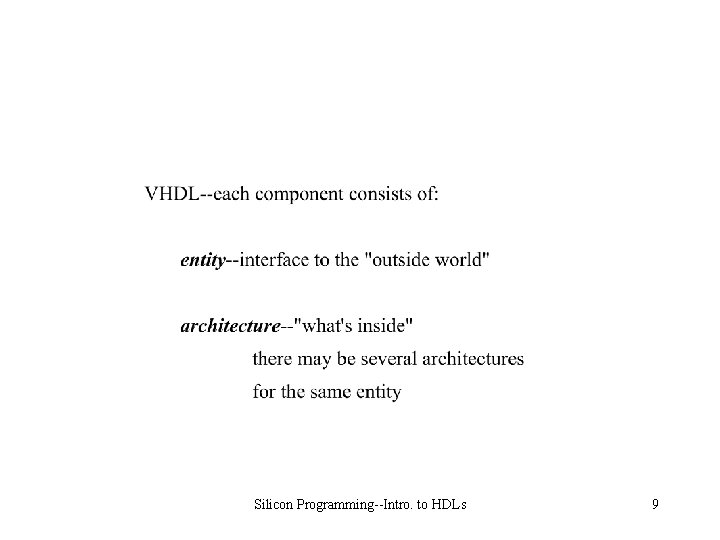

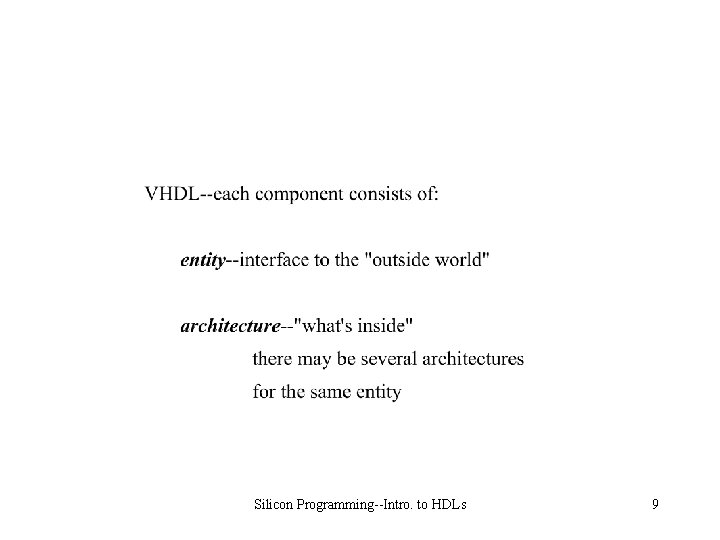

Silicon Programming--Intro. to HDLs 9

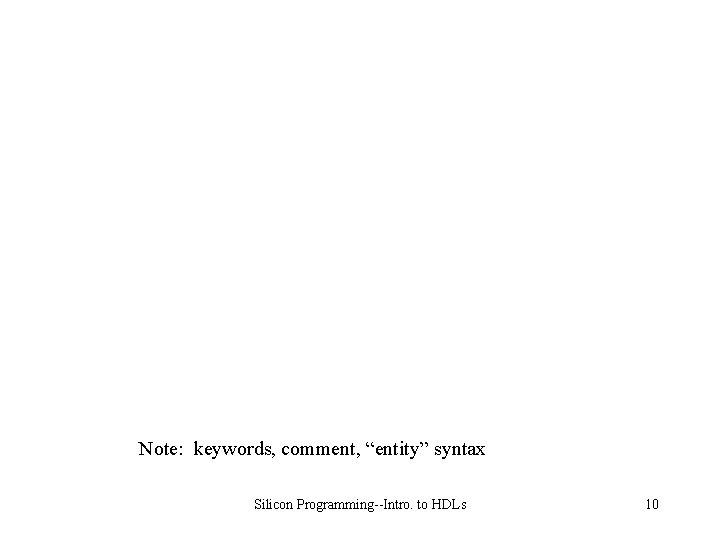

Note: keywords, comment, “entity” syntax Silicon Programming--Intro. to HDLs 10

Silicon Programming--Intro. to HDLs 11

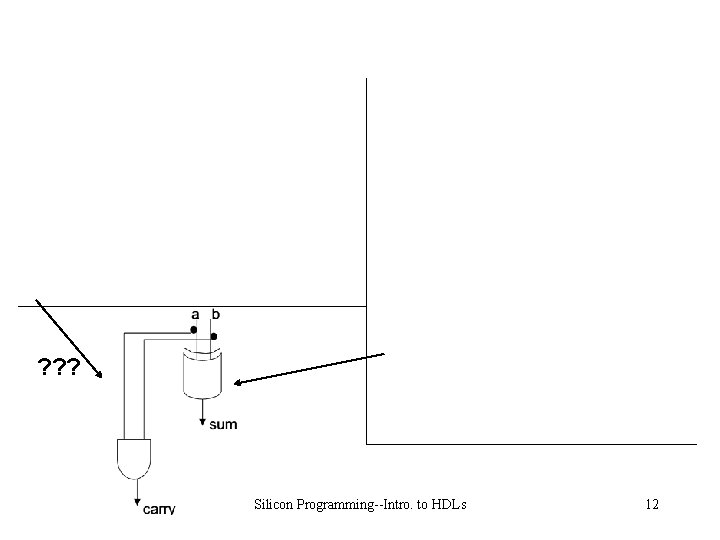

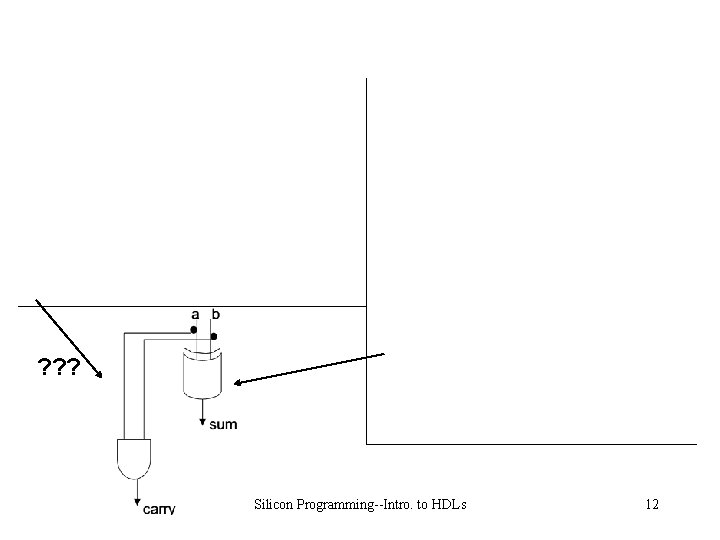

? ? ? Silicon Programming--Intro. to HDLs 12

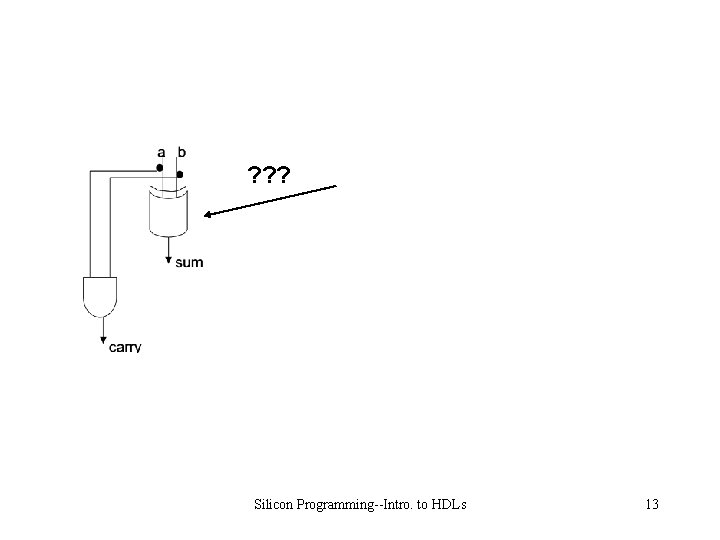

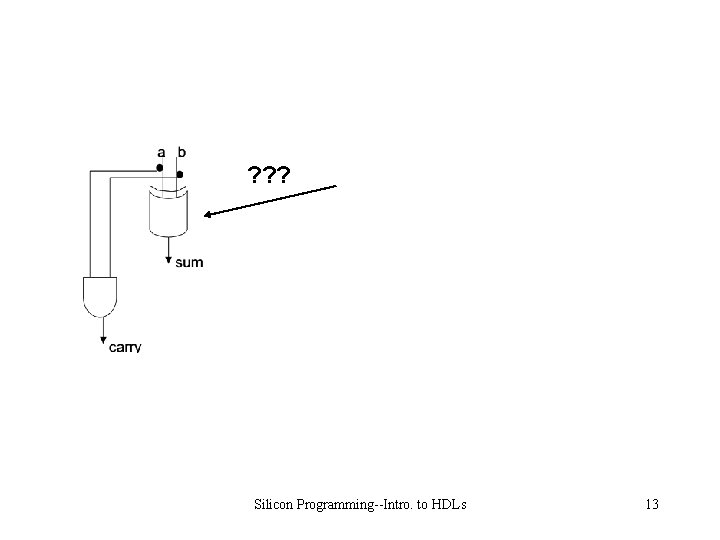

? ? ? Silicon Programming--Intro. to HDLs 13

Full adder example: Silicon Programming--Intro. to HDLs 14

Silicon Programming--Intro. to HDLs 15

Silicon Programming--Intro. to HDLs 16

Silicon Programming--Intro. to HDLs 17

Silicon Programming--Intro. to HDLs 18

Silicon Programming--Intro. to HDLs 19

Silicon Programming--Intro. to HDLs 20

Silicon Programming--Intro. to HDLs 21

Silicon Programming--Intro. to HDLs 22

Silicon Programming--Intro. to HDLs 23

Silicon Programming--Intro. to HDLs 24

Verilog: The following is taken from the introduction by Dan Hyde at: http: //www. eg. bucknell. edu/~cs 320/1995 -fall/verilog-manual. html Other references can be found at: http: //www. verilog. net/docs. html Architectural, behavioral, gate, and switch levels supported Gate level: logic elements (structural) Switch level: transistor level Verilog program can be used for design, simulation, synthesis Basic construct: module Verilog program consists of interconnected modules Usually a “top” module encapsulates all the others Silicon Programming--Intro. to HDLs 25

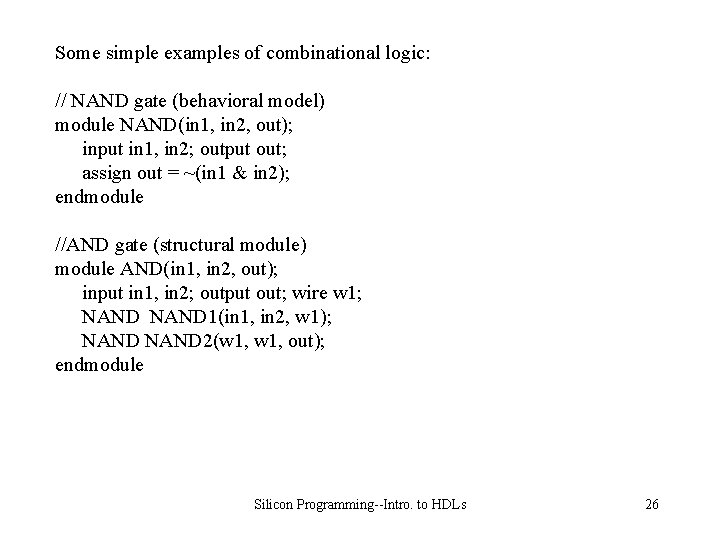

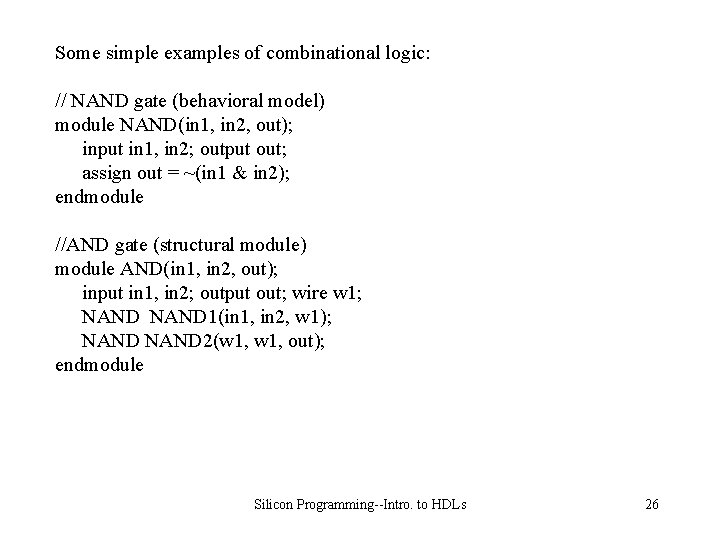

Some simple examples of combinational logic: // NAND gate (behavioral model) module NAND(in 1, in 2, out); input in 1, in 2; output out; assign out = ~(in 1 & in 2); endmodule //AND gate (structural module) module AND(in 1, in 2, out); input in 1, in 2; output out; wire w 1; NAND 1(in 1, in 2, w 1); NAND 2(w 1, out); endmodule Silicon Programming--Intro. to HDLs 26

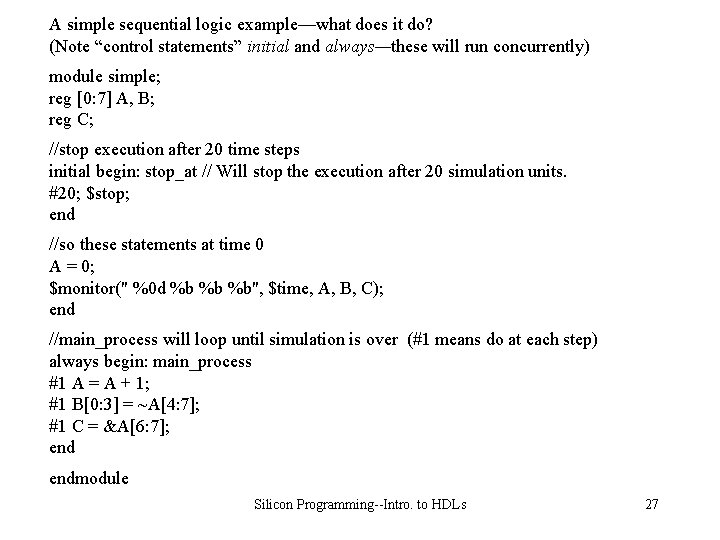

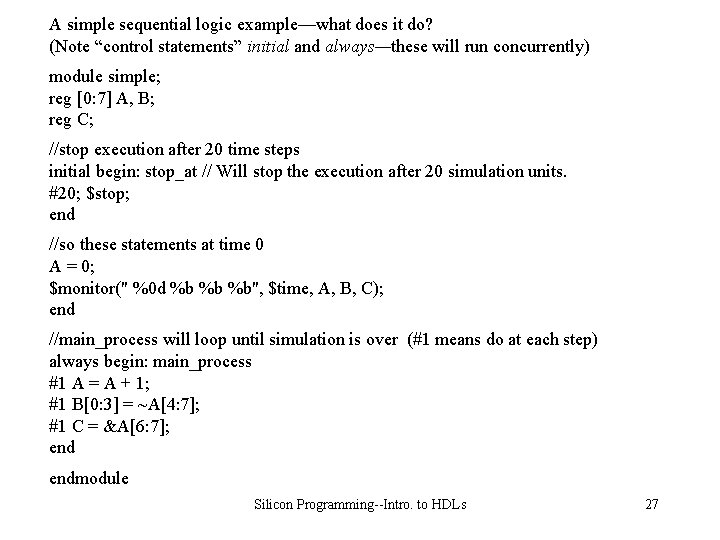

A simple sequential logic example—what does it do? (Note “control statements” initial and always—these will run concurrently) module simple; reg [0: 7] A, B; reg C; //stop execution after 20 time steps initial begin: stop_at // Will stop the execution after 20 simulation units. #20; $stop; end //so these statements at time 0 A = 0; $monitor(" %0 d %b %b %b", $time, A, B, C); end //main_process will loop until simulation is over (#1 means do at each step) always begin: main_process #1 A = A + 1; #1 B[0: 3] = ~A[4: 7]; #1 C = &A[6: 7]; endmodule Silicon Programming--Intro. to HDLs 27

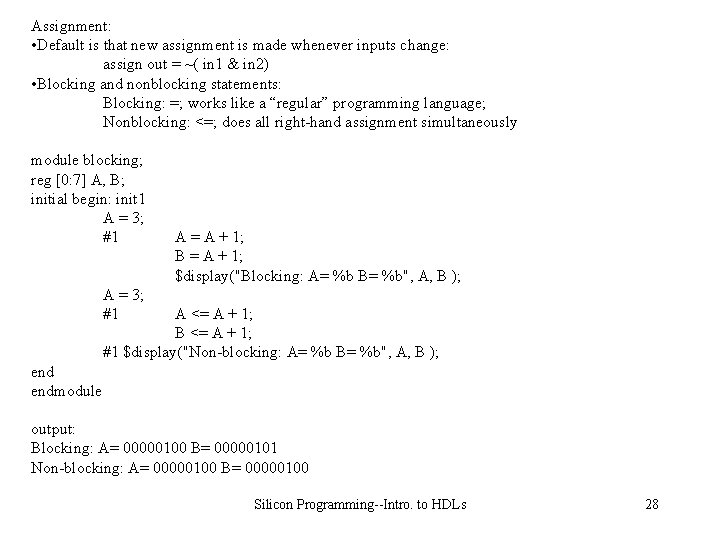

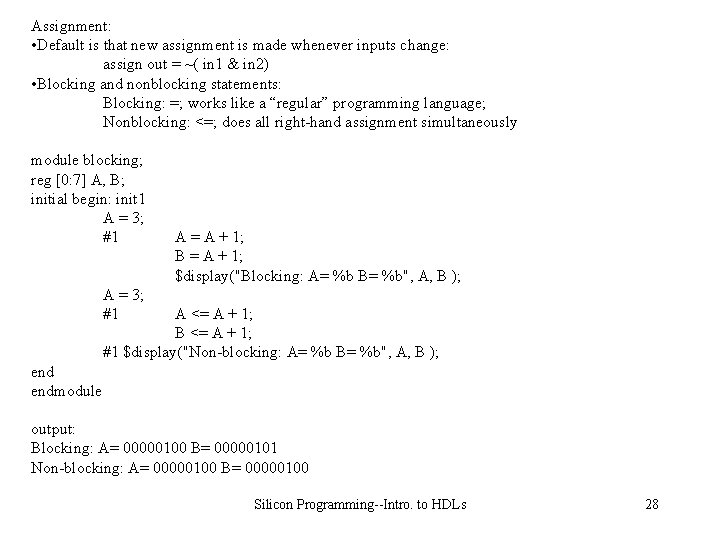

Assignment: • Default is that new assignment is made whenever inputs change: assign out = ~( in 1 & in 2) • Blocking and nonblocking statements: Blocking: =; works like a “regular” programming language; Nonblocking: <=; does all right-hand assignment simultaneously module blocking; reg [0: 7] A, B; initial begin: init 1 A = 3; #1 A = A + 1; B = A + 1; $display("Blocking: A= %b B= %b", A, B ); A = 3; #1 A <= A + 1; B <= A + 1; #1 $display("Non-blocking: A= %b B= %b", A, B ); endmodule output: Blocking: A= 00000100 B= 00000101 Non-blocking: A= 00000100 B= 00000100 Silicon Programming--Intro. to HDLs 28

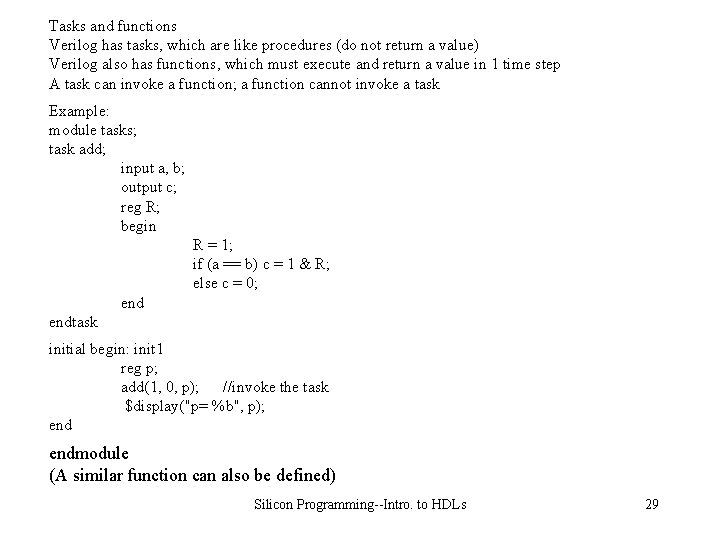

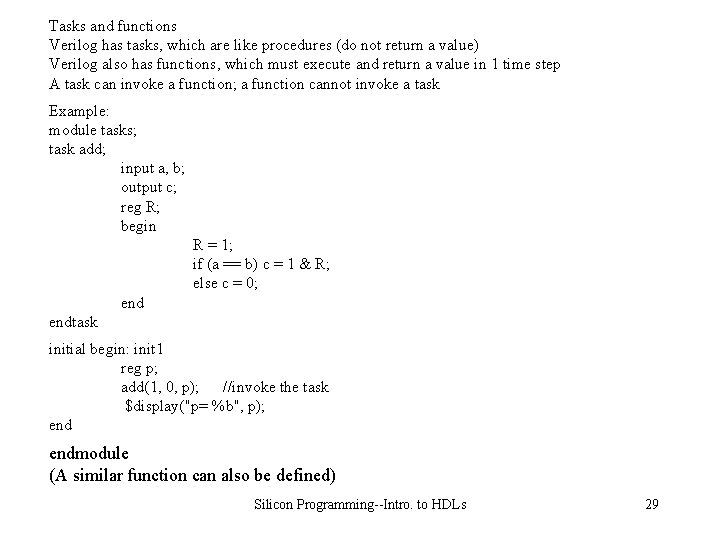

Tasks and functions Verilog has tasks, which are like procedures (do not return a value) Verilog also has functions, which must execute and return a value in 1 time step A task can invoke a function; a function cannot invoke a task Example: module tasks; task add; input a, b; output c; reg R; begin R = 1; if (a == b) c = 1 & R; else c = 0; endtask initial begin: init 1 reg p; add(1, 0, p); //invoke the task $display("p= %b", p); endmodule (A similar function can also be defined) Silicon Programming--Intro. to HDLs 29

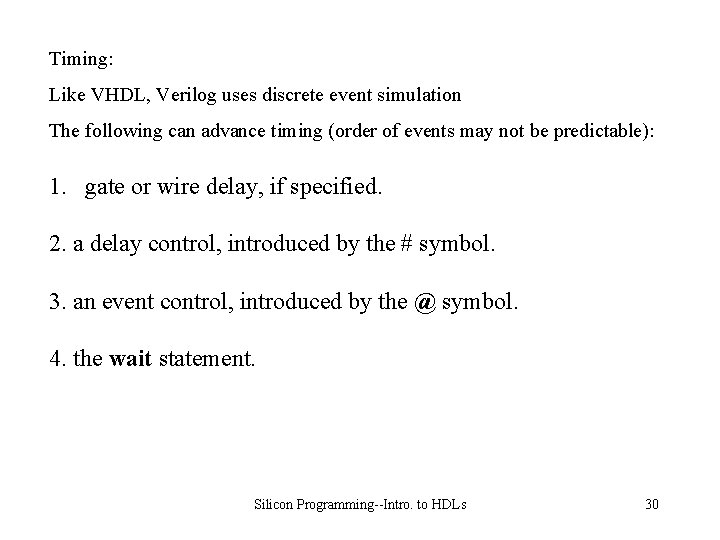

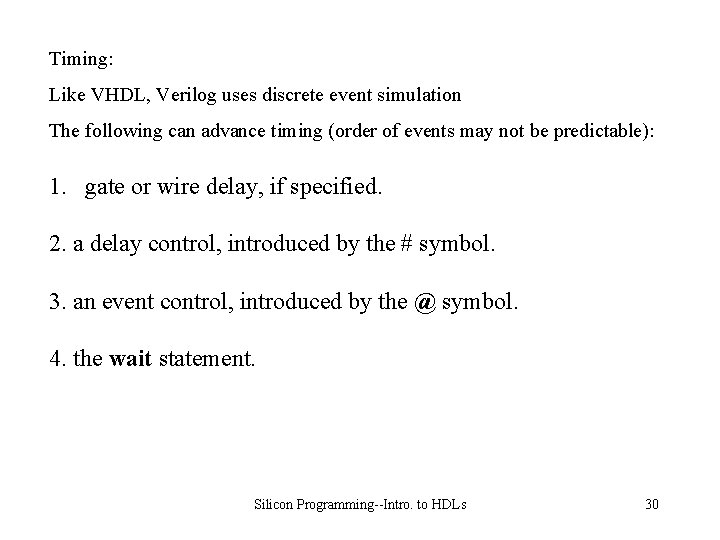

Timing: Like VHDL, Verilog uses discrete event simulation The following can advance timing (order of events may not be predictable): 1. gate or wire delay, if specified. 2. a delay control, introduced by the # symbol. 3. an event control, introduced by the @ symbol. 4. the wait statement. Silicon Programming--Intro. to HDLs 30

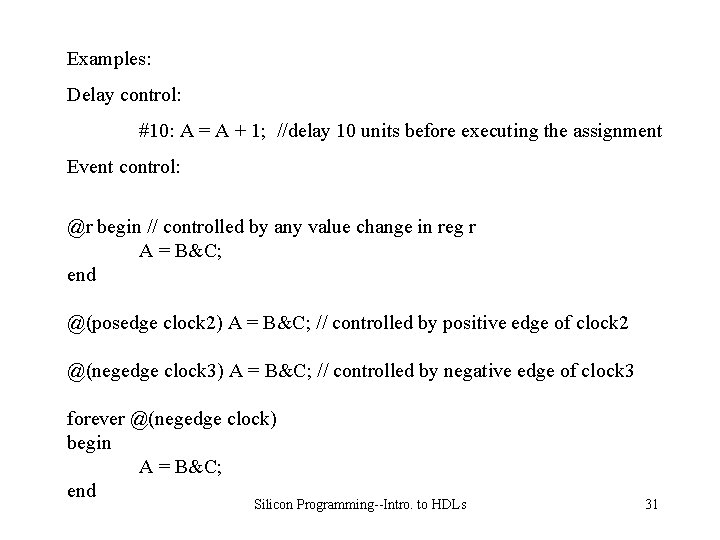

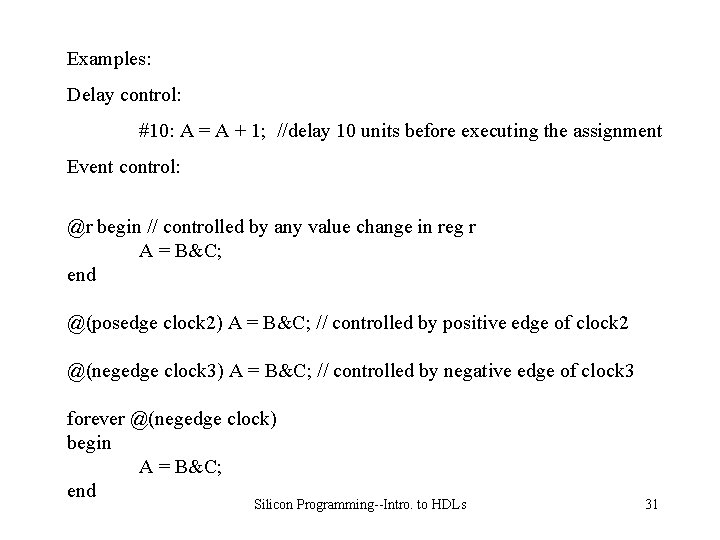

Examples: Delay control: #10: A = A + 1; //delay 10 units before executing the assignment Event control: @r begin // controlled by any value change in reg r A = B&C; end @(posedge clock 2) A = B&C; // controlled by positive edge of clock 2 @(negedge clock 3) A = B&C; // controlled by negative edge of clock 3 forever @(negedge clock) begin A = B&C; end Silicon Programming--Intro. to HDLs 31

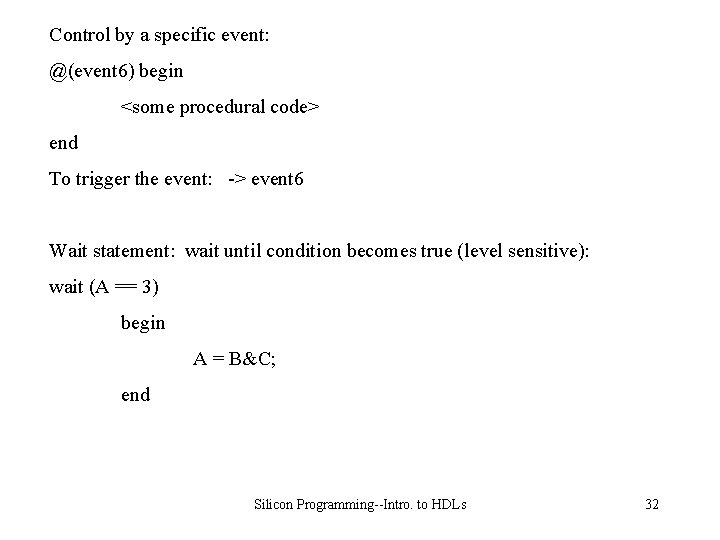

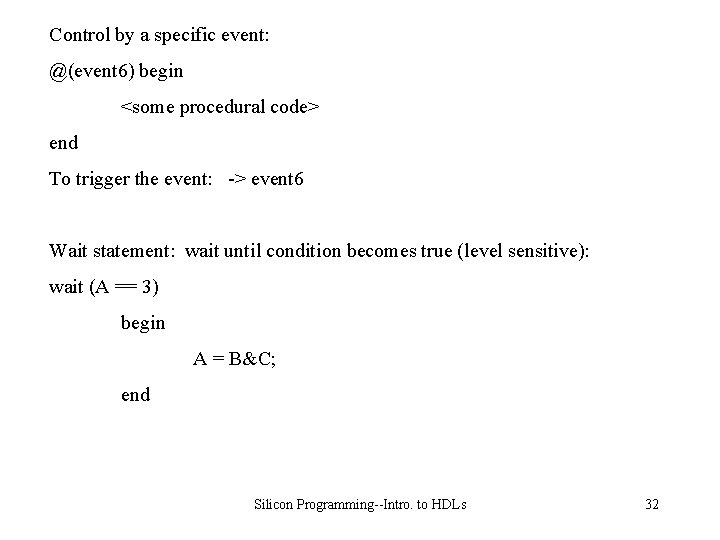

Control by a specific event: @(event 6) begin <some procedural code> end To trigger the event: -> event 6 Wait statement: wait until condition becomes true (level sensitive): wait (A == 3) begin A = B&C; end Silicon Programming--Intro. to HDLs 32

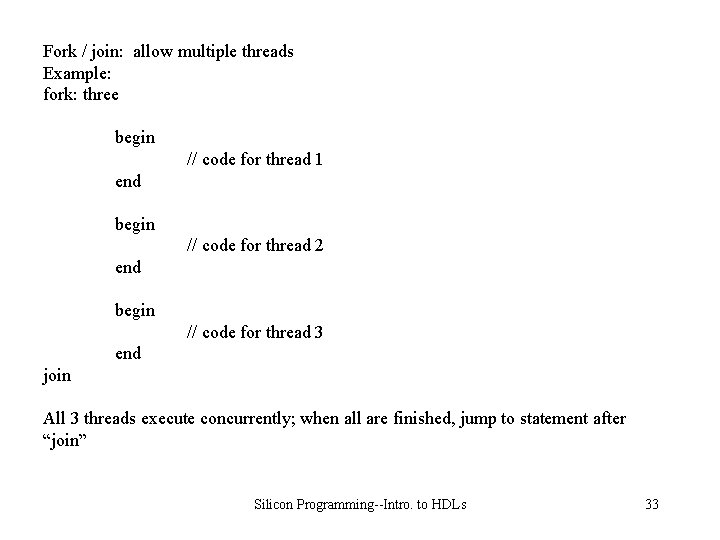

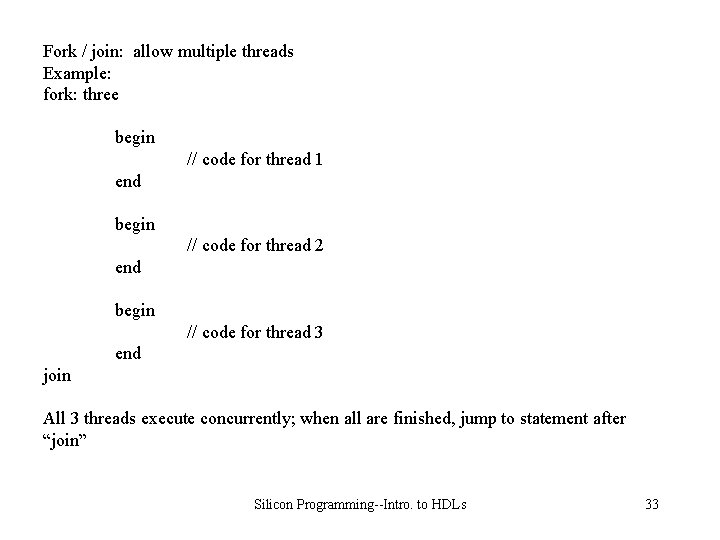

Fork / join: allow multiple threads Example: fork: three begin // code for thread 1 end begin // code for thread 2 end begin // code for thread 3 end join All 3 threads execute concurrently; when all are finished, jump to statement after “join” Silicon Programming--Intro. to HDLs 33