FRUGAL IP LOOKUP BASED ON A PARALLEL SEARCH

FRUGAL IP LOOKUP BASED ON A PARALLEL SEARCH Author: Zoran Cica and Aleksandra Smiljanic 1 Publisher/Conf. : IEEE Workshop on High Performance Switching and Routing, HPSR 2009 Speaker: Han-Jhen Guo Date: 2009. 16

OUTLINE Parallelized Frugal Lookup (PFL) Algorithm Idea Introduction Overall Architecture Level Module Performance 2

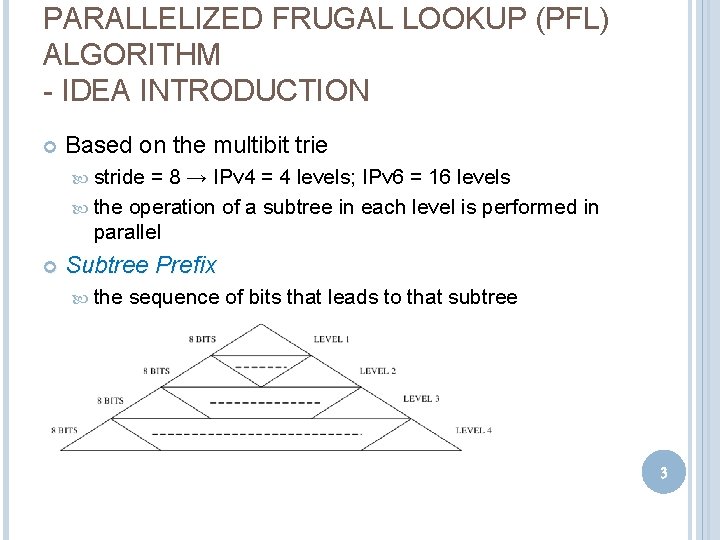

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - IDEA INTRODUCTION Based on the multibit trie stride = 8 → IPv 4 = 4 levels; IPv 6 = 16 levels the operation of a subtree in each level is performed in parallel Subtree Prefix the sequence of bits that leads to that subtree 3

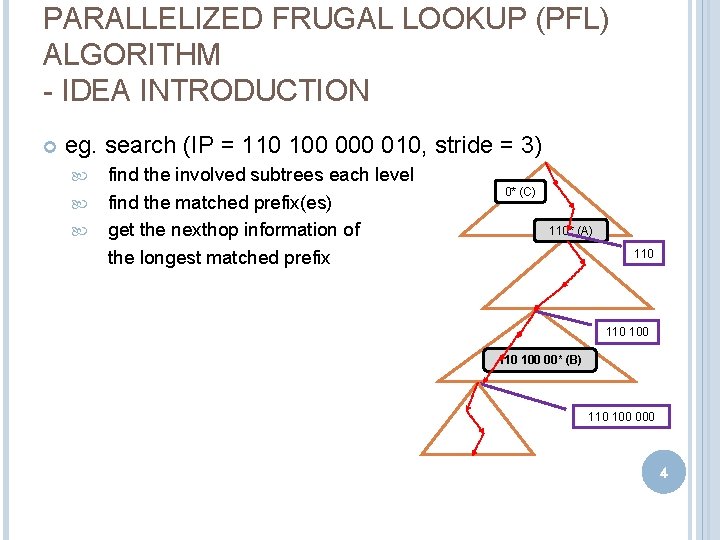

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - IDEA INTRODUCTION eg. search (IP = 110 100 010, stride = 3) find the involved subtrees each level find the matched prefix(es) get the nexthop information of the longest matched prefix 0* (C) 110* (A) 110 100 00* (B) 110 100 000 4

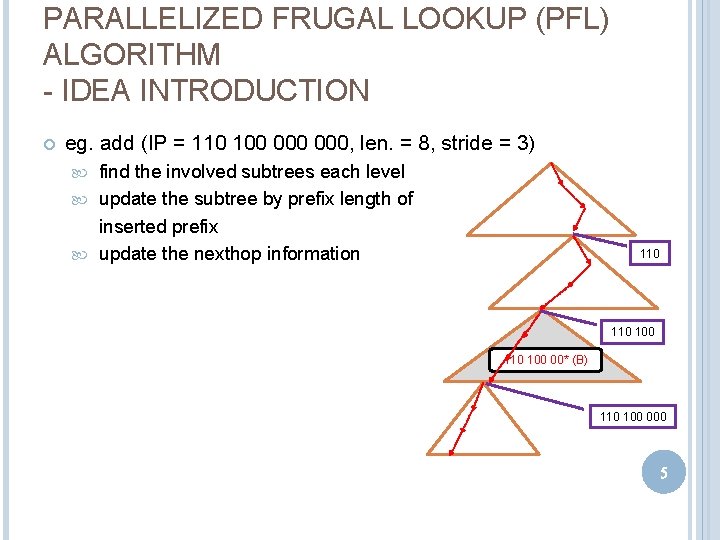

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - IDEA INTRODUCTION eg. add (IP = 110 100 000, len. = 8, stride = 3) find the involved subtrees each level update the subtree by prefix length of inserted prefix update the nexthop information 110 100 00* (B) 110 100 000 5

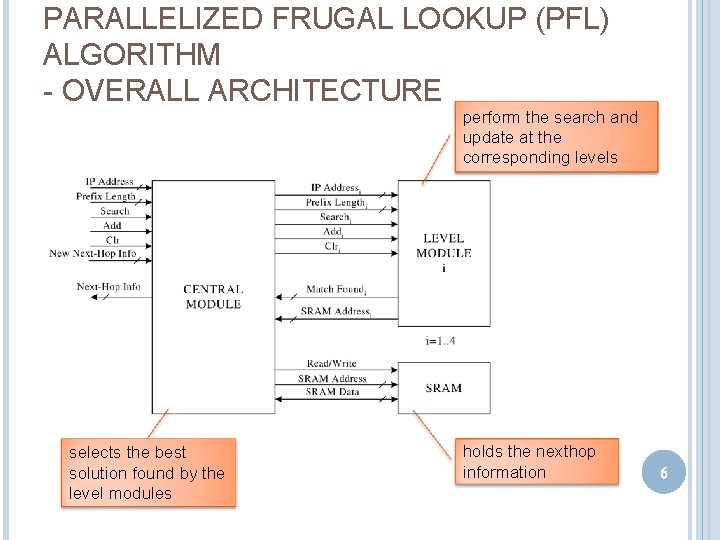

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - OVERALL ARCHITECTURE perform the search and update at the corresponding levels selects the best solution found by the level modules holds the nexthop information 6

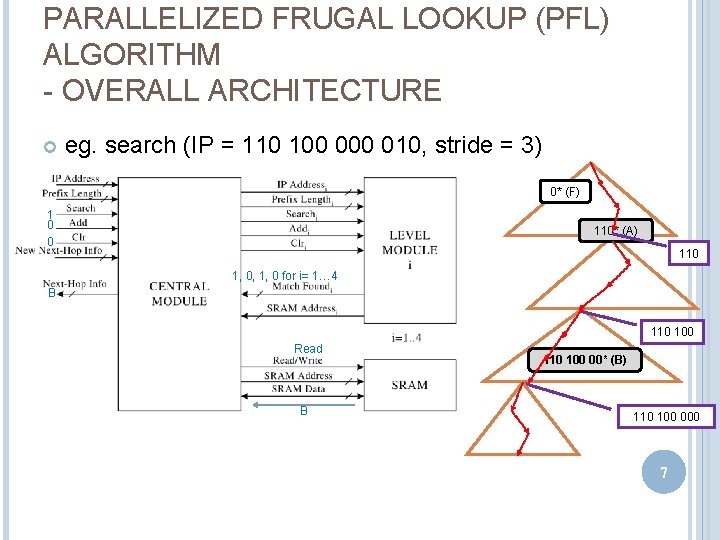

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - OVERALL ARCHITECTURE eg. search (IP = 110 100 010, stride = 3) 0* (F) 1 0 0 110* (A) 110 1, 0, 1, 0 for i= 1… 4 B 110 100 Read B 110 100 00* (B) 110 100 000 7

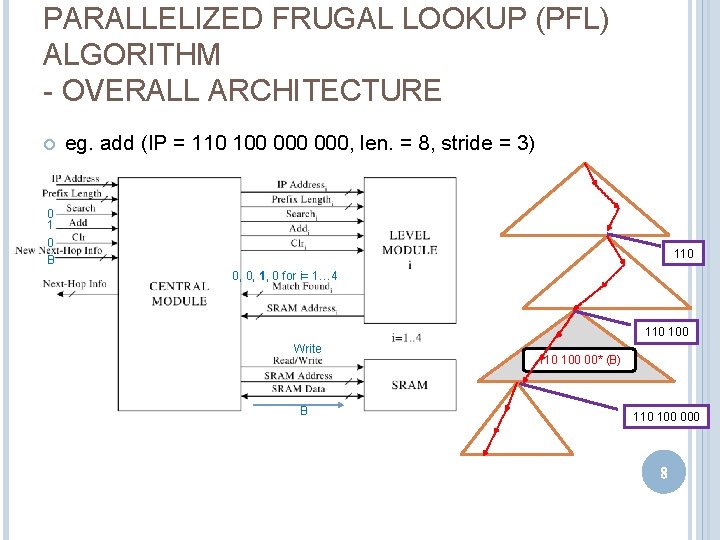

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - OVERALL ARCHITECTURE eg. add (IP = 110 100 000, len. = 8, stride = 3) 0 1 0 B 110 0, 0, 1, 0 for i= 1… 4 110 100 Write B 110 100 00* (B) 110 100 000 8

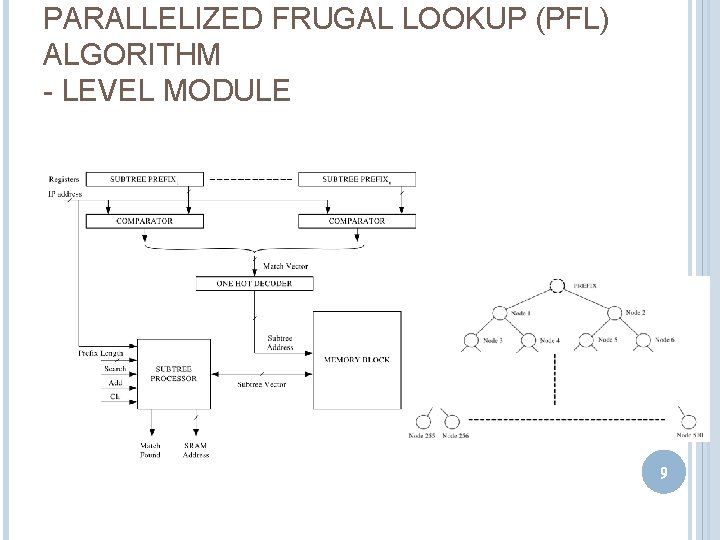

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - LEVEL MODULE 9

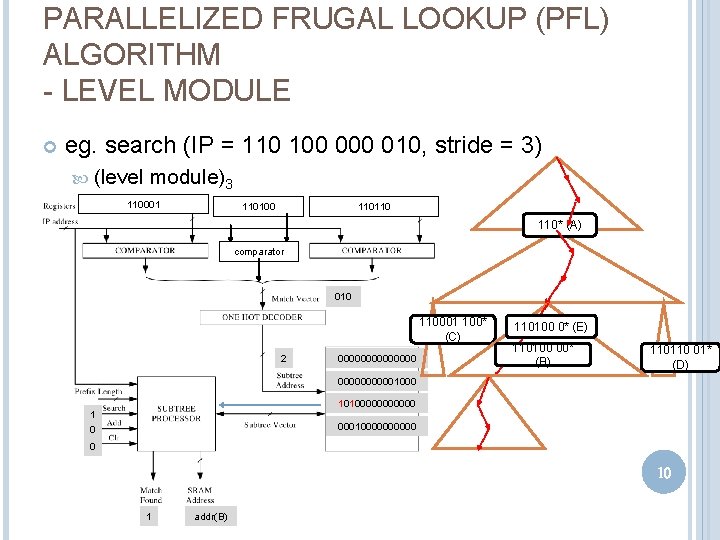

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - LEVEL MODULE eg. search (IP = 110 100 010, stride = 3) (level module)3 110001 110100 110110 110* (A) comparator 010 110001 100* (C) 2 0000000 110100 0* (E) 110100 00* (B) 110110 01* (D) 000001000 101000000 1 0 000100000 0 10 1 addr(B)

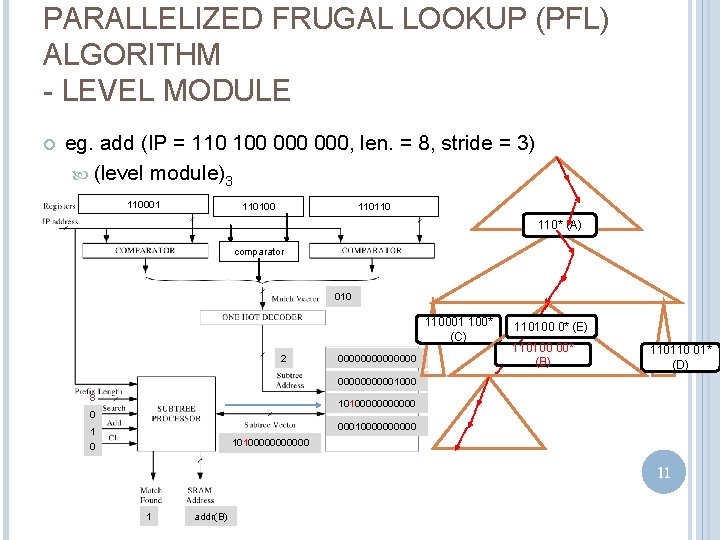

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - LEVEL MODULE eg. add (IP = 110 100 000, len. = 8, stride = 3) (level module)3 110001 110100 110110 110* (A) comparator 010 110001 100* (C) 2 0000000 110100 0* (E) 110100 00* (B) 110110 01* (D) 000001000 8 10000000 101000000 0 000100000 1 0 101000000 11 1 addr(B)

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - LEVEL MODULE For saving memory (resources are not used for an empty subtree) associating one counter to each register for counting the number of prefixes in each subtree with subtree prefix to the register 12

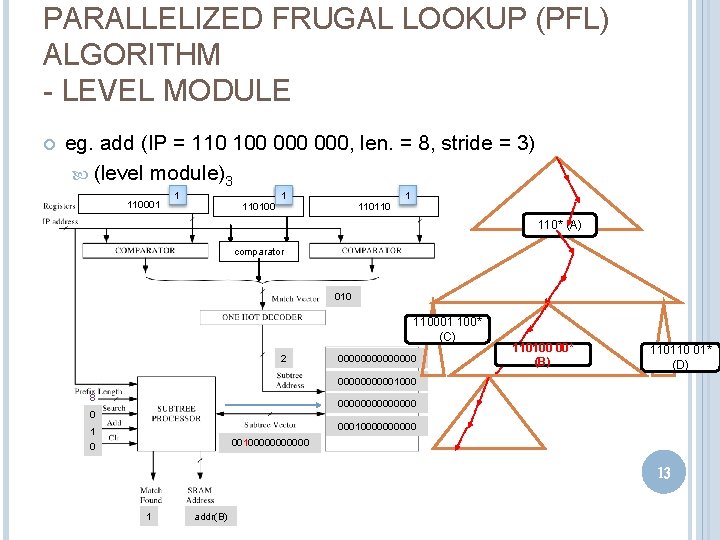

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - LEVEL MODULE eg. add (IP = 110 100 000, len. = 8, stride = 3) (level module)3 110001 1 0 1 1 110100 110110 110* (A) comparator 010 110001 100* (C) 2 0000000 110100 00* (B) 110110 01* (D) 000001000 8 0000000 0 000100000 1 0 001000000 13 1 addr(B)

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - PERFORMANCE Software Quartus II 8. 1 Chip Altera Cyclone II and III families, for IPv 4 and IPv 6 addresses, respectively Table 32. 5 K ~ 134 K entries 14

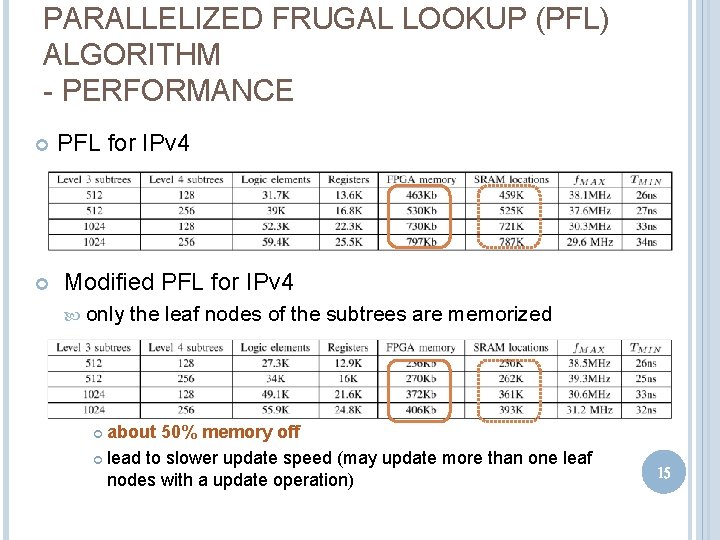

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - PERFORMANCE PFL for IPv 4 Modified PFL for IPv 4 only the leaf nodes of the subtrees are memorized about 50% memory off lead to slower update speed (may update more than one leaf nodes with a update operation) 15

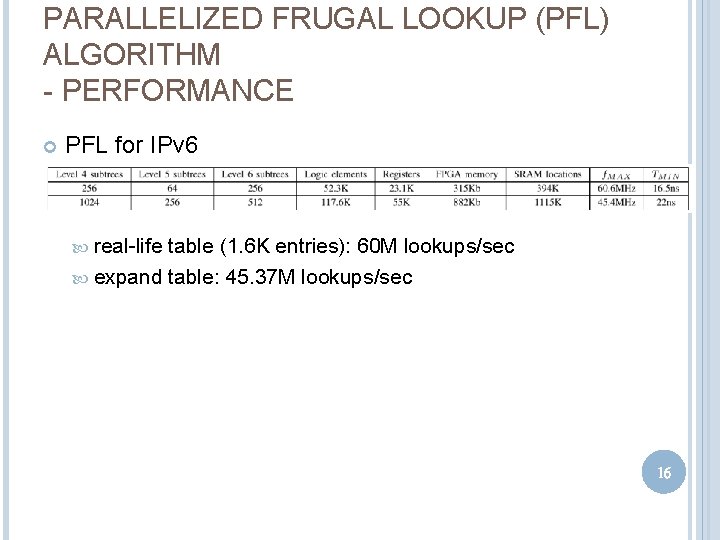

PARALLELIZED FRUGAL LOOKUP (PFL) ALGORITHM - PERFORMANCE PFL for IPv 6 real-life table (1. 6 K entries): 60 M lookups/sec expand table: 45. 37 M lookups/sec 16

Thanks for your listening! 17

- Slides: 17