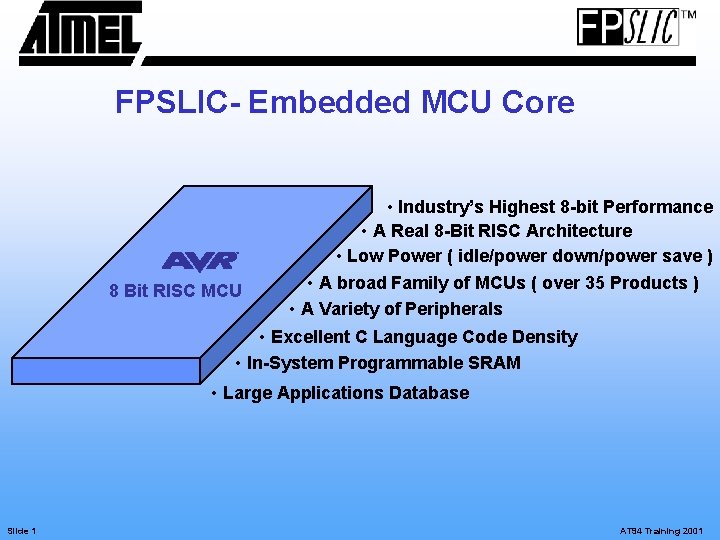

FPSLIC Embedded MCU Core 8 Bit RISC MCU

FPSLIC- Embedded MCU Core 8 Bit RISC MCU • Industry’s Highest 8 -bit Performance • A Real 8 -Bit RISC Architecture • Low Power ( idle/power down/power save ) • A broad Family of MCUs ( over 35 Products ) • A Variety of Peripherals • Excellent C Language Code Density • In-System Programmable SRAM • Large Applications Database Slide 1 AT 94 Training 2001

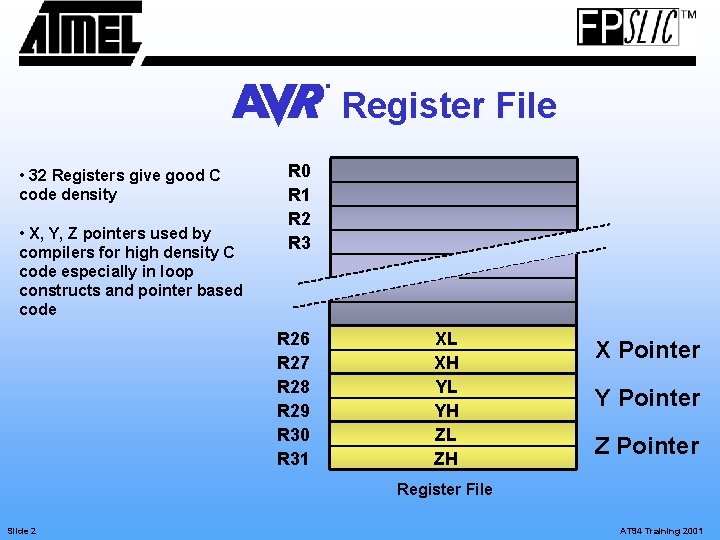

Register File • 32 Registers give good C code density • X, Y, Z pointers used by compilers for high density C code especially in loop constructs and pointer based code R 0 R 1 R 2 R 3 R 26 R 27 R 28 R 29 R 30 R 31 XL XH YL YH ZL ZH X Pointer Y Pointer Z Pointer Register File Slide 2 AT 94 Training 2001

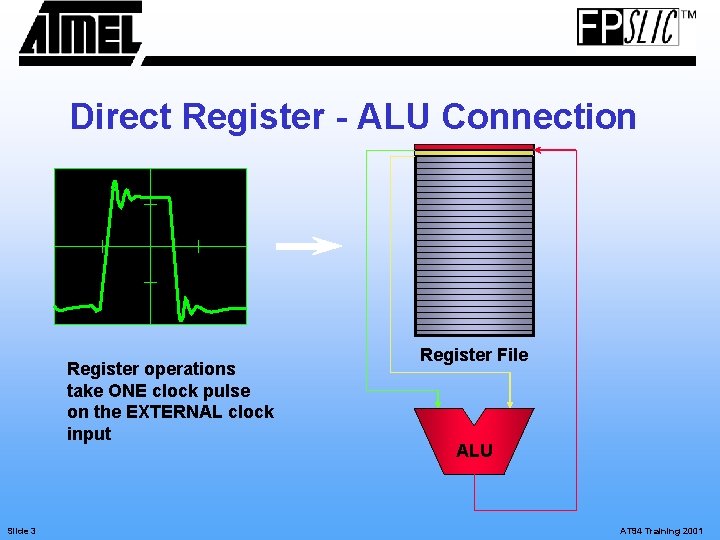

Direct Register - ALU Connection Register operations take ONE clock pulse on the EXTERNAL clock input Slide 3 Register File ALU AT 94 Training 2001

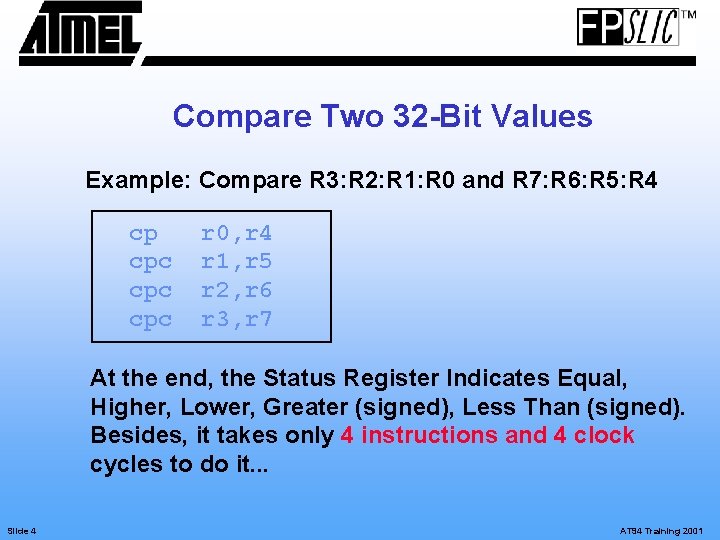

Compare Two 32 -Bit Values Example: Compare R 3: R 2: R 1: R 0 and R 7: R 6: R 5: R 4 cp cpc cpc r 0, r 4 r 1, r 5 r 2, r 6 r 3, r 7 At the end, the Status Register Indicates Equal, Higher, Lower, Greater (signed), Less Than (signed). Besides, it takes only 4 instructions and 4 clock cycles to do it. . . Slide 4 AT 94 Training 2001

What makes the AVR better? • Excellent support for 32/16 -bit arithmetic's. • (Zero-Flag) Propagation • A lot of registers - eliminate moves to and from SRAM • Single Cycle execution • 127+ powerful instructions available Slide 5 AT 94 Training 2001

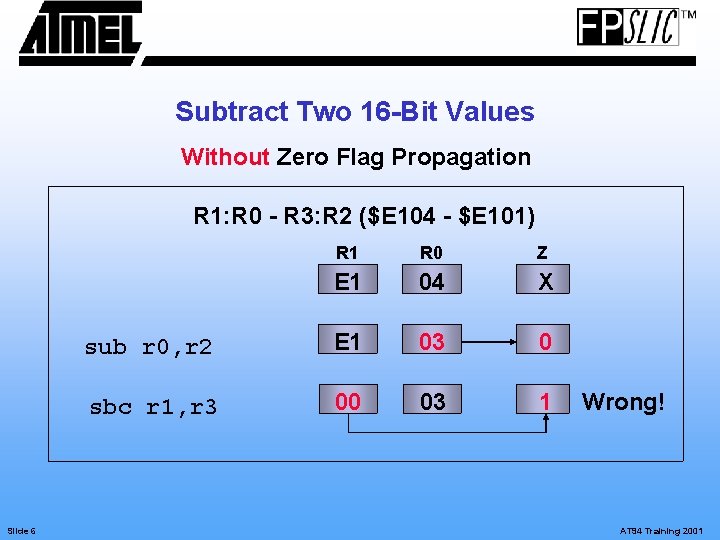

Subtract Two 16 -Bit Values Without Zero Flag Propagation R 1: R 0 - R 3: R 2 ($E 104 - $E 101) Slide 6 R 1 R 0 Z E 1 04 X sub r 0, r 2 E 1 03 0 sbc r 1, r 3 00 03 1 Wrong! AT 94 Training 2001

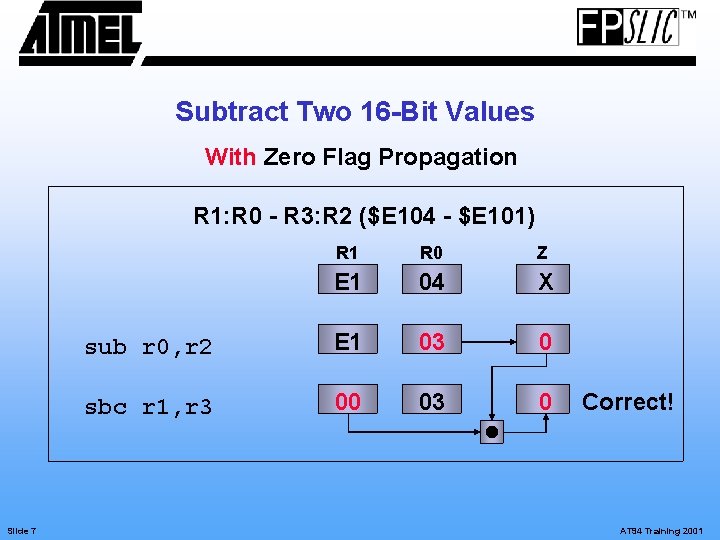

Subtract Two 16 -Bit Values With Zero Flag Propagation R 1: R 0 - R 3: R 2 ($E 104 - $E 101) Slide 7 R 1 R 0 Z E 1 04 X sub r 0, r 2 E 1 03 0 sbc r 1, r 3 00 03 0 Correct! AT 94 Training 2001

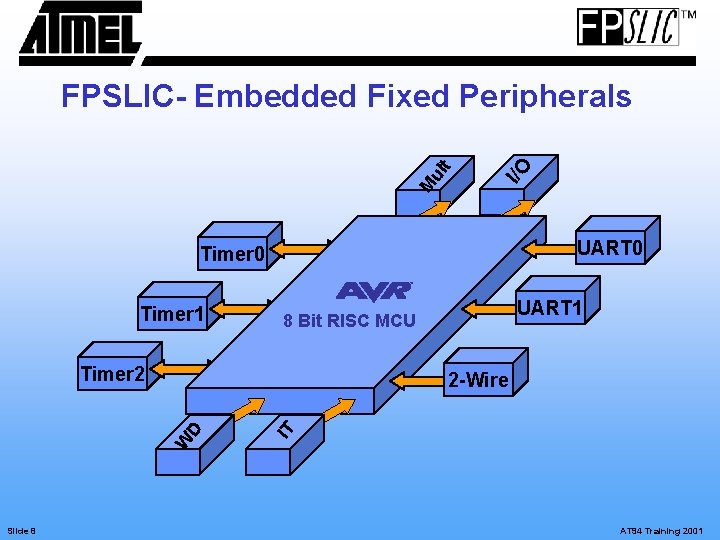

I/O M ul t FPSLIC- Embedded Fixed Peripherals UART 0 Timer 1 Timer 2 IT D 2 -Wire W Slide 8 UART 1 8 Bit RISC MCU AT 94 Training 2001

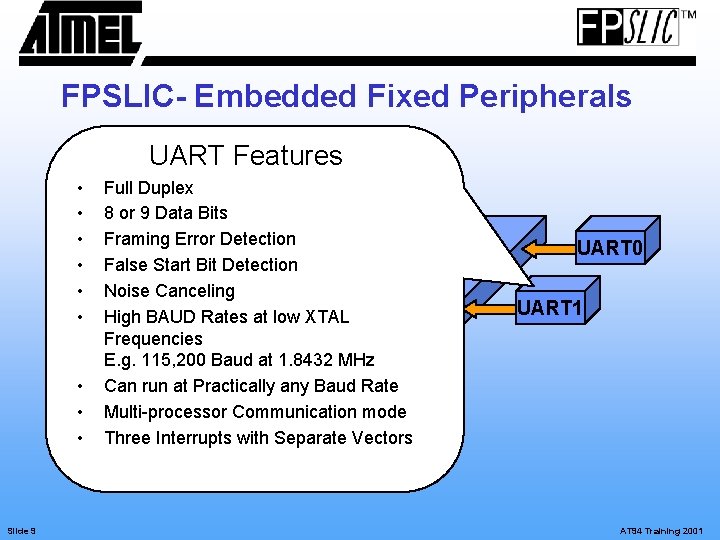

FPSLIC- Embedded Fixed Peripherals UART Features • • • Slide 9 Full Duplex 8 or 9 Data Bits Framing Error Detection False Start Bit Detection Noise Canceling High BAUD Rates at low XTAL Frequencies E. g. 115, 200 Baud at 1. 8432 MHz Can run at Practically any Baud Rate Multi-processor Communication mode Three Interrupts with Separate Vectors UART 0 UART 1 AT 94 Training 2001

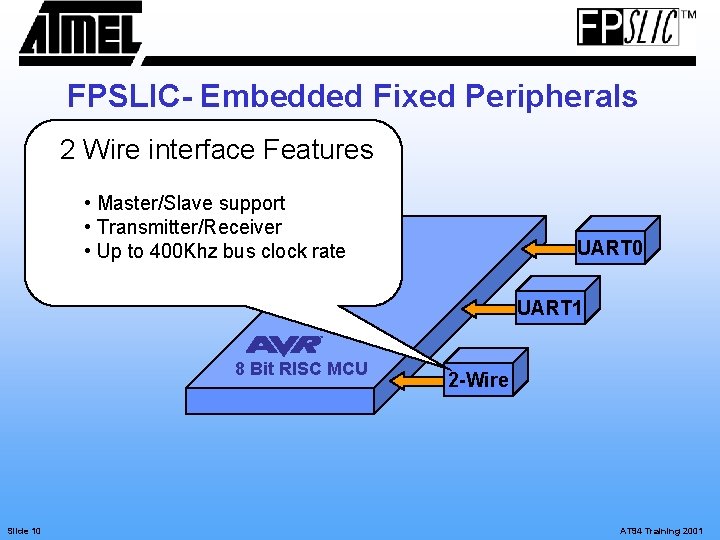

FPSLIC- Embedded Fixed Peripherals 2 Wire interface Features • Master/Slave support • Transmitter/Receiver • Up to 400 Khz bus clock rate UART 0 UART 1 8 Bit RISC MCU Slide 10 2 -Wire AT 94 Training 2001

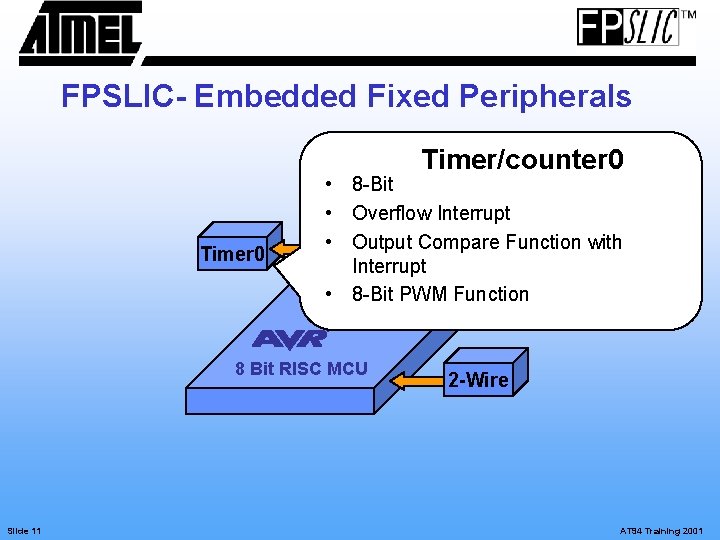

FPSLIC- Embedded Fixed Peripherals Timer/counter 0 Timer 0 • 8 -Bit • Overflow Interrupt • Output Compare Function with Interrupt • 8 -Bit PWM Function 8 Bit RISC MCU Slide 11 2 -Wire AT 94 Training 2001

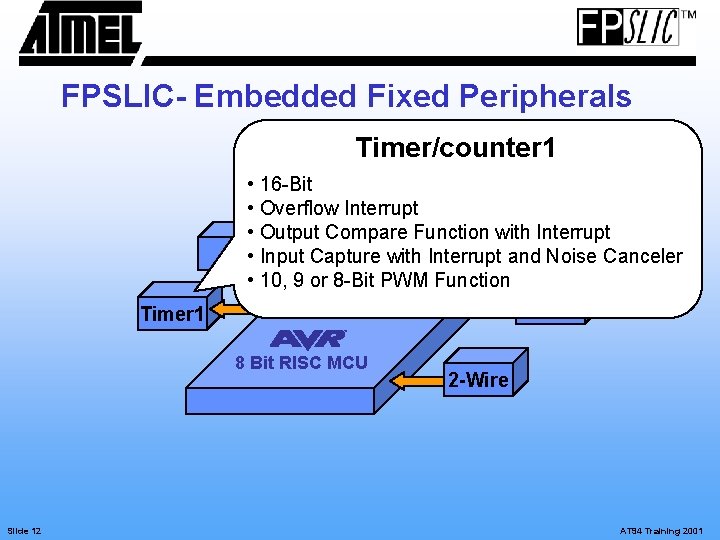

FPSLIC- Embedded Fixed Peripherals Timer/counter 1 • 16 -Bit • Overflow Interrupt • Output Compare Function with Interrupt • Input Capture with Interrupt and Noise Canceler • 10, 9 or 8 -Bit PWM Function Timer 1 8 Bit RISC MCU Slide 12 2 -Wire AT 94 Training 2001

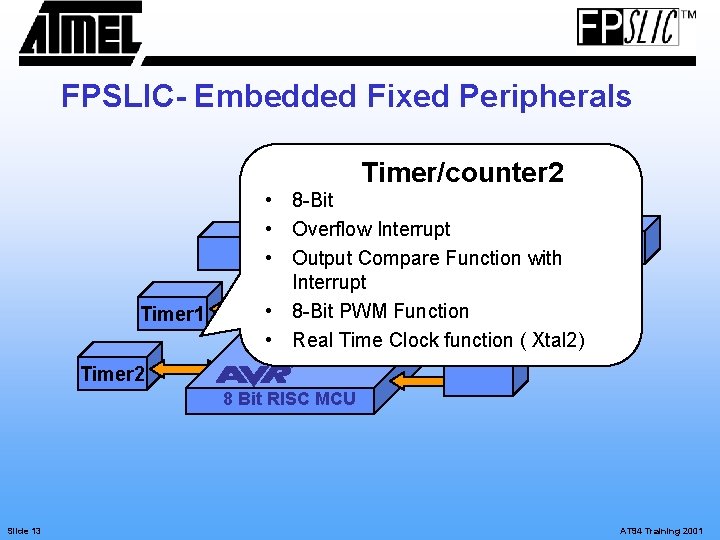

FPSLIC- Embedded Fixed Peripherals Timer/counter 2 Timer 1 • 8 -Bit • Overflow Interrupt • Output Compare Function with Interrupt • 8 -Bit PWM Function • Real Time Clock function ( Xtal 2) Timer 2 8 Bit RISC MCU Slide 13 AT 94 Training 2001

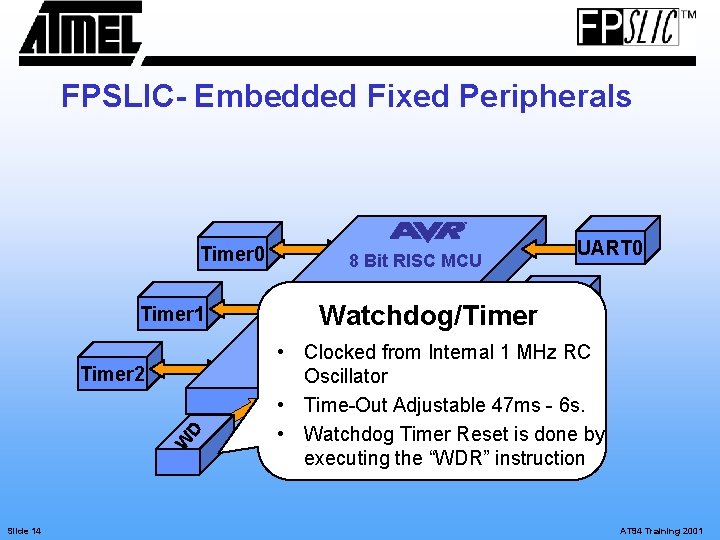

FPSLIC- Embedded Fixed Peripherals Timer 0 Timer 1 W D Timer 2 Slide 14 8 Bit RISC MCU UART 0 Watchdog/Timer • Clocked from Internal 1 MHz RC Oscillator • Time-Out Adjustable 47 ms - 6 s. • Watchdog Timer Reset is done by executing the “WDR” instruction AT 94 Training 2001

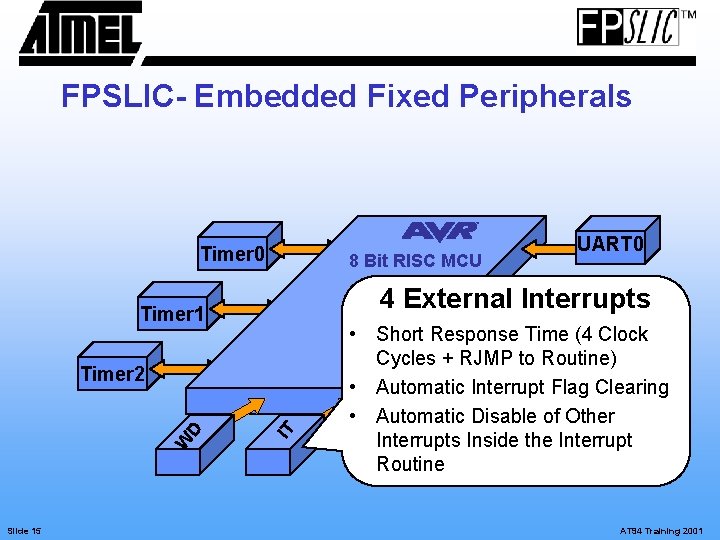

FPSLIC- Embedded Fixed Peripherals Timer 0 8 Bit RISC MCU 4 External Interrupts Timer 1 IT W D Timer 2 Slide 15 UART 0 • Short Response Time (4 Clock Cycles + RJMP to Routine) • Automatic Interrupt Flag Clearing • Automatic Disable of Other Interrupts Inside the Interrupt Routine AT 94 Training 2001

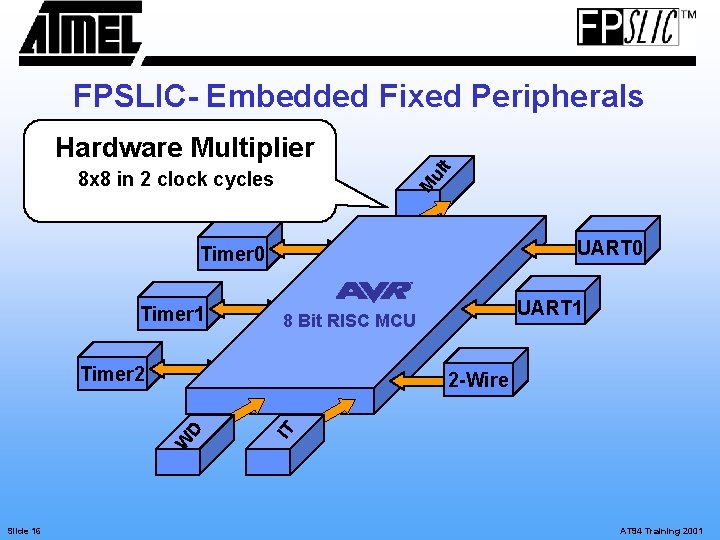

FPSLIC- Embedded Fixed Peripherals ul t Hardware Multiplier M 8 x 8 in 2 clock cycles UART 0 Timer 1 Timer 2 IT D 2 -Wire W Slide 16 UART 1 8 Bit RISC MCU AT 94 Training 2001

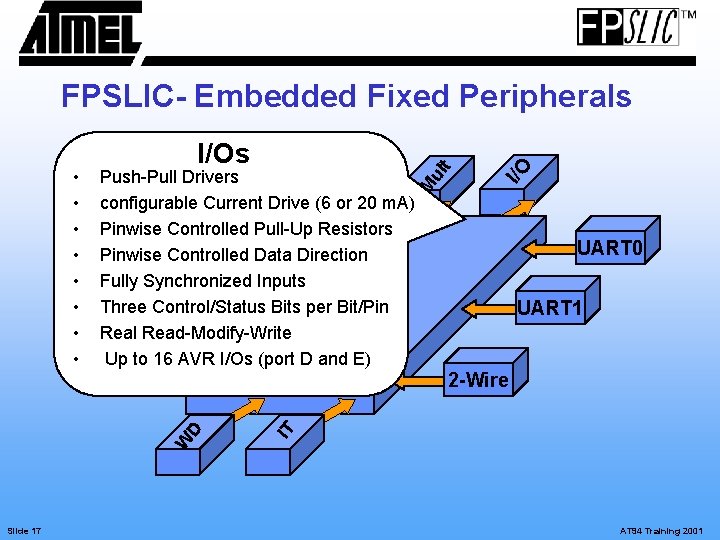

I/O Push-Pull Drivers configurable Current Drive (6 or 20 m. A) Pinwise Controlled Pull-Up Resistors Pinwise Controlled Data Direction Fully Synchronized Inputs Three Control/Status Bits per Bit/Pin Real Read-Modify-Write Up to 16 AVR I/Os (port D and E) M • • I/Os ul t FPSLIC- Embedded Fixed Peripherals UART 0 UART 1 Slide 17 IT W D 2 -Wire AT 94 Training 2001

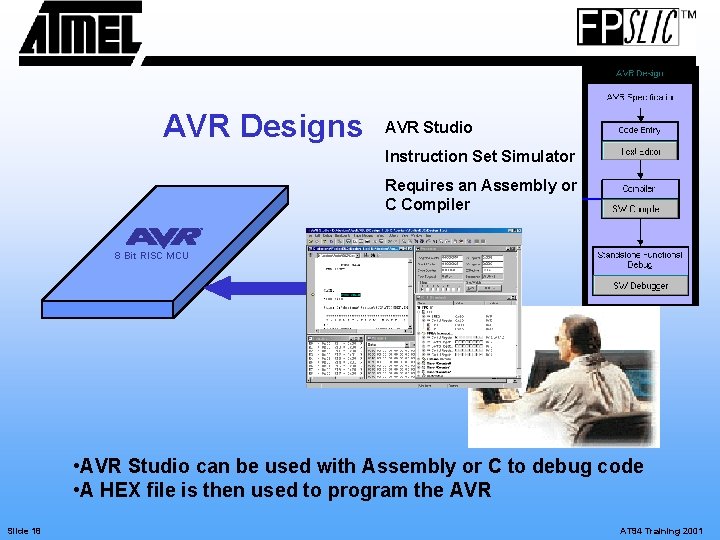

AVR Designs AVR Studio Instruction Set Simulator Requires an Assembly or C Compiler 8 Bit RISC MCU • AVR Studio can be used with Assembly or C to debug code • A HEX file is then used to program the AVR Slide 18 AT 94 Training 2001

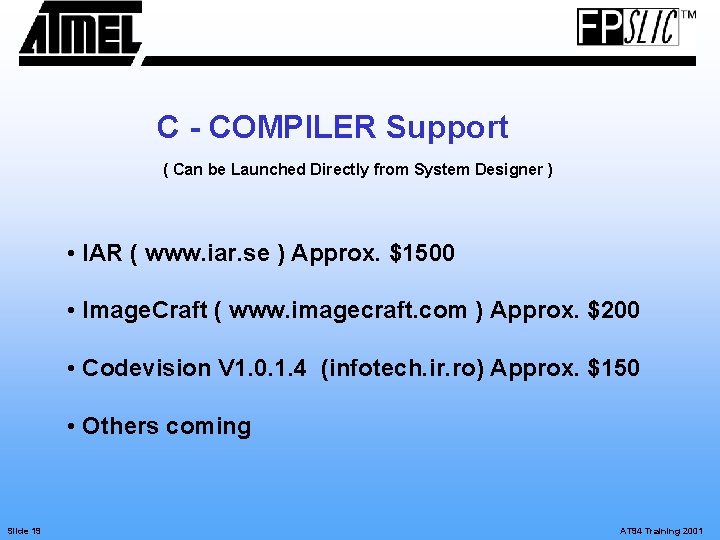

C - COMPILER Support ( Can be Launched Directly from System Designer ) • IAR ( www. iar. se ) Approx. $1500 • Image. Craft ( www. imagecraft. com ) Approx. $200 • Codevision V 1. 0. 1. 4 (infotech. ir. ro) Approx. $150 • Others coming Slide 19 AT 94 Training 2001

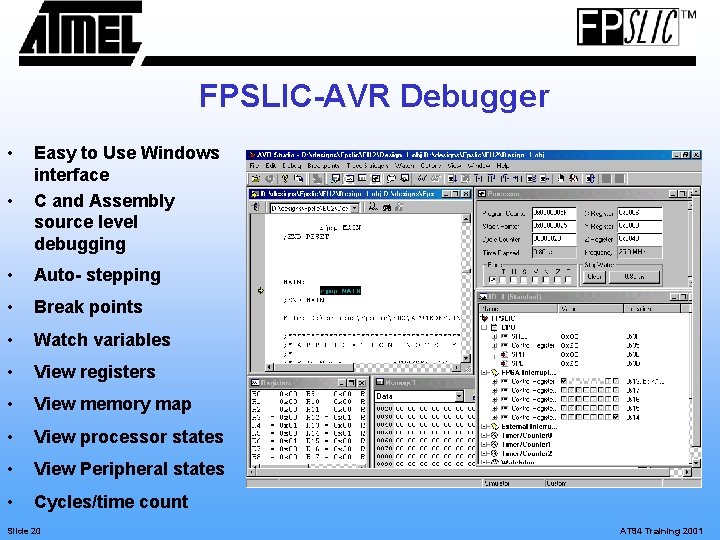

FPSLIC-AVR Debugger • • Easy to Use Windows interface C and Assembly source level debugging • Auto- stepping • Break points • Watch variables • View registers • View memory map • View processor states • View Peripheral states • Cycles/time count Slide 20 AT 94 Training 2001

- Slides: 20