Effective Implementation of a 32 bit RISC Processor

Effective Implementation of a 32 -bit RISC Processor Pirouz Bazargan Sabet University of Paris 6 - LIP 6 - ASIM Pirouz. Bazargan-Sabet@lip 6. fr Pirouz Bazargan Sabet December 2003

Outline Architecture of a RISC Processor Implementation Pirouz Bazargan Sabet December 2003

Introduction Architecture ? All aspects visible from the USER’s (programmer) point of view External view Specifications of the processor What the processor is supposed to do Pirouz Bazargan Sabet December 2003

Introduction Implementation ? All aspects visible from the DESIGNER’s point of view Internal view How much time does it take to perform some operation ? Which hardware may be used and how it should be organized to make the specifications feasable Pirouz Bazargan Sabet December 2003

Architecture Software visible registers Memory Addressing The instruction set The exception / reset mechanism Pirouz Bazargan Sabet December 2003

Architecture of the MIPS processor Mips ? A 32 -bit processor One of the two first RISC architectures Defined in 1981 by the Architecture Research Group at the Stanford University (John Hennessy) Pirouz Bazargan Sabet December 2003

Architecture Simplified Mips-R 3000 architecture No floating point operations No virtual memory management Pirouz Bazargan Sabet December 2003

Architecture Software visible registers Memory Addressing The instruction set The exception / reset mechanism Pirouz Bazargan Sabet December 2003

Architecture Software visible registers Registers that can be manipulated (written and read) in the assembly language Pirouz Bazargan Sabet December 2003

Software Visible Registers 32 common 32 -bit registers Integer Registers R 0 …. R 31 Addressed from their number Pirouz Bazargan Sabet December 2003

Software Visible Registers R 0 : The Trash Register R 0 contains always 0 A value written into R 0 is lost R 31 : The Link Register When a subroutine is called, the return address is saved into R 31 Pirouz Bazargan Sabet December 2003

Software Visible Registers Two 32 -bit registers : HI and LO Used by multiply and divide instructions Multiply Divide HI 32 most significant bits LO 32 least significant bits HI Result LO Remainder Pirouz Bazargan Sabet December 2003

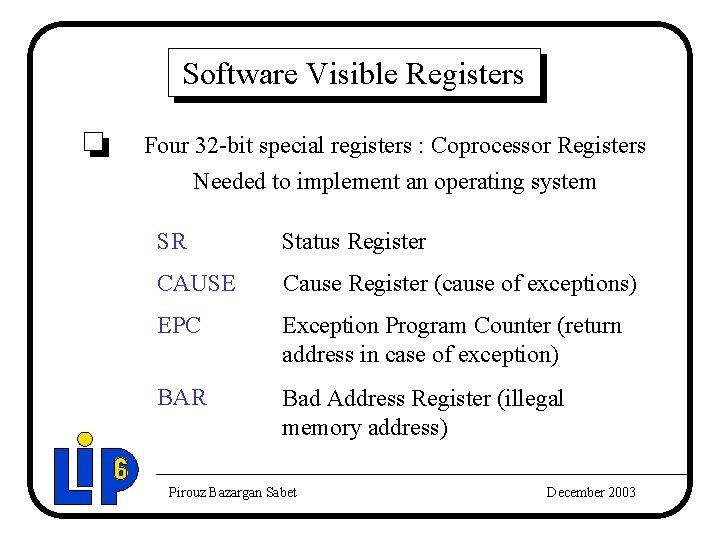

Software Visible Registers Four 32 -bit special registers : Coprocessor Registers Needed to implement an operating system SR Status Register CAUSE Cause Register (cause of exceptions) EPC Exception Program Counter (return address in case of exception) BAR Bad Address Register (illegal memory address) Pirouz Bazargan Sabet December 2003

Architecture Software visible registers Memory Addressing The instruction set The exception / reset mechanism Pirouz Bazargan Sabet December 2003

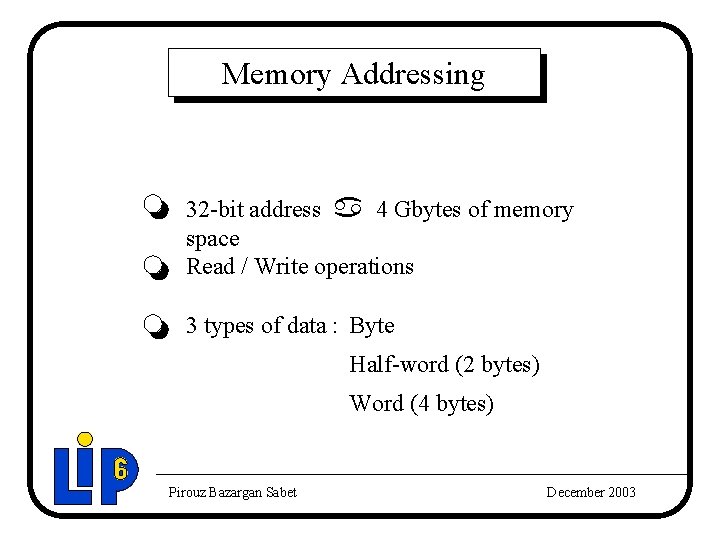

Memory Addressing 32 -bit address a 4 Gbytes of memory space Read / Write operations 3 types of data : Byte Half-word (2 bytes) Word (4 bytes) Pirouz Bazargan Sabet December 2003

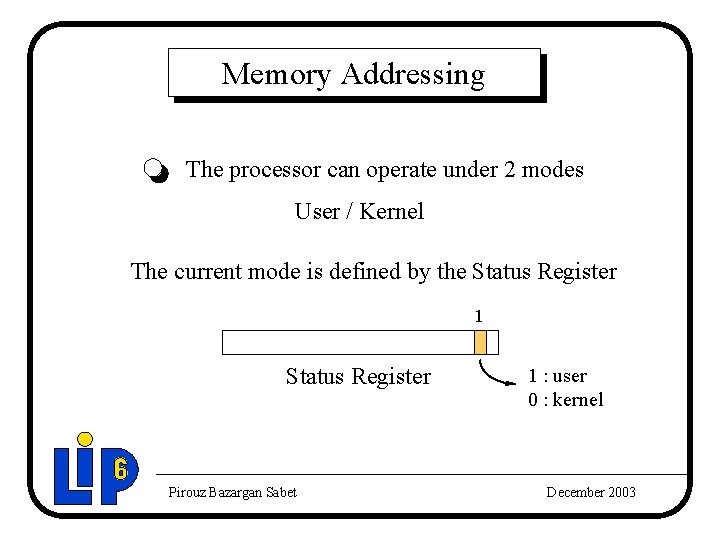

Memory Addressing The processor can operate under 2 modes User / Kernel The current mode is defined by the Status Register 1 Status Register Pirouz Bazargan Sabet 1 : user 0 : kernel December 2003

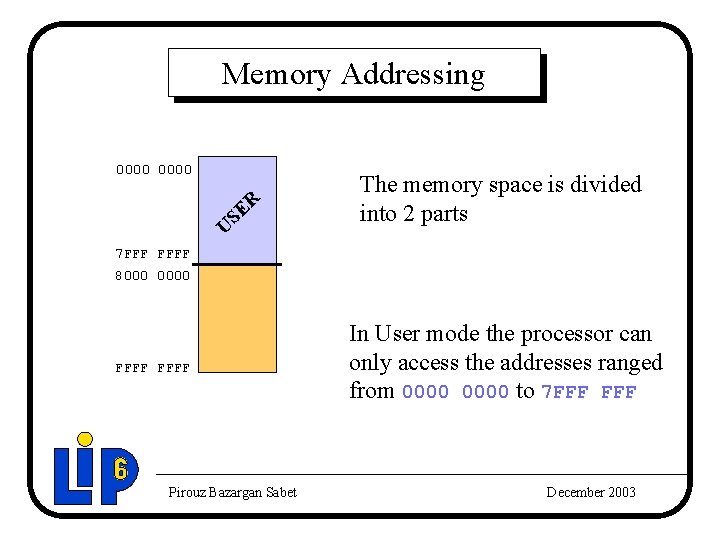

Memory Addressing 0000 R E S U The memory space is divided into 2 parts 7 FFF FFFF 8000 0000 FFFF Pirouz Bazargan Sabet In User mode the processor can only access the addresses ranged from 0000 to 7 FFF December 2003

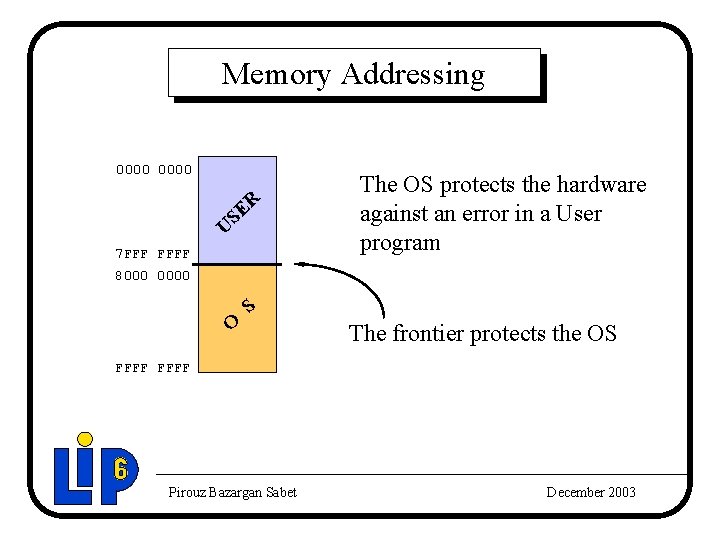

Memory Addressing 0000 R E S U 7 FFF FFFF The OS protects the hardware against an error in a User program 8000 0000 O S The frontier protects the OS FFFF Pirouz Bazargan Sabet December 2003

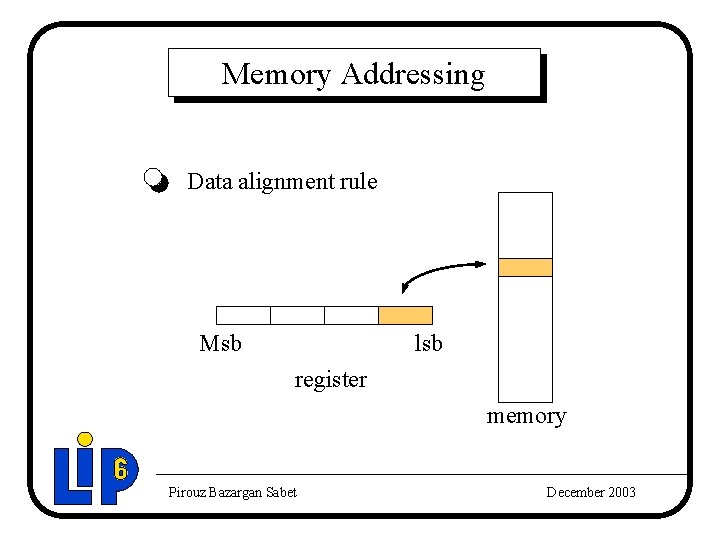

Memory Addressing Data alignment rule Msb lsb register memory Pirouz Bazargan Sabet December 2003

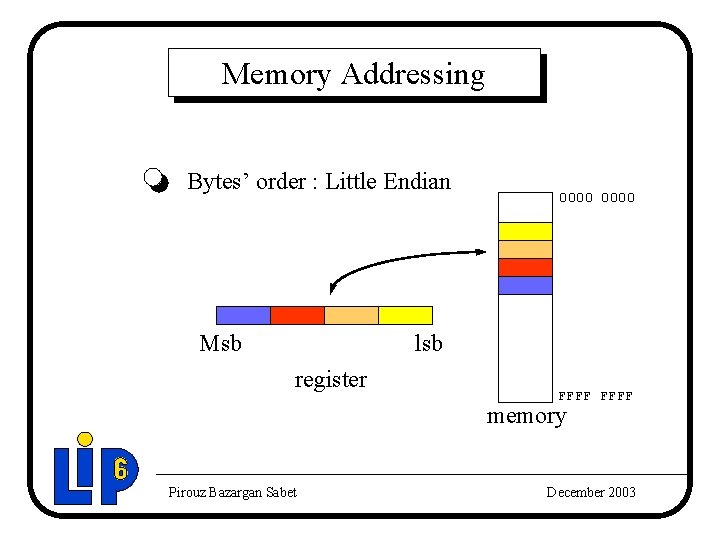

Memory Addressing Bytes’ order : Little Endian Msb 0000 lsb register FFFF memory Pirouz Bazargan Sabet December 2003

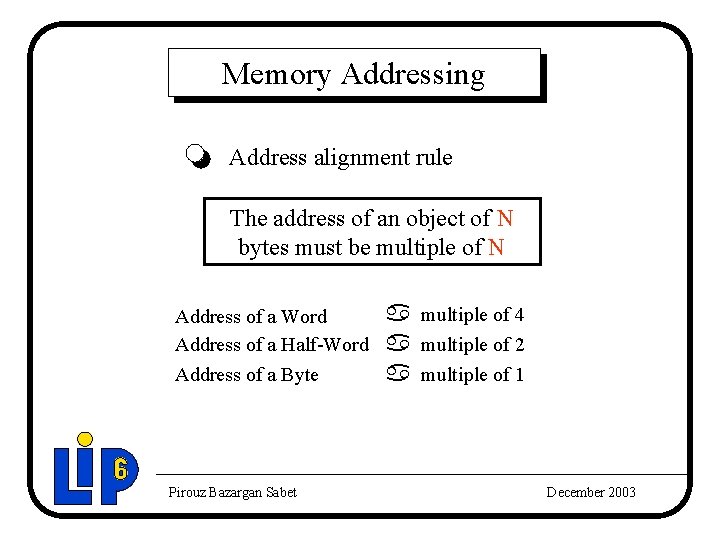

Memory Addressing Address alignment rule The address of an object of N bytes must be multiple of N Address of a Word Address of a Half-Word Address of a Byte Pirouz Bazargan Sabet a multiple of 4 a multiple of 2 a multiple of 1 December 2003

Architecture Software visible registers Memory Addressing The instruction set The exception / reset mechanism Pirouz Bazargan Sabet December 2003

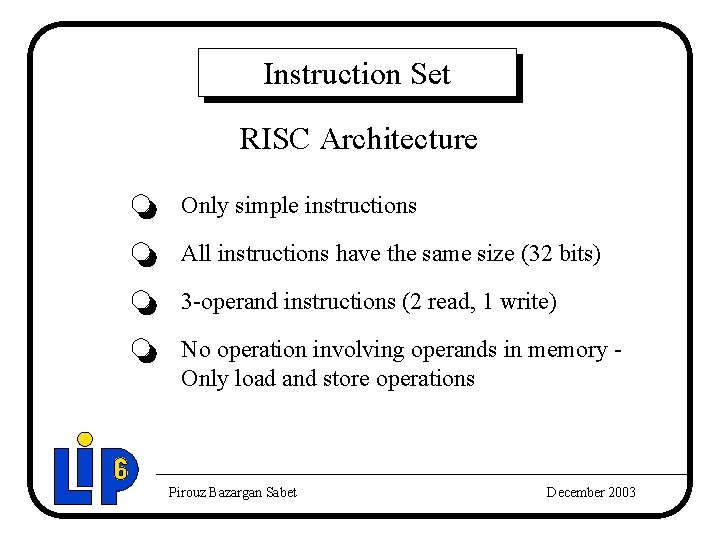

Instruction Set RISC Architecture Only simple instructions All instructions have the same size (32 bits) 3 -operand instructions (2 read, 1 write) No operation involving operands in memory Only load and store operations Pirouz Bazargan Sabet December 2003

Instruction Set 3 instruction formats R Register-register instructions I Immediate instructions J Jump instructions Pirouz Bazargan Sabet December 2003

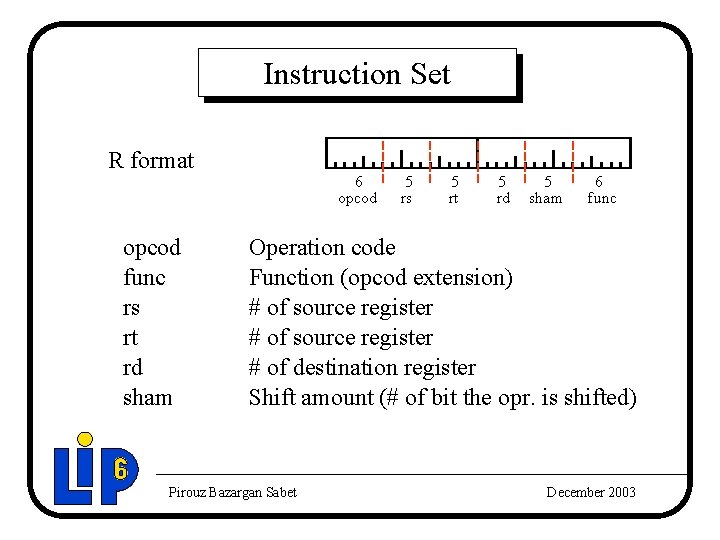

Instruction Set R format opcod func rs rt rd sham 6 opcod 5 rs 5 rt 5 rd 5 sham 6 func Operation code Function (opcod extension) # of source register # of destination register Shift amount (# of bit the opr. is shifted) Pirouz Bazargan Sabet December 2003

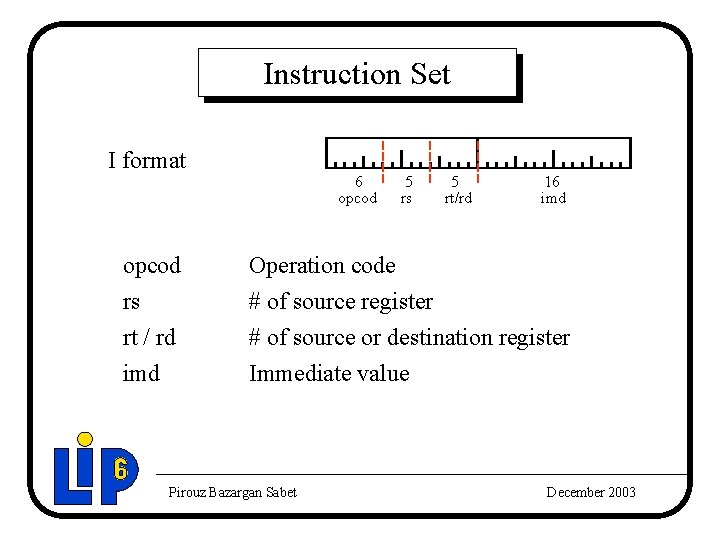

Instruction Set I format opcod rs rt / rd imd 6 opcod 5 rs 5 rt/rd 16 imd Operation code # of source register # of source or destination register Immediate value Pirouz Bazargan Sabet December 2003

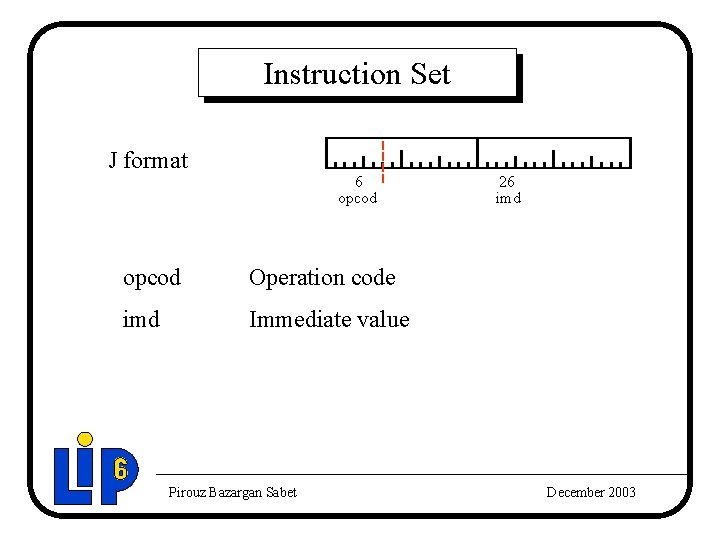

Instruction Set J format 6 opcod Operation code imd Immediate value Pirouz Bazargan Sabet 26 imd December 2003

Instruction Set Arithmetic and logic instructions Memory access instructions Control instructions System instructions Pirouz Bazargan Sabet December 2003

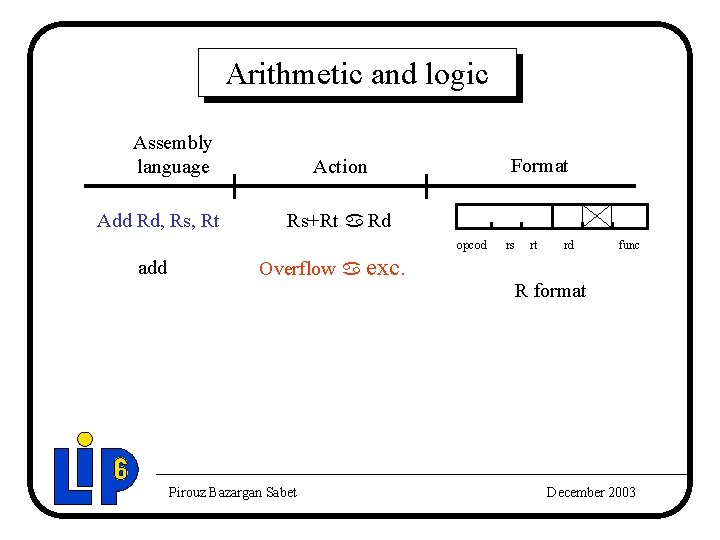

Arithmetic and logic Assembly language Add Rd, Rs, Rt Format Action Rs+Rt a Rd opcod add Overflow a Pirouz Bazargan Sabet exc. rs rt rd func R format December 2003

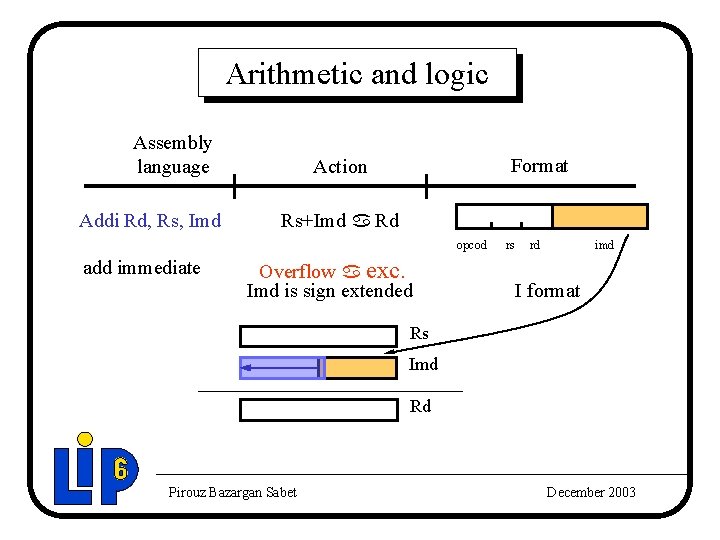

Arithmetic and logic Assembly language Addi Rd, Rs, Imd Format Action Rs+Imd a Rd opcod add immediate Overflow a exc. Imd is sign extended rs rd imd I format Rs Imd Rd Pirouz Bazargan Sabet December 2003

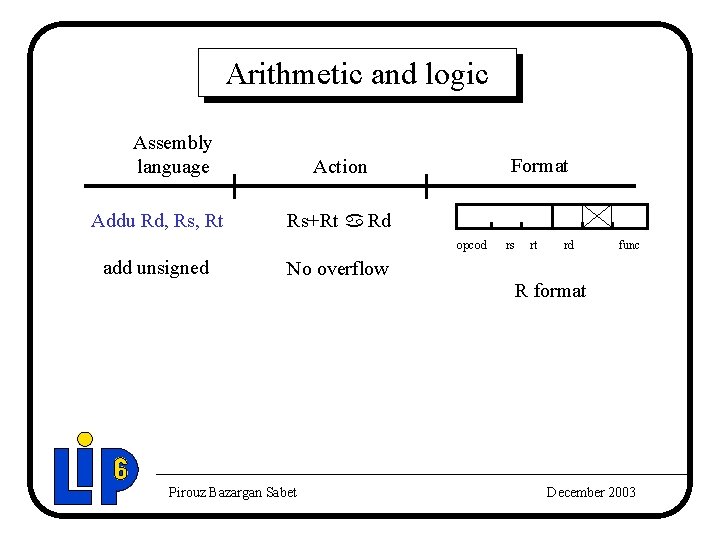

Arithmetic and logic Assembly language Addu Rd, Rs, Rt Format Action Rs+Rt a Rd opcod add unsigned No overflow Pirouz Bazargan Sabet rs rt rd func R format December 2003

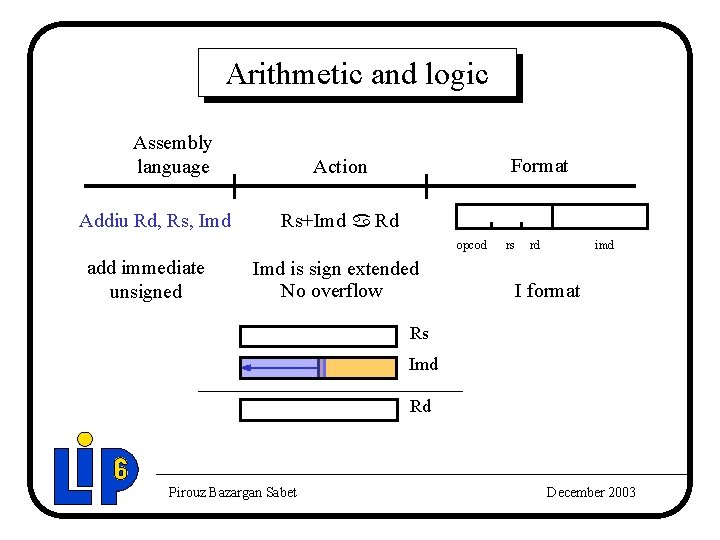

Arithmetic and logic Assembly language Addiu Rd, Rs, Imd Format Action Rs+Imd a Rd opcod add immediate unsigned Imd is sign extended No overflow rs rd imd I format Rs Imd Rd Pirouz Bazargan Sabet December 2003

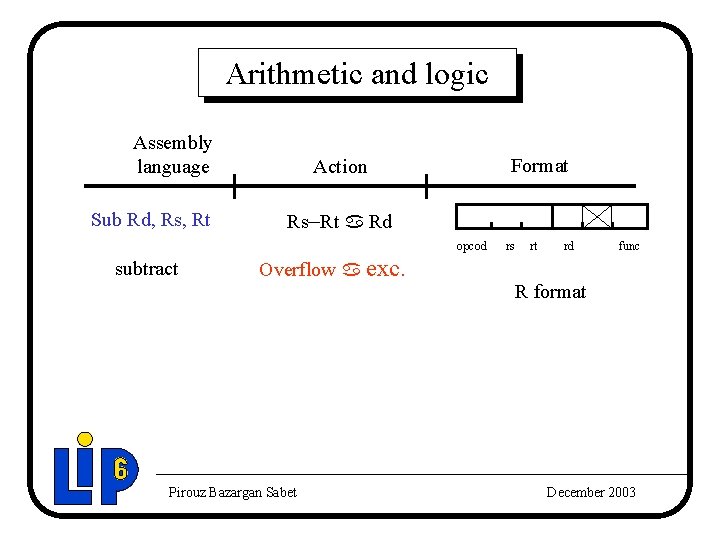

Arithmetic and logic Assembly language Sub Rd, Rs, Rt Format Action Rs–Rt a Rd opcod subtract Overflow a Pirouz Bazargan Sabet exc. rs rt rd func R format December 2003

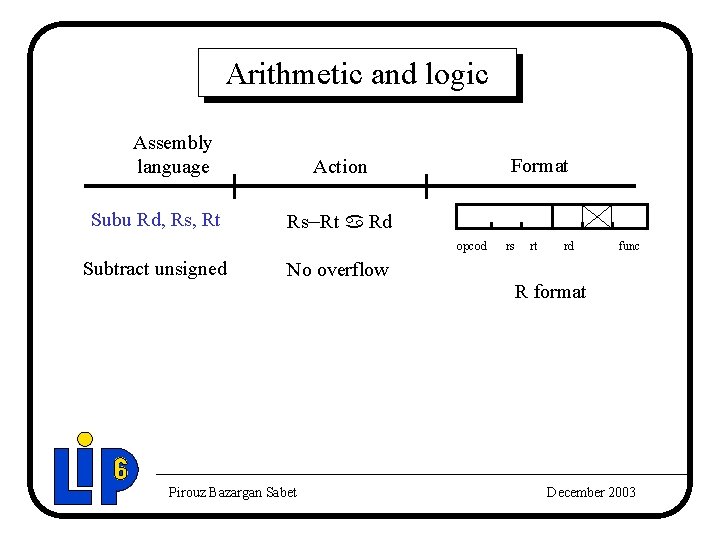

Arithmetic and logic Assembly language Subu Rd, Rs, Rt Format Action Rs–Rt a Rd opcod Subtract unsigned No overflow Pirouz Bazargan Sabet rs rt rd func R format December 2003

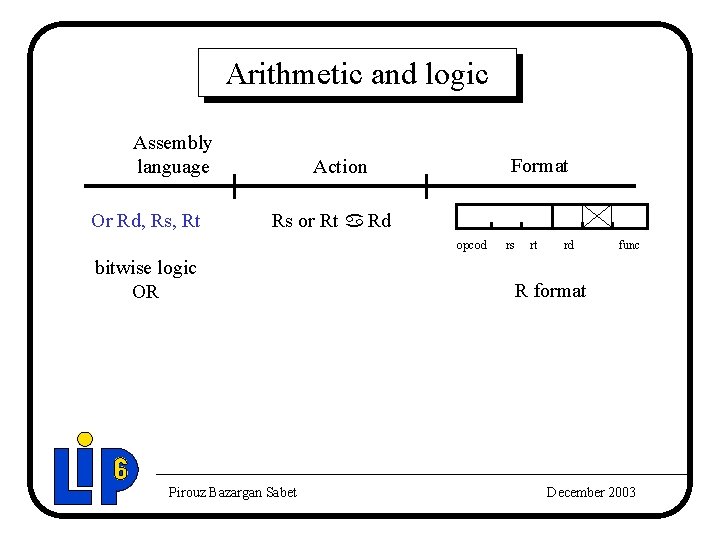

Arithmetic and logic Assembly language Or Rd, Rs, Rt Format Action Rs or Rt a Rd opcod bitwise logic OR Pirouz Bazargan Sabet rs rt rd func R format December 2003

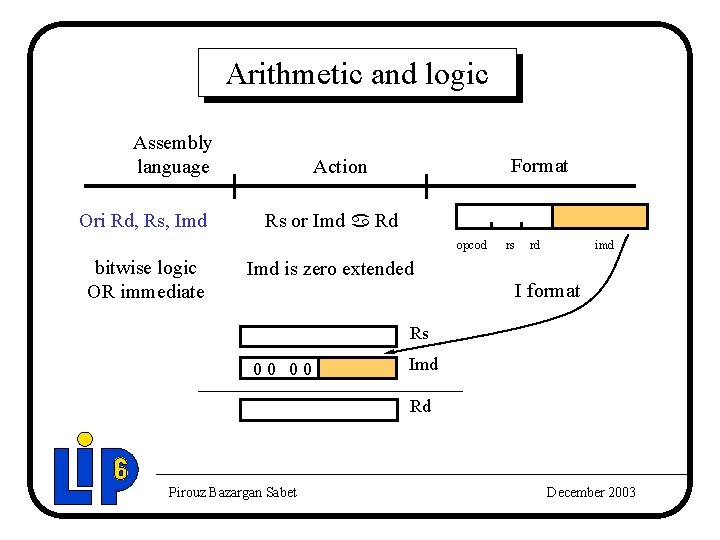

Arithmetic and logic Assembly language Ori Rd, Rs, Imd Format Action Rs or Imd a Rd opcod bitwise logic OR immediate Imd is zero extended rs rd imd I format Rs 00 00 Imd Rd Pirouz Bazargan Sabet December 2003

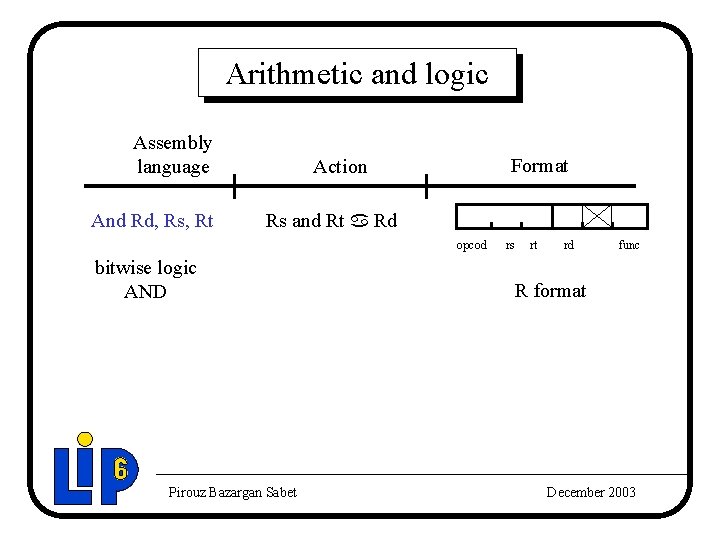

Arithmetic and logic Assembly language And Rd, Rs, Rt Format Action Rs and Rt a Rd opcod bitwise logic AND Pirouz Bazargan Sabet rs rt rd func R format December 2003

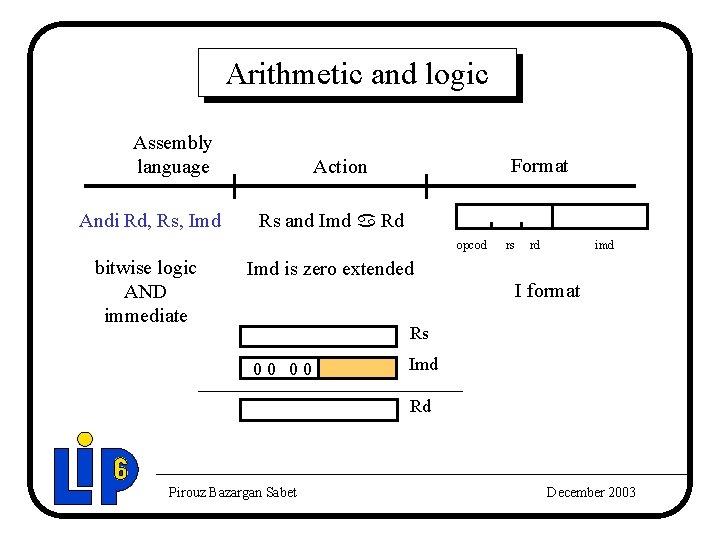

Arithmetic and logic Assembly language Andi Rd, Rs, Imd Format Action Rs and Imd a Rd opcod bitwise logic AND immediate Imd is zero extended rs rd imd I format Rs 00 00 Imd Rd Pirouz Bazargan Sabet December 2003

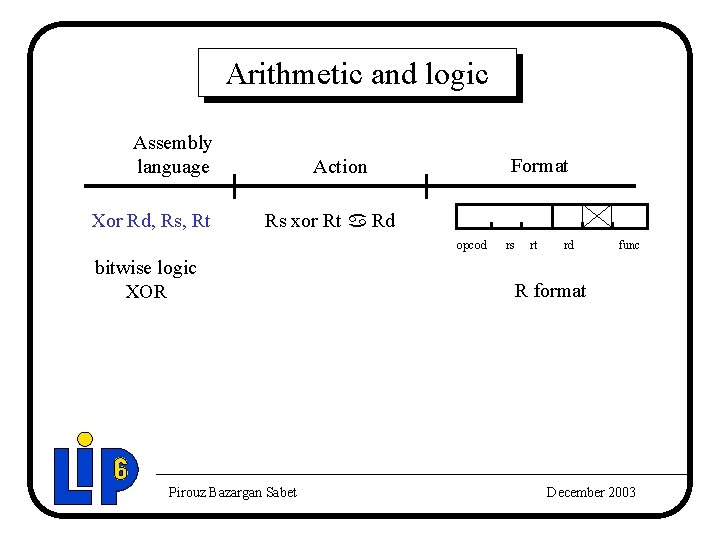

Arithmetic and logic Assembly language Xor Rd, Rs, Rt Format Action Rs xor Rt a Rd opcod bitwise logic XOR Pirouz Bazargan Sabet rs rt rd func R format December 2003

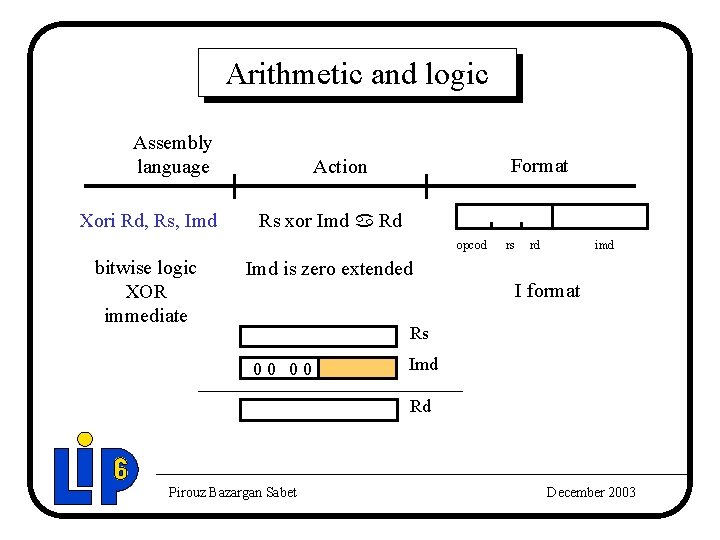

Arithmetic and logic Assembly language Xori Rd, Rs, Imd Format Action Rs xor Imd a Rd opcod bitwise logic XOR immediate Imd is zero extended rs rd imd I format Rs 00 00 Imd Rd Pirouz Bazargan Sabet December 2003

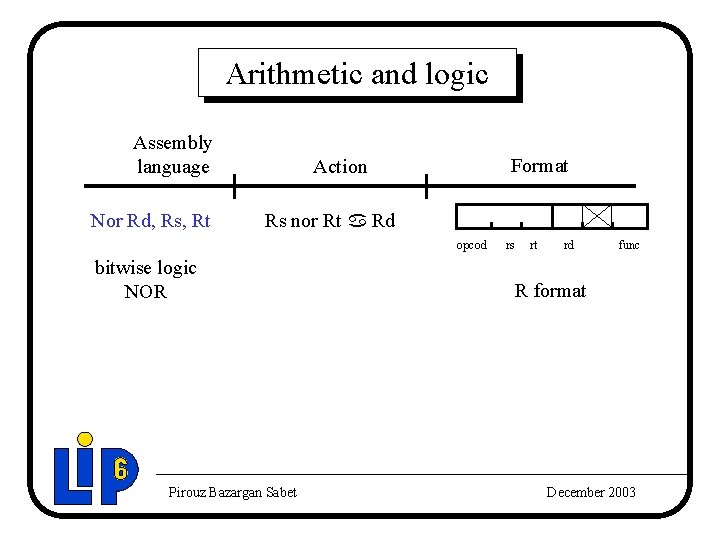

Arithmetic and logic Assembly language Nor Rd, Rs, Rt Format Action Rs nor Rt a Rd opcod bitwise logic NOR Pirouz Bazargan Sabet rs rt rd func R format December 2003

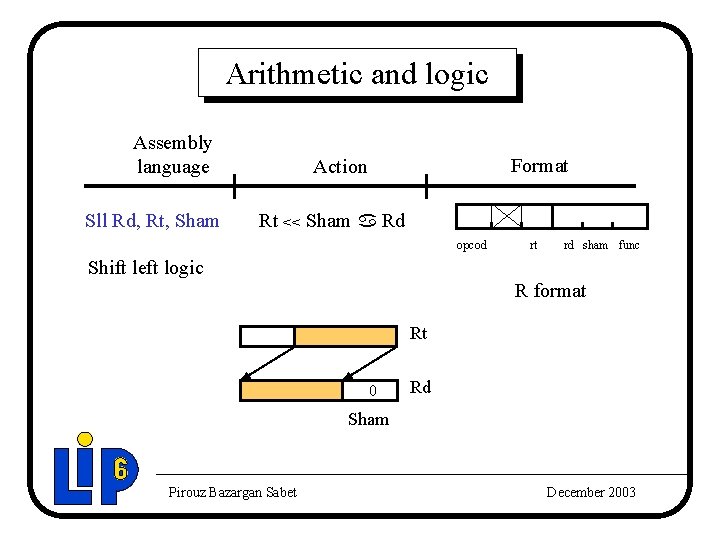

Arithmetic and logic Assembly language Sll Rd, Rt, Sham Format Action Rt << Sham a Rd opcod rt rd sham func Shift left logic R format Rt 0 Rd Sham Pirouz Bazargan Sabet December 2003

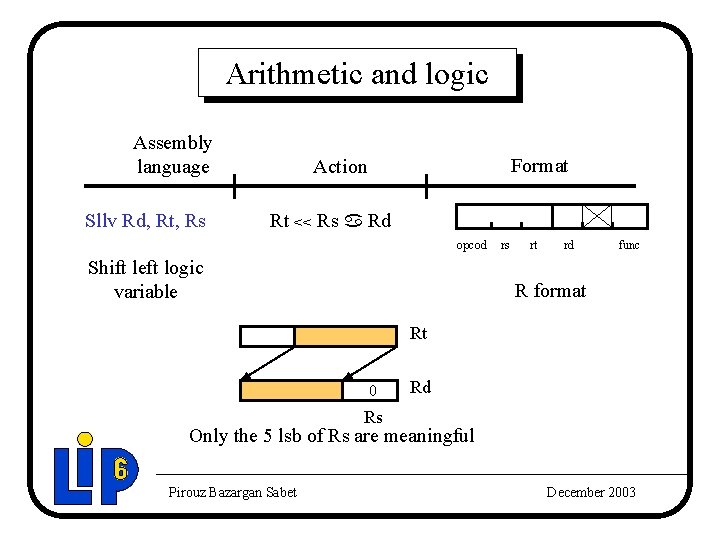

Arithmetic and logic Assembly language Sllv Rd, Rt, Rs Format Action Rt << Rs a Rd opcod Shift left logic variable rs rt rd func R format Rt 0 Rd Rs Only the 5 lsb of Rs are meaningful Pirouz Bazargan Sabet December 2003

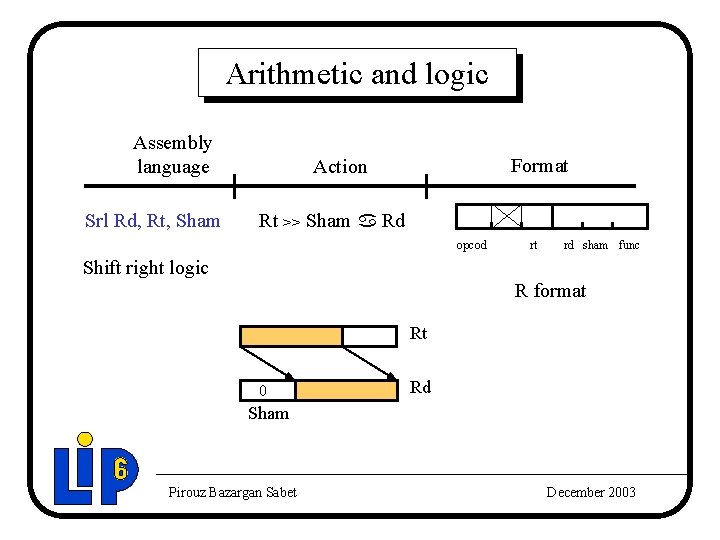

Arithmetic and logic Assembly language Srl Rd, Rt, Sham Format Action Rt >> Sham a Rd opcod rt rd sham func Shift right logic R format Rt 0 Rd Sham Pirouz Bazargan Sabet December 2003

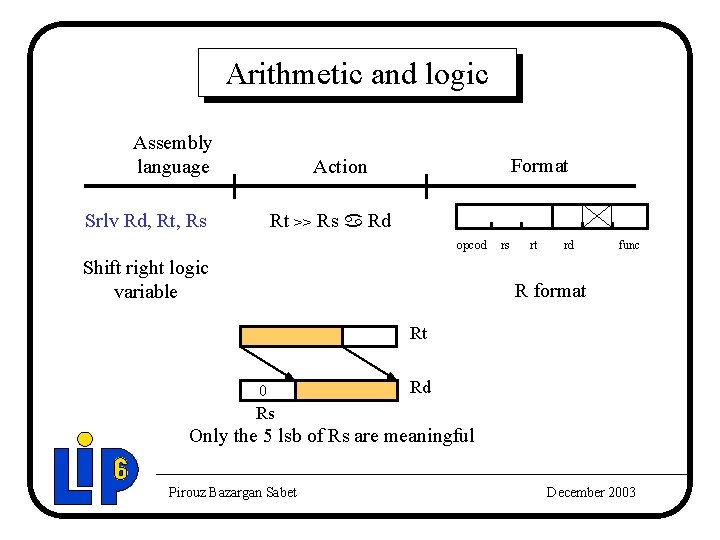

Arithmetic and logic Assembly language Format Action Srlv Rd, Rt, Rs Rt >> Rs a Rd opcod Shift right logic variable rs rt rd func R format Rt 0 Rd Rs Only the 5 lsb of Rs are meaningful Pirouz Bazargan Sabet December 2003

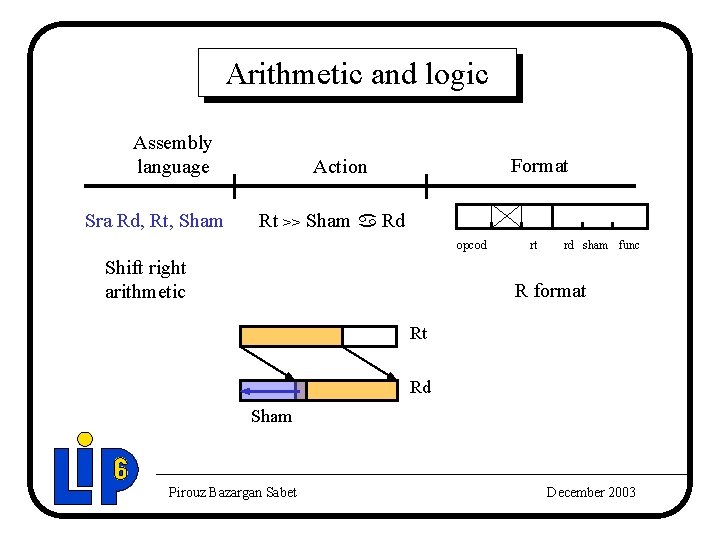

Arithmetic and logic Assembly language Sra Rd, Rt, Sham Format Action Rt >> Sham a Rd opcod Shift right arithmetic rt rd sham func R format Rt Rd Sham Pirouz Bazargan Sabet December 2003

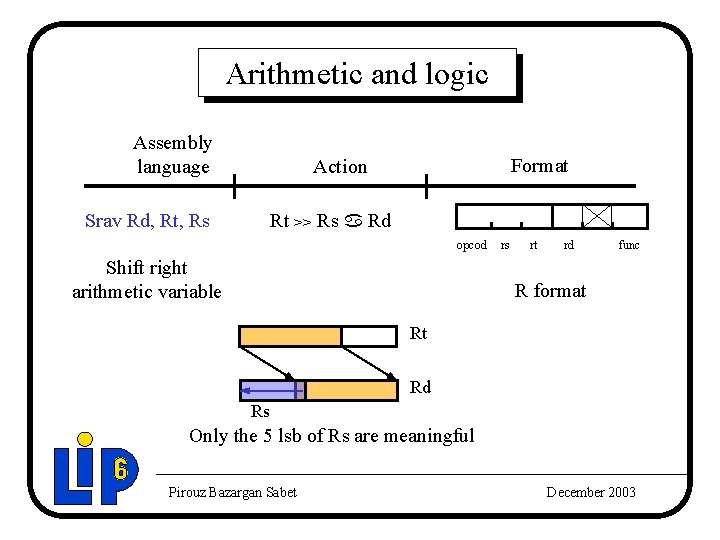

Arithmetic and logic Assembly language Format Action Srav Rd, Rt, Rs Rt >> Rs a Rd opcod Shift right arithmetic variable rs rt rd func R format Rt Rd Rs Only the 5 lsb of Rs are meaningful Pirouz Bazargan Sabet December 2003

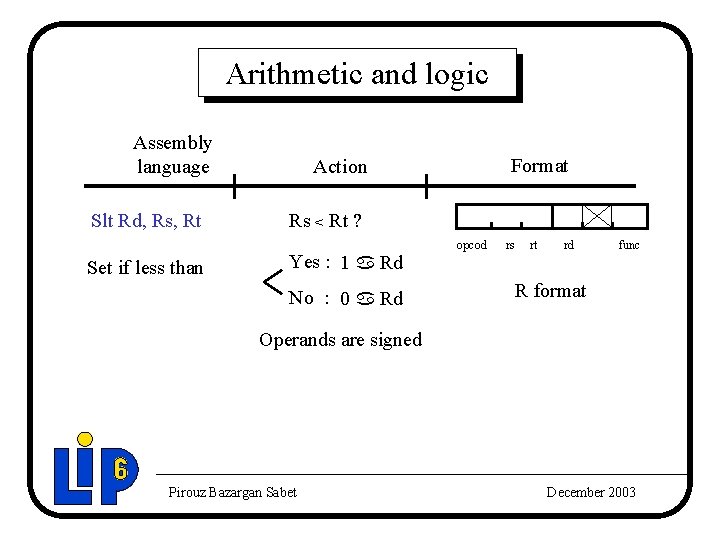

Arithmetic and logic Assembly language Slt Rd, Rs, Rt Set if less than Format Action Rs < Rt ? Yes : 1 a Rd No : 0 a Rd opcod rs rt rd func R format Operands are signed Pirouz Bazargan Sabet December 2003

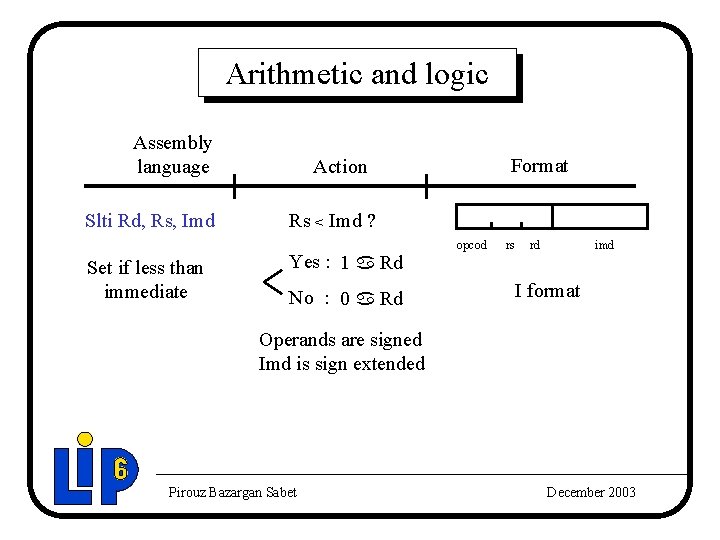

Arithmetic and logic Assembly language Slti Rd, Rs, Imd Set if less than immediate Format Action Rs < Imd ? Yes : 1 a Rd No : 0 a Rd opcod rs rd imd I format Operands are signed Imd is sign extended Pirouz Bazargan Sabet December 2003

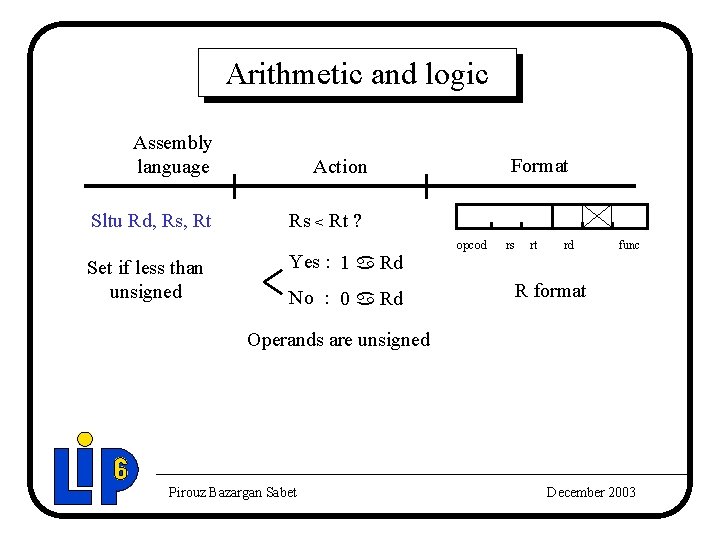

Arithmetic and logic Assembly language Action Sltu Rd, Rs, Rt Rs < Rt ? Set if less than unsigned Yes : 1 a Rd No : 0 a Rd Format opcod rs rt rd func R format Operands are unsigned Pirouz Bazargan Sabet December 2003

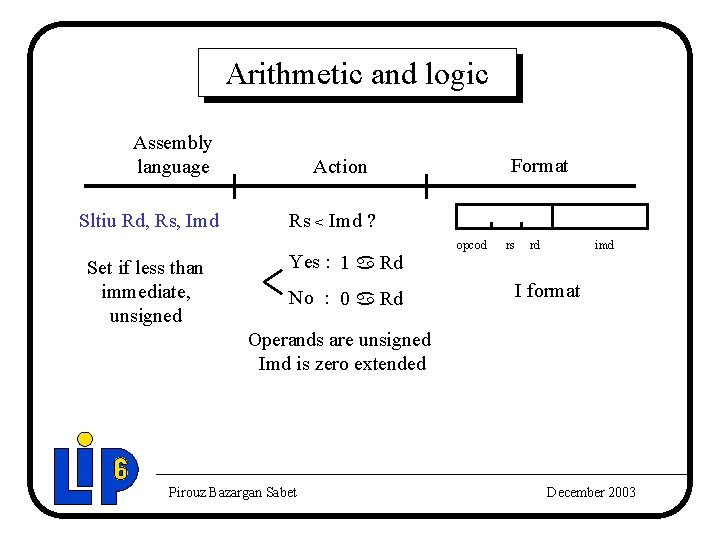

Arithmetic and logic Assembly language Sltiu Rd, Rs, Imd Set if less than immediate, unsigned Format Action Rs < Imd ? Yes : 1 a Rd No : 0 a Rd opcod rs rd imd I format Operands are unsigned Imd is zero extended Pirouz Bazargan Sabet December 2003

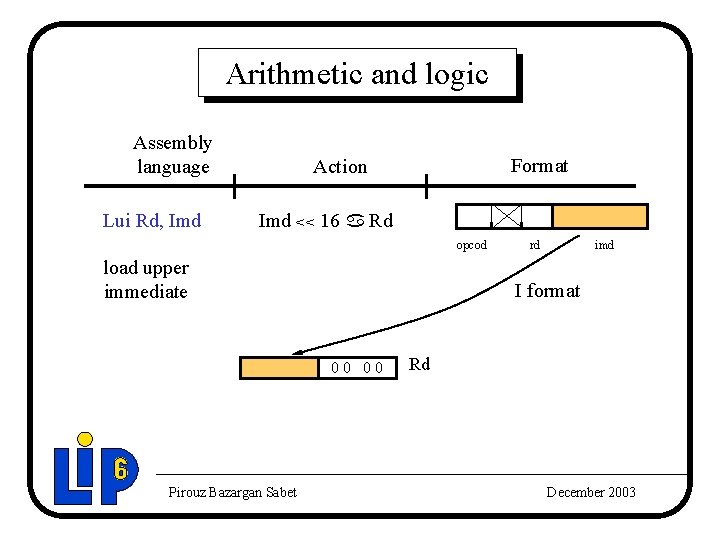

Arithmetic and logic Assembly language Lui Rd, Imd Format Action Imd << 16 a Rd opcod load upper immediate imd I format 00 00 Pirouz Bazargan Sabet rd Rd December 2003

- Slides: 52