ECE 383 Embedded Computer Systems II Lecture 19

ECE 383 – Embedded Computer Systems II Lecture 19 – Soft Core (Micro. Blaze) + Custom IP with Interrupt Maj Jeffrey Falkinburg Room 2 E 46 E 333 -9193 1

Lesson Outline n n Time Logs! Micro. Blaze + Custom IP with Interrupt Integrity - Service - Excellence 2

Micro. Blaze + Custom IP with Interrupt Integrity - Service - Excellence 3

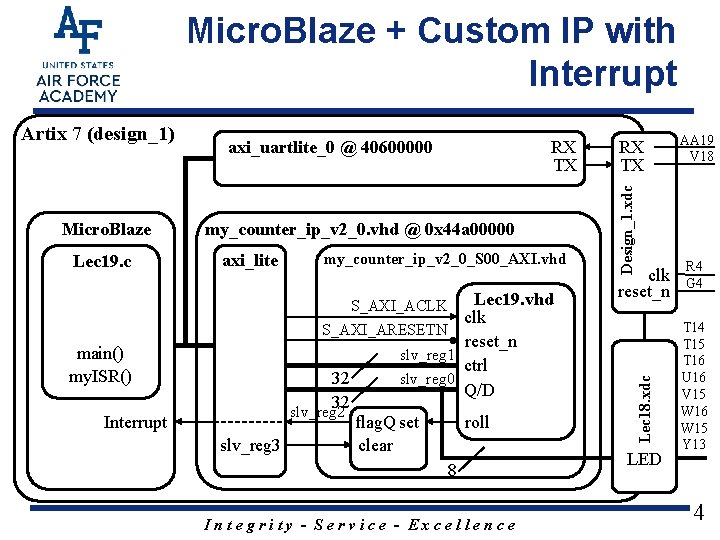

Micro. Blaze + Custom IP with Interrupt Lec 19. c RX TX my_counter_ip_v 2_0. vhd @ 0 x 44 a 00000 axi_lite my_counter_ip_v 2_0_S 00_AXI. vhd Lec 19. vhd S_AXI_ACLK clk S_AXI_ARESETN main() my. ISR() reset_n ctrl slv_reg 0 Q/D RX TX clk reset_n slv_reg 1 32 32 slv_reg 2 Interrupt slv_reg 3 flag. Q set clear roll 8 Integrity - Service - Excellence Lec 18. xdc Micro. Blaze axi_uartlite_0 @ 40600000 Design_1. xdc Artix 7 (design_1) LED AA 19 V 18 R 4 G 4 T 15 T 16 U 16 V 15 W 16 W 15 Y 13 4

Micro. Blaze + Custom IP – Workflow n The work flow has three main steps. Define a new hardware design (Micro. Blaze + axi_uartlite) in Vivado IP Integrator (using the Micro. Blaze Tutorial from Lecture 17) 2. Create and package new custom IP (your custom hardware) and import it into your Vivado design 3. Program the resulting hardware in the SDK environment. 1. n Lets start with the first step. Integrity - Service - Excellence 5

Xilinx Vivado – IP Integrator This step requires that you start a new hardware design (Micro. Blaze + axi_uartlite) in Vivado IP Integrator in a new project called Lecture_19. n You will add a new Block Design with a Micro. Blaze and axi_uartlite following the Micro. Blaze Tutorial. n n http: //ece. ninja/383/hand/Nexys_Video_Micro. Blaze_Tutorial. pdf n ***Deviation from Lecture 17 Tutorial*** Do not include the Micro. Blaze Interrupt Controller check box. n If you do you could probably delete it from your design n Integrity - Service - Excellence 6

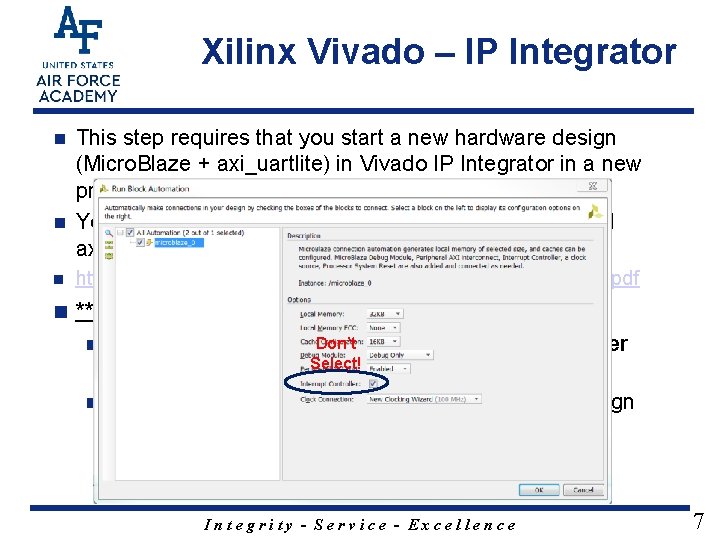

Xilinx Vivado – IP Integrator This step requires that you start a new hardware design (Micro. Blaze + axi_uartlite) in Vivado IP Integrator in a new project called Lecture_19. n You will add a new Block Design with a Micro. Blaze and axi_uartlite following the Micro. Blaze Tutorial. n n http: //ece. ninja/383/hand/Nexys_Video_Micro. Blaze_Tutorial. pdf n ***Deviation from Lecture 17 Tutorial*** Don’t Do not include the Micro. Blaze Interrupt Controller Select! check box. n If you do you could probably delete it from your design n Integrity - Service - Excellence 7

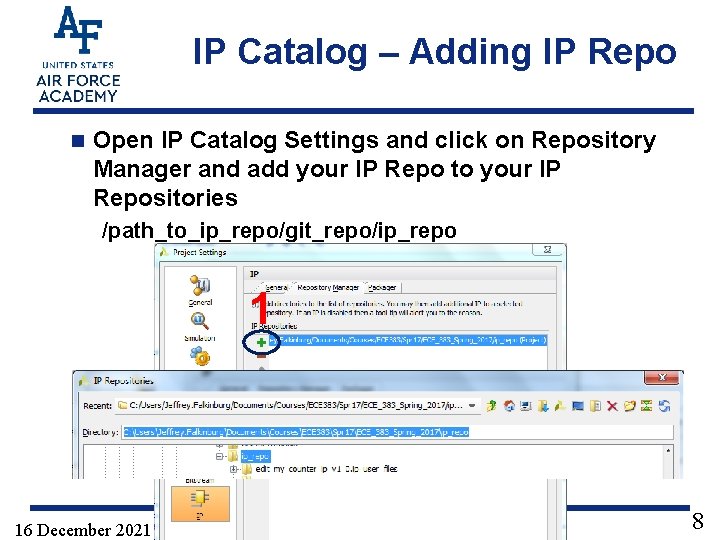

IP Catalog – Adding IP Repo n Open IP Catalog Settings and click on Repository Manager and add your IP Repo to your IP Repositories /path_to_ip_repo/git_repo/ip_repo 1 16 December 2021 Integrity - Service - Excellence 8

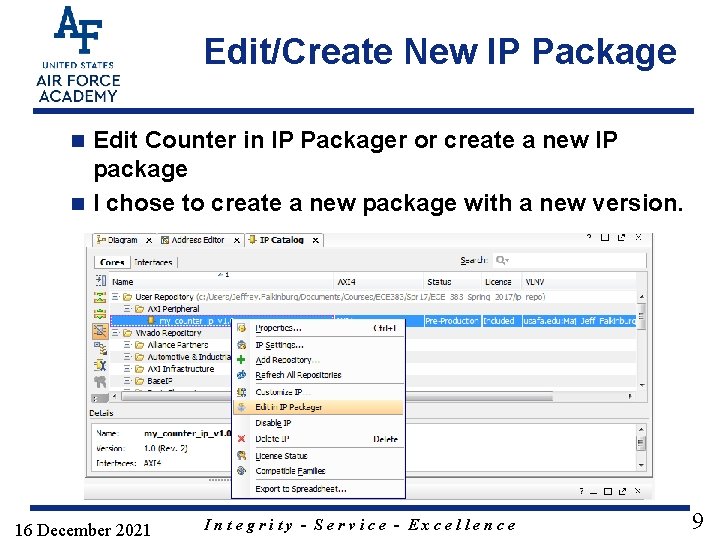

Edit/Create New IP Package Edit Counter in IP Packager or create a new IP package n I chose to create a new package with a new version. n 16 December 2021 Integrity - Service - Excellence 9

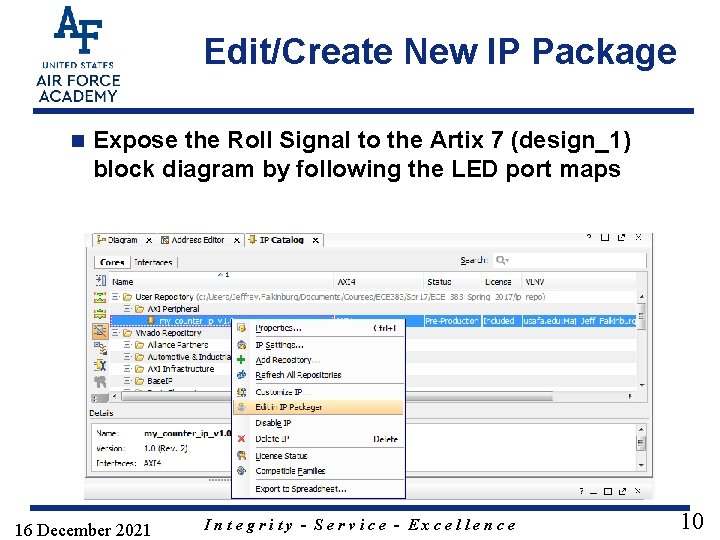

Edit/Create New IP Package n Expose the Roll Signal to the Artix 7 (design_1) block diagram by following the LED port maps 16 December 2021 Integrity - Service - Excellence 10

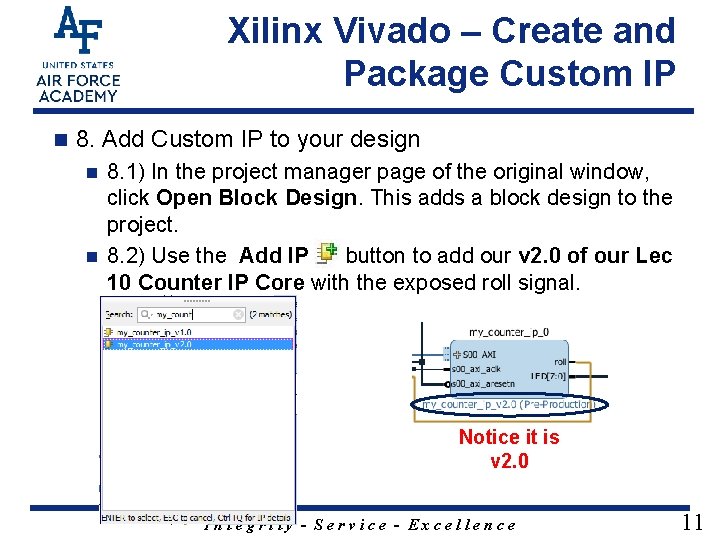

Xilinx Vivado – Create and Package Custom IP n 8. Add Custom IP to your design 8. 1) In the project manager page of the original window, click Open Block Design. This adds a block design to the project. n 8. 2) Use the Add IP button to add our v 2. 0 of our Lec 10 Counter IP Core with the exposed roll signal. n Notice it is v 2. 0 Integrity - Service - Excellence 11

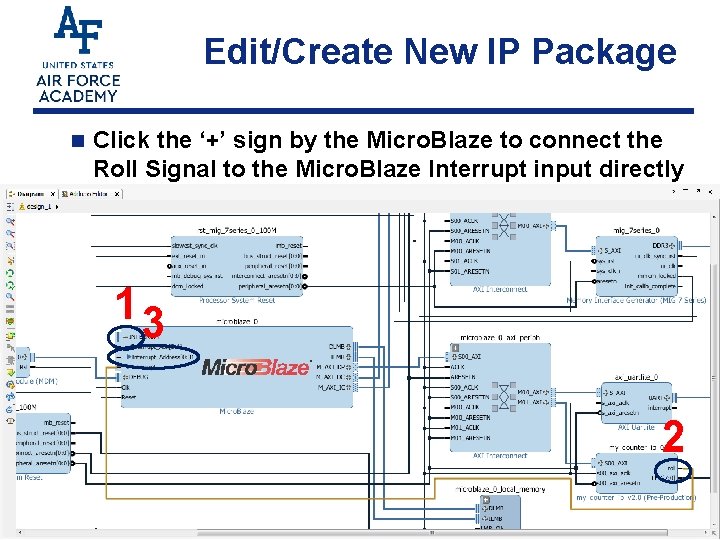

Edit/Create New IP Package n Click the ‘+’ sign by the Micro. Blaze to connect the Roll Signal to the Micro. Blaze Interrupt input directly 13 2 16 December 2021 Integrity - Service - Excellence 12

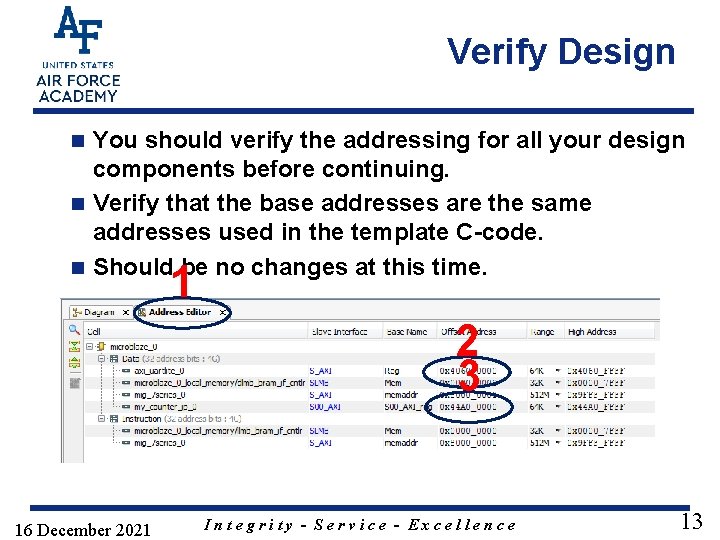

Verify Design You should verify the addressing for all your design components before continuing. n Verify that the base addresses are the same addresses used in the template C-code. n Should be no changes at this time. n 1 2 3 16 December 2021 Integrity - Service - Excellence 13

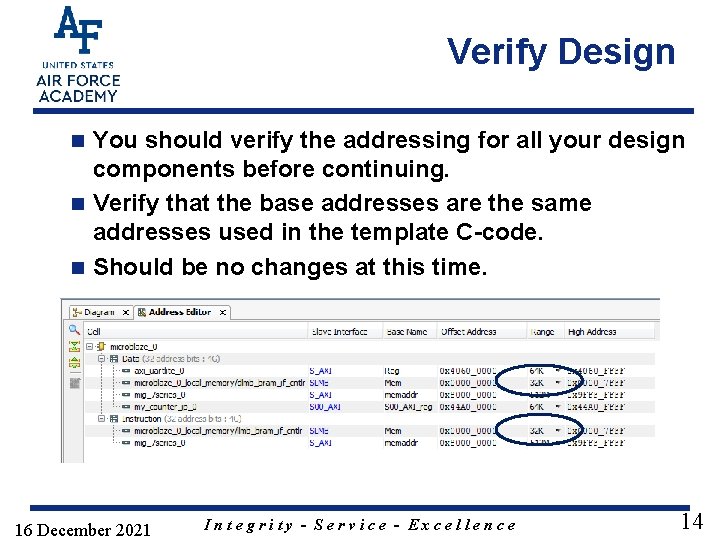

Verify Design You should verify the addressing for all your design components before continuing. n Verify that the base addresses are the same addresses used in the template C-code. n Should be no changes at this time. n 16 December 2021 Integrity - Service - Excellence 14

Validate and Export Design First click validate design_1 2. Regenerate the design_1 HDL wrapper. 3. Finally you need to generate the Generate Design bitstream 4. Take a coffee break while it builds 1. Integrity - Service - Excellence 15

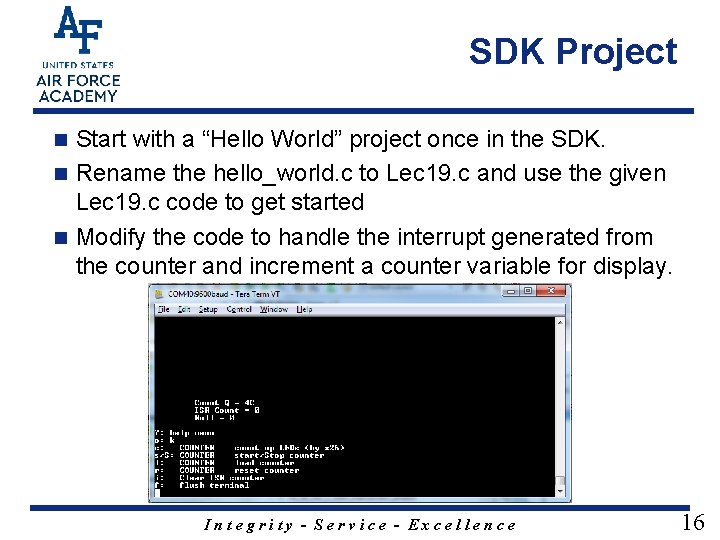

SDK Project Start with a “Hello World” project once in the SDK. n Rename the hello_world. c to Lec 19. c and use the given Lec 19. c code to get started n Modify the code to handle the interrupt generated from the counter and increment a counter variable for display. n Integrity - Service - Excellence 16

16 December 2021 Integrity - Service - Excellence 17

- Slides: 17