Dose Map and Placement CoOptimization for Timing Yield

- Slides: 16

Dose Map and Placement Co-Optimization for Timing Yield Enhancement and Leakage Power Reduction Kwangok Jeong, Andrew B. Kahng, Chul-Hong Park, Hailong Yao University of California, San Diego

Background l Critical dimension (CD) variation ¤ Dominant factor in the variation of delay and leakage current of transistor gates l Equipment improvement ¤ Opportunity to leverage design information for cost and turnaround time improvements l ASML’s Dose. Mapper technology ¤ Extensively used to improve global CD uniformity ¤ We explore a method that Dose. Mapper can be used to improve design parametric yield

Motivation l Motivation ¤ Use Dose. Mapper to improve device performance and parametric yield l Idea ¤ Increase dose decrease gate CD of timing critical device more speed ¤ Decrease dose increase gate CD of non-timing critical device less leakage power l Methods ¤ Dose map optimization method: given placement, optimize the dose map ¤ Placement optimization method: given dose map, optimize the placement

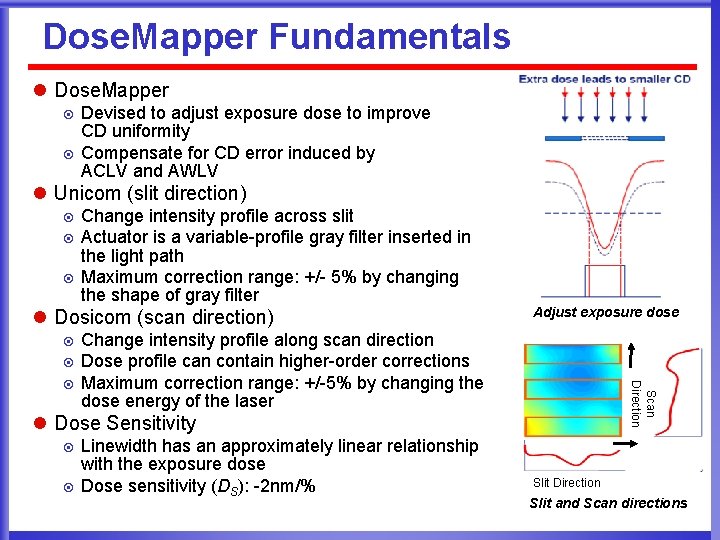

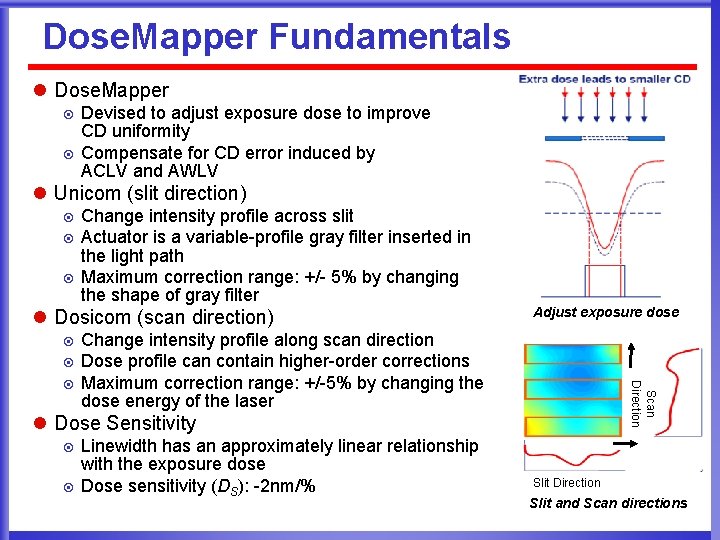

Dose. Mapper Fundamentals l Dose. Mapper ¤ ¤ Devised to adjust exposure dose to improve CD uniformity Compensate for CD error induced by ACLV and AWLV l Unicom (slit direction) ¤ ¤ ¤ Change intensity profile across slit Actuator is a variable-profile gray filter inserted in the light path Maximum correction range: +/- 5% by changing the shape of gray filter l Dosicom (scan direction) ¤ ¤ Change intensity profile along scan direction Dose profile can contain higher-order corrections Maximum correction range: +/-5% by changing the dose energy of the laser Scan Direction ¤ Adjust exposure dose l Dose Sensitivity ¤ ¤ Linewidth has an approximately linear relationship with the exposure dose Dose sensitivity (DS): -2 nm/% Slit Direction Slit and Scan directions

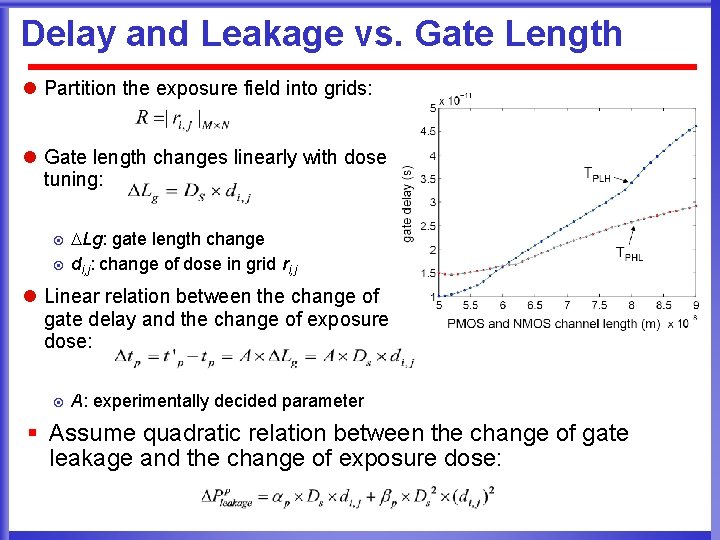

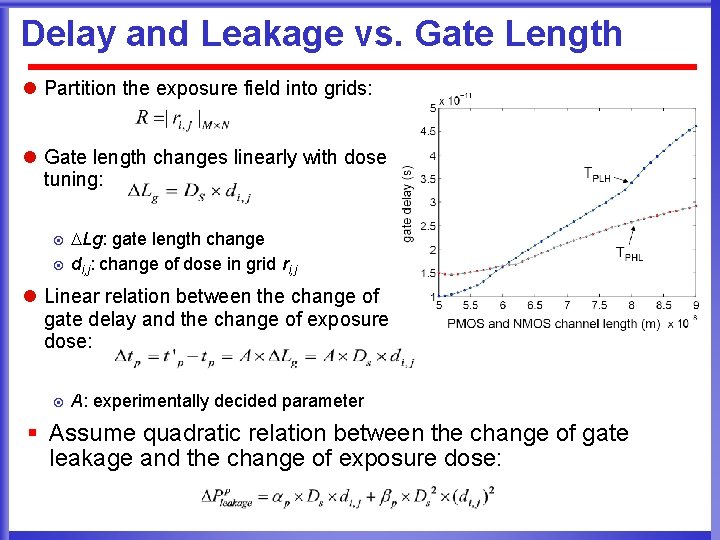

Delay and Leakage vs. Gate Length l Partition the exposure field into grids: l Gate length changes linearly with dose tuning: ¤ ¤ Lg: gate length change di, j: change of dose in grid ri, j l Linear relation between the change of gate delay and the change of exposure dose: ¤ A: experimentally decided parameter § Assume quadratic relation between the change of gate leakage and the change of exposure dose:

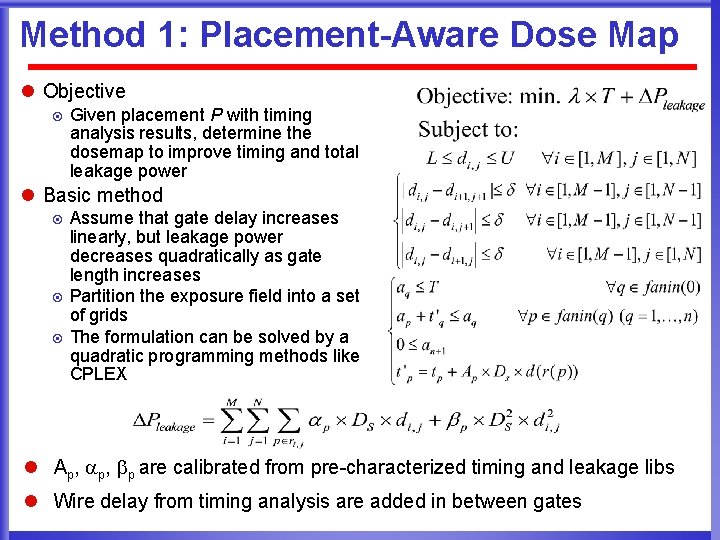

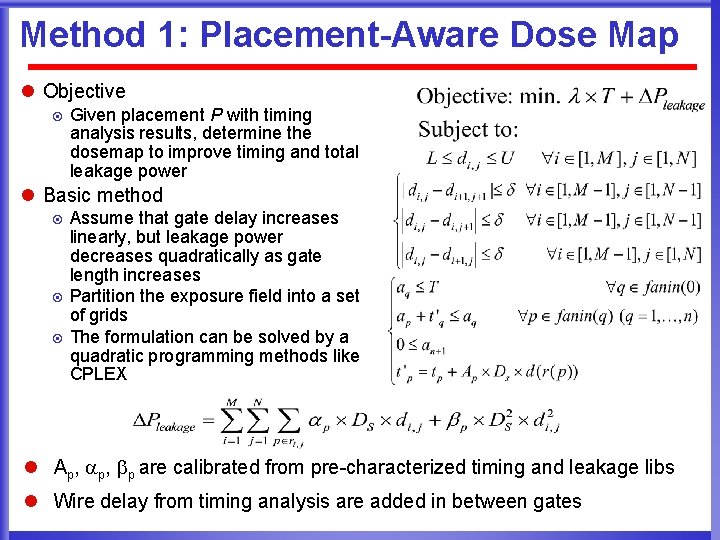

Method 1: Placement-Aware Dose Map l Objective ¤ Given placement P with timing analysis results, determine the dosemap to improve timing and total leakage power l Basic method ¤ ¤ ¤ Assume that gate delay increases linearly, but leakage power decreases quadratically as gate length increases Partition the exposure field into a set of grids The formulation can be solved by a quadratic programming methods like CPLEX l Ap, p are calibrated from pre-characterized timing and leakage libs l Wire delay from timing analysis are added in between gates

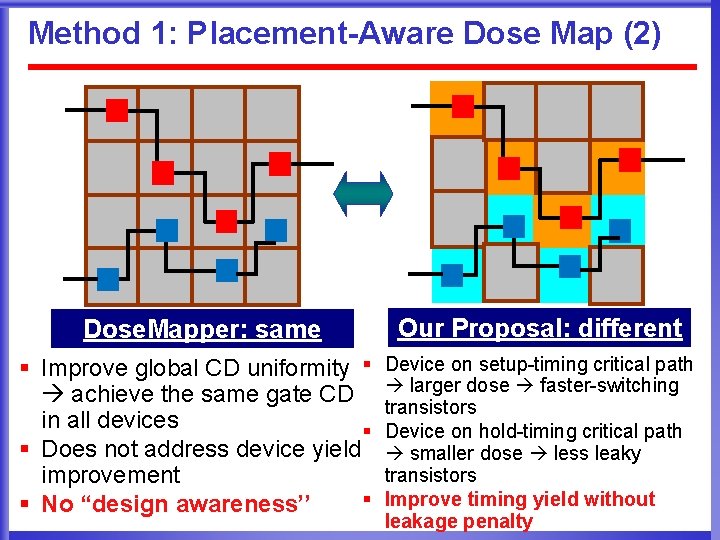

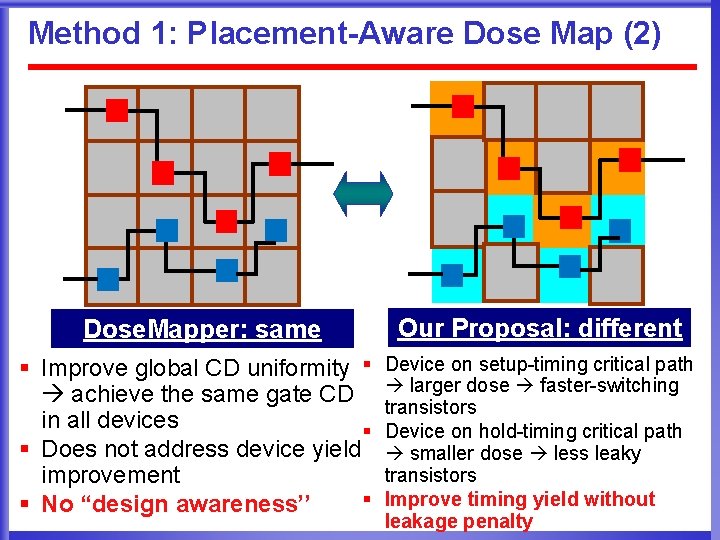

Method 1: Placement-Aware Dose Map (2) Dose. Mapper: same CDs § Improve global CD uniformity § achieve the same gate CD in all devices § § Does not address device yield improvement § § No “design awareness’’ Our Proposal: different CDs critical path Device on setup-timing larger dose faster-switching transistors Device on hold-timing critical path smaller dose less leaky transistors Improve timing yield without leakage penalty

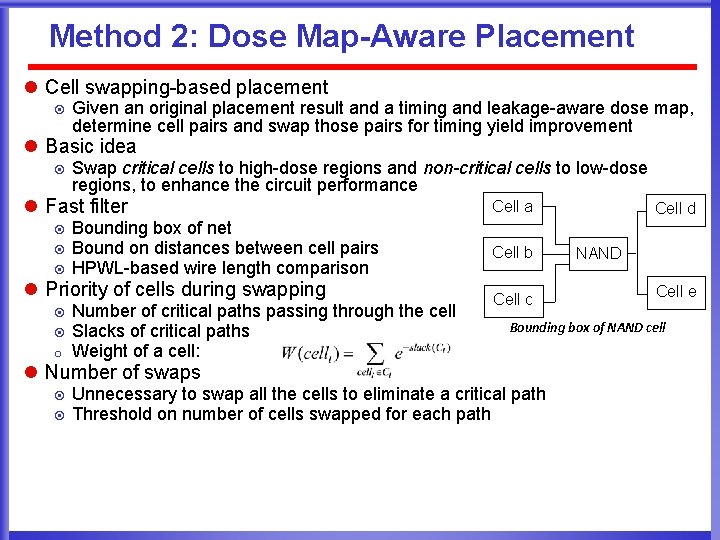

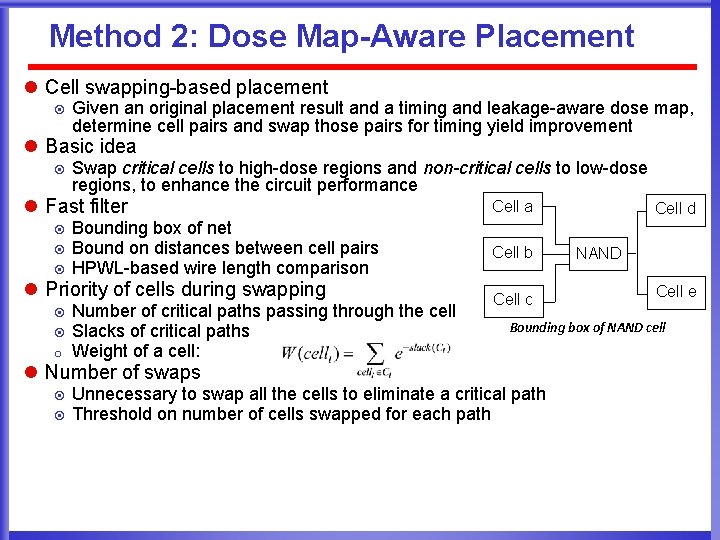

Method 2: Dose Map-Aware Placement l Cell swapping-based placement ¤ Given an original placement result and a timing and leakage-aware dose map, determine cell pairs and swap those pairs for timing yield improvement l Basic idea ¤ Swap critical cells to high-dose regions and non-critical cells to low-dose regions, to enhance the circuit performance l Fast filter ¤ ¤ ¤ Bounding box of net Bound on distances between cell pairs HPWL-based wire length comparison l Priority of cells during swapping Cell a Cell b Cell c ¤ ¤ o Number of critical paths passing through the cell Slacks of critical paths Weight of a cell: ¤ ¤ Unnecessary to swap all the cells to eliminate a critical path Threshold on number of cells swapped for each path Cell d NAND Cell e Bounding box of NAND cell l Number of swaps

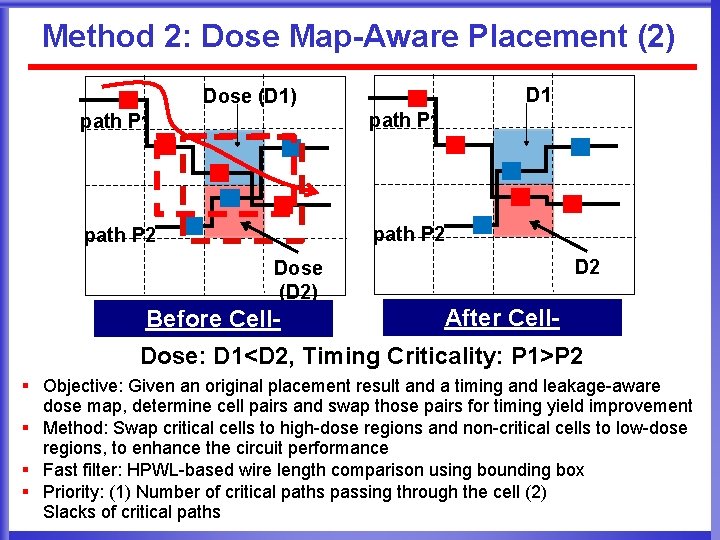

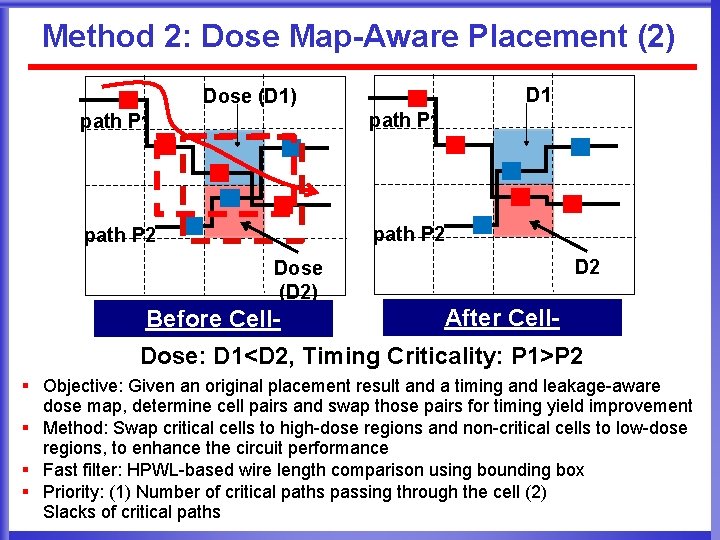

Method 2: Dose Map-Aware Placement (2) D 1 Dose (D 1) path P 1 path P 2 Dose (D 2) D 2 After Cell. Before Cell. Swapping Dose: D 1<D 2, Timing Criticality: P 1>P 2 § Objective: Given an original placement result and a timing and leakage-aware dose map, determine cell pairs and swap those pairs for timing yield improvement § Method: Swap critical cells to high-dose regions and non-critical cells to low-dose regions, to enhance the circuit performance § Fast filter: HPWL-based wire length comparison using bounding box § Priority: (1) Number of critical paths passing through the cell (2) Slacks of critical paths

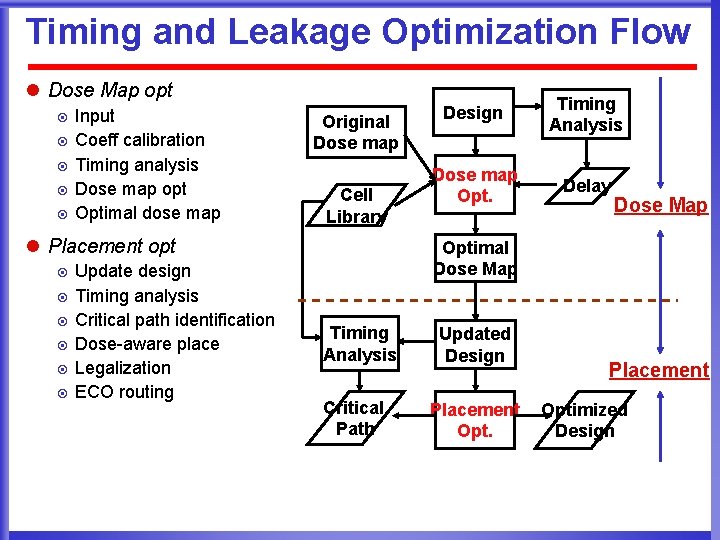

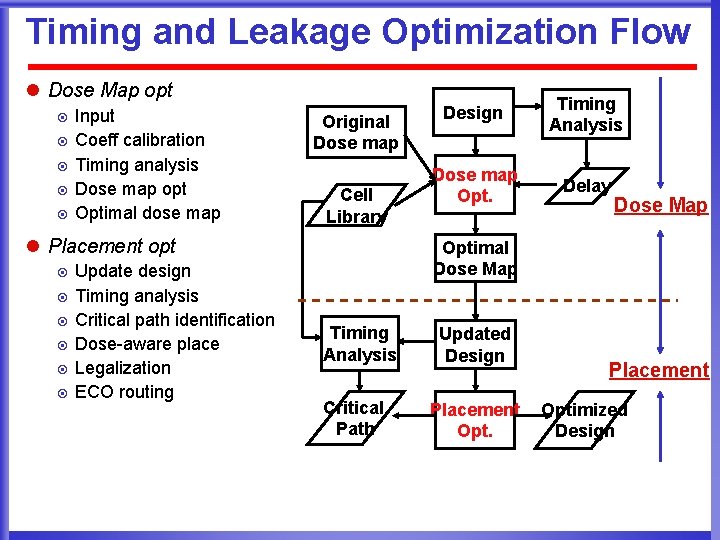

Timing and Leakage Optimization Flow l Dose Map opt ¤ ¤ ¤ Input Coeff calibration Timing analysis Dose map opt Optimal dose map Original Dose map Cell Library l Placement opt ¤ ¤ ¤ Update design Timing analysis Critical path identification Dose-aware place Legalization ECO routing Design Timing Analysis Dose map Opt. Delay Dose Map Optimal Dose Map Timing Analysis Critical Path Updated Design Placement Optimized Design

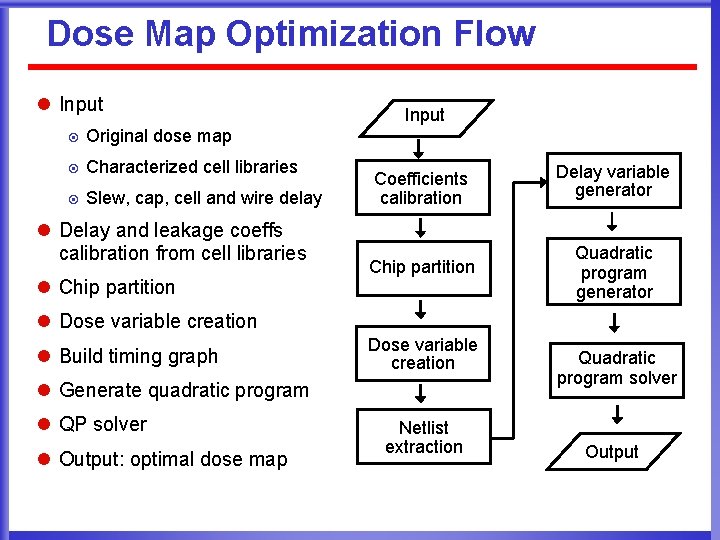

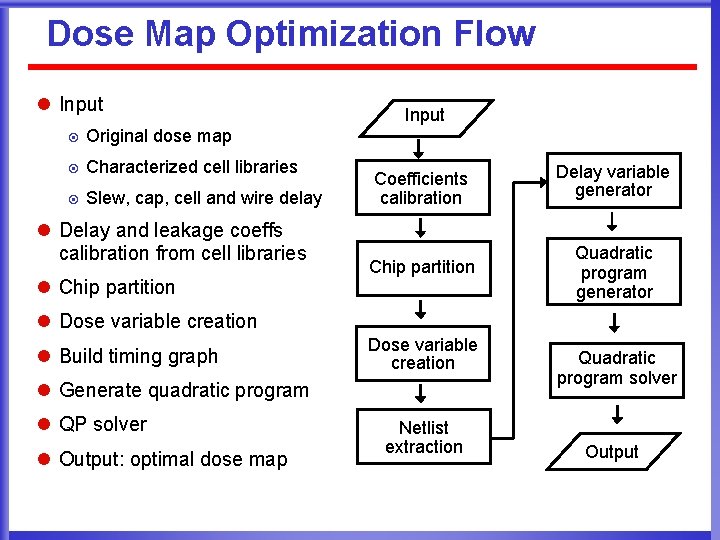

Dose Map Optimization Flow l Input ¤ Original dose map ¤ Characterized cell libraries ¤ Slew, cap, cell and wire delay l Delay and leakage coeffs calibration from cell libraries l Chip partition Input Coefficients calibration Delay variable generator Chip partition Quadratic program generator l Dose variable creation l Build timing graph Dose variable creation l Generate quadratic program l QP solver l Output: optimal dose map Netlist extraction Quadratic program solver Output

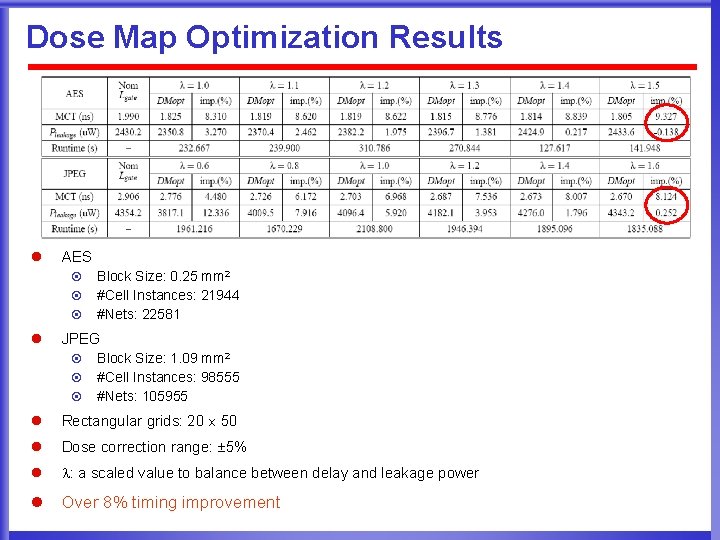

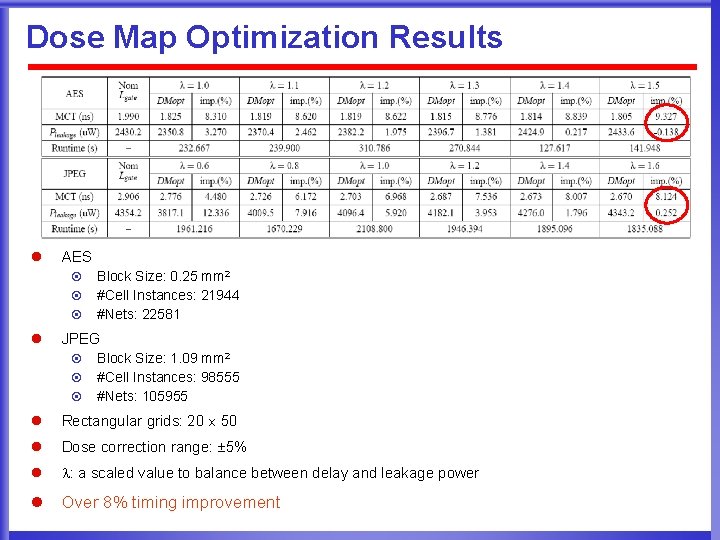

Dose Map Optimization Results l AES ¤ ¤ ¤ l Block Size: 0. 25 mm 2 #Cell Instances: 21944 #Nets: 22581 JPEG ¤ ¤ ¤ Block Size: 1. 09 mm 2 #Cell Instances: 98555 #Nets: 105955 l Rectangular grids: 20 50 l Dose correction range: 5% l : a scaled value to balance between delay and leakage power l Over 8% timing improvement

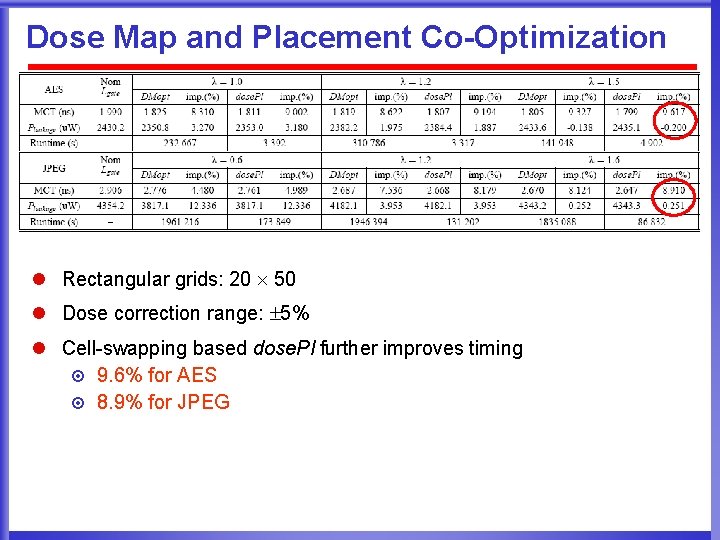

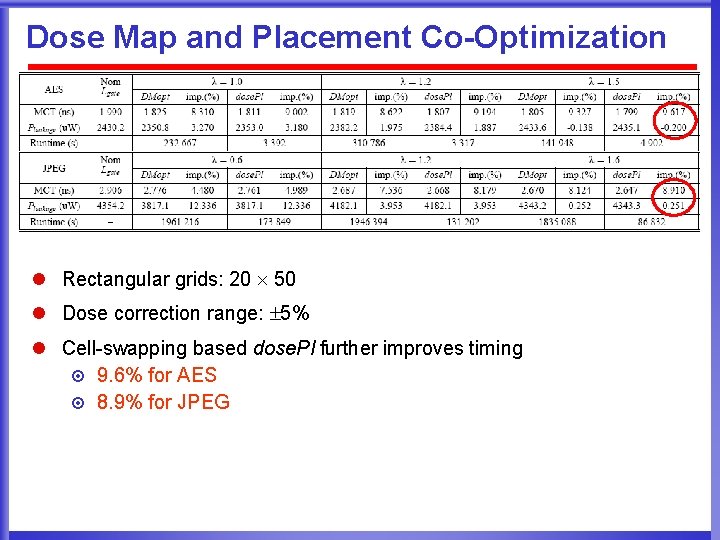

Dose Map and Placement Co-Optimization l Rectangular grids: 20 50 l Dose correction range: 5% l Cell-swapping based dose. Pl further improves timing ¤ 9. 6% for AES ¤ 8. 9% for JPEG

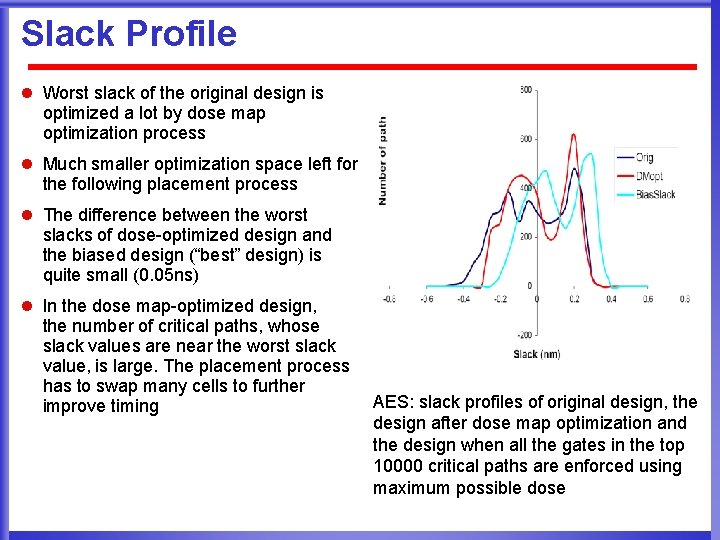

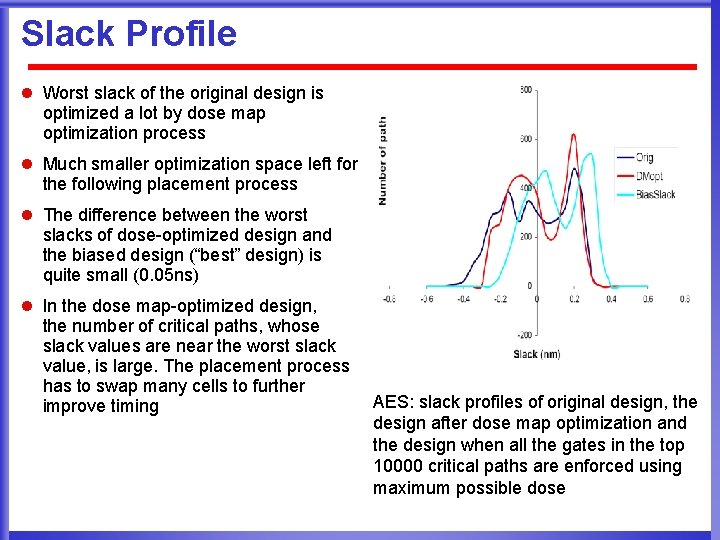

Slack Profile l Worst slack of the original design is optimized a lot by dose map optimization process l Much smaller optimization space left for the following placement process l The difference between the worst slacks of dose-optimized design and the biased design (“best” design) is quite small (0. 05 ns) l In the dose map-optimized design, the number of critical paths, whose slack values are near the worst slack value, is large. The placement process has to swap many cells to further improve timing AES: slack profiles of original design, the design after dose map optimization and the design when all the gates in the top 10000 critical paths are enforced using maximum possible dose

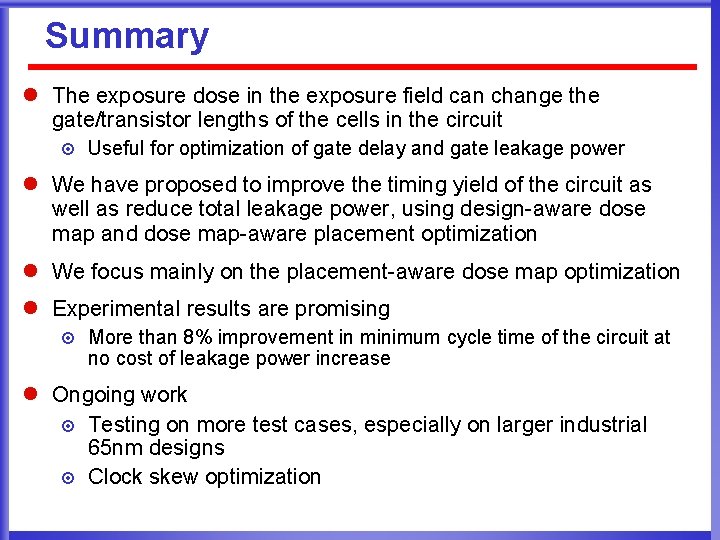

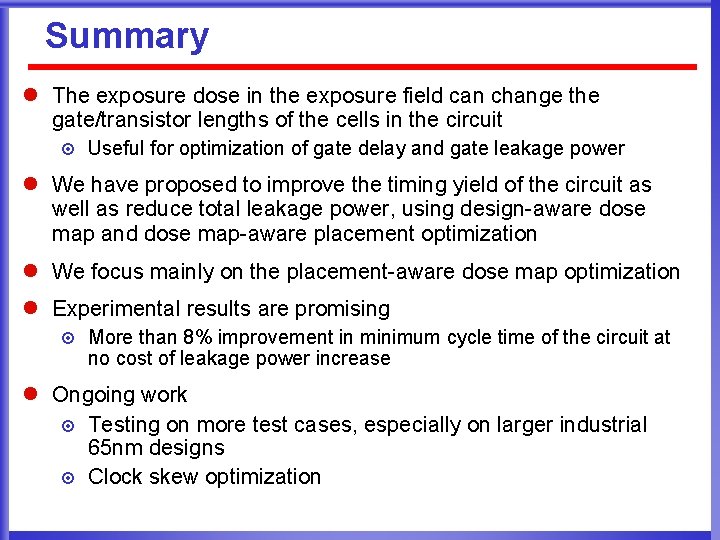

Summary l The exposure dose in the exposure field can change the gate/transistor lengths of the cells in the circuit ¤ Useful for optimization of gate delay and gate leakage power l We have proposed to improve the timing yield of the circuit as well as reduce total leakage power, using design-aware dose map and dose map-aware placement optimization l We focus mainly on the placement-aware dose map optimization l Experimental results are promising ¤ More than 8% improvement in minimum cycle time of the circuit at no cost of leakage power increase l Ongoing work ¤ Testing on more test cases, especially on larger industrial 65 nm designs ¤ Clock skew optimization