Device Tradeoffs Greg Stitt ECE Department University of

- Slides: 20

Device Tradeoffs Greg Stitt ECE Department University of Florida

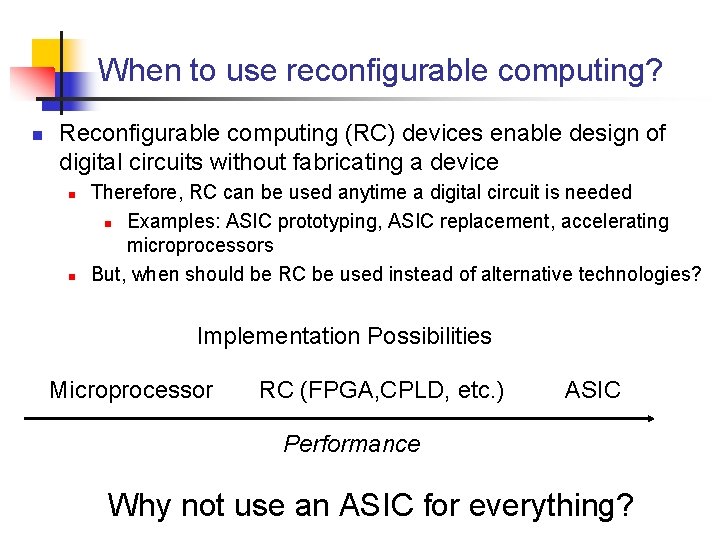

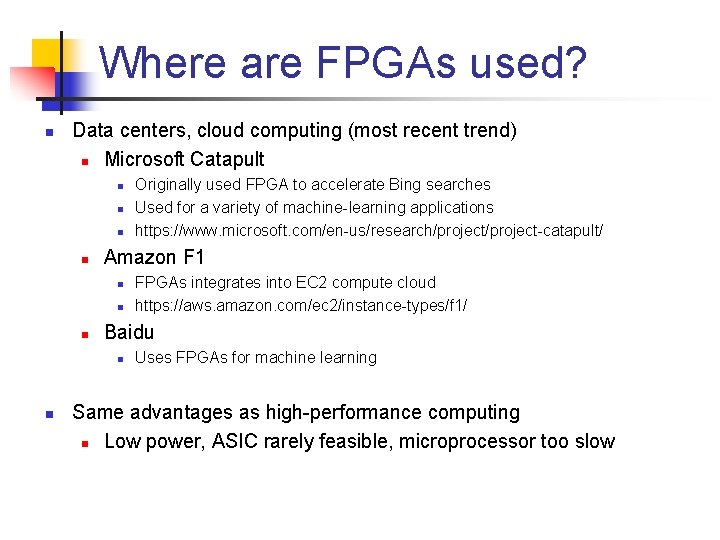

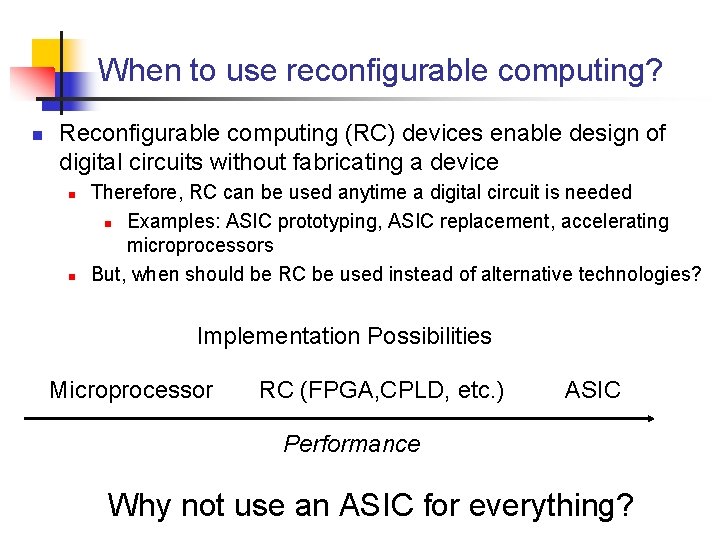

When to use reconfigurable computing? n Reconfigurable computing (RC) devices enable design of digital circuits without fabricating a device n n Therefore, RC can be used anytime a digital circuit is needed n Examples: ASIC prototyping, ASIC replacement, accelerating microprocessors But, when should be RC be used instead of alternative technologies? Implementation Possibilities Microprocessor RC (FPGA, CPLD, etc. ) ASIC Performance Why not use an ASIC for everything?

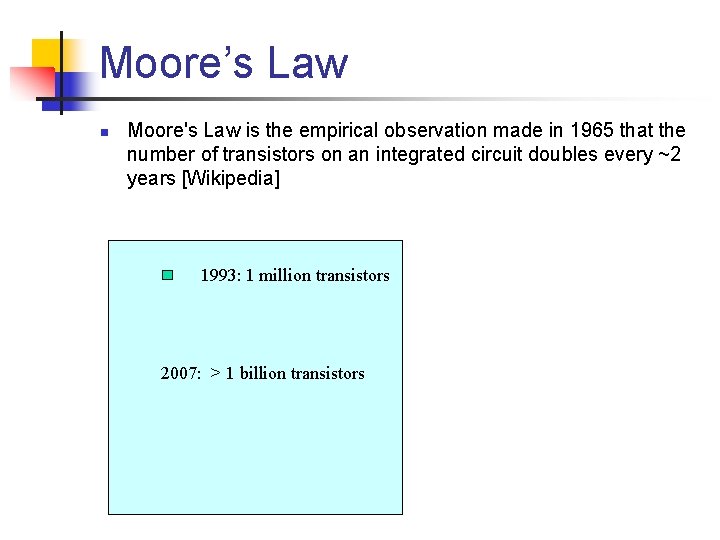

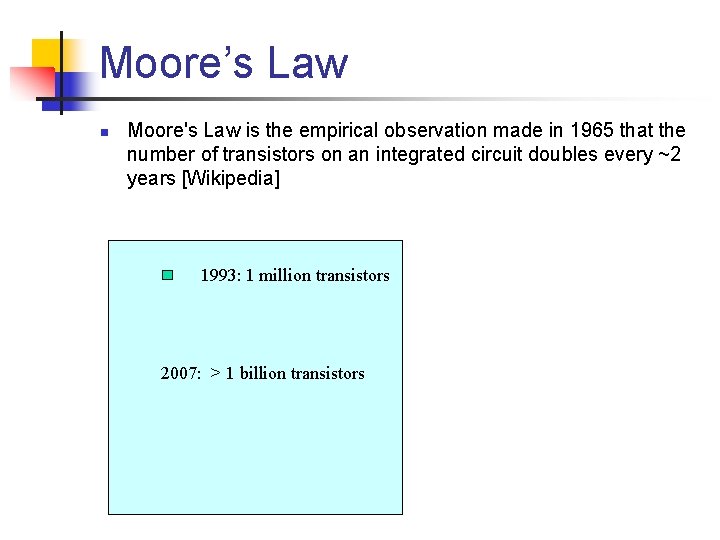

Moore’s Law n Moore's Law is the empirical observation made in 1965 that the number of transistors on an integrated circuit doubles every ~2 years [Wikipedia] 1993: 1 million transistors 2007: > 1 billion transistors

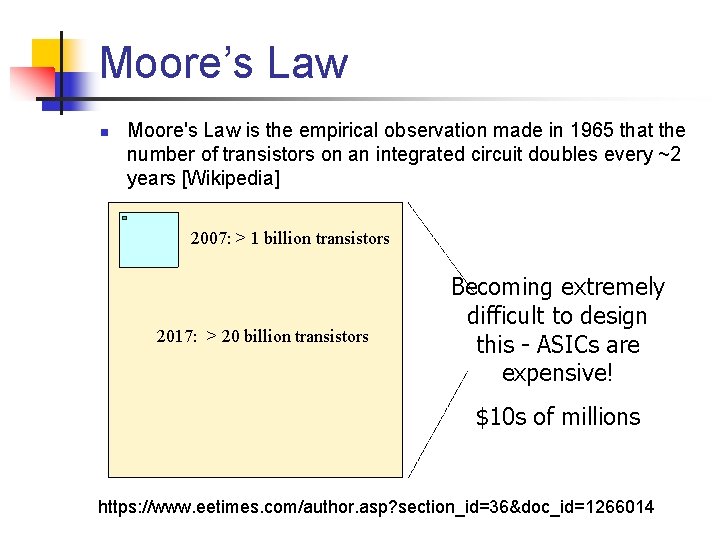

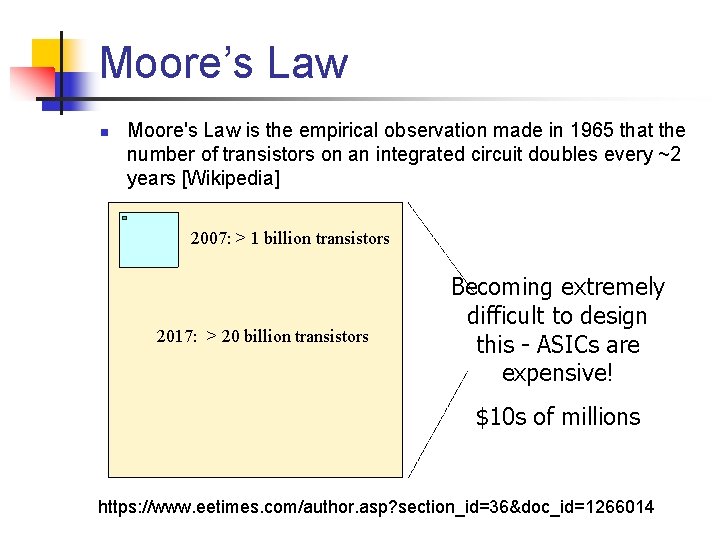

Moore’s Law n Moore's Law is the empirical observation made in 1965 that the number of transistors on an integrated circuit doubles every ~2 years [Wikipedia] 2007: > 1 billion transistors 2017: > 20 billion transistors Becoming extremely difficult to design this - ASICs are expensive! $10 s of millions https: //www. eetimes. com/author. asp? section_id=36&doc_id=1266014

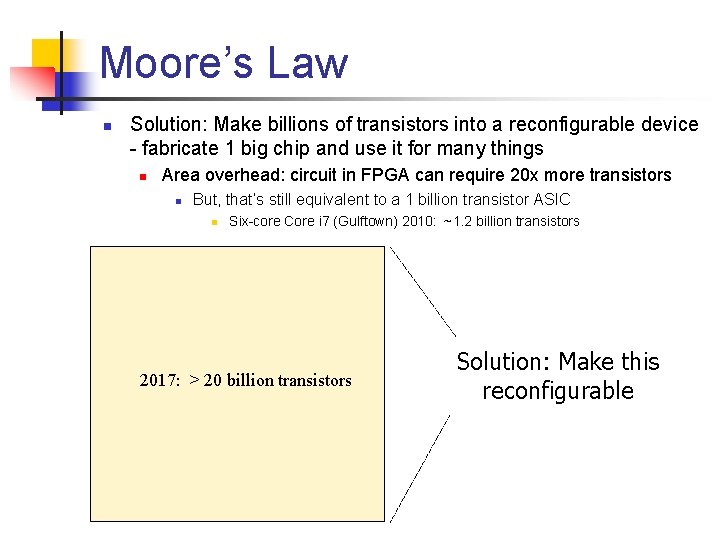

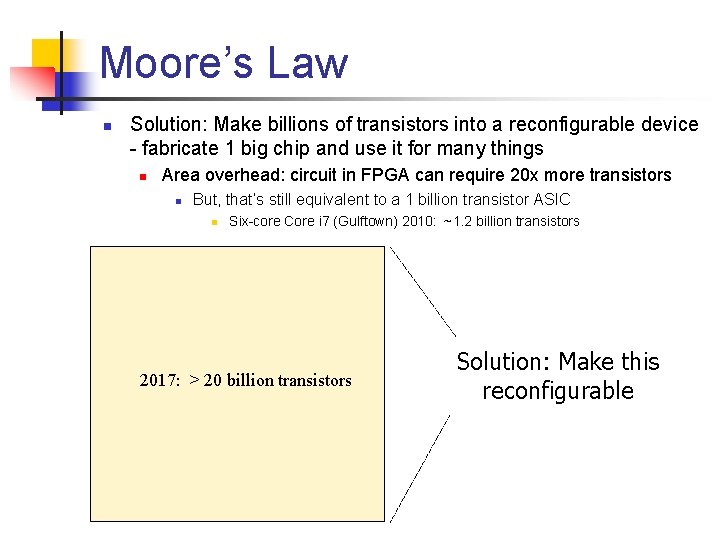

Moore’s Law n Solution: Make billions of transistors into a reconfigurable device - fabricate 1 big chip and use it for many things n Area overhead: circuit in FPGA can require 20 x more transistors n But, that’s still equivalent to a 1 billion transistor ASIC n Six-core Core i 7 (Gulftown) 2010: ~1. 2 billion transistors 2017: > 20 billion transistors Solution: Make this reconfigurable

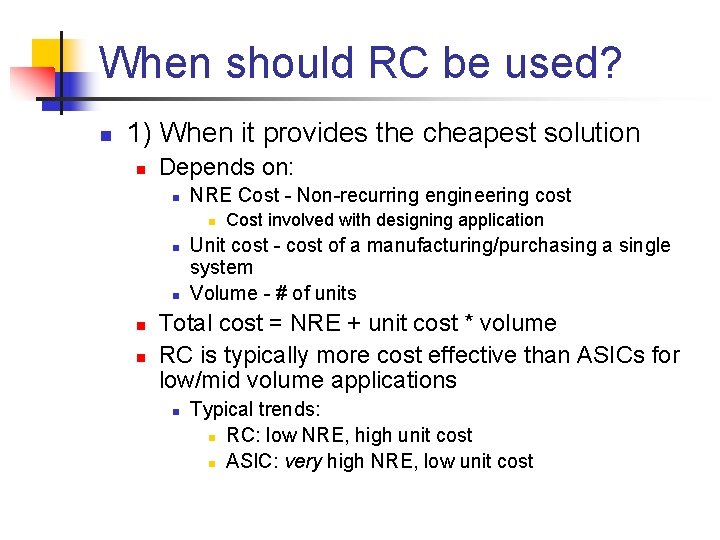

When should RC be used? n 1) When it provides the cheapest solution n Depends on: n NRE Cost - Non-recurring engineering cost n n n Cost involved with designing application Unit cost - cost of a manufacturing/purchasing a single system Volume - # of units Total cost = NRE + unit cost * volume RC is typically more cost effective than ASICs for low/mid volume applications n Typical trends: n RC: low NRE, high unit cost n ASIC: very high NRE, low unit cost

What about microprocessors? n Similar cost issues n µP (microprocessor) trends n n n low NRE cost (coding is cheap) Unit cost varies from several dollars to several thousand Wouldn’t cheapest microprocessor always be the cheapest solution? n Yes, but …

What about microprocessors? n Often, microprocessors cannot meet performance constraints n n e. g. video decoder must achieve minimum frame rate Common reason for using custom circuit implementation

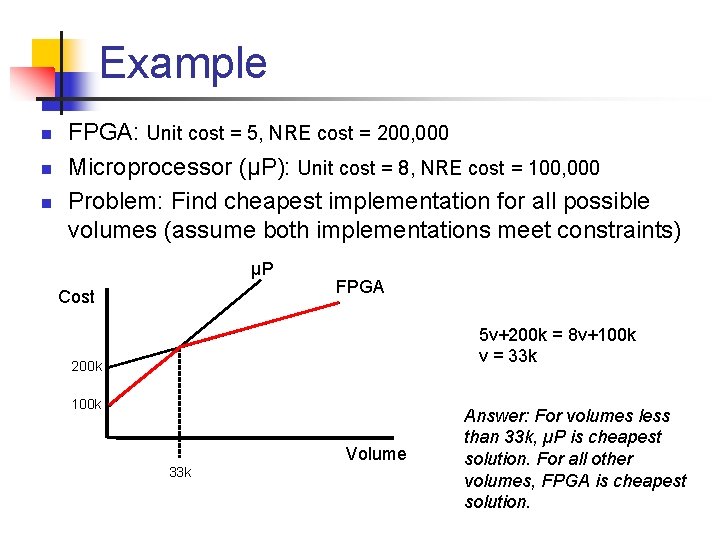

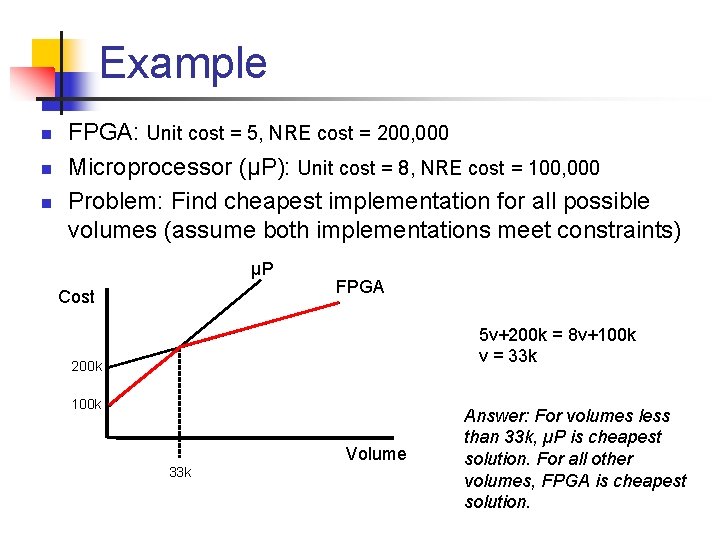

Example n n n FPGA: Unit cost = 5, NRE cost = 200, 000 Microprocessor (µP): Unit cost = 8, NRE cost = 100, 000 Problem: Find cheapest implementation for all possible volumes (assume both implementations meet constraints) µP Cost FPGA 5 v+200 k = 8 v+100 k v = 33 k 200 k 100 k Volume 33 k Answer: For volumes less than 33 k, µP is cheapest solution. For all other volumes, FPGA is cheapest solution.

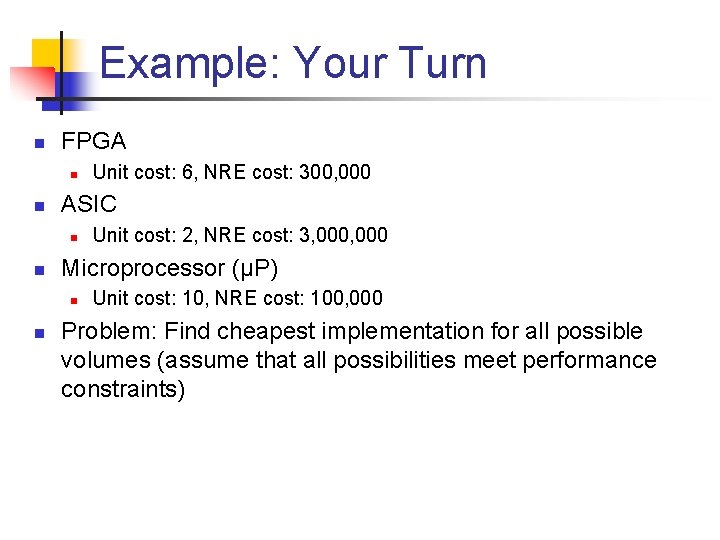

Example: Your Turn n FPGA n n ASIC n n Unit cost: 2, NRE cost: 3, 000 Microprocessor (µP) n n Unit cost: 6, NRE cost: 300, 000 Unit cost: 10, NRE cost: 100, 000 Problem: Find cheapest implementation for all possible volumes (assume that all possibilities meet performance constraints)

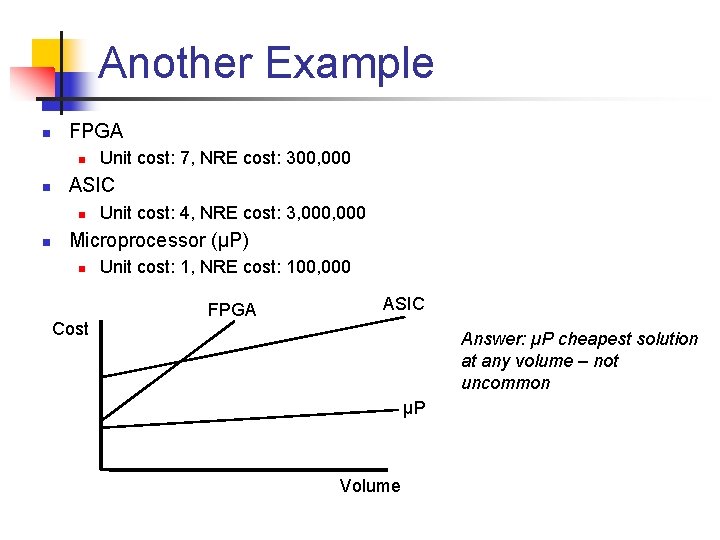

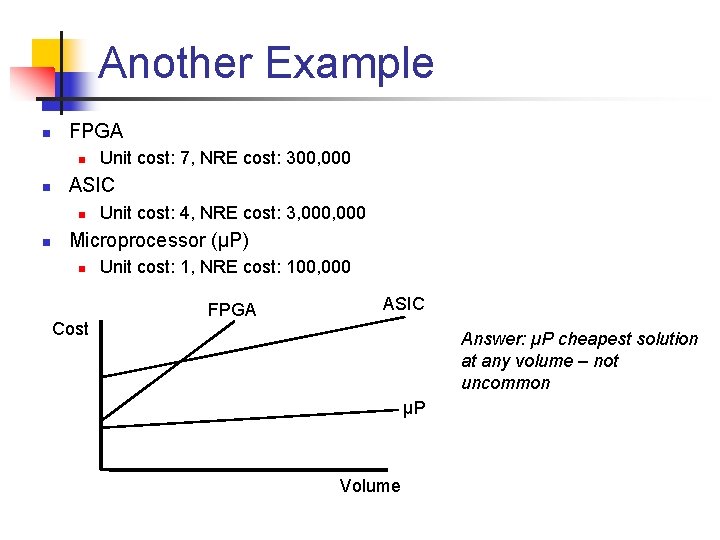

Another Example n FPGA n n ASIC n n Unit cost: 7, NRE cost: 300, 000 Unit cost: 4, NRE cost: 3, 000 Microprocessor (µP) n Cost Unit cost: 1, NRE cost: 100, 000 FPGA ASIC Answer: µP cheapest solution at any volume – not uncommon µP Volume

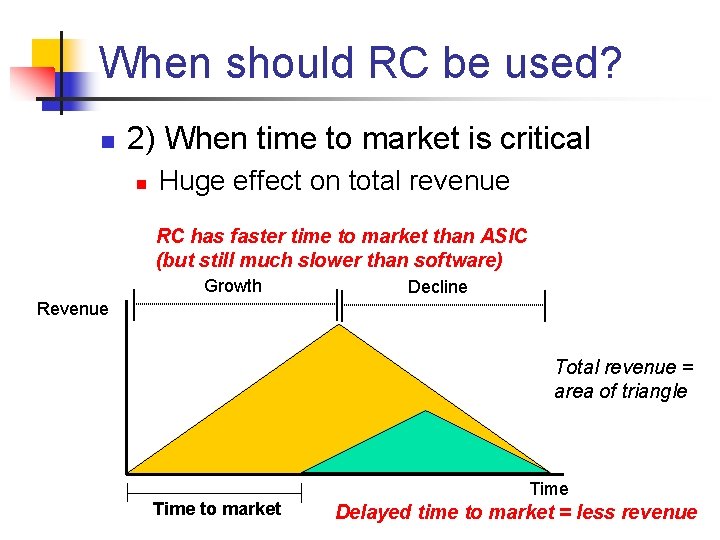

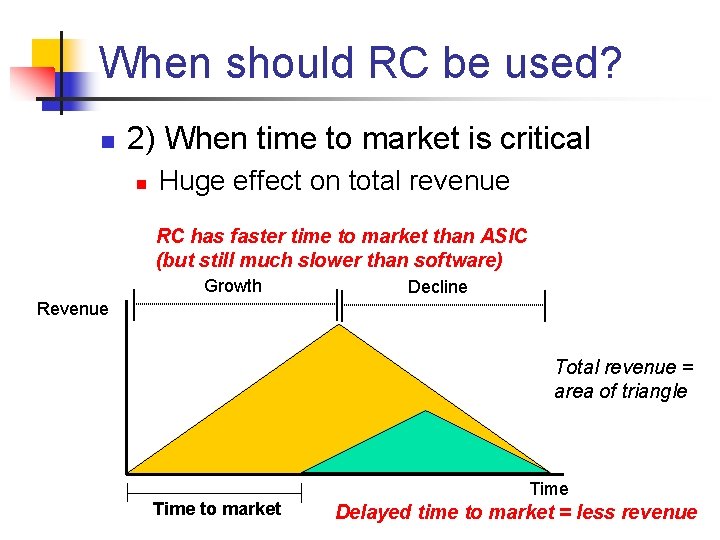

When should RC be used? n 2) When time to market is critical n Huge effect on total revenue RC has faster time to market than ASIC (but still much slower than software) Growth Decline Revenue Total revenue = area of triangle Time to market Delayed time to market = less revenue

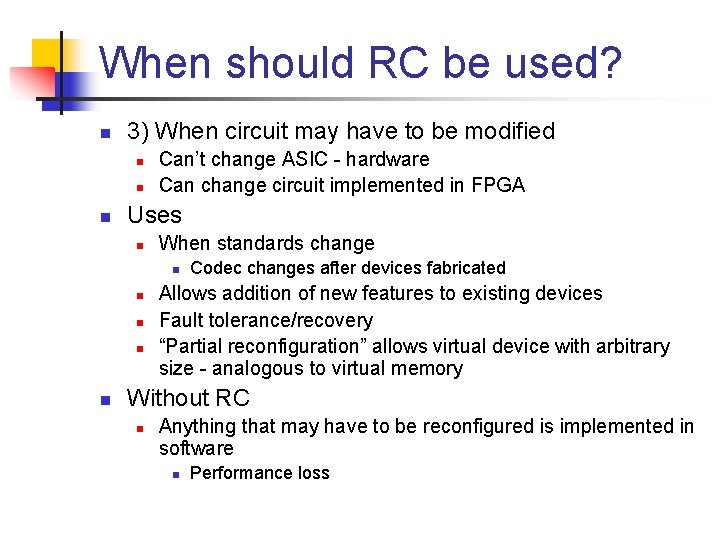

When should RC be used? n 3) When circuit may have to be modified n n n Can’t change ASIC - hardware Can change circuit implemented in FPGA Uses n When standards change n n n Codec changes after devices fabricated Allows addition of new features to existing devices Fault tolerance/recovery “Partial reconfiguration” allows virtual device with arbitrary size - analogous to virtual memory Without RC n Anything that may have to be reconfigured is implemented in software n Performance loss

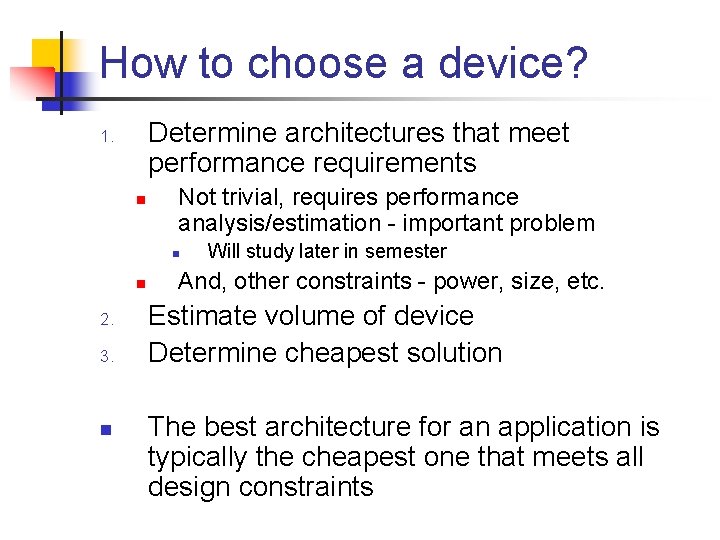

How to choose a device? Determine architectures that meet performance requirements 1. n Not trivial, requires performance analysis/estimation - important problem n n 2. 3. n Will study later in semester And, other constraints - power, size, etc. Estimate volume of device Determine cheapest solution The best architecture for an application is typically the cheapest one that meets all design constraints

Where are FPGAs used? n ASIC prototyping (first main market for FPGAs) n n Validate ASIC on many FPGAs before fabricating Embedded systems n n FPGAs used in low-power networking and signal-processing systems (e. g. routers, audio equipment) Advantages n FPGAs achieve performance close to ASIC, sometimes at much lower cost (ASIC replacement) n n High-volume systems still use ASICs (e. g. cell phones) n But, ASICs becoming less common due to increasing costs Reconfigurable! n n If standards change, architecture is not fixed Can add new features (or fix bugs) after production

Where are FPGAs used? n High-performance embedded computing (HPEC) n High-performance/super computing with special needs (low power, low size/weight, etc. ) n n n Satellite image processing Defense applications FPGA advantages n n Much smaller and lower power than a supercomputer Provide fault tolerance mechanisms

Where are FPGAs used? n High-performance computing (HPC) n Mid 2000 s: first appearance of high-end processors with FPGA accelerator boards n Cray, SGI, DRC, Gi. DEL, Nallatech, Xtreme. Data n n Novo-G n n 192 Altera Stratix III FPGAs integrated with 24 quad-core microprocessors ~2016: shared-memory “coherent” systems n n n Combine high-performance microprocessors with FPGA accelerators Intel Xeon+FPGA processor IBM Power 9 FPGA advantages n HPC used for many scientific apps n n Low volume, ASIC rarely feasible, microprocessor too slow Lower power consumption n n Increasingly important Cooling and energy costs are dominant factor in total cost of ownership

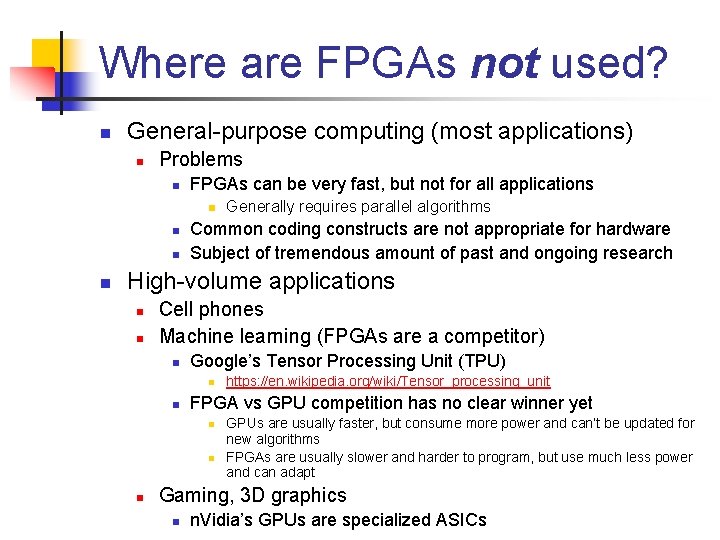

Where are FPGAs used? n Data centers, cloud computing (most recent trend) n Microsoft Catapult n n Amazon F 1 n n n FPGAs integrates into EC 2 compute cloud https: //aws. amazon. com/ec 2/instance-types/f 1/ Baidu n n Originally used FPGA to accelerate Bing searches Used for a variety of machine-learning applications https: //www. microsoft. com/en-us/research/project-catapult/ Uses FPGAs for machine learning Same advantages as high-performance computing n Low power, ASIC rarely feasible, microprocessor too slow

Where are FPGAs not used? n General-purpose computing (most applications) n Problems n FPGAs can be very fast, but not for all applications n n Generally requires parallel algorithms Common coding constructs are not appropriate for hardware Subject of tremendous amount of past and ongoing research High-volume applications n n Cell phones Machine learning (FPGAs are a competitor) n Google’s Tensor Processing Unit (TPU) n n FPGA vs GPU competition has no clear winner yet n n n https: //en. wikipedia. org/wiki/Tensor_processing_unit GPUs are usually faster, but consume more power and can’t be updated for new algorithms FPGAs are usually slower and harder to program, but use much less power and can adapt Gaming, 3 D graphics n n. Vidia’s GPUs are specialized ASICs

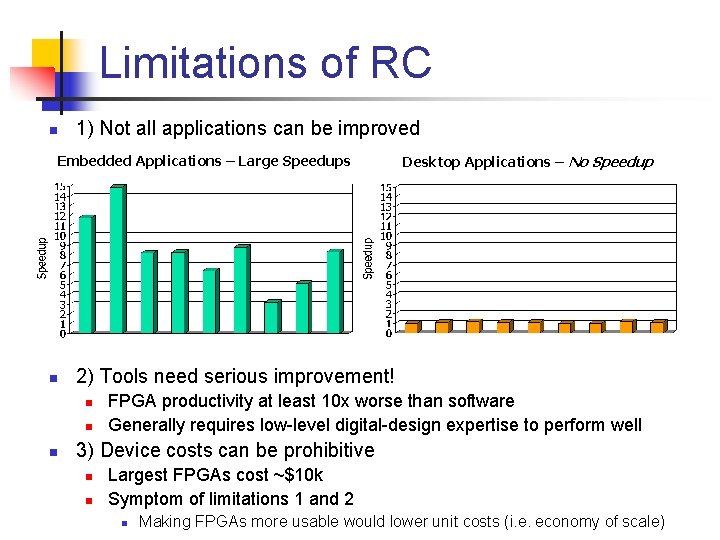

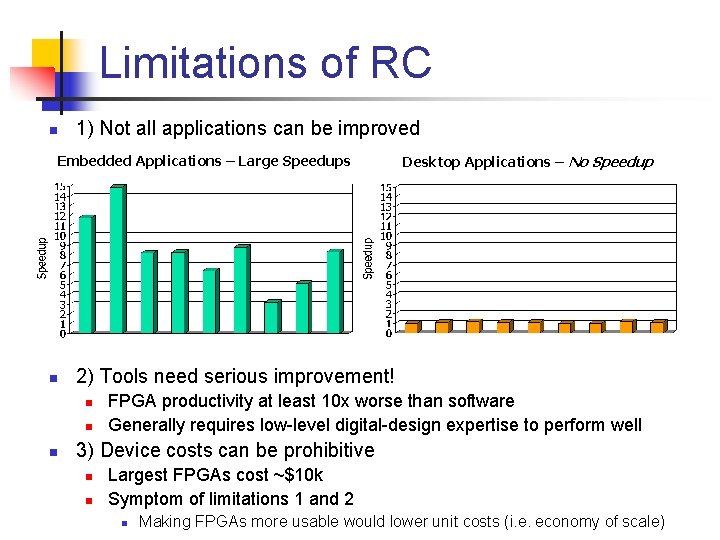

Limitations of RC n 1) Not all applications can be improved Embedded Applications – Large Speedups n 2) Tools need serious improvement! n n n Desktop Applications – No Speedup FPGA productivity at least 10 x worse than software Generally requires low-level digital-design expertise to perform well 3) Device costs can be prohibitive n n Largest FPGAs cost ~$10 k Symptom of limitations 1 and 2 n Making FPGAs more usable would lower unit costs (i. e. economy of scale)