Reconfigurable Architectures Greg Stitt ECE Department University of

Reconfigurable Architectures Greg Stitt ECE Department University of Florida

How can hardware be reconfigurable? n Problem: Can’t change fabricated chip n n ASICs are fixed Solution: n Create components that can be made to function in different ways

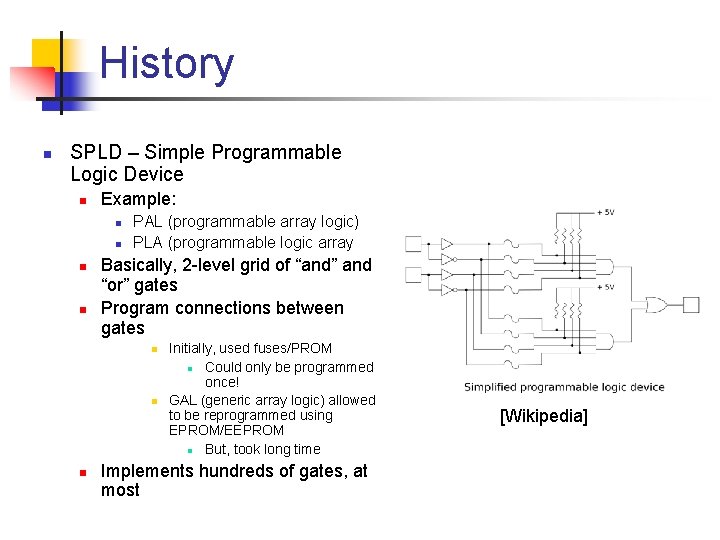

History n SPLD – Simple Programmable Logic Device n Example: n n PAL (programmable array logic) PLA (programmable logic array Basically, 2 -level grid of “and” and “or” gates Program connections between gates n n n Initially, used fuses/PROM n Could only be programmed once! GAL (generic array logic) allowed to be reprogrammed using EPROM/EEPROM n But, took long time Implements hundreds of gates, at most [Wikipedia]

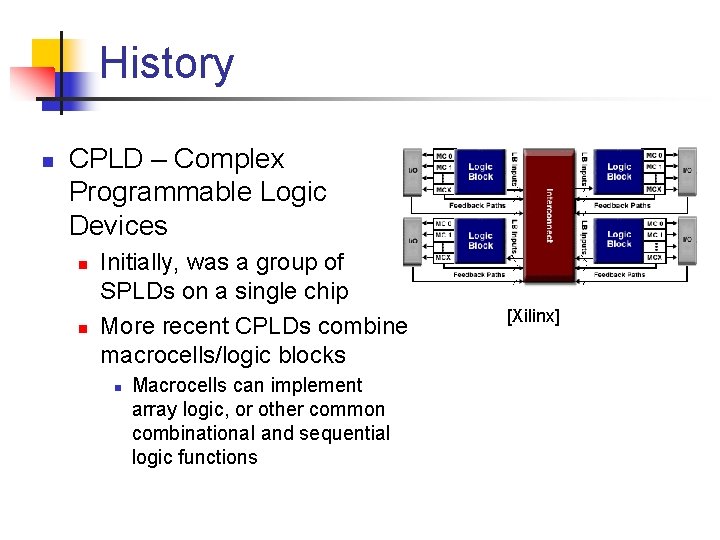

History n CPLD – Complex Programmable Logic Devices n n Initially, was a group of SPLDs on a single chip More recent CPLDs combine macrocells/logic blocks n Macrocells can implement array logic, or other common combinational and sequential logic functions [Xilinx]

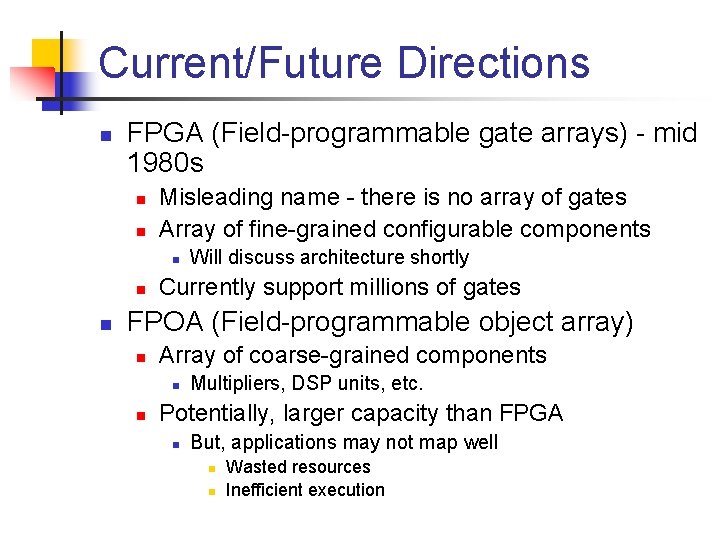

Current/Future Directions n FPGA (Field-programmable gate arrays) - mid 1980 s n n Misleading name - there is no array of gates Array of fine-grained configurable components n n n Will discuss architecture shortly Currently support millions of gates FPOA (Field-programmable object array) n Array of coarse-grained components n n Multipliers, DSP units, etc. Potentially, larger capacity than FPGA n But, applications may not map well n n Wasted resources Inefficient execution

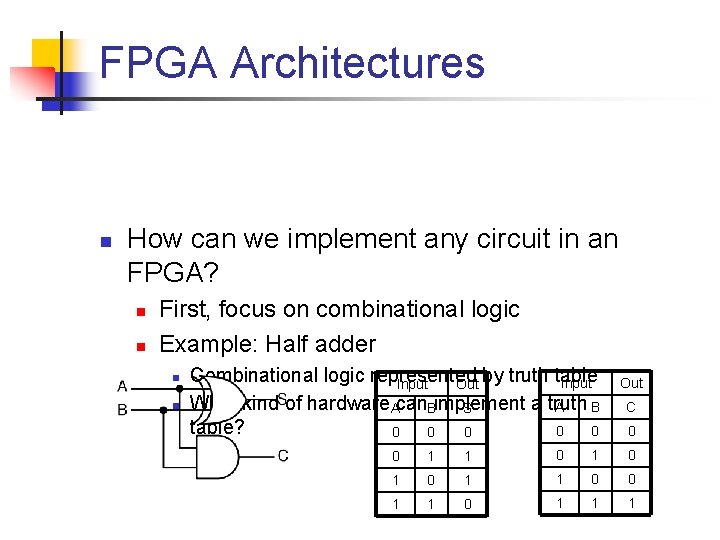

FPGA Architectures n How can we implement any circuit in an FPGA? n n First, focus on combinational logic Example: Half adder n n Combinational logic represented by truth table Input Out What kind of hardware. Acan. Bimplement a truth A B S table? 0 0 0 Out C 0 0 1 1 0 1 1 1

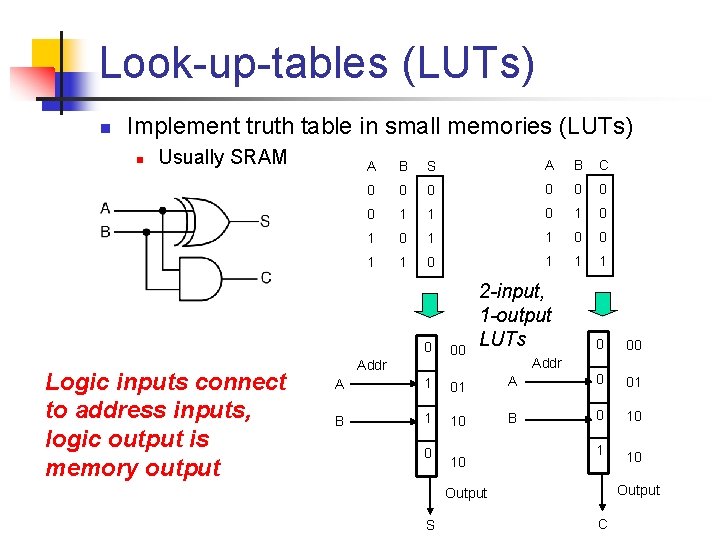

Look-up-tables (LUTs) n Implement truth table in small memories (LUTs) n Usually SRAM Logic inputs connect to address inputs, logic output is memory output A B S A B C 0 0 0 0 1 1 0 1 1 1 0 2 -input, 1 -output LUTs Addr 00 0 00 Addr A 1 01 A 0 01 B 1 10 B 0 10 1 Output S 10 C

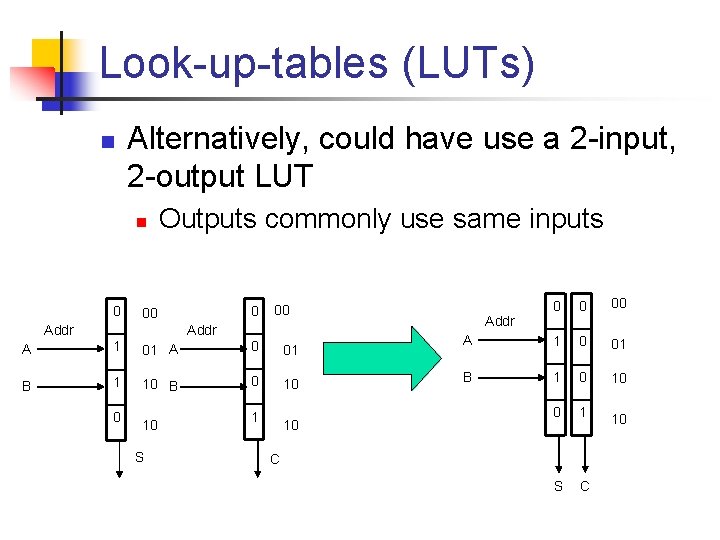

Look-up-tables (LUTs) n Alternatively, could have use a 2 -input, 2 -output LUT n 0 Outputs commonly use same inputs 0 00 Addr A 1 01 A 0 01 B 1 10 B 0 10 S 0 0 00 A 1 0 01 B 1 0 10 0 1 S C 00 1 10 Addr C 10

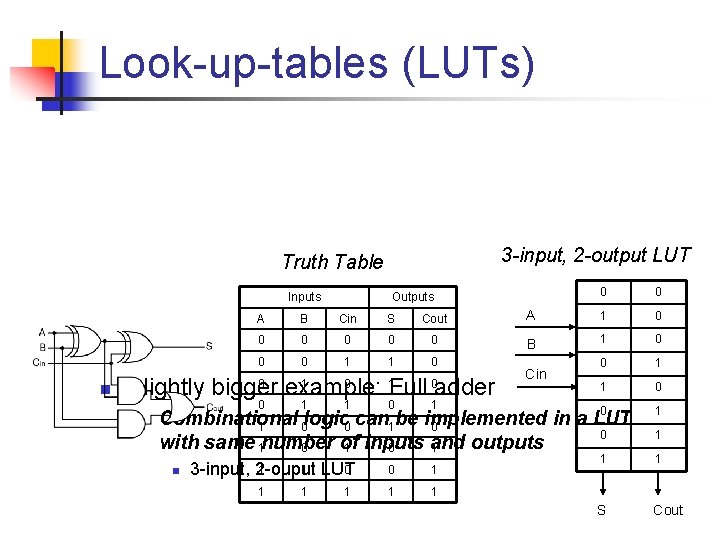

Look-up-tables (LUTs) 3 -input, 2 -output LUT Truth Table Inputs n Outputs 0 A B Cin S Cout A 1 0 0 0 B 1 0 0 0 1 1 0 0 1 Slightly bigger example: Full 0 adder 0 n 0 1 1 0 Cin 1 0 Combinational logic can be implemented in a LUT 1 0 0 with same 1 number of inputs and outputs 0 1 n 1 1 LUT 0 3 -input, 2 -ouput 1 1 1 0 1 1 1 1 S Cout

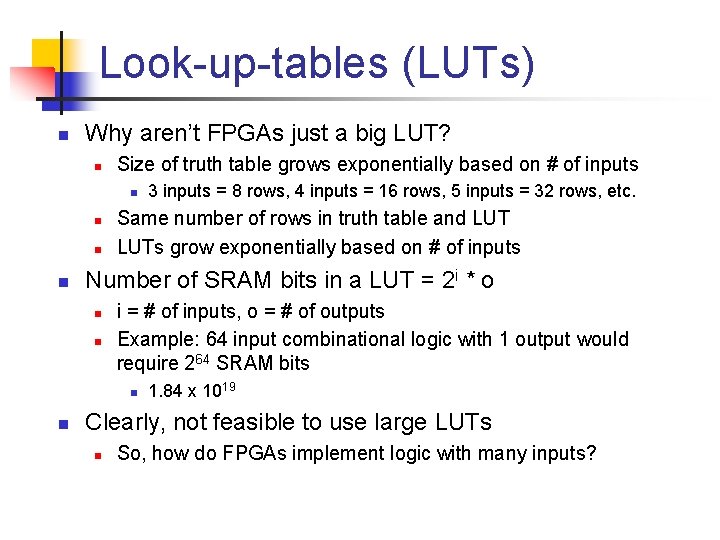

Look-up-tables (LUTs) n Why aren’t FPGAs just a big LUT? n Size of truth table grows exponentially based on # of inputs n n Same number of rows in truth table and LUTs grow exponentially based on # of inputs Number of SRAM bits in a LUT = 2 i * o n n i = # of inputs, o = # of outputs Example: 64 input combinational logic with 1 output would require 264 SRAM bits n n 3 inputs = 8 rows, 4 inputs = 16 rows, 5 inputs = 32 rows, etc. 1. 84 x 1019 Clearly, not feasible to use large LUTs n So, how do FPGAs implement logic with many inputs?

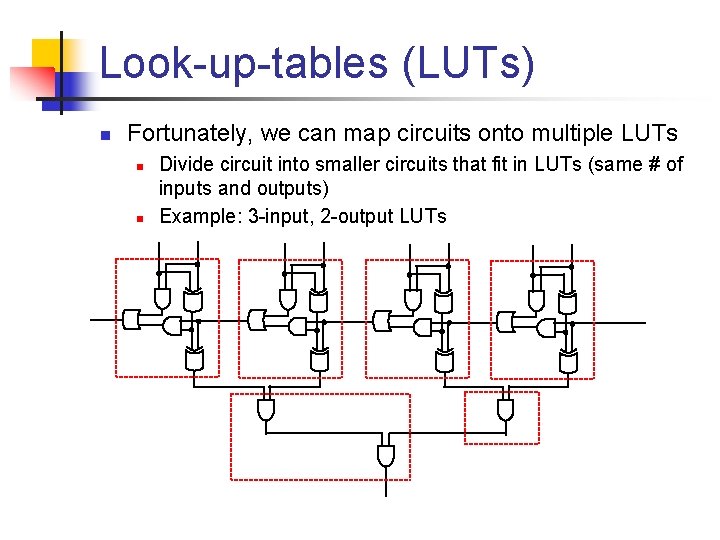

Look-up-tables (LUTs) n Fortunately, we can map circuits onto multiple LUTs n n Divide circuit into smaller circuits that fit in LUTs (same # of inputs and outputs) Example: 3 -input, 2 -output LUTs

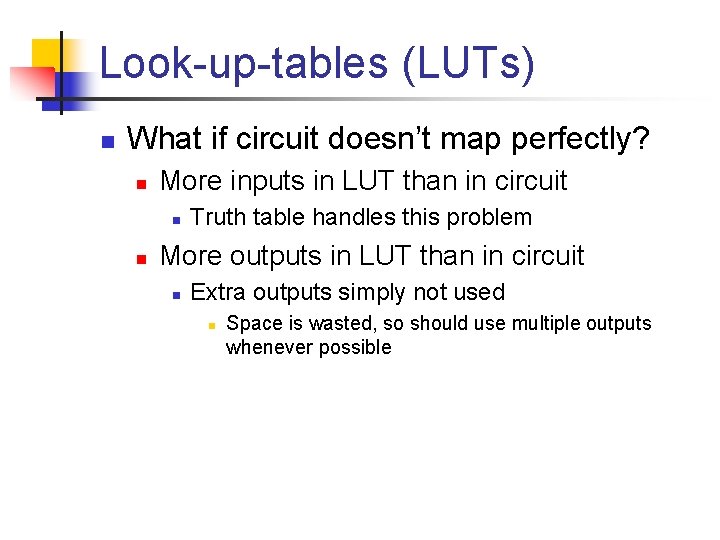

Look-up-tables (LUTs) n What if circuit doesn’t map perfectly? n More inputs in LUT than in circuit n n Truth table handles this problem More outputs in LUT than in circuit n Extra outputs simply not used n Space is wasted, so should use multiple outputs whenever possible

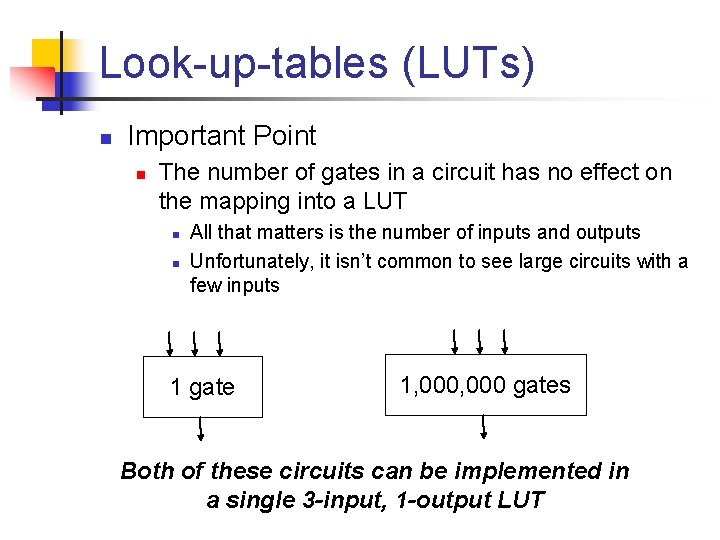

Look-up-tables (LUTs) n Important Point n The number of gates in a circuit has no effect on the mapping into a LUT n n All that matters is the number of inputs and outputs Unfortunately, it isn’t common to see large circuits with a few inputs 1 gate 1, 000 gates Both of these circuits can be implemented in a single 3 -input, 1 -output LUT

- Slides: 13