DCM II DCM II system Status Chain test

- Slides: 12

DCM II • • DCM II system Status Chain test Schedule 1

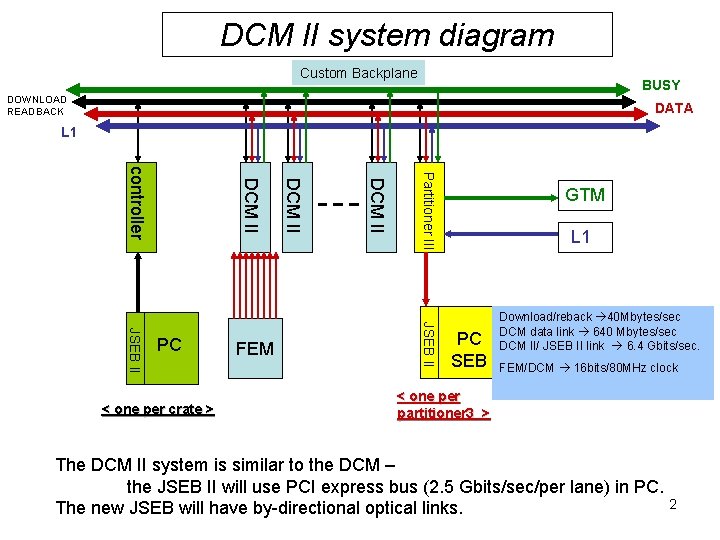

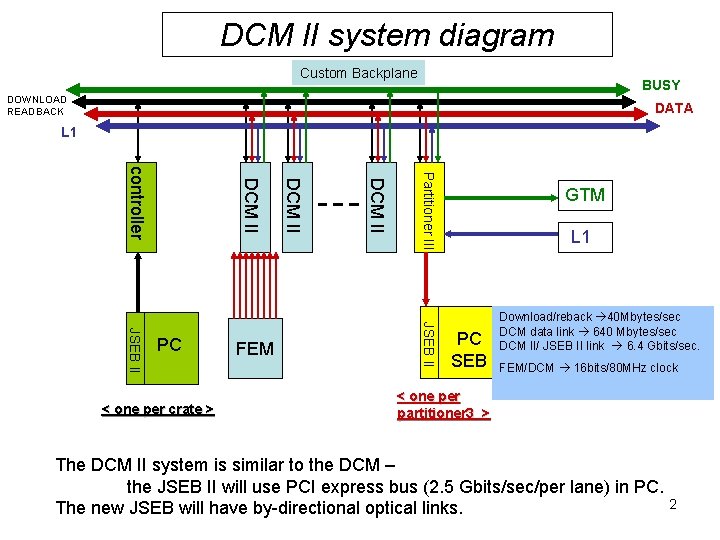

DCM II system diagram Custom Backplane BUSY DOWNLOAD READBACK DATA L 1 Partitioner III DCM II JSEB II < one per crate > FEM DCM II controller PC GTM L 1 PC SEB Download/reback 40 Mbytes/sec DCM data link 640 Mbytes/sec DCM II/ JSEB II link 6. 4 Gbits/sec. FEM/DCM 16 bits/80 MHz clock < one per partitioner 3 > The DCM II system is similar to the DCM – the JSEB II will use PCI express bus (2. 5 Gbits/sec/per lane) in PC. 2 The new JSEB will have by-directional optical links.

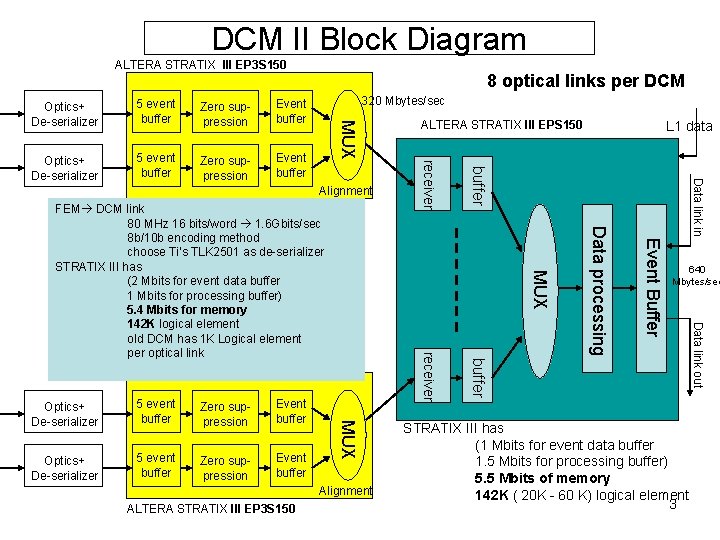

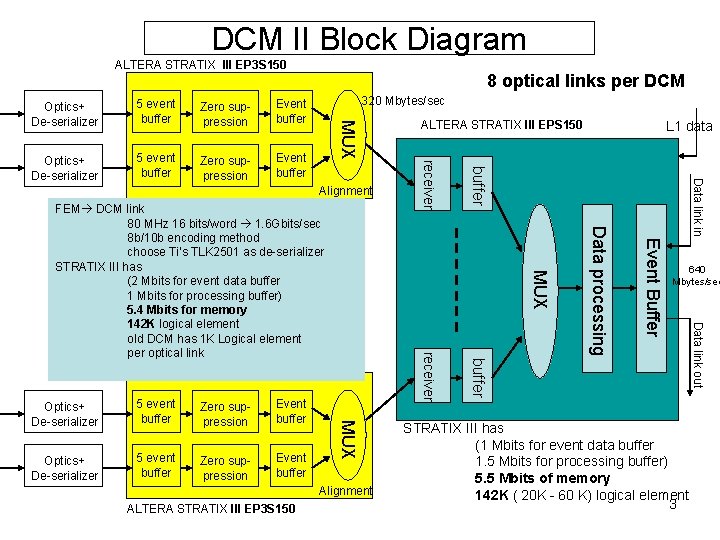

DCM II Block Diagram ALTERA STRATIX III EP 3 S 150 Optics+ De-serializer 5 event buffer Zero suppression Event buffer 320 Mbytes/sec Alignment Zero suppression Event buffer Alignment ALTERA STRATIX III EP 3 S 150 640 Mbytes/sec STRATIX III has (1 Mbits for event data buffer 1. 5 Mbits for processing buffer) 5. 5 Mbits of memory 142 K ( 20 K - 60 K) logical element 3 Data link out 5 event buffer Event Buffer Optics+ De-serializer Data processing Event buffer L 1 data buffer Zero suppression receiver 5 event buffer MUX Optics+ De-serializer MUX FEM DCM link 80 MHz 16 bits/word 1. 6 Gbits/sec 8 b/10 b encoding method choose Ti’s TLK 2501 as de-serializer STRATIX III has (2 Mbits for event data buffer 1 Mbits for processing buffer) 5. 4 Mbits for memory 142 K logical element old DCM has 1 K Logical element per optical link ALTERA STRATIX III EPS 150 Data link in Event buffer Zero suppression receiver 5 event buffer MUX Optics+ De-serializer 8 optical links per DCM

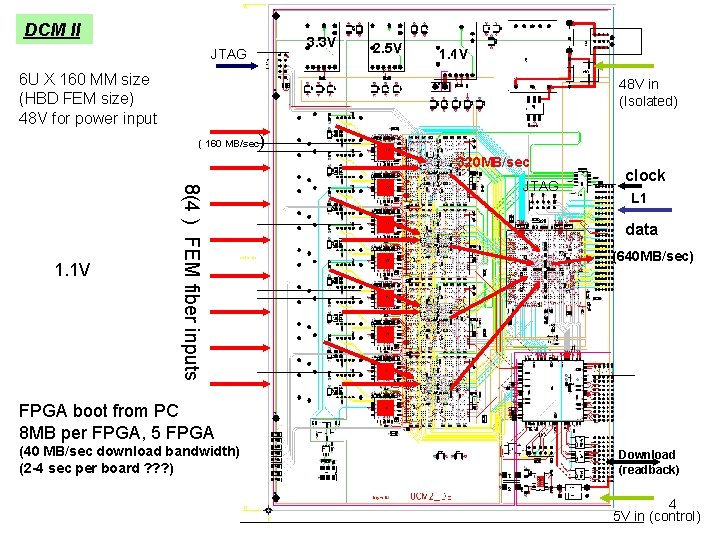

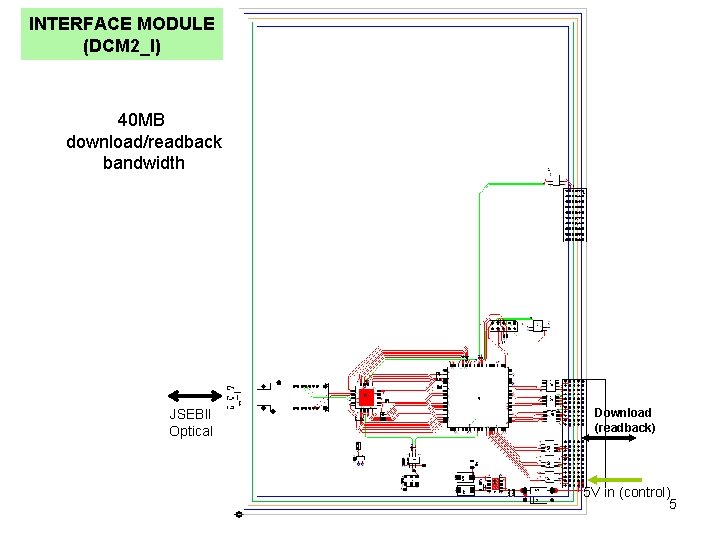

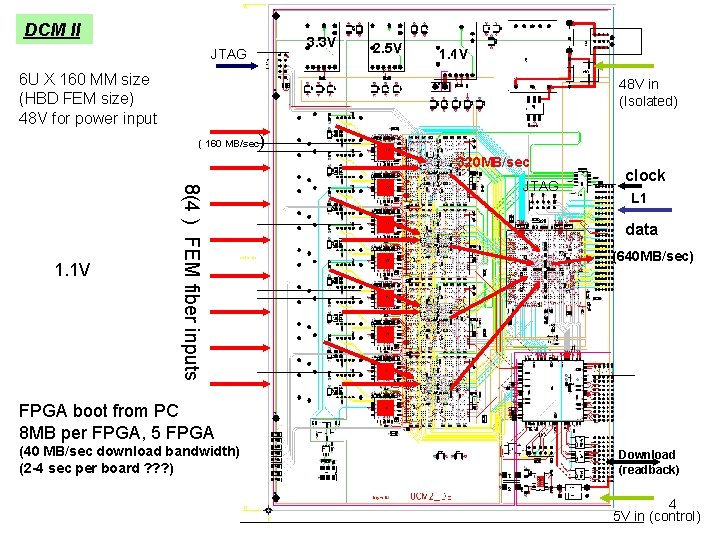

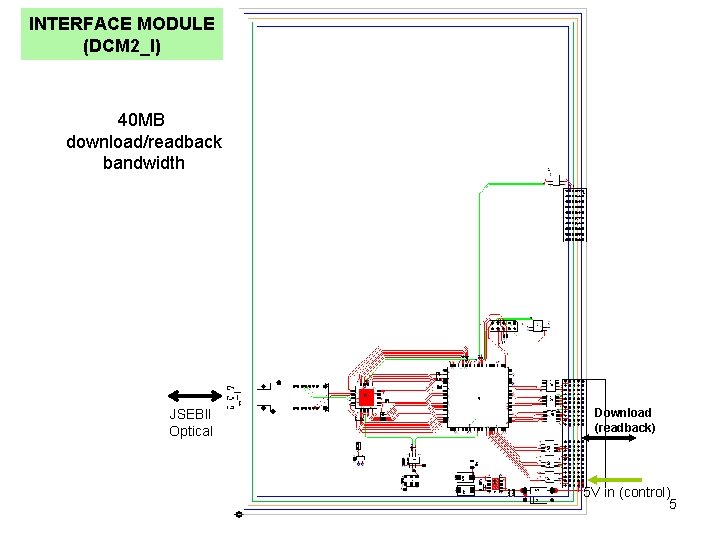

DCM II 3. 3 V JTAG 2. 5 V 1. 1 V 6 U X 160 MM size (HBD FEM size) 48 V for power input 48 V in (Isolated) ) ( 160 MB/sec 320 MB/sec 8(4 ) FEM fiber inputs 1. 1 V JTAG clock L 1 data (640 MB/sec) FPGA boot from PC 8 MB per FPGA, 5 FPGA (40 MB/sec download bandwidth) (2 -4 sec per board ? ? ? ) Download (readback) 4 5 V in (control)

INTERFACE MODULE (DCM 2_I) 40 MB download/readback bandwidth JSEBII Optical Download (readback) 5 V in (control) 5

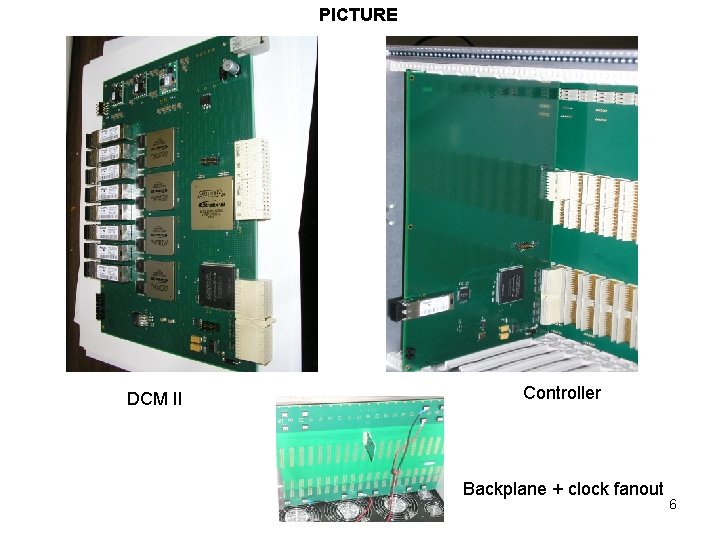

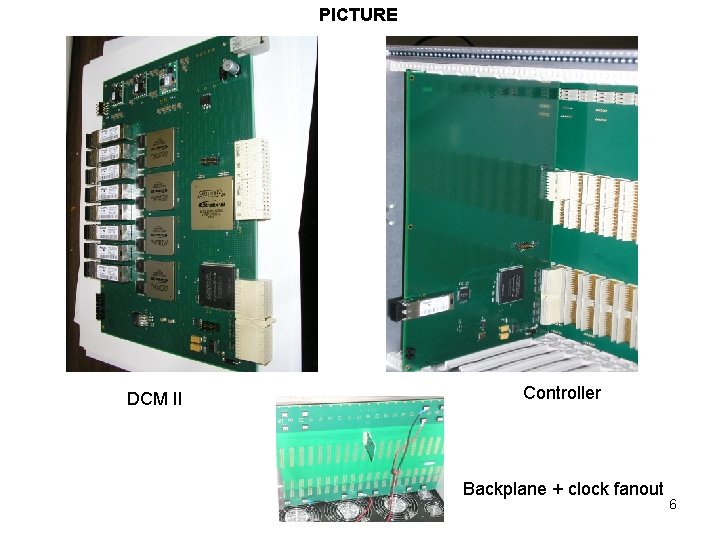

PICTURE DCM II Controller Backplane + clock fanout 6

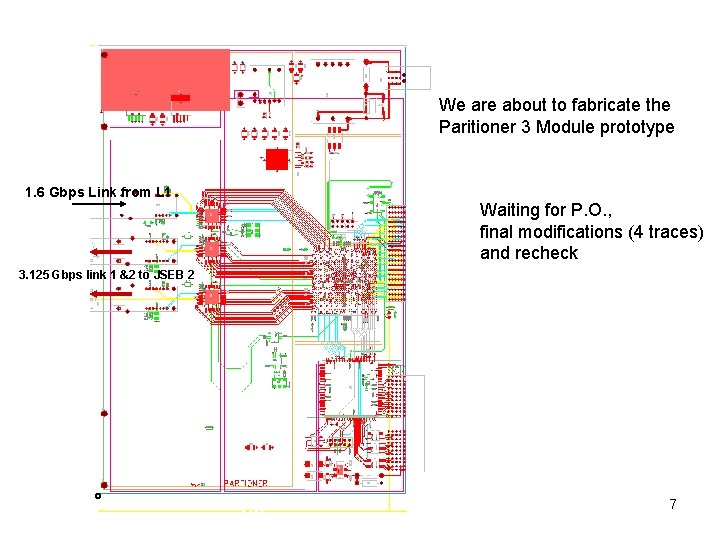

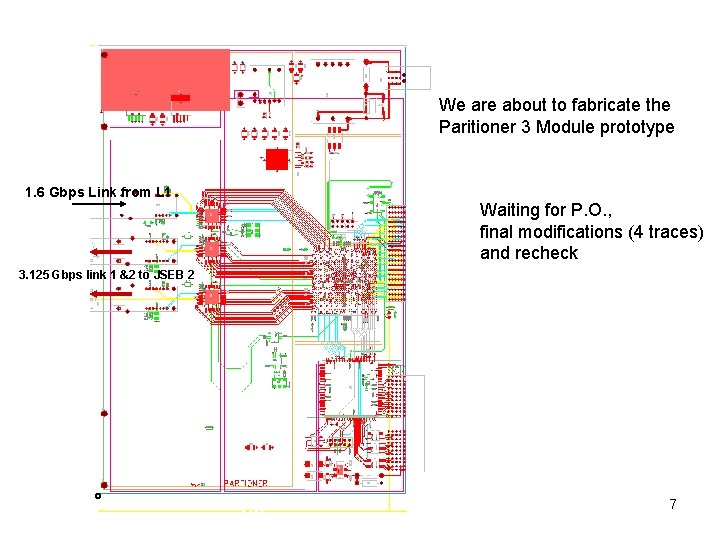

We are about to fabricate the Paritioner 3 Module prototype 1. 6 Gbps Link from L 1 Waiting for P. O. , final modifications (4 traces) and recheck 3. 125 Gbps link 1 &2 to JSEB 2 7

DCM 2 status • We are able to boot the FPGA on DCM 2 – Power up boards – Controller is fine. . – Able to download/loopback on the downloaded code – Start to test optical inputs. 8

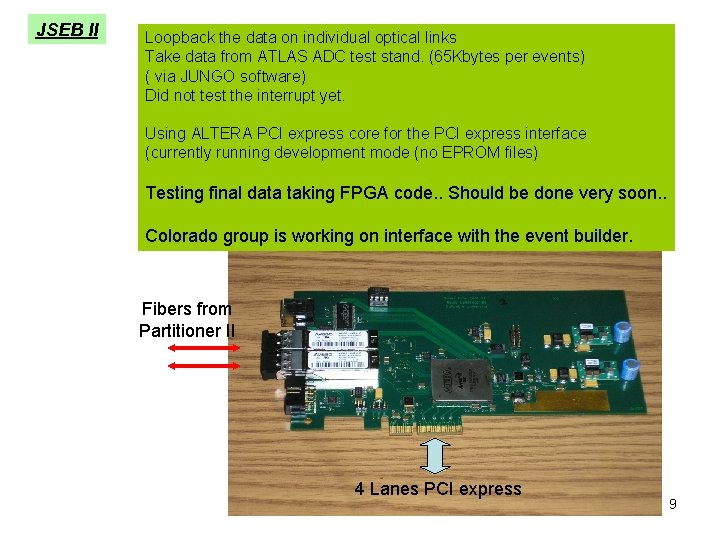

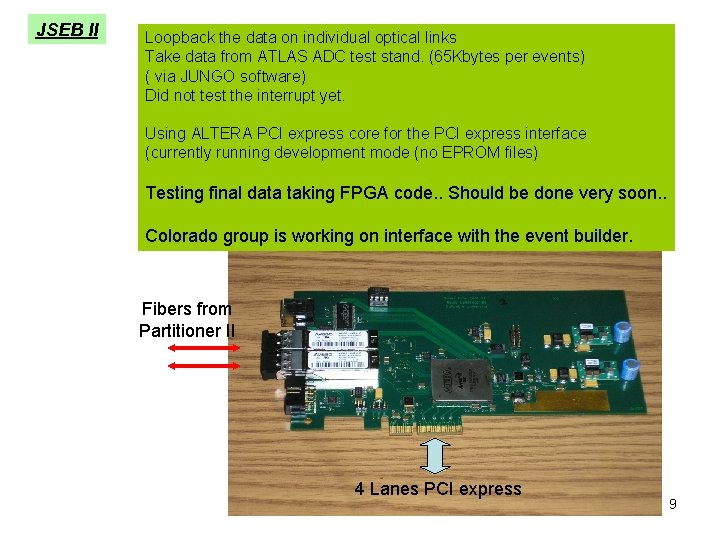

JSEB II Loopback the data on individual optical links Take data from ATLAS ADC test stand. (65 Kbytes per events) ( via JUNGO software) Did not test the interrupt yet. Using ALTERA PCI express core for the PCI express interface (currently running development mode (no EPROM files) Testing final data taking FPGA code. . Should be done very soon. . Colorado group is working on interface with the event builder. Fibers from Partitioner II 4 Lanes PCI express 9

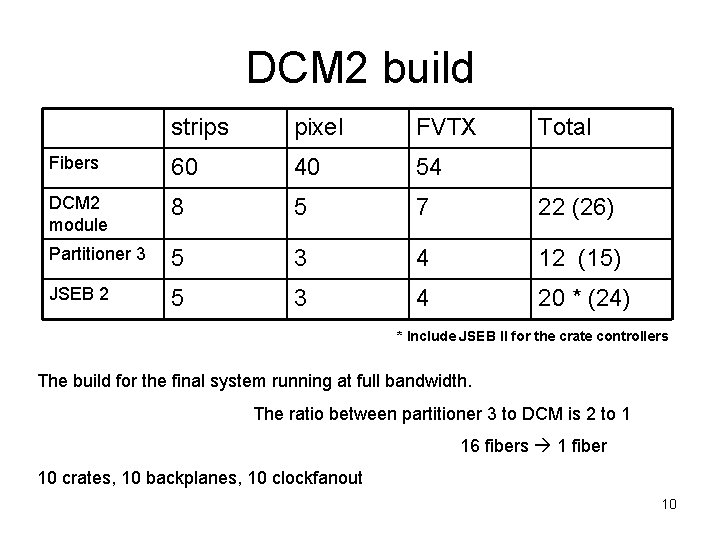

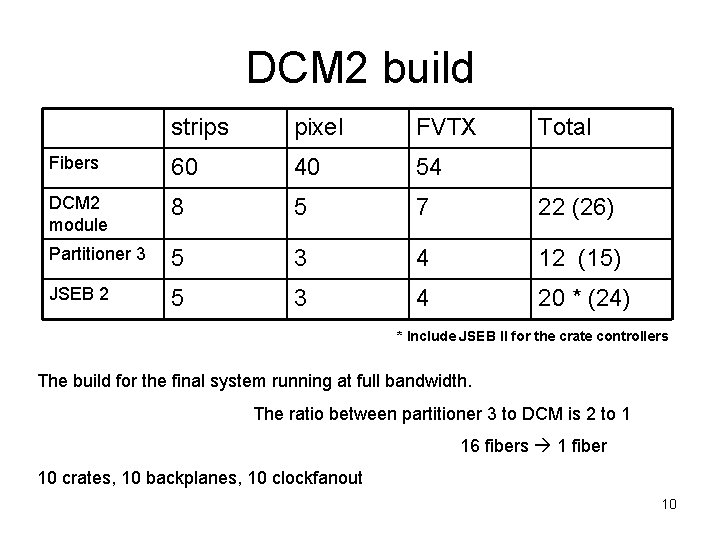

DCM 2 build strips pixel FVTX Total Fibers 60 40 54 DCM 2 module 8 5 7 22 (26) Partitioner 3 5 3 4 12 (15) JSEB 2 5 3 4 20 * (24) * Include JSEB II for the crate controllers The build for the final system running at full bandwidth. The ratio between partitioner 3 to DCM is 2 to 1 16 fibers 1 fiber 10 crates, 10 backplanes, 10 clockfanout 10

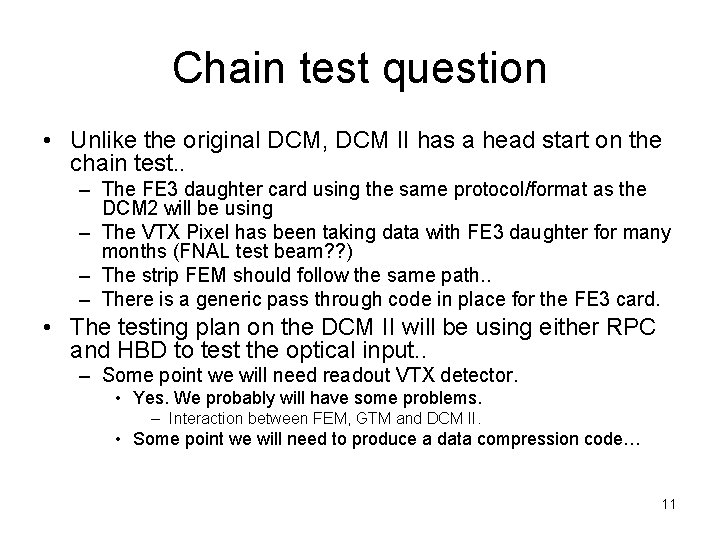

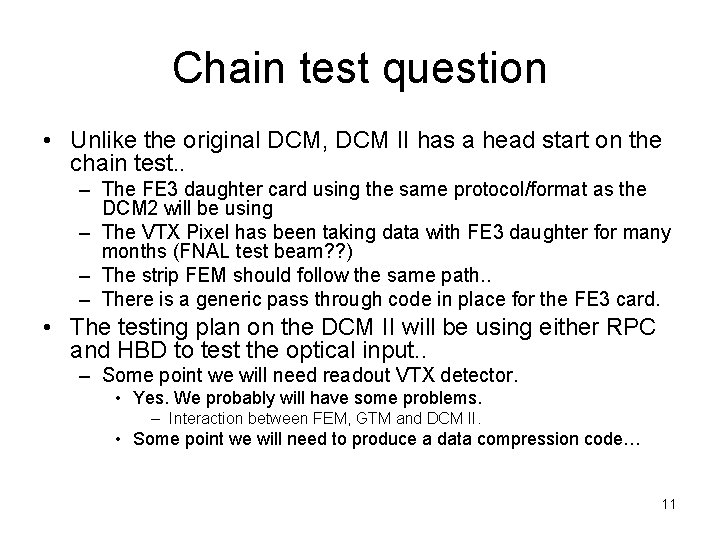

Chain test question • Unlike the original DCM, DCM II has a head start on the chain test. . – The FE 3 daughter card using the same protocol/format as the DCM 2 will be using – The VTX Pixel has been taking data with FE 3 daughter for many months (FNAL test beam? ? ) – The strip FEM should follow the same path. . – There is a generic pass through code in place for the FE 3 card. • The testing plan on the DCM II will be using either RPC and HBD to test the optical input. . – Some point we will need readout VTX detector. • Yes. We probably will have some problems. – Interaction between FEM, GTM and DCM II. • Some point we will need to produce a data compression code… 11

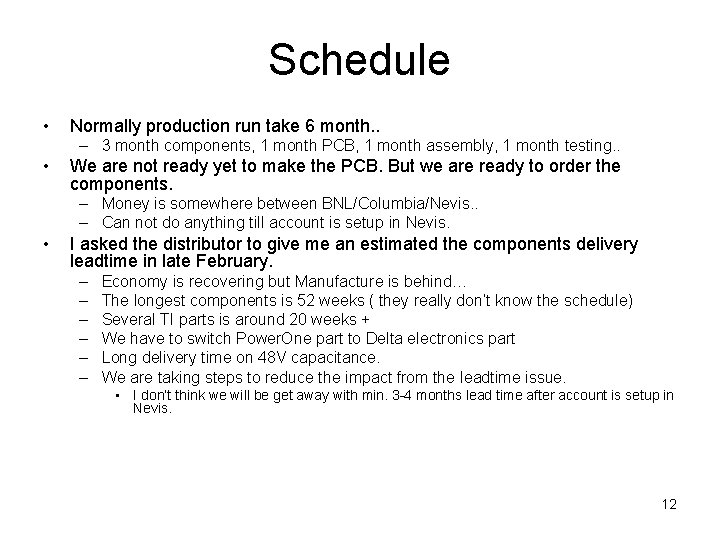

Schedule • Normally production run take 6 month. . – 3 month components, 1 month PCB, 1 month assembly, 1 month testing. . • We are not ready yet to make the PCB. But we are ready to order the components. – Money is somewhere between BNL/Columbia/Nevis. . – Can not do anything till account is setup in Nevis. • I asked the distributor to give me an estimated the components delivery leadtime in late February. – – – Economy is recovering but Manufacture is behind… The longest components is 52 weeks ( they really don’t know the schedule) Several TI parts is around 20 weeks + We have to switch Power. One part to Delta electronics part Long delivery time on 48 V capacitance. We are taking steps to reduce the impact from the leadtime issue. • I don’t think we will be get away with min. 3 -4 months lead time after account is setup in Nevis. 12