CSCE 430830 Course Project Guidelines By Dongyuan Zhan

CSCE 430/830 Course Project Guidelines By Dongyuan Zhan dzhan@cse. unl. edu Feb. 4, 2010

Objectives • The project is designed to help you reinforce your understanding of RISC ISA and pipeline architectures • Learn to do HW/SW co-design, which involves the implementation of both the processor and assembler • Develop the skill to finish a complex FPGA design with the DE-2 board • Practice team work and make your project a splendid one 2/20/2021 CSCE 430/830 Course Project Guidelines 2

The Project Tasks • System design and implementation – – – system schematic design component design and functional verification pipelining design and functional verification assembler design (c/c++, java, perl, python…. ) benchmark program design (in assembly language) • Project documentation maintained about – – – the people in your team meeting log with substantial details design documentation special features of your design the final result (e. g. correctness, performance, future work) • Final project demo, presentation and report 2/20/2021 CSCE 430/830 Course Project Guidelines 3

The Project Teams • 3 -4 members per team • It is better to have a team leader for each group (schedule meetings and coordinate collaboration) • Each team needs to maintain a website for the project documentation – it might be a good idea to create a project wiki at http: //csce. unl. edu/wiki/index. php/Main_Page) 2/20/2021 CSCE 430/830 Course Project Guidelines 4

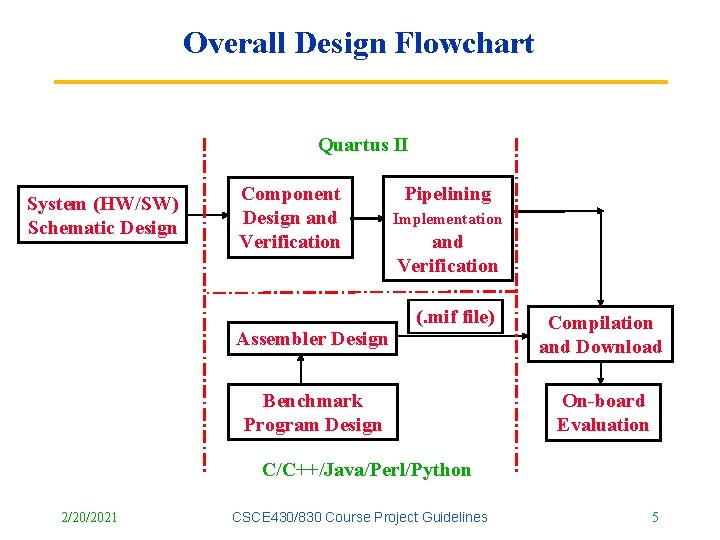

Overall Design Flowchart Quartus II System (HW/SW) Schematic Design Component Design and Verification Assembler Design Pipelining Implementation and Verification (. mif file) Benchmark Program Design Compilation and Download On-board Evaluation C/C++/Java/Perl/Python 2/20/2021 CSCE 430/830 Course Project Guidelines 5

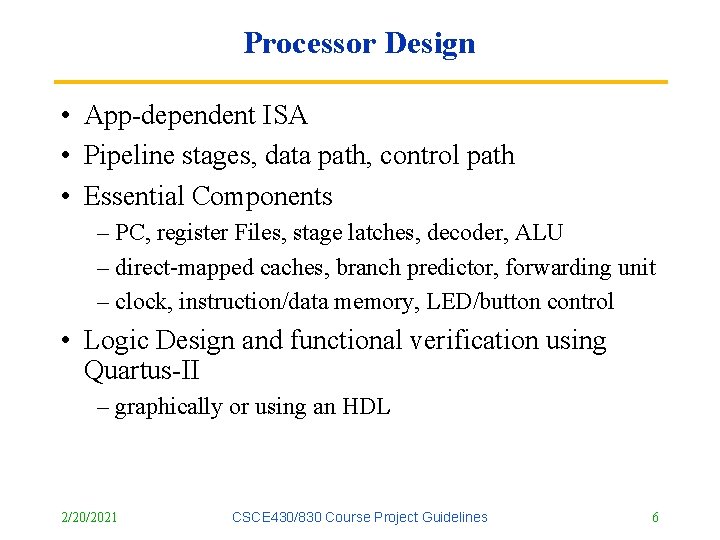

Processor Design • App-dependent ISA • Pipeline stages, data path, control path • Essential Components – PC, register Files, stage latches, decoder, ALU – direct-mapped caches, branch predictor, forwarding unit – clock, instruction/data memory, LED/button control • Logic Design and functional verification using Quartus-II – graphically or using an HDL 2/20/2021 CSCE 430/830 Course Project Guidelines 6

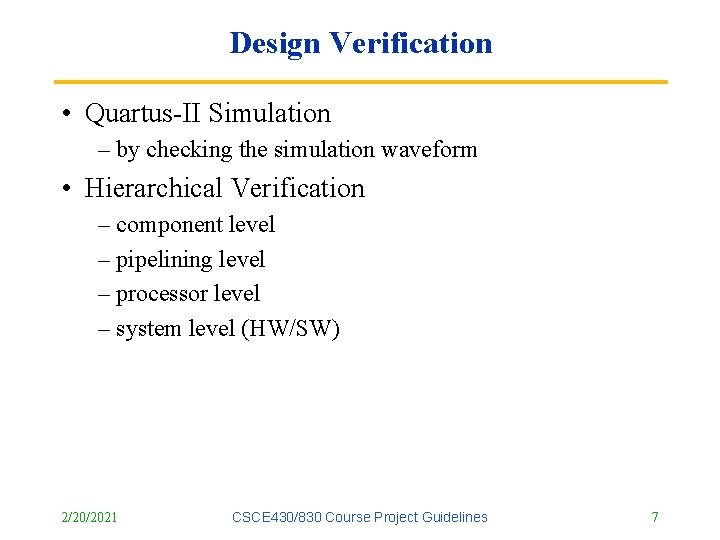

Design Verification • Quartus-II Simulation – by checking the simulation waveform • Hierarchical Verification – component level – pipelining level – processor level – system level (HW/SW) 2/20/2021 CSCE 430/830 Course Project Guidelines 7

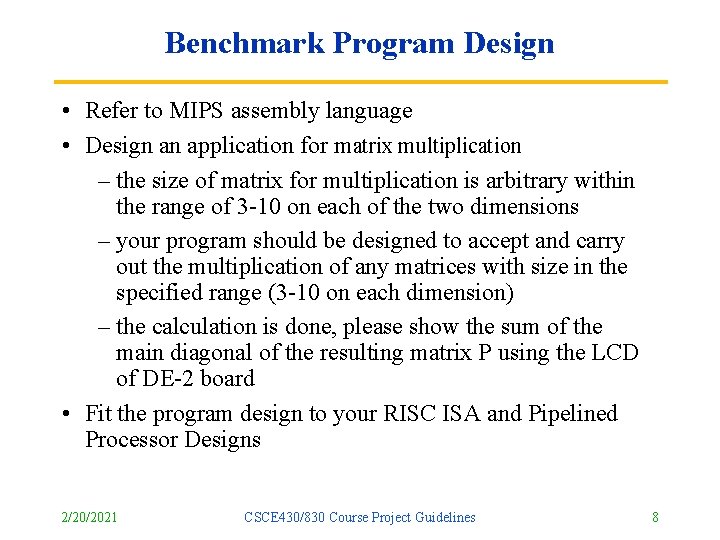

Benchmark Program Design • Refer to MIPS assembly language • Design an application for matrix multiplication – the size of matrix for multiplication is arbitrary within the range of 3 -10 on each of the two dimensions – your program should be designed to accept and carry out the multiplication of any matrices with size in the specified range (3 -10 on each dimension) – the calculation is done, please show the sum of the main diagonal of the resulting matrix P using the LCD of DE-2 board • Fit the program design to your RISC ISA and Pipelined Processor Designs 2/20/2021 CSCE 430/830 Course Project Guidelines 8

Assembler Design • Choose A High-level Language – • Java, C, C++, Perl, Python Design Steps – – – 2/20/2021 identify and resolve symbols and hazards convert application program to machine code (according to your ISA design) follow the Memory Initialization Format (MIF) specified for Altera devices CSCE 430/830 Course Project Guidelines 9

Download, Debugging and Evaluation • Experiment Tools – Altera DE-1 with Cyclone-II FPGA – Quartus II Web Edition • Pin Assignment – define the connects between the FPGA and external SDRAM/FLASH/LCD/Pushbuttons • Design Download – use the USB Blaster cable to connect DE-1 and your computer • On Board Debugging and Evaluation – report the correctness, efficiency, overhead and future work 2/20/2021 CSCE 430/830 Course Project Guidelines 10

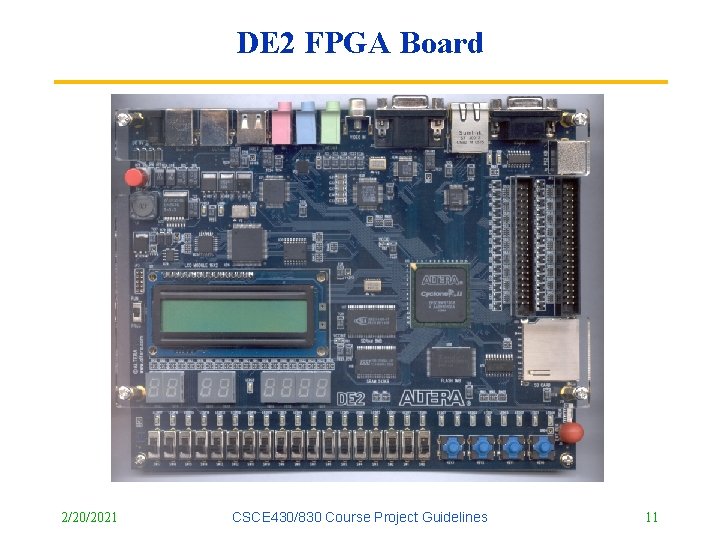

DE 2 FPGA Board 2/20/2021 CSCE 430/830 Course Project Guidelines 11

Extra Credits • Special Features Entitling Teams to Extra Credits – Here are some of my suggestions » Upgrade your cache design to a set-associative cache » Upgrade your branch predictor to a 2 -bit FSM scheme » Enhance your pipelined processor with out-of-order execution capabilities (very challenging) » Upgrade your processor to have two cores and split your matrix multiplication benchmark into two parallel parts that are calculated by each core respectively (very challenging) – You can propose any ideas to TA that you think can make your project feature special merits during the system schematic design stage. – If your proposal is approved by TA and finally implemented by your team, you will be honored with extra credits 2/20/2021 CSCE 430/830 Course Project Guidelines 12

Important Milestones • • • Group Formation (by Feb. 4) System Schematic Design (by Feb. 23) Design & Verification of Major Components (by Oct. 27) Design & Implementation of the Assembler (by Mar. 23) Project Demo (Apr. 27 – May 1) Project Presentation (During the final week) 2/20/2021 CSCE 430/830 Course Project Guidelines 13

References • For more details, please refer to – http: //cse. unl. edu/~jiang/cse 430/Project/Description_S 2010. html 2/20/2021 CSCE 430/830 Course Project Guidelines 14

- Slides: 14