CSCE 430830 Computer Architecture MIPS Case Study of

- Slides: 35

CSCE 430/830 Computer Architecture MIPS: Case Study of Instruction Set Architecture Instructor: Hong Jiang Courtesy of Prof. Yifeng Zhu @ U. of Maine Fall, 2006 CSCE 430/830 Portions of these slides are derived from: Dave Patterson © UCB ISA-2

Outline - Instruction Sets • Instruction Set Overview • MIPS Instruction Set – Overview – Registers and Memory – MIPS Instructions CSCE 430/830 ISA-2

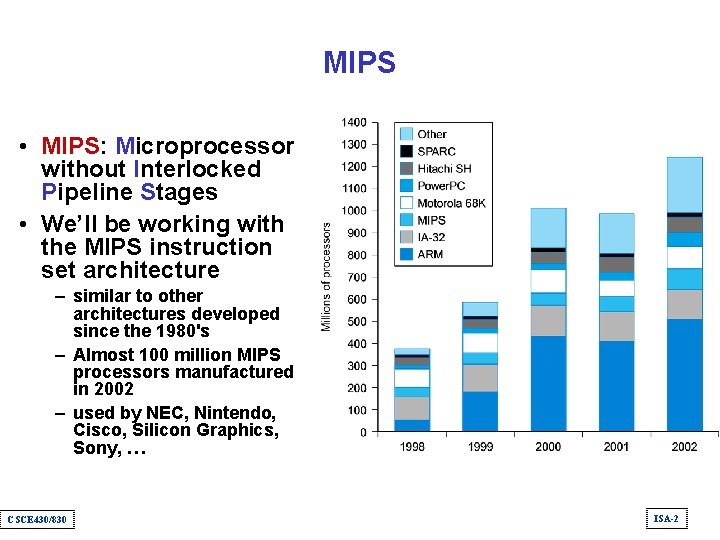

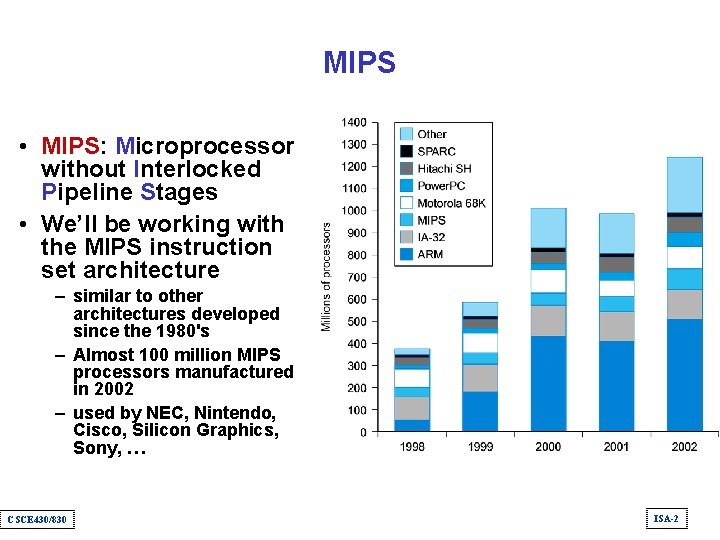

MIPS • MIPS: Microprocessor without Interlocked Pipeline Stages • We’ll be working with the MIPS instruction set architecture – similar to other architectures developed since the 1980's – Almost 100 million MIPS processors manufactured in 2002 – used by NEC, Nintendo, Cisco, Silicon Graphics, Sony, … CSCE 430/830 ISA-2

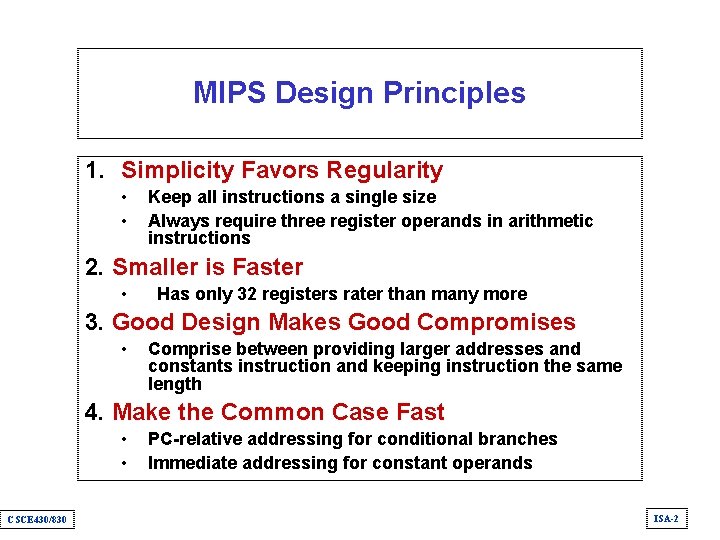

MIPS Design Principles 1. Simplicity Favors Regularity • • Keep all instructions a single size Always require three register operands in arithmetic instructions 2. Smaller is Faster • Has only 32 registers rater than many more 3. Good Design Makes Good Compromises • Comprise between providing larger addresses and constants instruction and keeping instruction the same length 4. Make the Common Case Fast • • CSCE 430/830 PC-relative addressing for conditional branches Immediate addressing for constant operands ISA-2

Outline - Instruction Sets • Instruction Set Overview • MIPS Instruction Set – Overview – Registers and Memory – MIPS Instructions CSCE 430/830 ISA-2

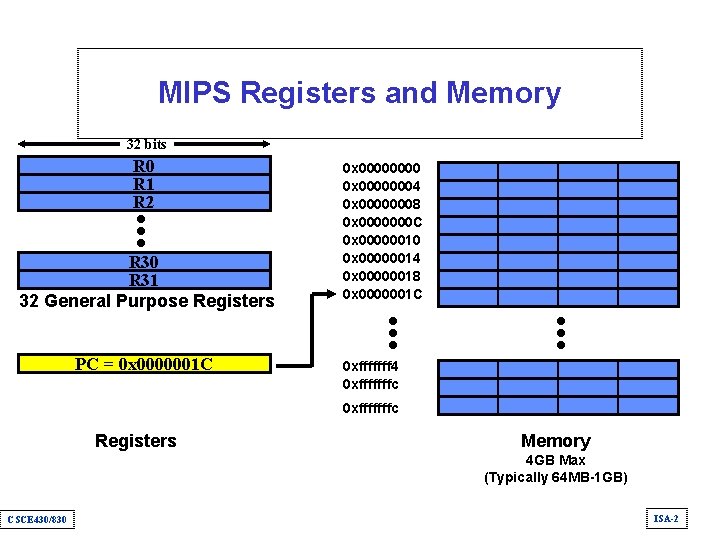

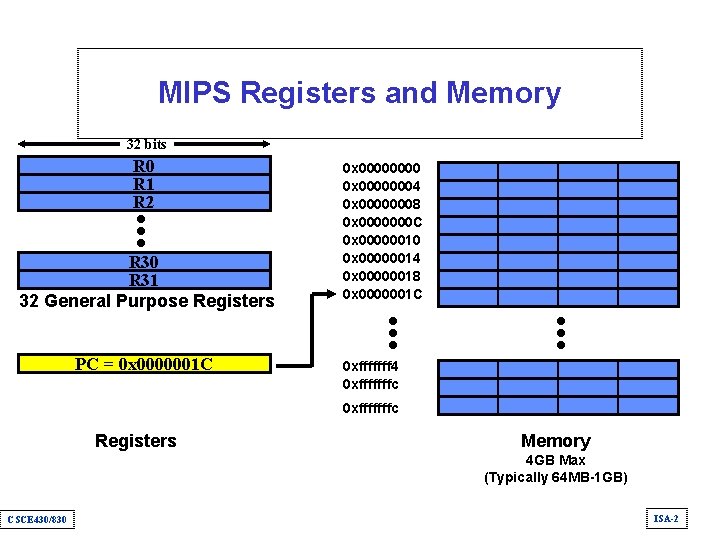

MIPS Registers and Memory 32 bits R 0 R 1 R 2 R 30 R 31 32 General Purpose Registers PC = 0 x 0000001 C 0 x 00000004 0 x 00000008 0 x 0000000 C 0 x 00000010 0 x 00000014 0 x 00000018 0 x 0000001 C 0 xfffffff 4 0 xfffffffc Registers Memory 4 GB Max (Typically 64 MB-1 GB) CSCE 430/830 ISA-2

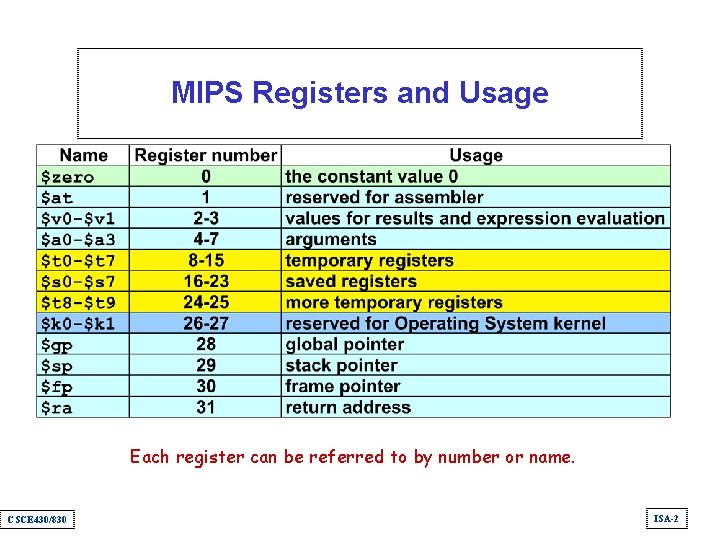

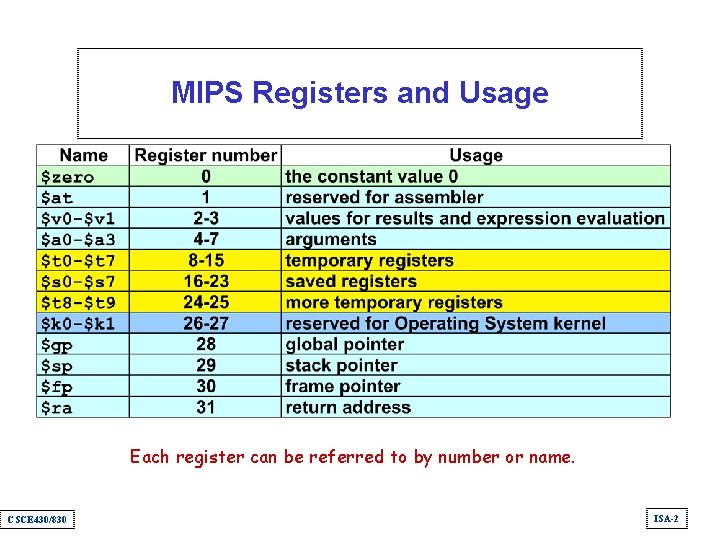

MIPS Registers and Usage Each register can be referred to by number or name. CSCE 430/830 ISA-2

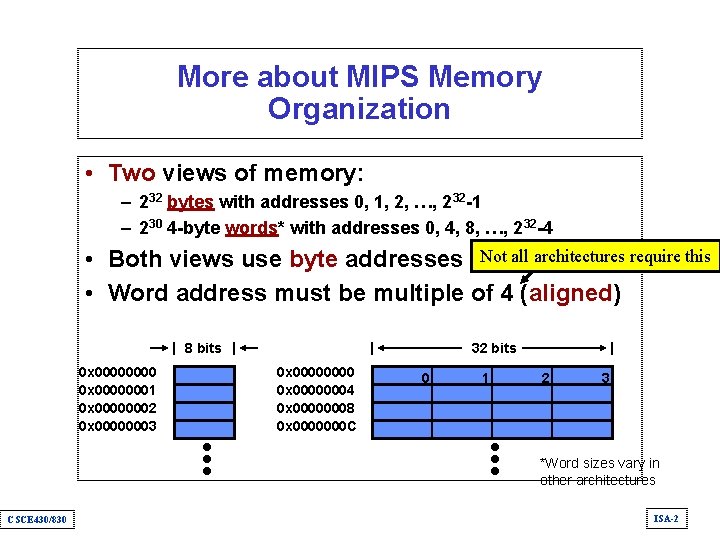

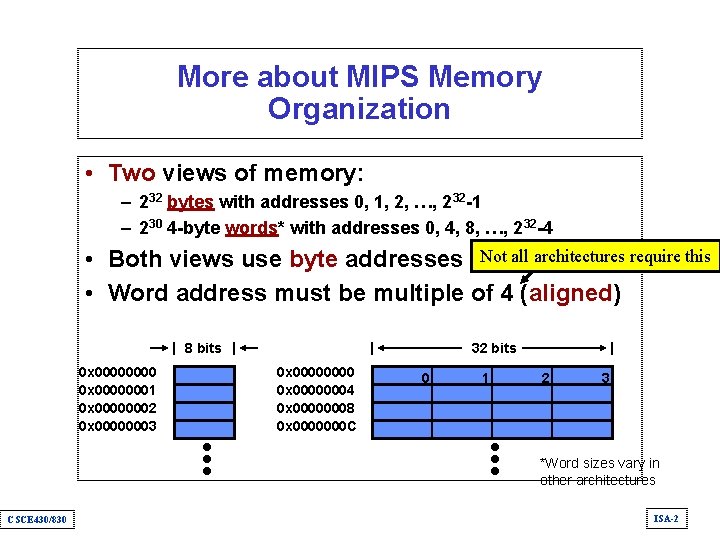

More about MIPS Memory Organization • Two views of memory: – 232 bytes with addresses 0, 1, 2, …, 232 -1 – 230 4 -byte words* with addresses 0, 4, 8, …, 232 -4 • Both views use byte addresses Not all architectures require this • Word address must be multiple of 4 (aligned) 8 bits 0 x 00000001 0 x 00000002 0 x 00000003 32 bits 0 x 00000004 0 x 00000008 0 x 0000000 C 0 1 2 3 *Word sizes vary in other architectures CSCE 430/830 ISA-2

Outline - Instruction Sets • Instruction Set Overview • MIPS Instruction Set – Overview – Registers and Memory – MIPS Instructions • Summary CSCE 430/830 ISA-2

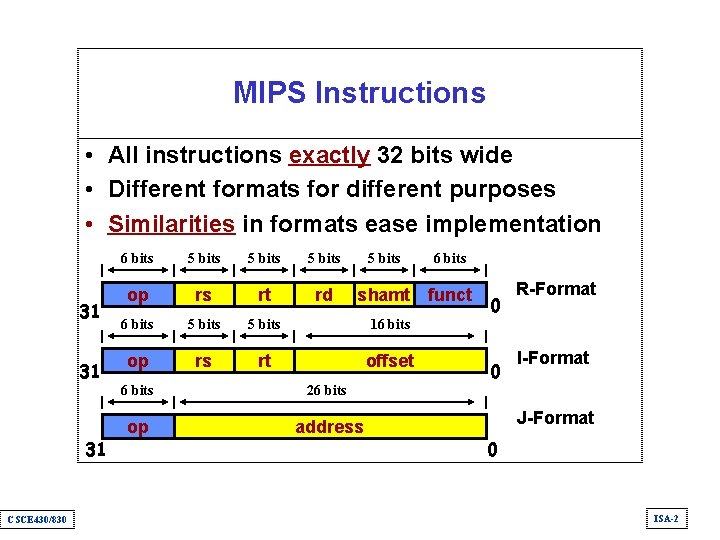

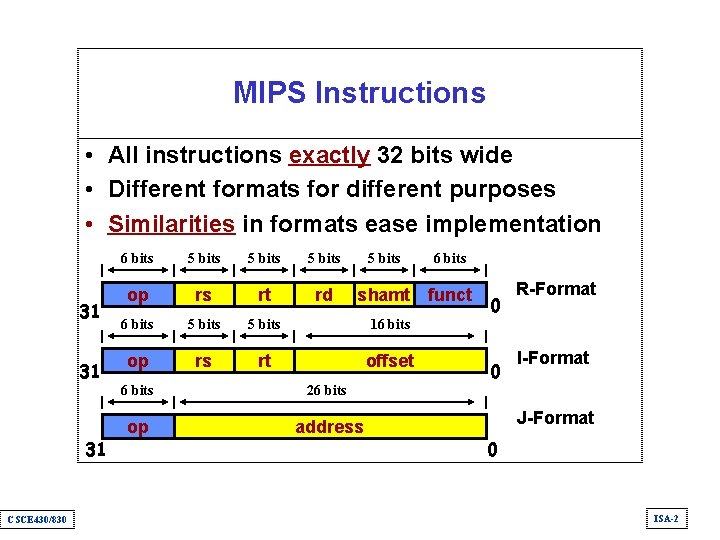

MIPS Instructions • All instructions exactly 32 bits wide • Different formats for different purposes • Similarities in formats ease implementation 31 31 31 CSCE 430/830 6 bits 5 bits op rs rt rd 6 bits 5 bits 16 bits op rs rt offset 6 bits shamt funct 6 bits 26 bits op address 0 0 R-Format I-Format J-Format 0 ISA-2

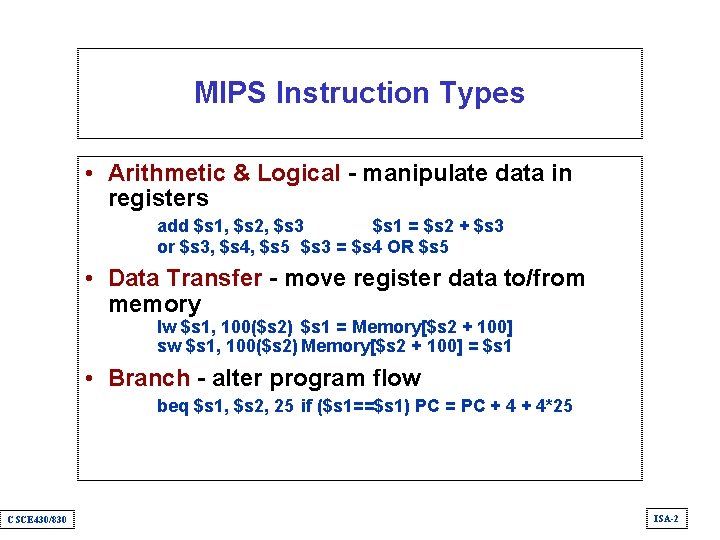

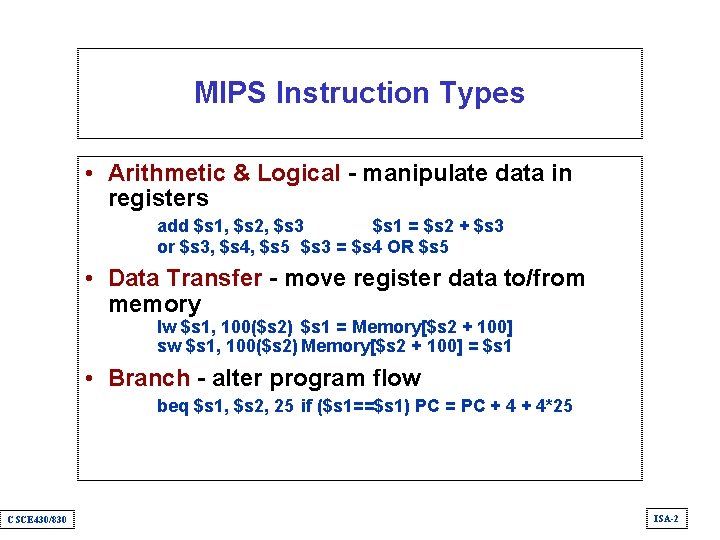

MIPS Instruction Types • Arithmetic & Logical - manipulate data in registers add $s 1, $s 2, $s 3 $s 1 = $s 2 + $s 3 or $s 3, $s 4, $s 5 $s 3 = $s 4 OR $s 5 • Data Transfer - move register data to/from memory lw $s 1, 100($s 2) $s 1 = Memory[$s 2 + 100] sw $s 1, 100($s 2) Memory[$s 2 + 100] = $s 1 • Branch - alter program flow beq $s 1, $s 2, 25 if ($s 1==$s 1) PC = PC + 4*25 CSCE 430/830 ISA-2

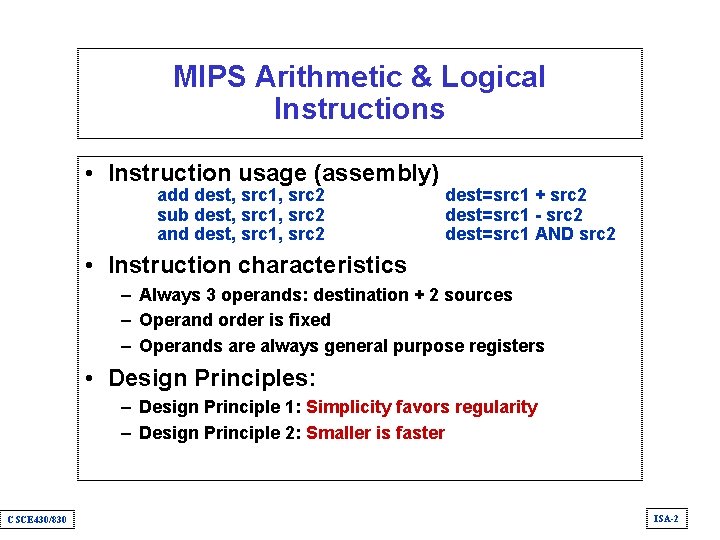

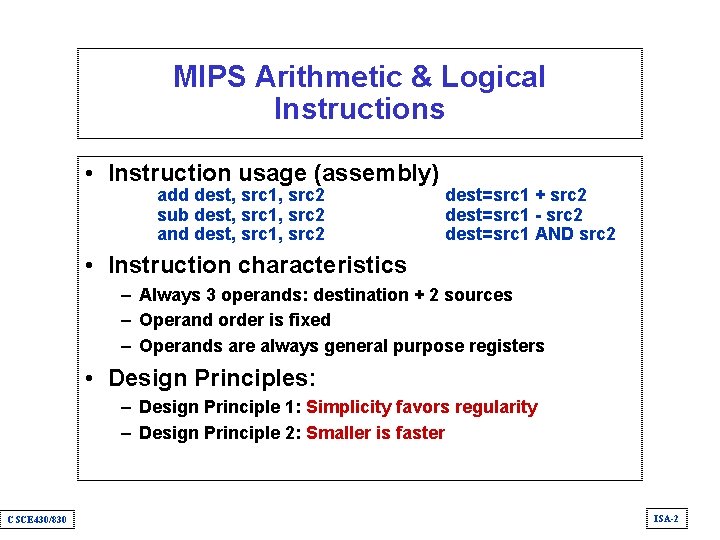

MIPS Arithmetic & Logical Instructions • Instruction usage (assembly) add dest, src 1, src 2 sub dest, src 1, src 2 and dest, src 1, src 2 dest=src 1 + src 2 dest=src 1 - src 2 dest=src 1 AND src 2 • Instruction characteristics – Always 3 operands: destination + 2 sources – Operand order is fixed – Operands are always general purpose registers • Design Principles: – Design Principle 1: Simplicity favors regularity – Design Principle 2: Smaller is faster CSCE 430/830 ISA-2

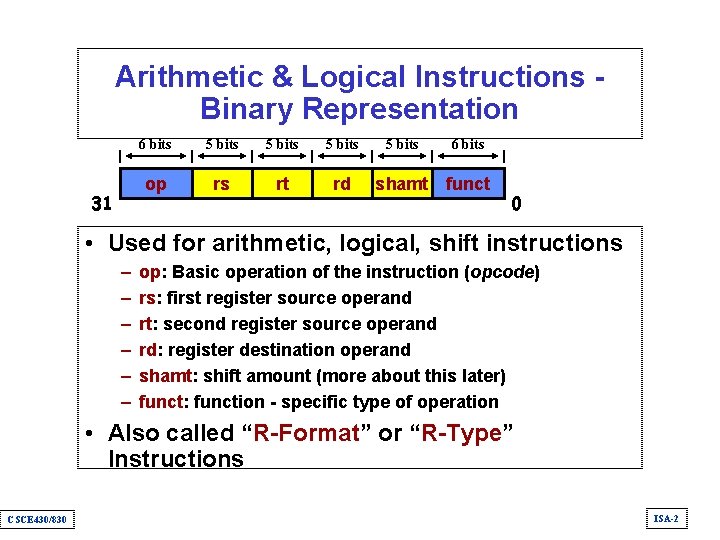

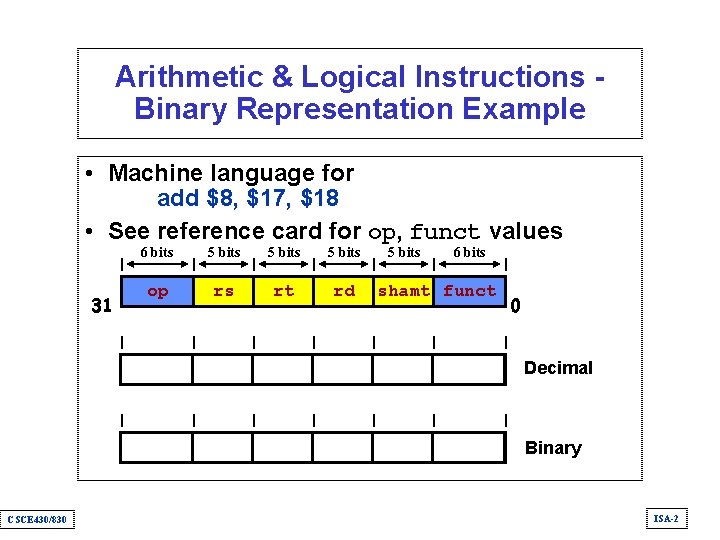

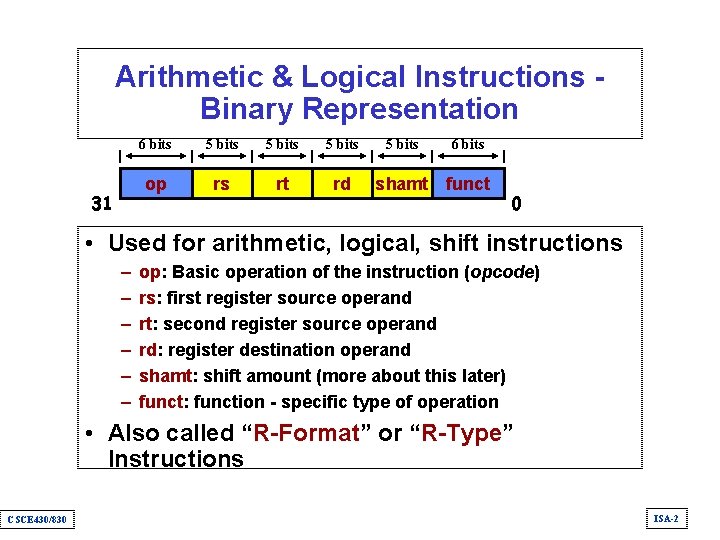

Arithmetic & Logical Instructions Binary Representation 31 6 bits 5 bits op rs rt rd 5 bits 6 bits shamt funct 0 • Used for arithmetic, logical, shift instructions – – – op: Basic operation of the instruction (opcode) rs: first register source operand rt: second register source operand rd: register destination operand shamt: shift amount (more about this later) funct: function - specific type of operation • Also called “R-Format” or “R-Type” Instructions CSCE 430/830 ISA-2

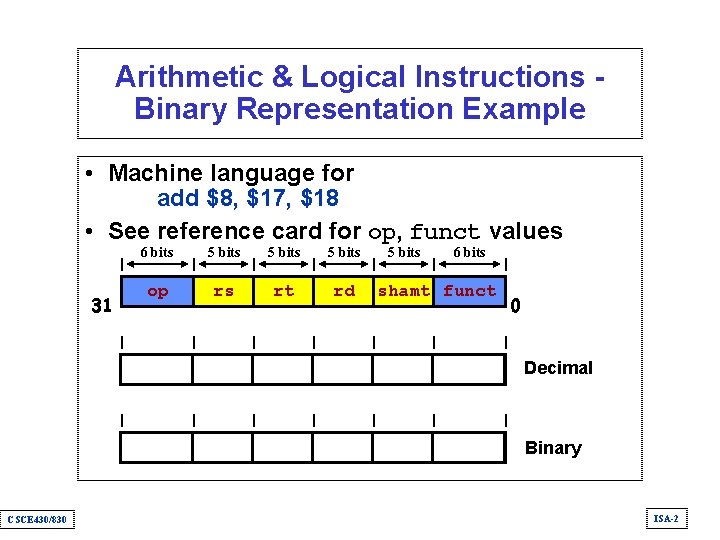

Arithmetic & Logical Instructions Binary Representation Example • Machine language for add $8, $17, $18 • See reference card for op, funct values 31 6 bits 5 bits op rs rt rd 0 17 18 8 5 bits 6 bits shamt funct 0 32 000000 10001 10010 01000 00000 100000 CSCE 430/830 0 Decimal Binary ISA-2

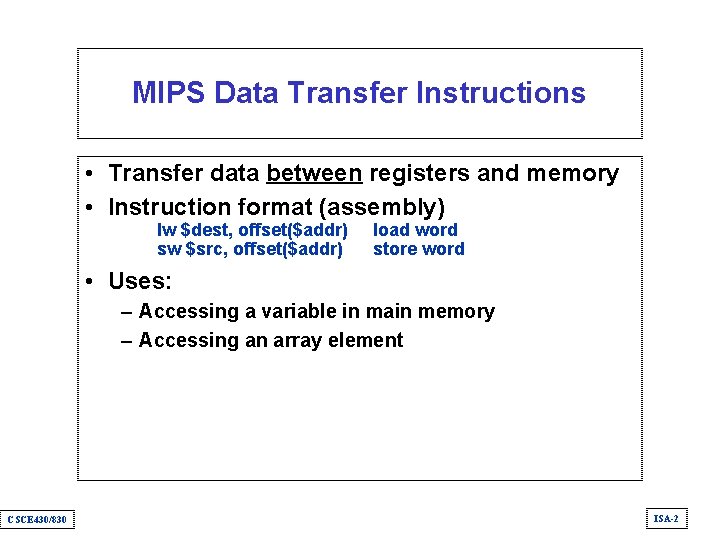

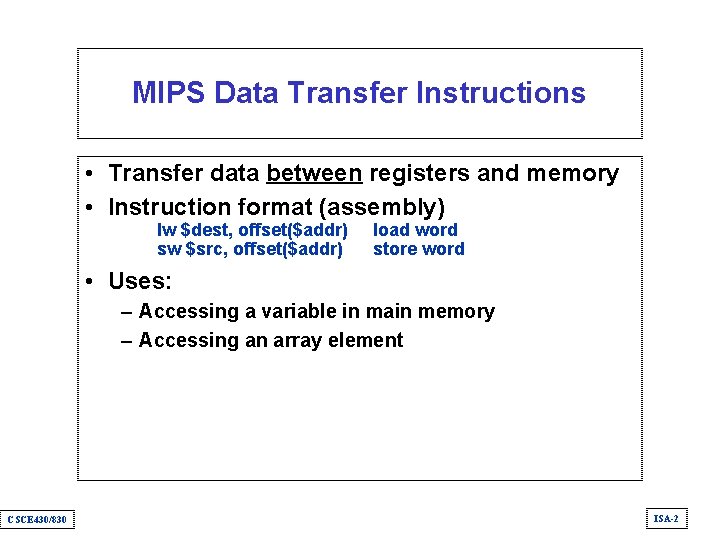

MIPS Data Transfer Instructions • Transfer data between registers and memory • Instruction format (assembly) lw $dest, offset($addr) sw $src, offset($addr) load word store word • Uses: – Accessing a variable in main memory – Accessing an array element CSCE 430/830 ISA-2

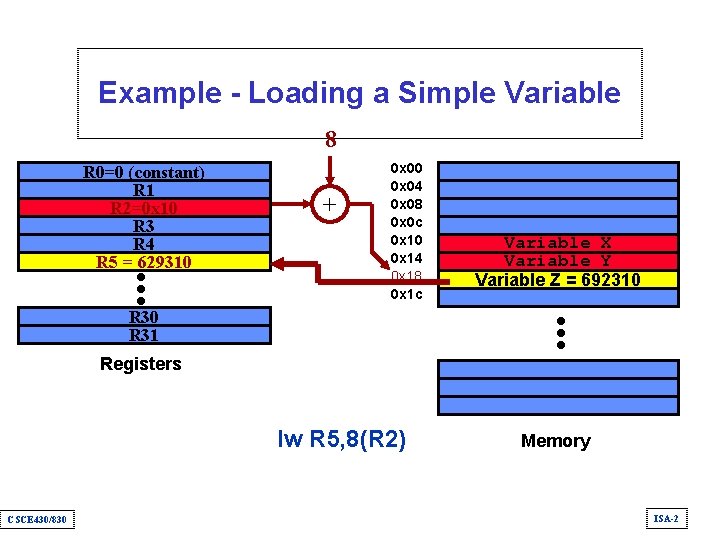

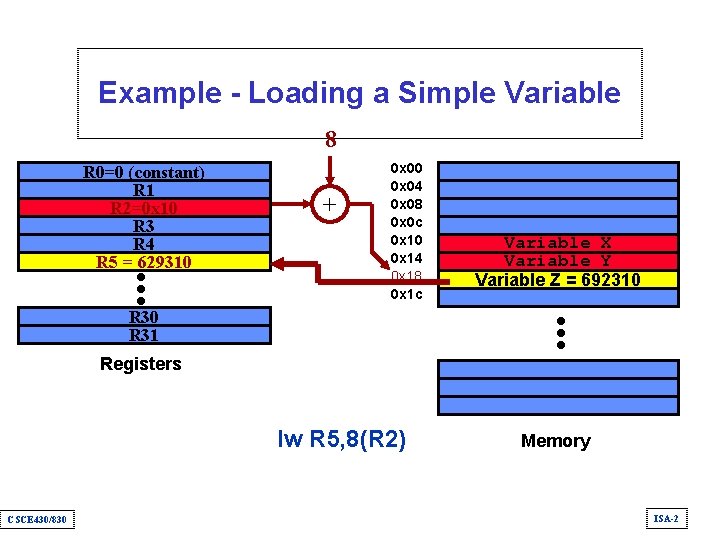

Example - Loading a Simple Variable 8 R 0=0 (constant) R 1 R 2=0 x 10 R 3 R 4 R 5 =R 5 629310 + 0 x 00 0 x 04 0 x 08 0 x 0 c 0 x 10 0 x 14 0 x 18 0 x 1 c Variable X Variable Y Variable Z = 692310 R 31 Registers lw R 5, 8(R 2) CSCE 430/830 Memory ISA-2

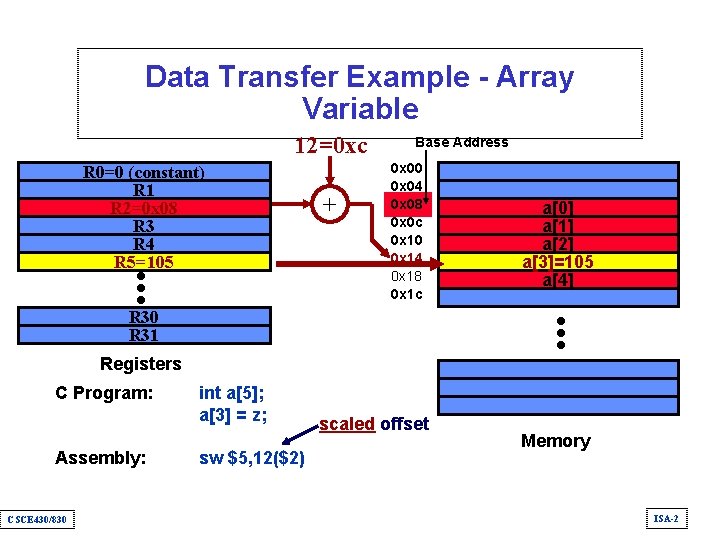

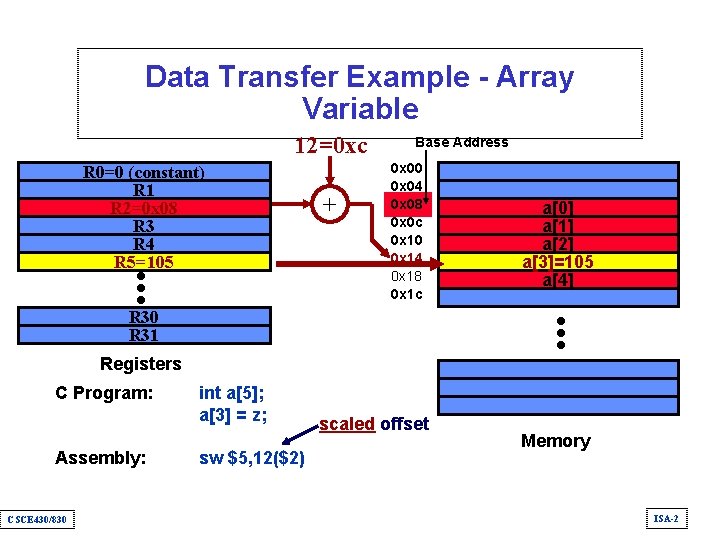

Data Transfer Example - Array Variable 12=0 xc R 0=0 (constant) R 1 R 2=0 x 08 R 3 R 4 R 5=105 + Base Address 0 x 00 0 x 04 0 x 08 0 x 0 c 0 x 10 0 x 14 0 x 18 0 x 1 c a[0] a[1] a[2] a[3]=105 a[3] a[4] R 30 R 31 Registers C Program: Assembly: CSCE 430/830 int a[5]; a[3] = z; sw $5, 12($2) scaled offset Memory ISA-2

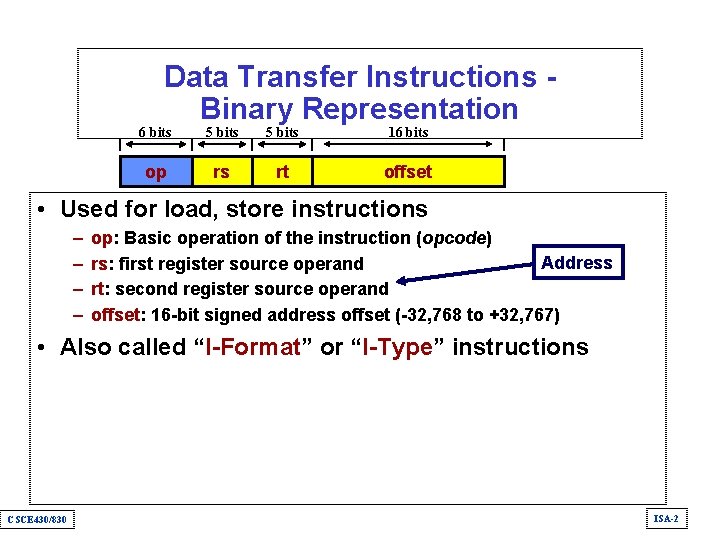

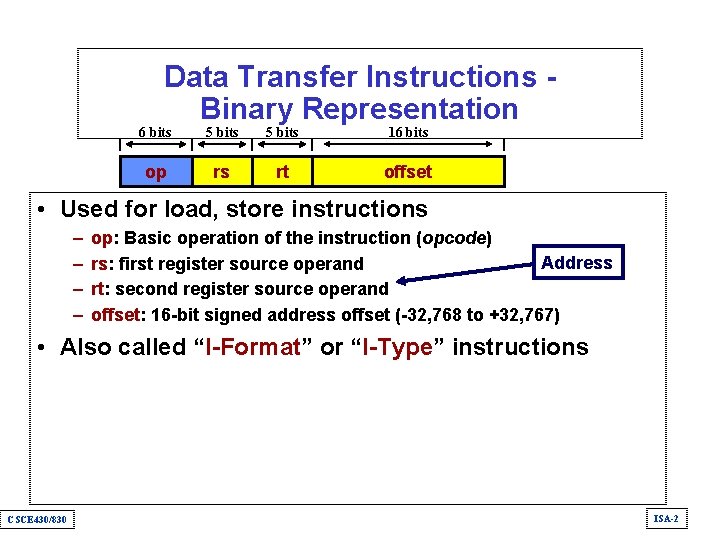

Data Transfer Instructions Binary Representation 6 bits 5 bits 16 bits op rs rt offset • Used for load, store instructions – – op: Basic operation of the instruction (opcode) Address rs: first register source operand rt: second register source operand offset: 16 -bit signed address offset (-32, 768 to +32, 767) • Also called “I-Format” or “I-Type” instructions CSCE 430/830 ISA-2

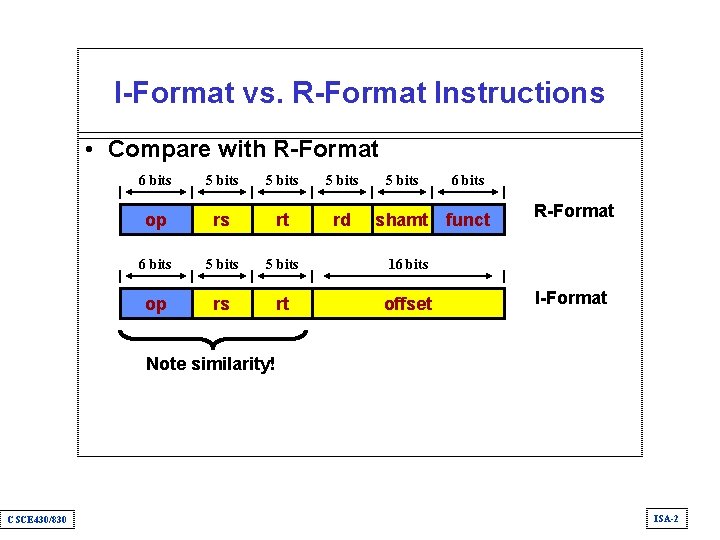

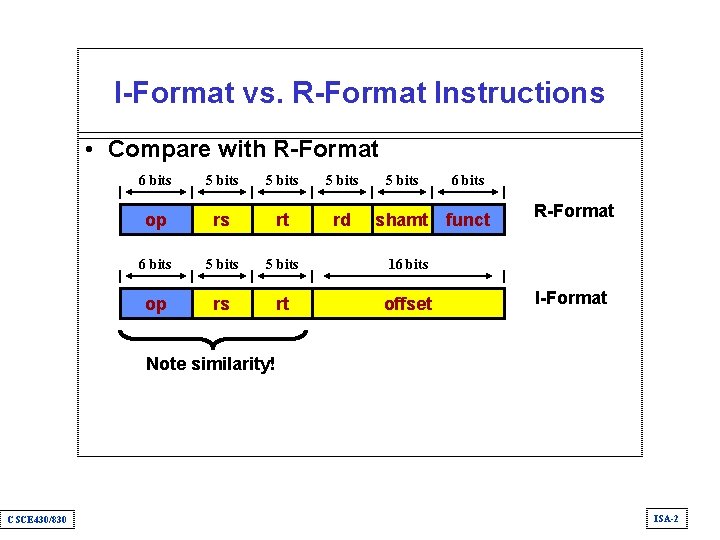

I-Format vs. R-Format Instructions • Compare with R-Format 6 bits 5 bits op rs rt rd 6 bits 5 bits 16 bits op rs rt offset 6 bits shamt funct R-Format I-Format Note similarity! CSCE 430/830 ISA-2

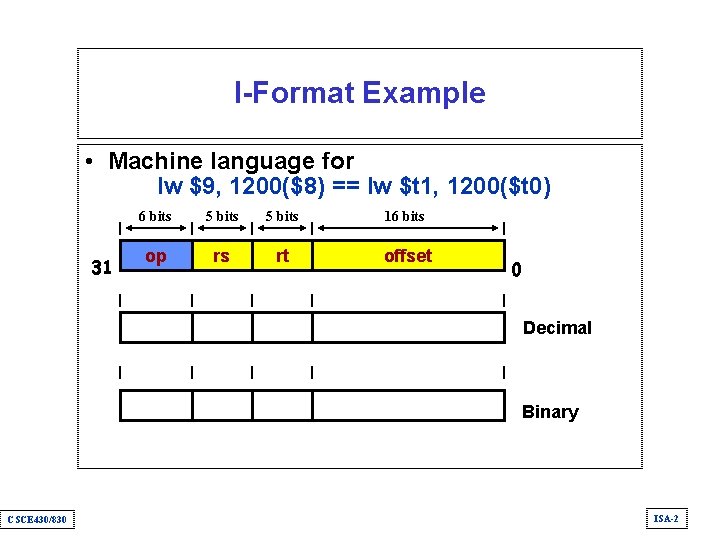

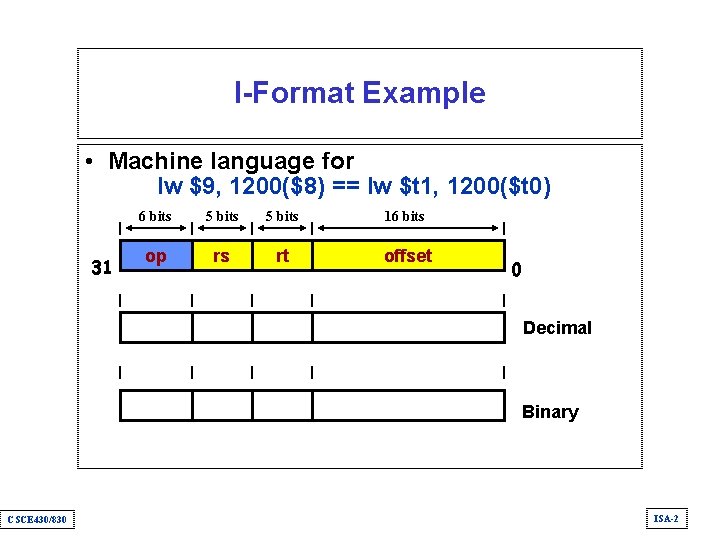

I-Format Example • Machine language for lw $9, 1200($8) == lw $t 1, 1200($t 0) 31 6 bits 5 bits 16 bits op rs rt offset 35 8 9 1200 100011 01000 01001 CSCE 430/830 0000010010110000 0 Decimal Binary ISA-2

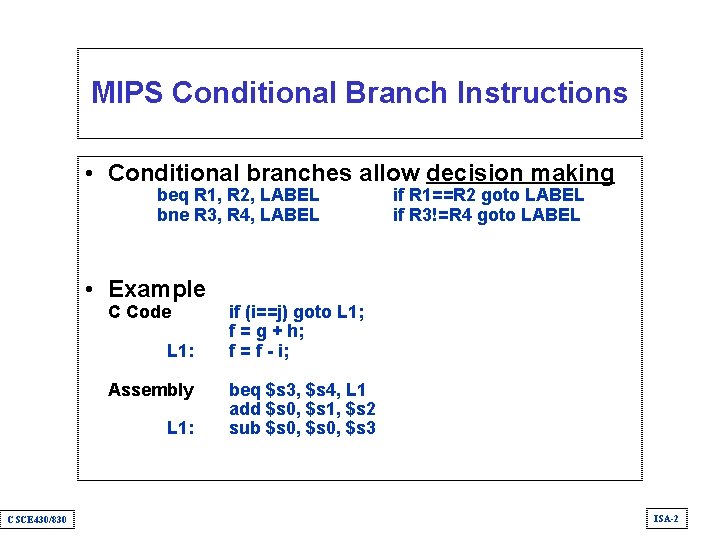

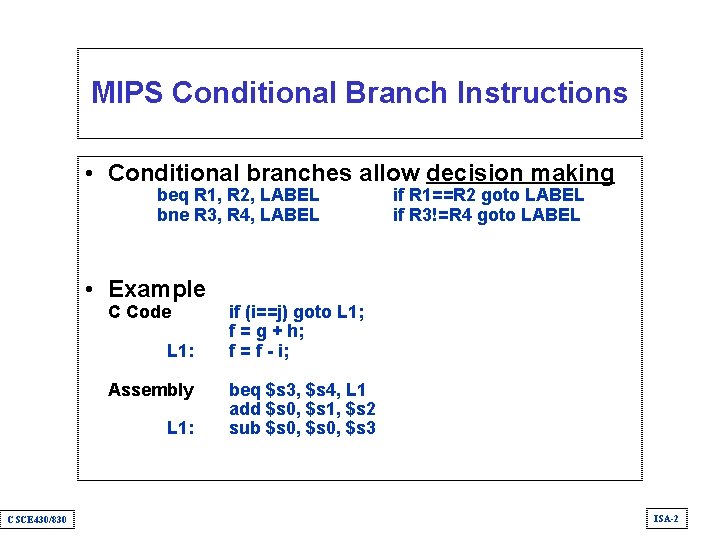

MIPS Conditional Branch Instructions • Conditional branches allow decision making beq R 1, R 2, LABEL bne R 3, R 4, LABEL • Example C Code L 1: Assembly L 1: CSCE 430/830 if R 1==R 2 goto LABEL if R 3!=R 4 goto LABEL if (i==j) goto L 1; f = g + h; f = f - i; beq $s 3, $s 4, L 1 add $s 0, $s 1, $s 2 sub $s 0, $s 3 ISA-2

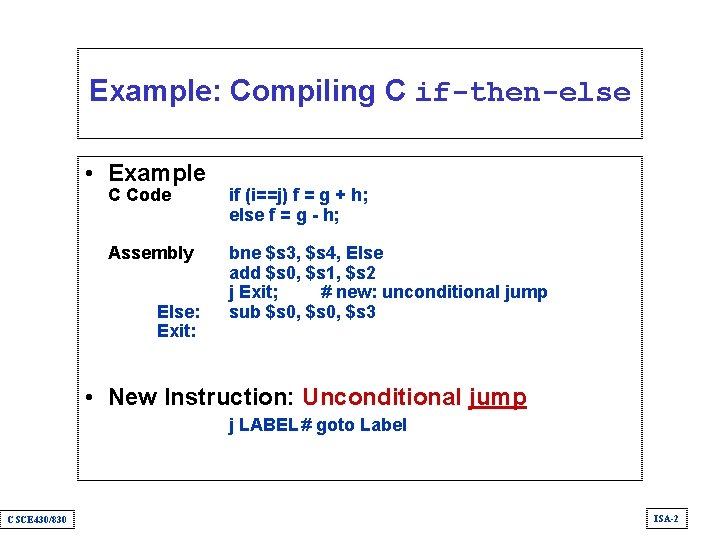

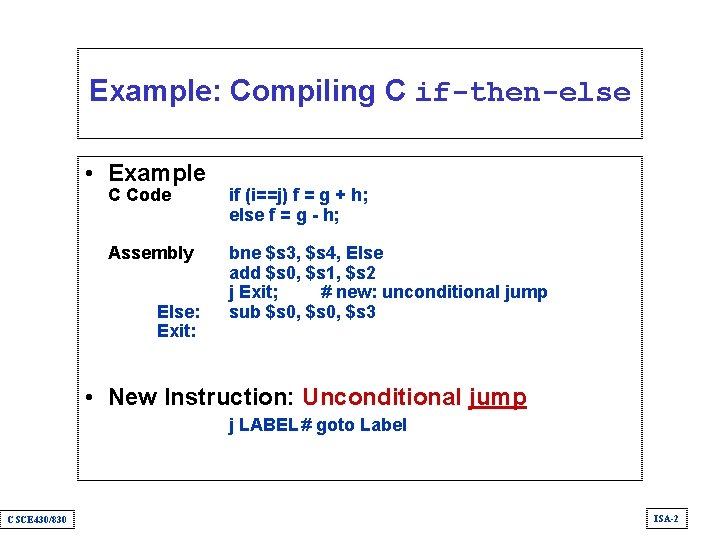

Example: Compiling C if-then-else • Example C Code if (i==j) f = g + h; else f = g - h; Assembly bne $s 3, $s 4, Else add $s 0, $s 1, $s 2 j Exit; # new: unconditional jump sub $s 0, $s 3 Else: Exit: • New Instruction: Unconditional jump j LABEL # goto Label CSCE 430/830 ISA-2

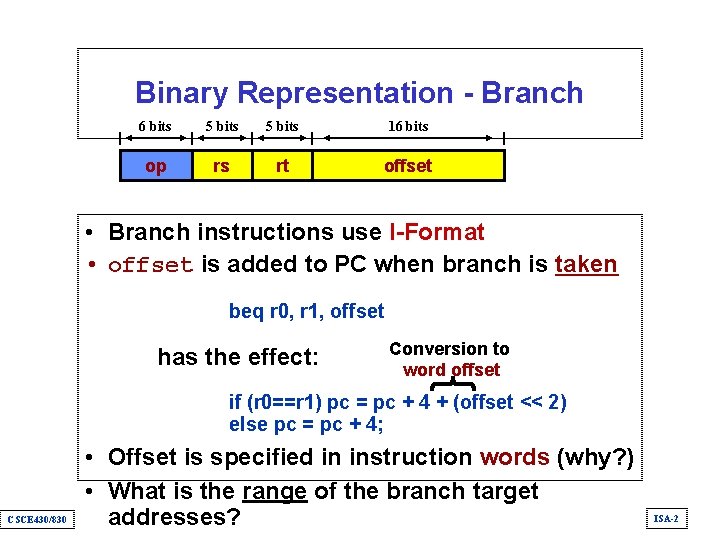

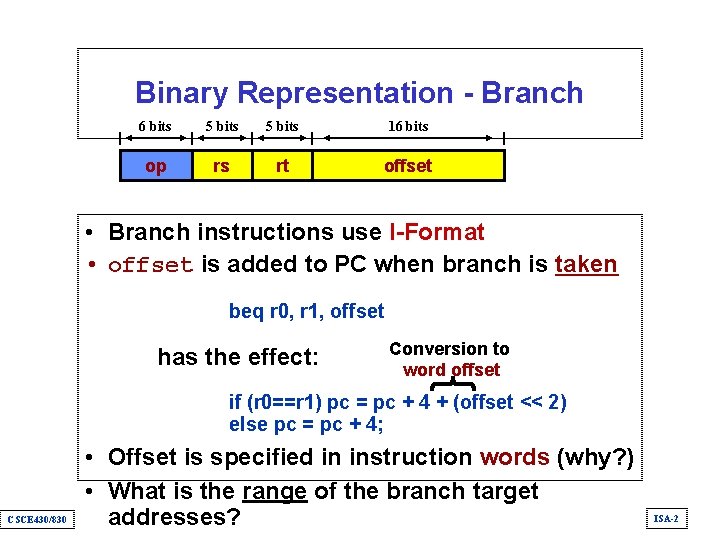

Binary Representation - Branch 6 bits 5 bits 16 bits op rs rt offset • Branch instructions use I-Format • offset is added to PC when branch is taken beq r 0, r 1, offset has the effect: Conversion to word offset if (r 0==r 1) pc = pc + 4 + (offset << 2) else pc = pc + 4; CSCE 430/830 • Offset is specified in instruction words (why? ) • What is the range of the branch target addresses? ISA-2

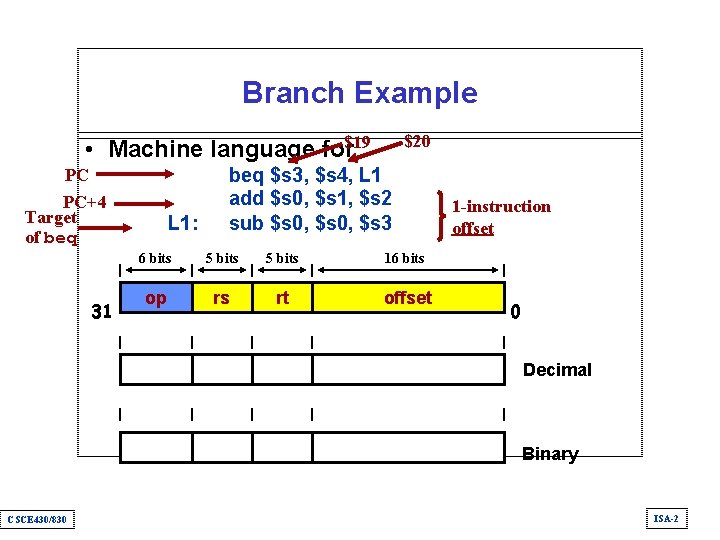

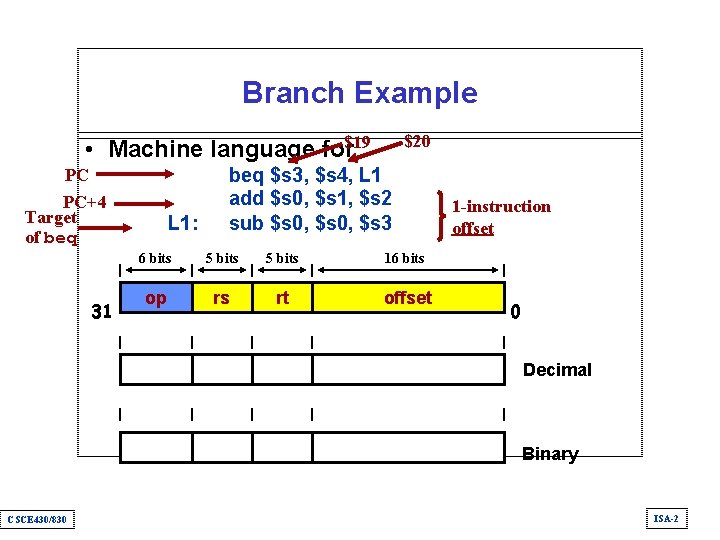

Branch Example $20 • Machine language for$19 PC PC+4 Target of beq 31 L 1: beq $s 3, $s 4, L 1 add $s 0, $s 1, $s 2 sub $s 0, $s 3 6 bits 5 bits 16 bits op rs rt offset 4 19 20 1 000100 10011 10100 CSCE 430/830 1 -instruction offset 000000001 0 Decimal Binary ISA-2

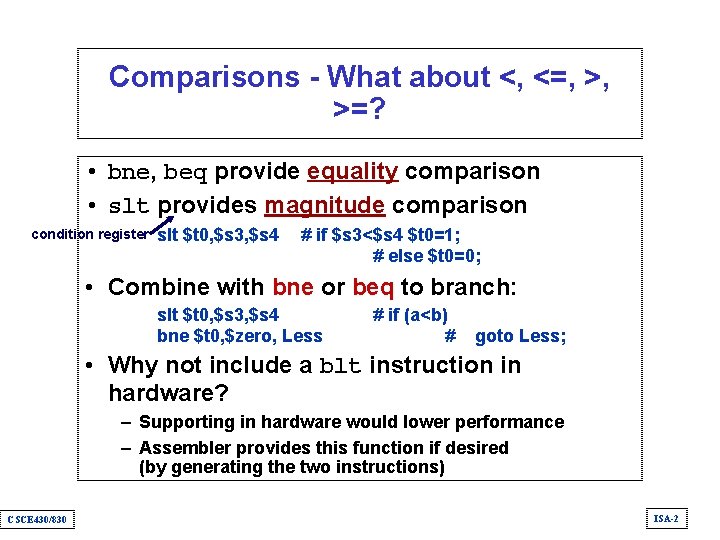

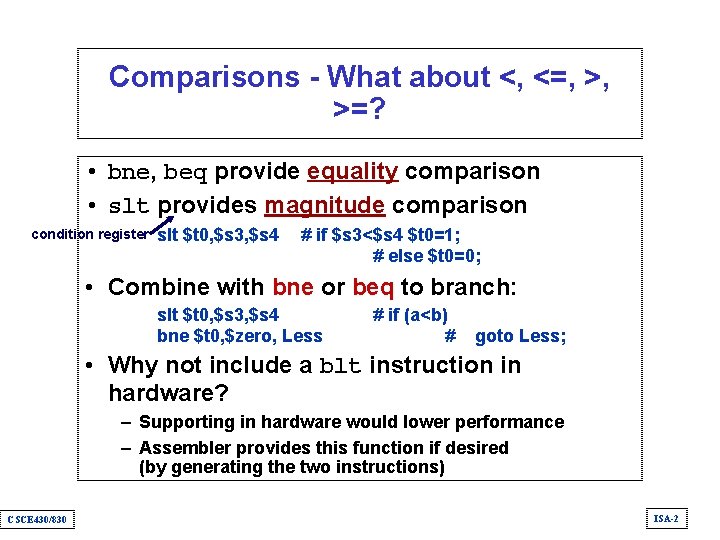

Comparisons - What about <, <=, >, >=? • bne, beq provide equality comparison • slt provides magnitude comparison condition register slt $t 0, $s 3, $s 4 # if $s 3<$s 4 $t 0=1; # else $t 0=0; • Combine with bne or beq to branch: slt $t 0, $s 3, $s 4 bne $t 0, $zero, Less # if (a<b) # goto Less; • Why not include a blt instruction in hardware? – Supporting in hardware would lower performance – Assembler provides this function if desired (by generating the two instructions) CSCE 430/830 ISA-2

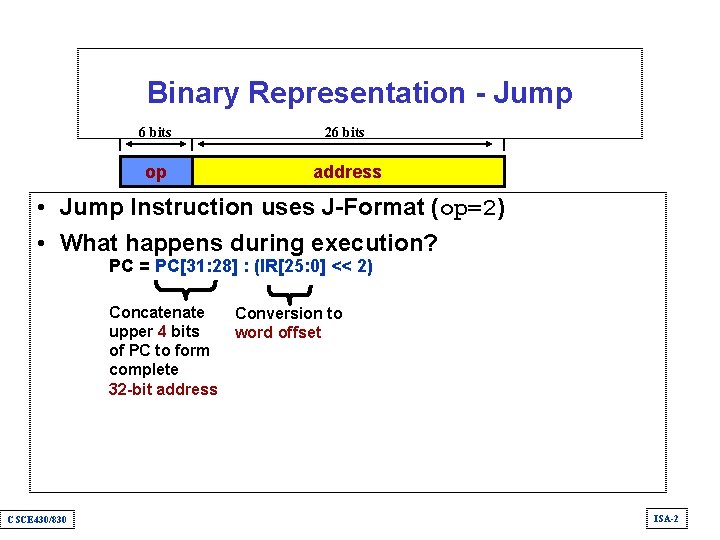

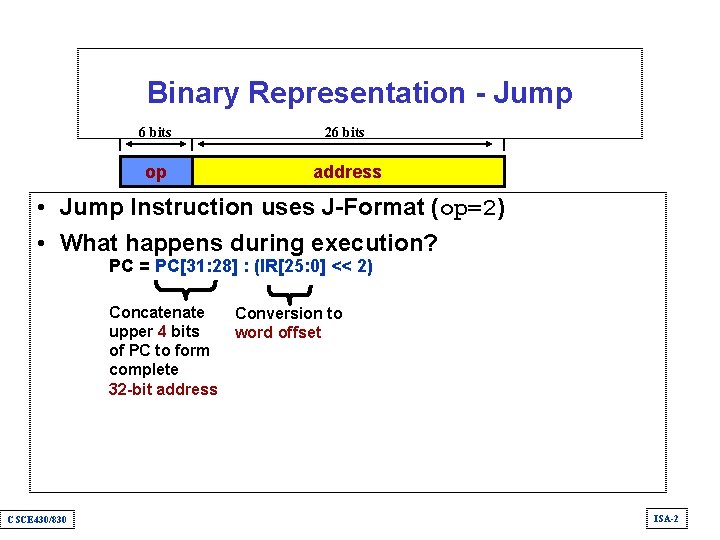

Binary Representation - Jump 6 bits 26 bits op address • Jump Instruction uses J-Format (op=2) • What happens during execution? PC = PC[31: 28] : (IR[25: 0] << 2) Concatenate upper 4 bits of PC to form complete 32 -bit address CSCE 430/830 Conversion to word offset ISA-2

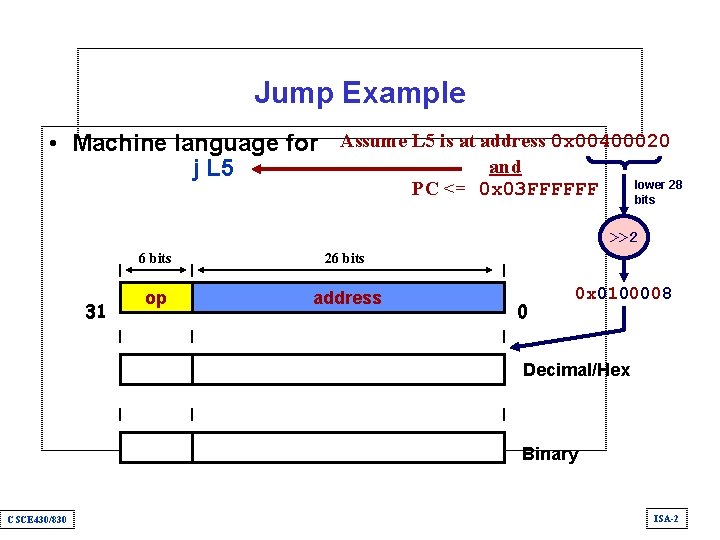

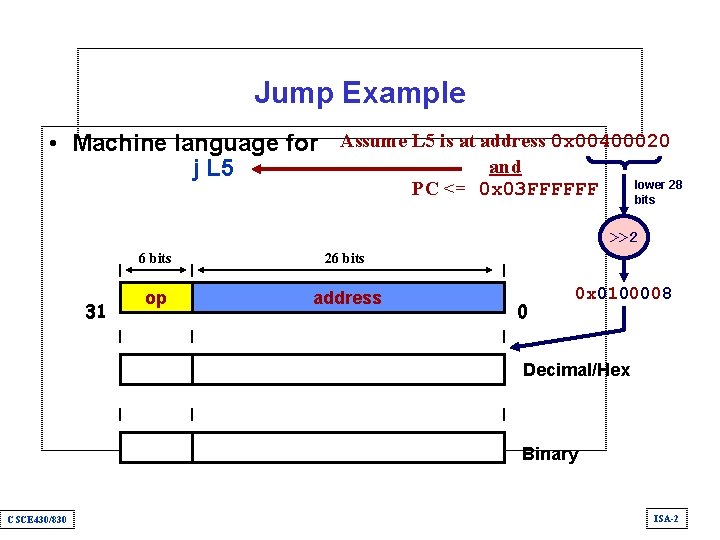

Jump Example • Machine language for Assume L 5 is at address 0 x 00400020 and j L 5 PC <= 0 x 03 FFFFFF lower 28 bits >>2 31 CSCE 430/830 6 bits 26 bits op address 2 0 x 0100008 000010 000001000000001000 0 0 x 0100008 Decimal/Hex Binary ISA-2

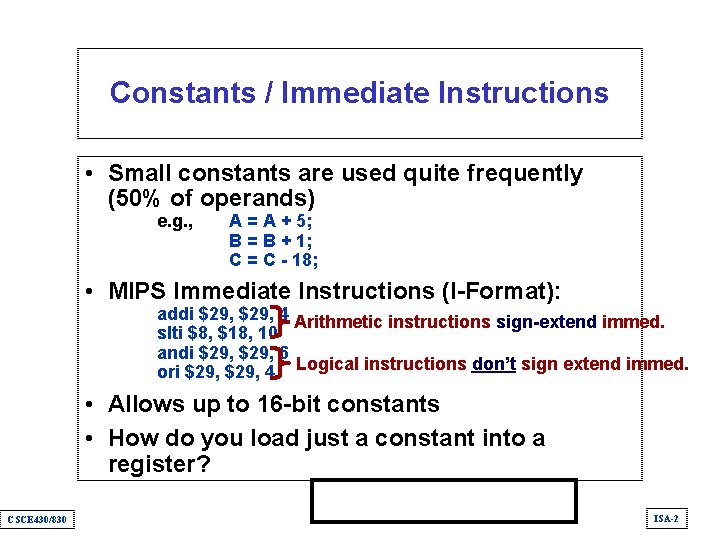

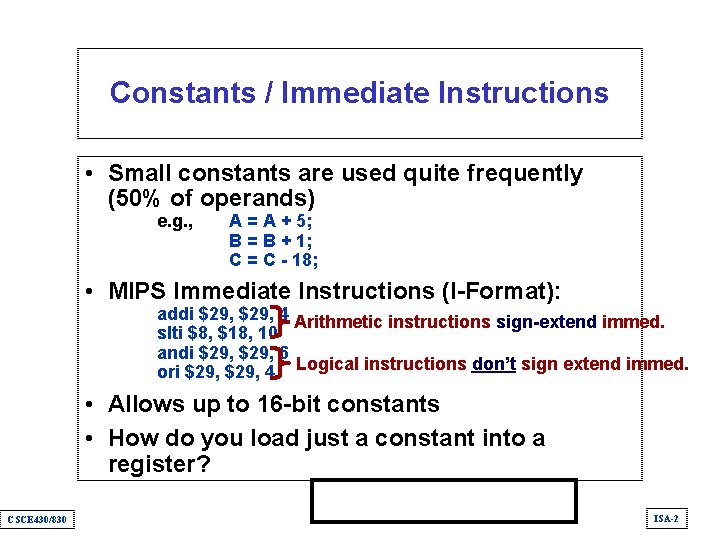

Constants / Immediate Instructions • Small constants are used quite frequently (50% of operands) e. g. , A = A + 5; B = B + 1; C = C - 18; • MIPS Immediate Instructions (I-Format): addi $29, 4 Arithmetic instructions sign-extend immed. slti $8, $18, 10 andi $29, 6 ori $29, 4 Logical instructions don’t sign extend immed. • Allows up to 16 -bit constants • How do you load just a constant into a register? ori $5, $zero, 666 CSCE 430/830 ISA-2

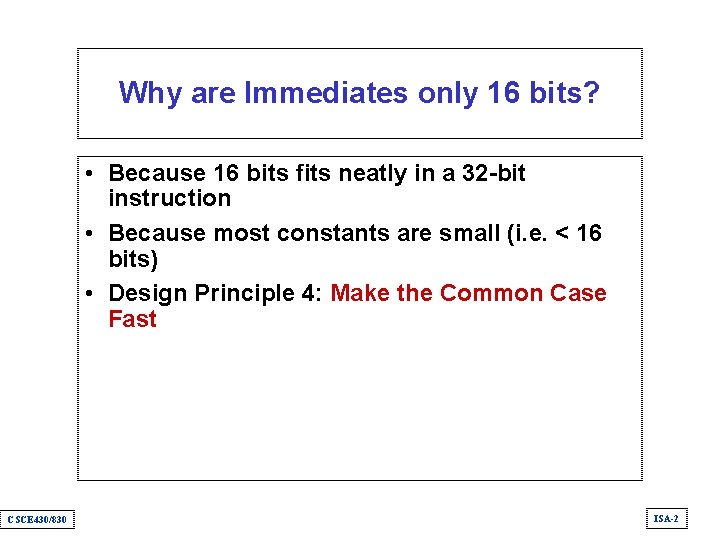

Why are Immediates only 16 bits? • Because 16 bits fits neatly in a 32 -bit instruction • Because most constants are small (i. e. < 16 bits) • Design Principle 4: Make the Common Case Fast CSCE 430/830 ISA-2

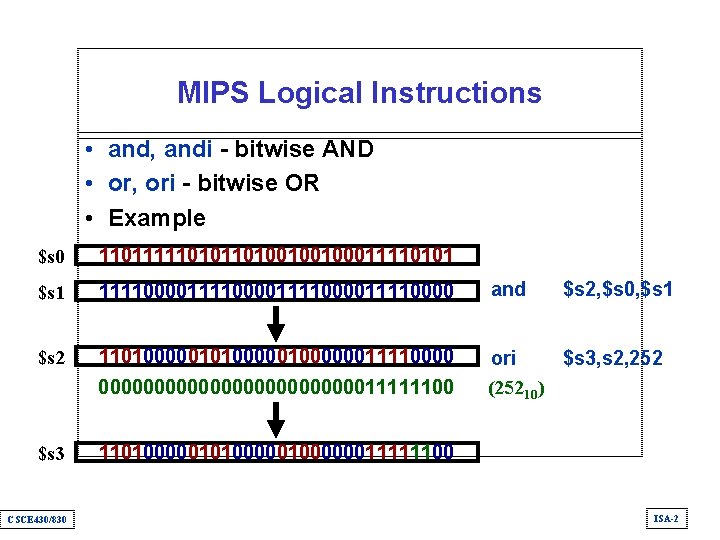

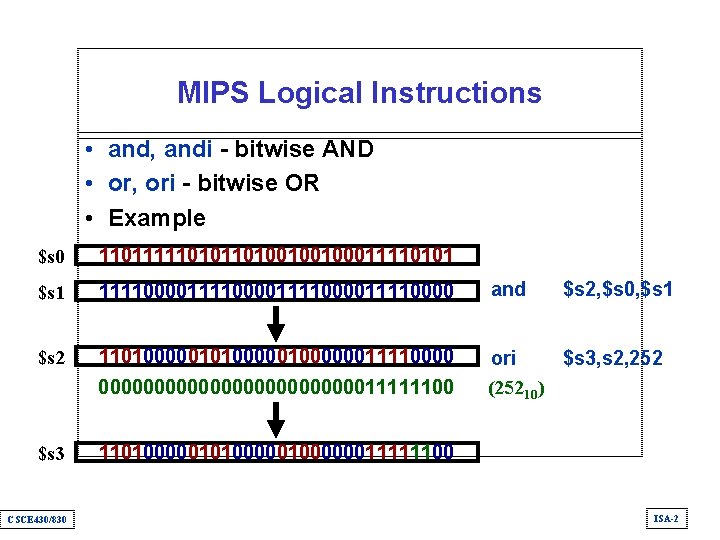

MIPS Logical Instructions • and, andi - bitwise AND • or, ori - bitwise OR • Example $s 0 110111110100100100011110101 $s 1 1111000011110000 and $s 2 110100000100000011110000 ori $s 3, s 2, 252 (25210) 00000000000011111100 $s 3 CSCE 430/830 $s 2, $s 0, $s 1 110100000100000011111100 ISA-2

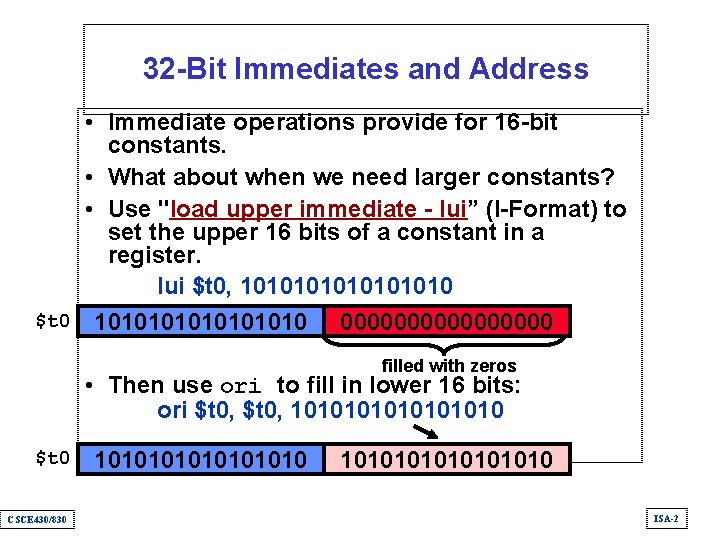

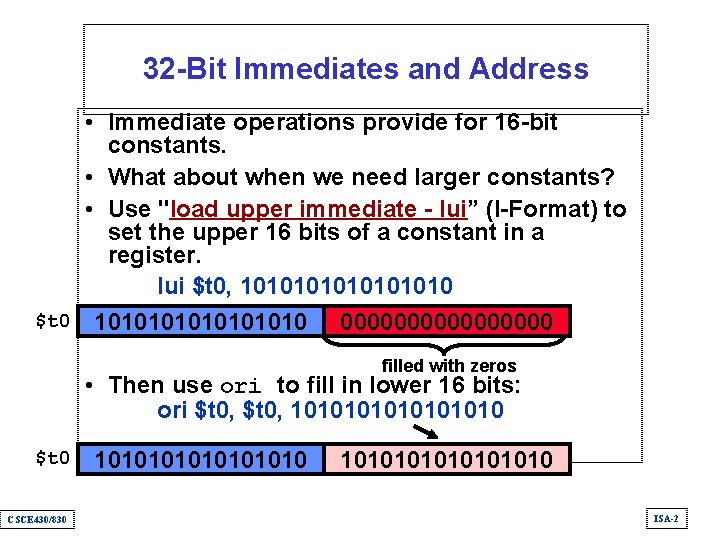

32 -Bit Immediates and Address • Immediate operations provide for 16 -bit constants. • What about when we need larger constants? • Use "load upper immediate - lui” (I-Format) to set the upper 16 bits of a constant in a register. lui $t 0, 10101010 $t 0 10101010 (original contents) 00000000 filled with zeros • Then use ori to fill in lower 16 bits: ori $t 0, 10101010 $t 0 CSCE 430/830 1010101010101010 00000000 ISA-2

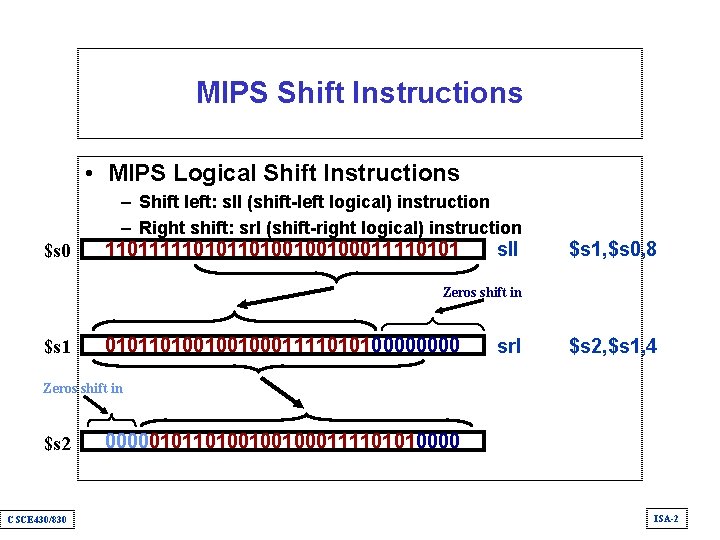

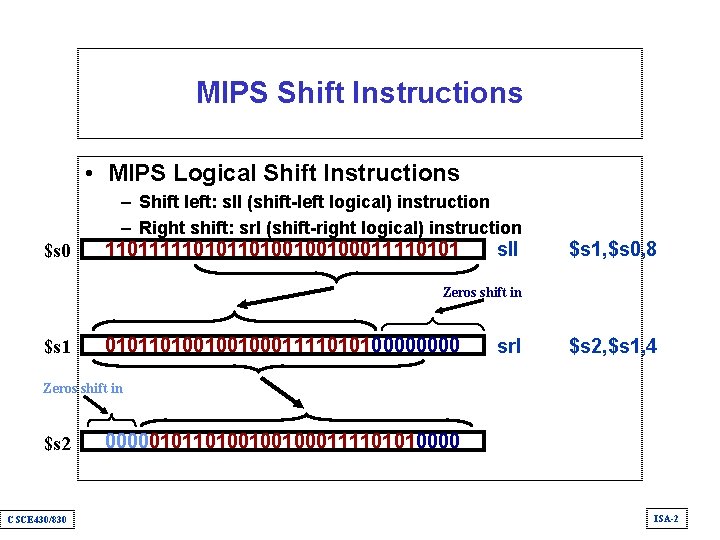

MIPS Shift Instructions • MIPS Logical Shift Instructions – Shift left: sll (shift-left logical) instruction – Right shift: srl (shift-right logical) instruction $s 0 110111110100100100011110101 sll $s 1, $s 0, 8 Zeros shift in $s 1 0101101001001000111101010000 srl $s 2, $s 1, 4 Zeros shift in $s 2 CSCE 430/830 00000101101001001000111101010000 ISA-2

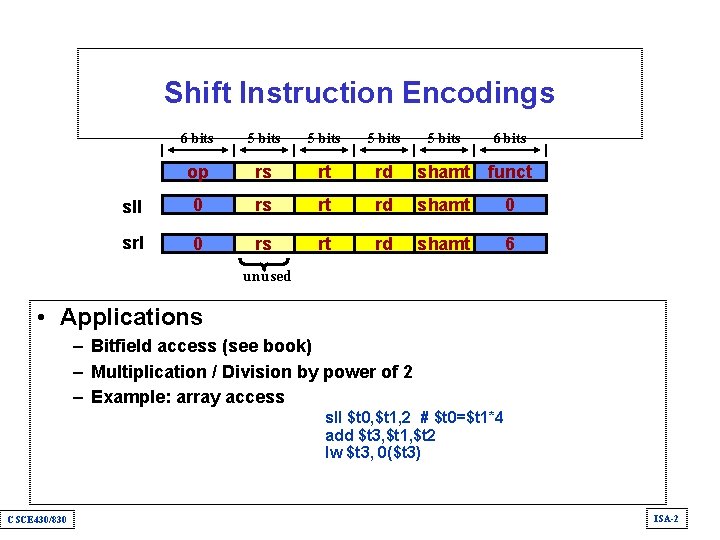

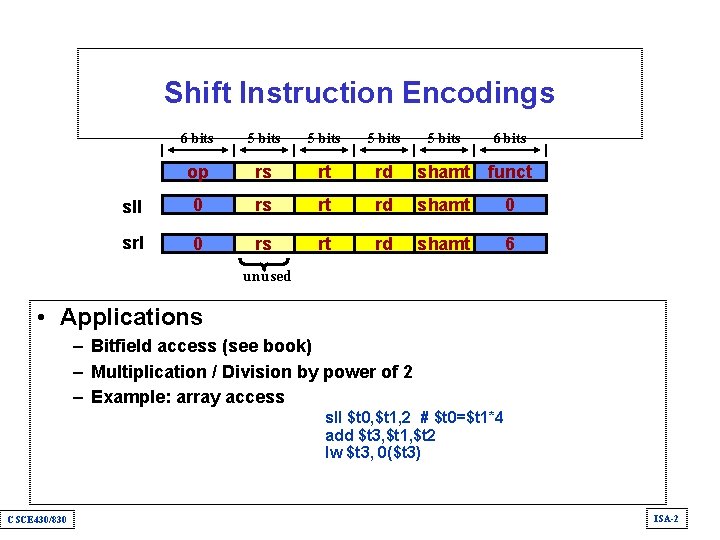

Shift Instruction Encodings 6 bits 5 bits 6 bits op rs rt rd shamt funct sll 0 rs rt rd shamt 0 srl 0 rs rt rd shamt 6 unused • Applications – Bitfield access (see book) – Multiplication / Division by power of 2 – Example: array access sll $t 0, $t 1, 2 # $t 0=$t 1*4 add $t 3, $t 1, $t 2 lw $t 3, 0($t 3) CSCE 430/830 ISA-2

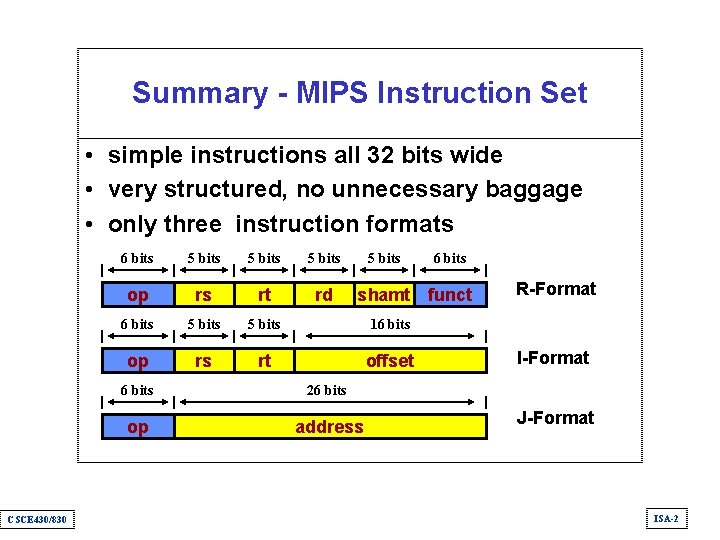

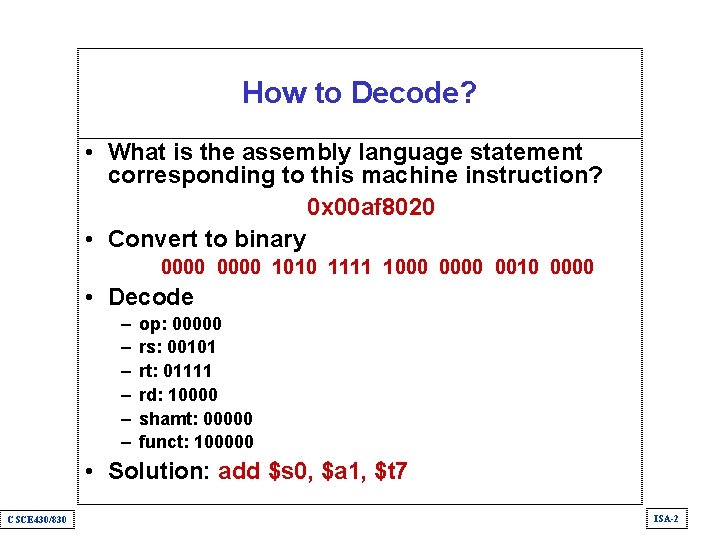

How to Decode? • What is the assembly language statement corresponding to this machine instruction? 0 x 00 af 8020 • Convert to binary 0000 1010 1111 1000 0010 0000 • Decode – – – op: 00000 rs: 00101 rt: 01111 rd: 10000 shamt: 00000 funct: 100000 • Solution: add $s 0, $a 1, $t 7 CSCE 430/830 ISA-2

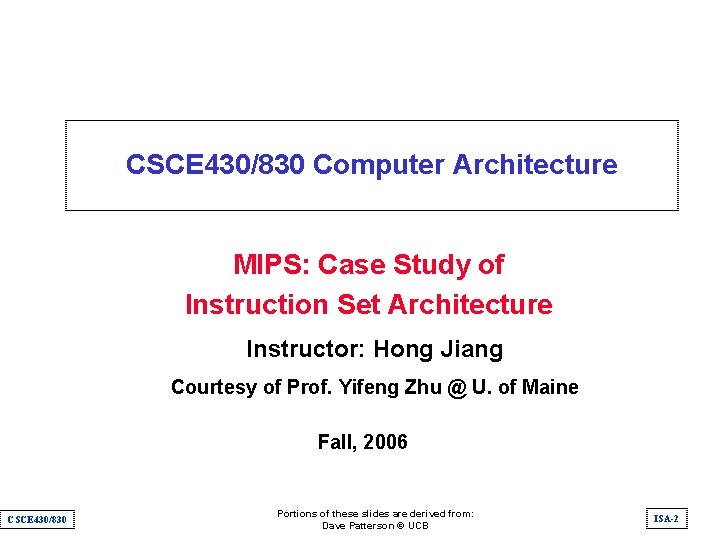

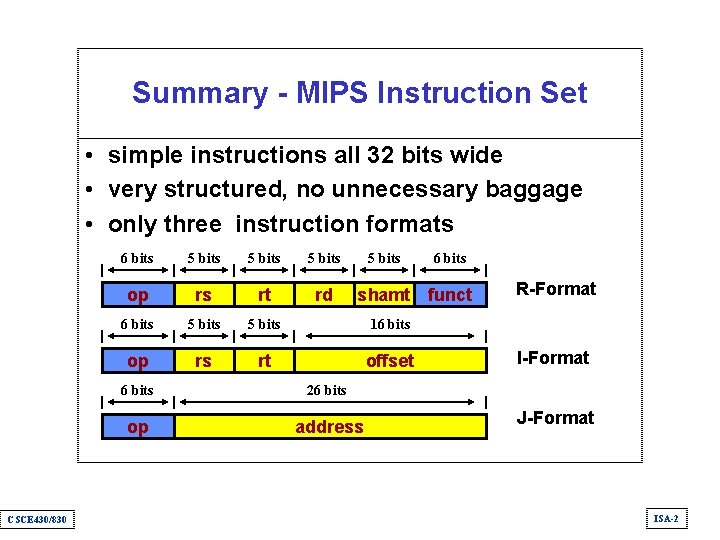

Summary - MIPS Instruction Set • simple instructions all 32 bits wide • very structured, no unnecessary baggage • only three instruction formats CSCE 430/830 6 bits 5 bits op rs rt rd 6 bits 5 bits 16 bits op rs rt offset 6 bits shamt funct 6 bits 26 bits op address R-Format I-Format J-Format ISA-2