Conceitos Avanados de Arquitetura de Computadores Arquiteturas RISC

- Slides: 21

Conceitos Avançados de Arquitetura de Computadores Arquiteturas RISC Arquiteturas Superpipeline e Superescalares

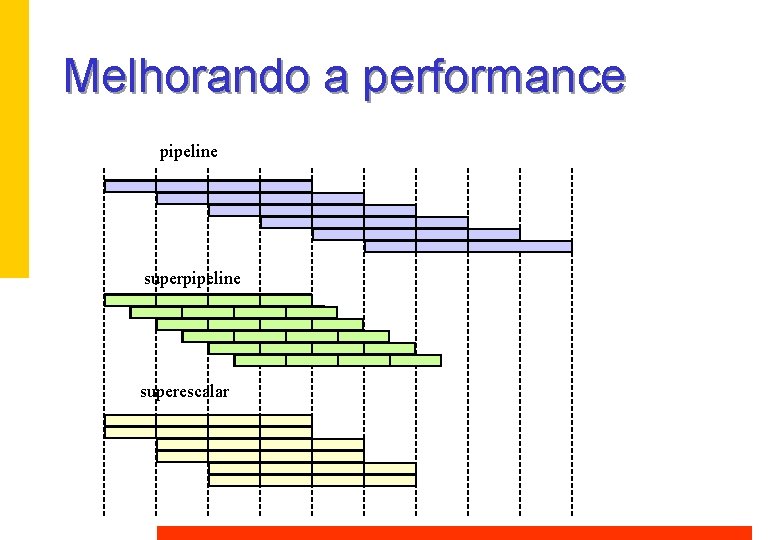

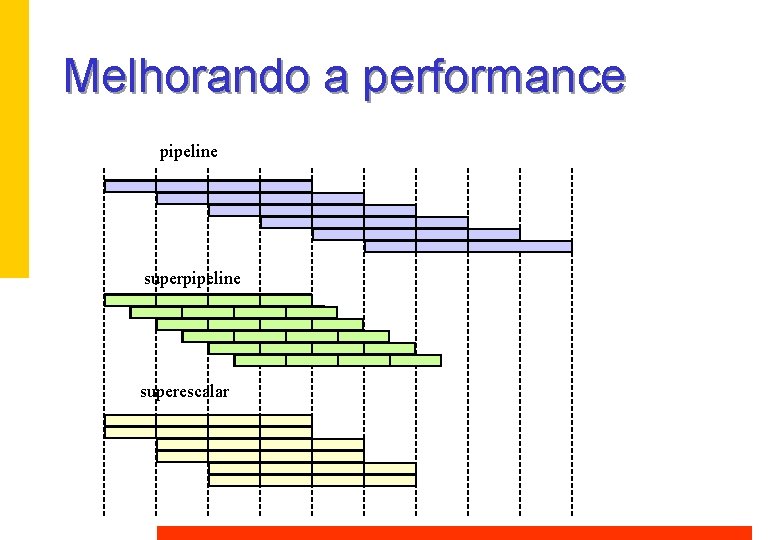

Melhorando a performance • Como melhorar a performance de máquinas implementadas como pipeline? – Aumentar o número de estágios do pipeline • Superpipeline – Replicar recursos para executar instruções em paralelo • Superescalar

Melhorando a performance pipeline superescalar

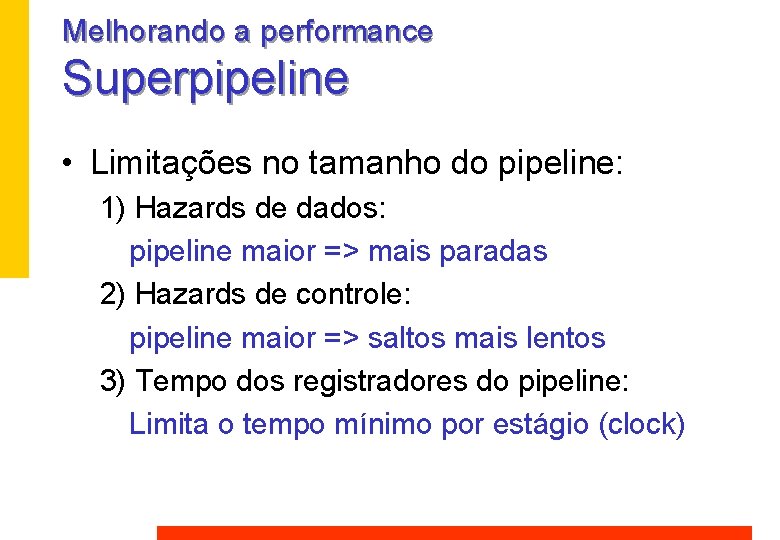

Melhorando a performance Superpipeline • Limitações no tamanho do pipeline: 1) Hazards de dados: pipeline maior => mais paradas 2) Hazards de controle: pipeline maior => saltos mais lentos 3) Tempo dos registradores do pipeline: Limita o tempo mínimo por estágio (clock)

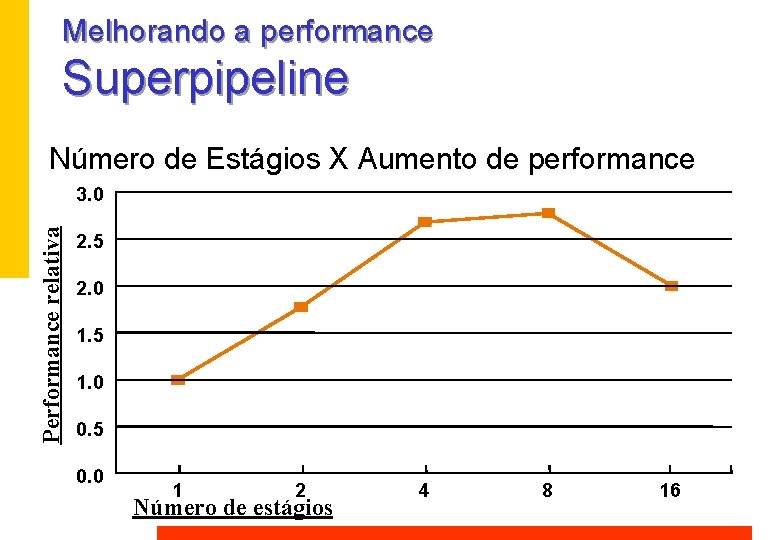

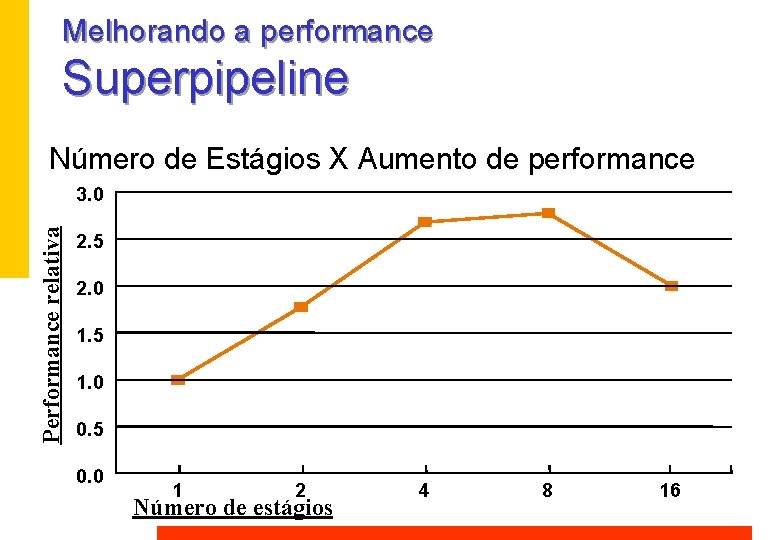

Melhorando a performance Superpipeline Número de Estágios X Aumento de performance Performance relativa 3. 0 2. 5 2. 0 1. 5 1. 0 0. 5 0. 0 1 2 Número de estágios 4 8 16

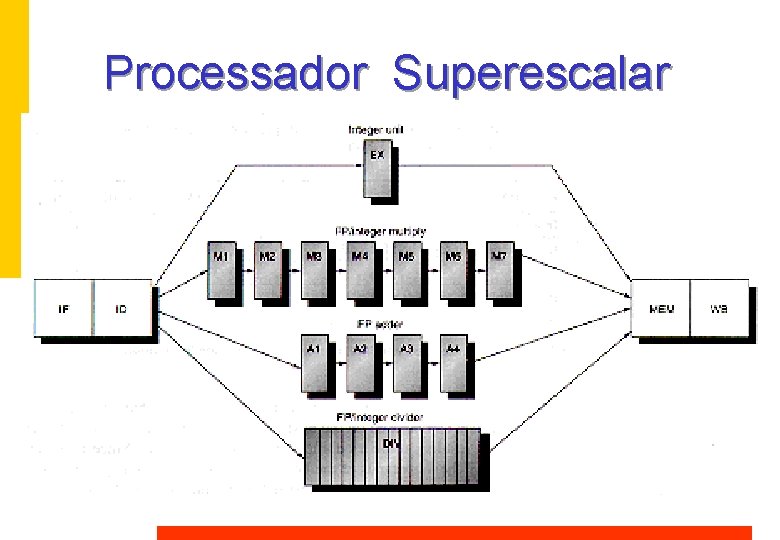

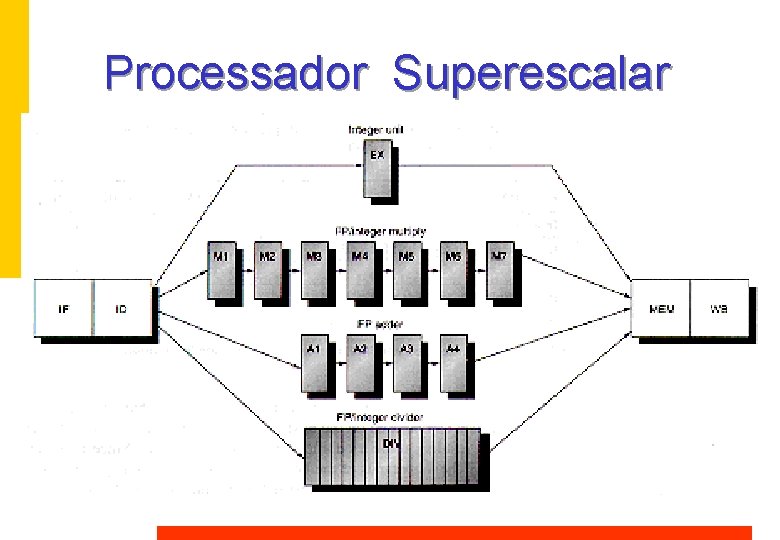

Processador superescalar • Execução simultânea de instruções: – aritméticas, loads, stores, etc • Aplicável a máquinas RISC e CISC – RISC: melhor uso efetivo – CISC: implementação mais difícil

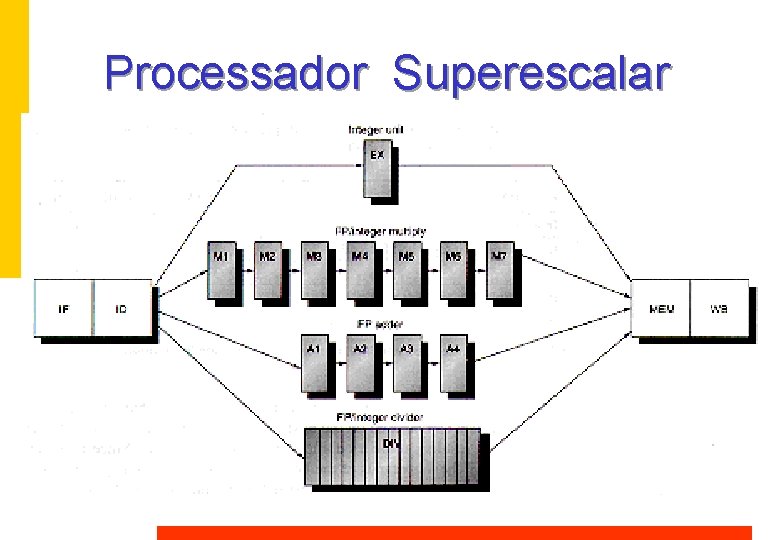

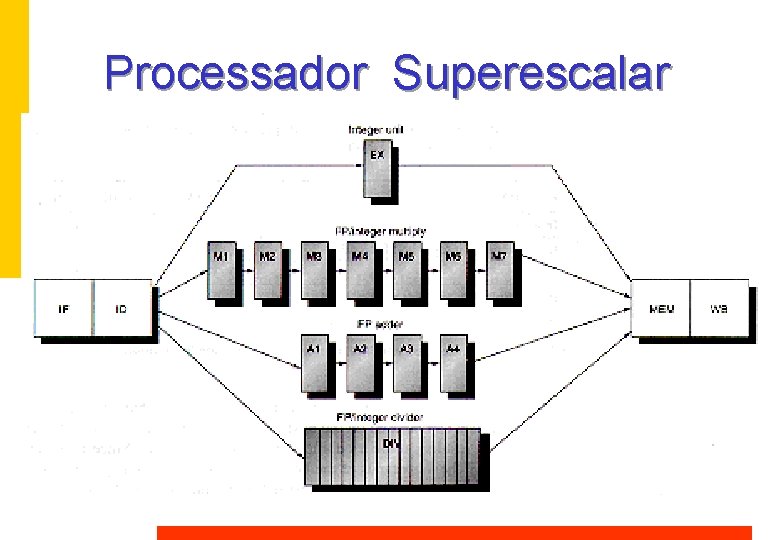

Processador Superescalar

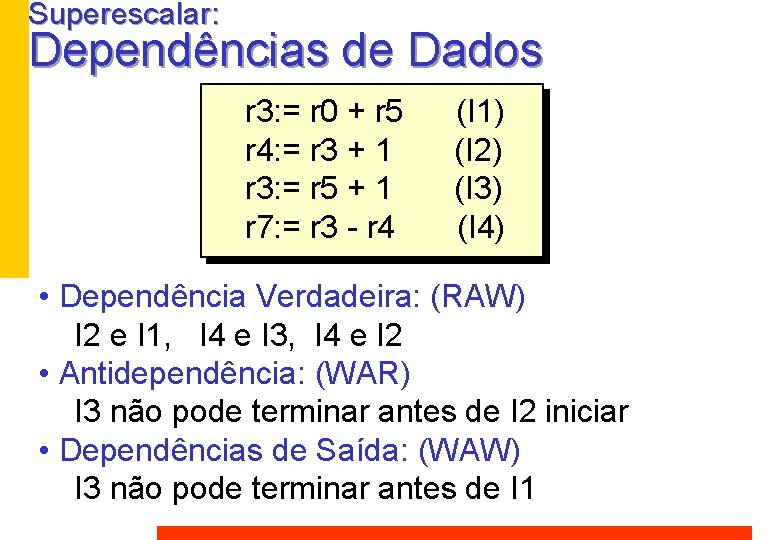

Superescalar: Revisando Dependências de Dados - Dependência Verdadeira: Read-after-Write (RAW) - Dependência de Saída: Write-after-Write (WAW) - Antidependências: Write-after-Read (WAR)

Superescalar: Dependências WAR e WAW As CPUs comuns não apresentam estas dependências porque apenas um estágio do pipeline altera o estado da máquina (os registradores) na ordem em que as instruções são iniciadas.

Processador Superescalar

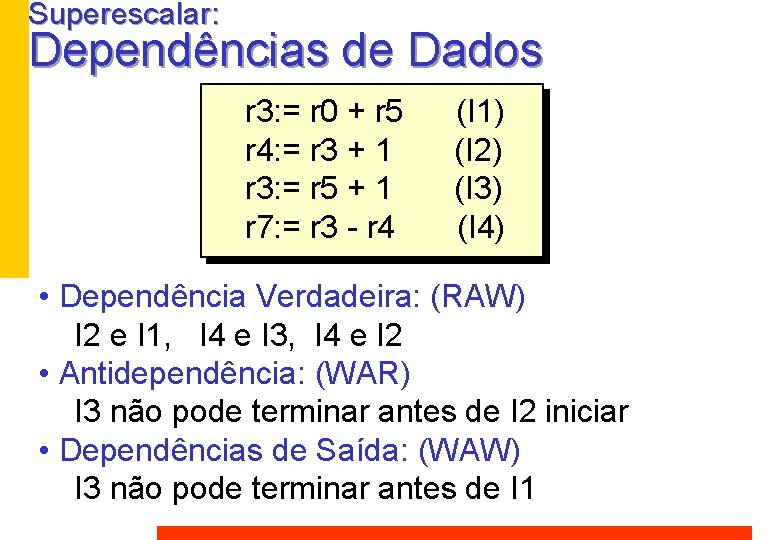

Superescalar: Dependências de Dados r 3: = r 0 + r 5 r 4: = r 3 + 1 r 3: = r 5 + 1 r 7: = r 3 - r 4 (I 1) (I 2) (I 3) (I 4) • Dependência Verdadeira: (RAW) I 2 e I 1, I 4 e I 3, I 4 e I 2 • Antidependência: (WAR) I 3 não pode terminar antes de I 2 iniciar • Dependências de Saída: (WAW) I 3 não pode terminar antes de I 1

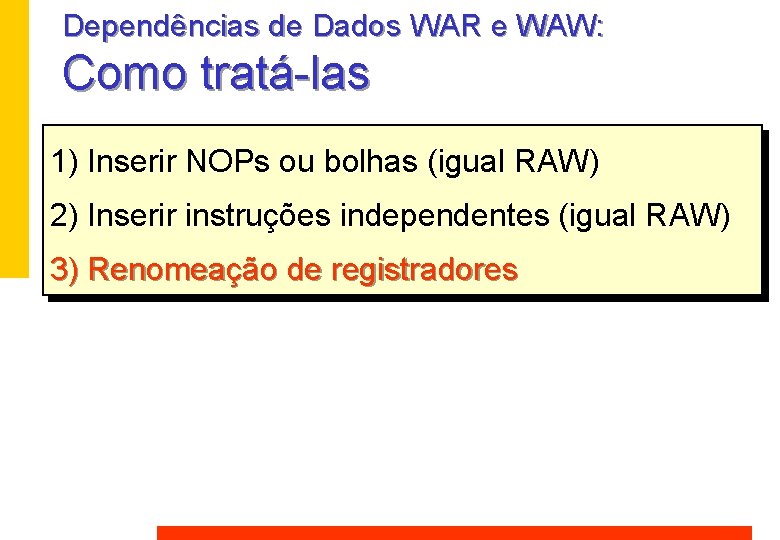

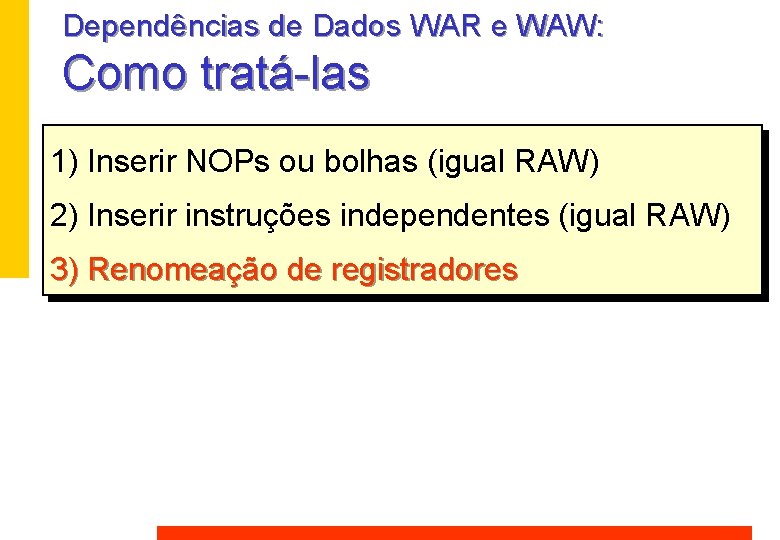

Dependências de Dados WAR e WAW: Como tratá-las 1) Inserir NOPs ou bolhas (igual RAW) 2) Inserir instruções independentes (igual RAW) 3) Renomeação de registradores

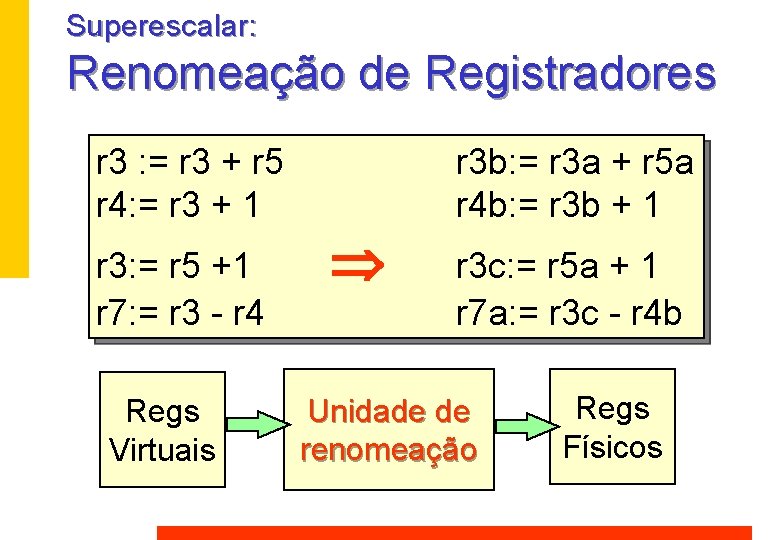

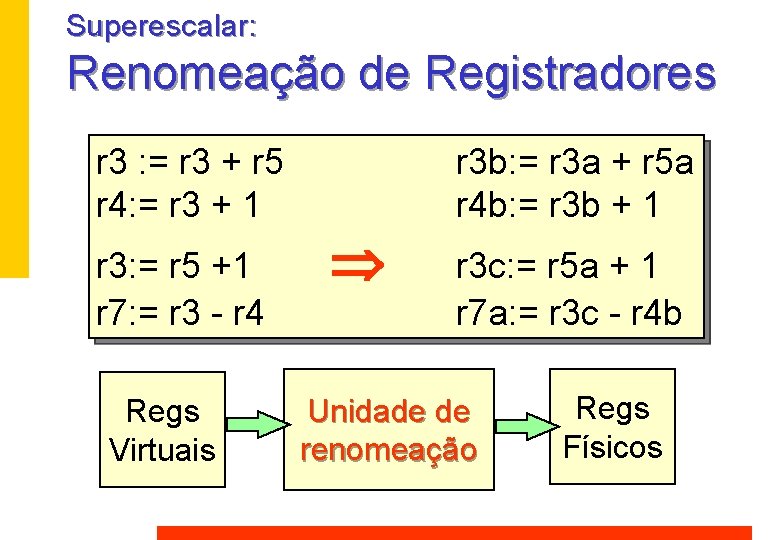

Superescalar: Renomeação de Registradores r 3 : = r 3 + r 5 r 4: = r 3 + 1 r 3: = r 5 +1 r 7: = r 3 - r 4 Regs Virtuais r 3 b: = r 3 a + r 5 a r 4 b: = r 3 b + 1 r 3 c: = r 5 a + 1 r 7 a: = r 3 c - r 4 b Unidade de renomeação Regs Físicos

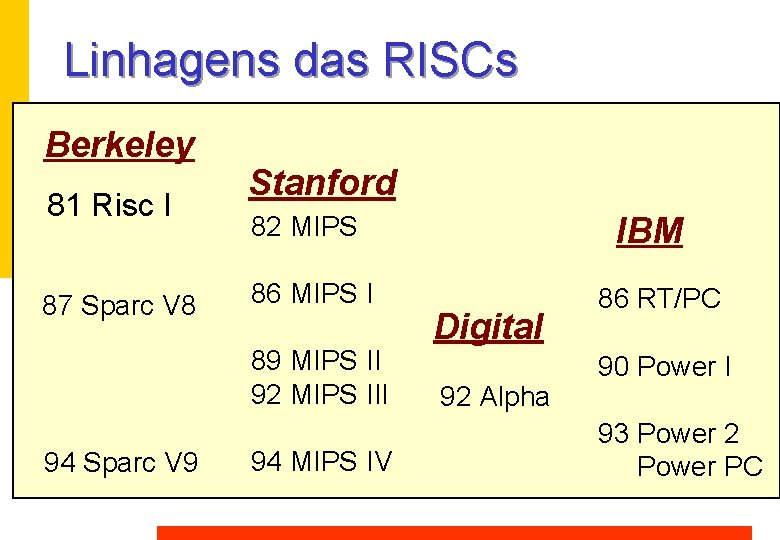

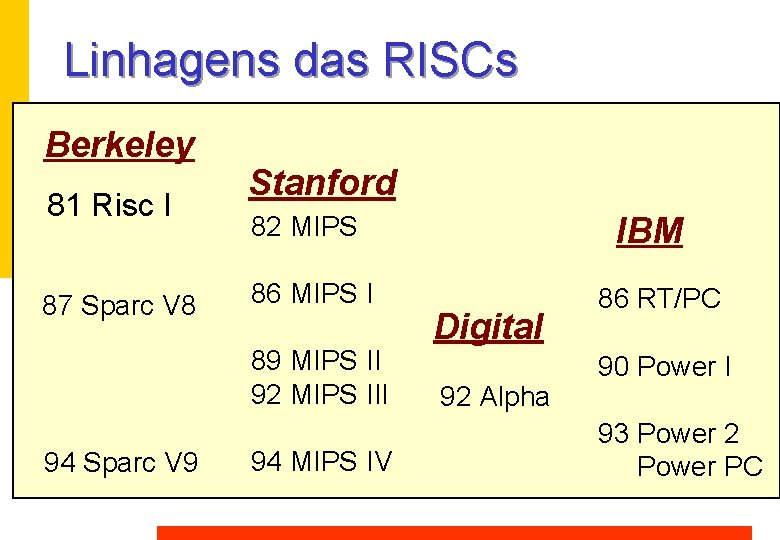

Linhagens das RISCs Berkeley 81 Risc I 87 Sparc V 8 Stanford 82 MIPS 86 MIPS I 89 MIPS II 92 MIPS III 94 Sparc V 9 94 MIPS IV IBM Digital 92 Alpha 86 RT/PC 90 Power I 93 Power 2 Power PC

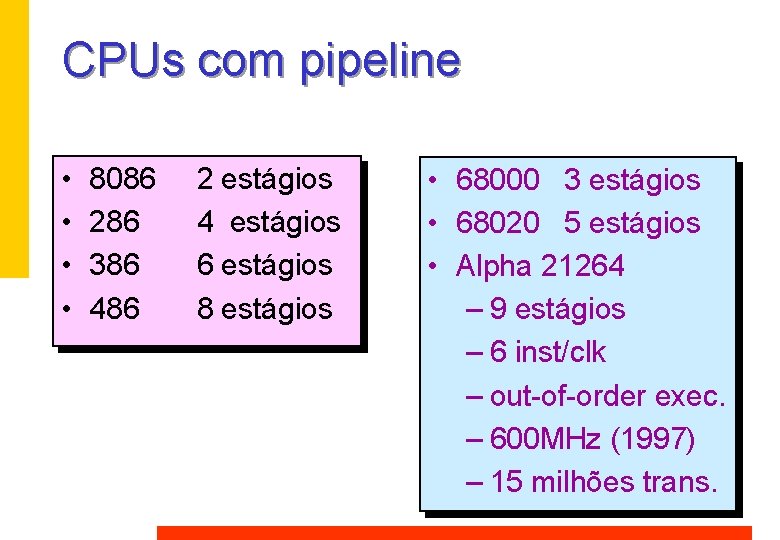

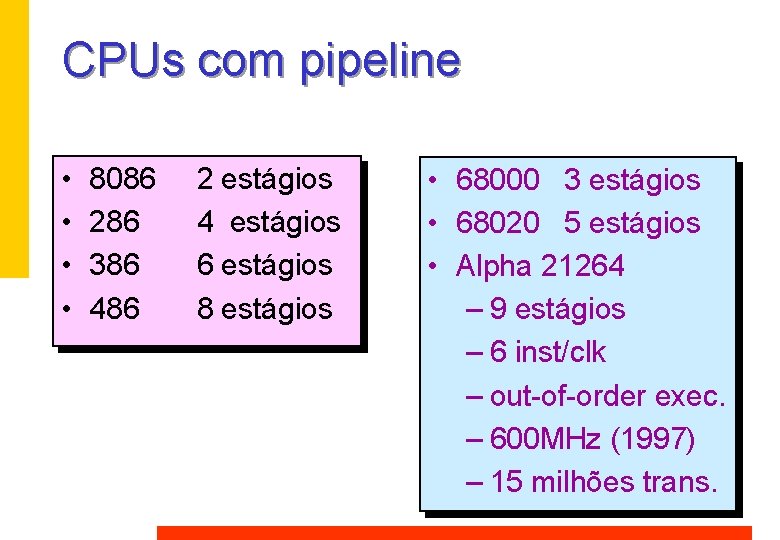

CPUs com pipeline • • 8086 286 386 486 2 estágios 4 estágios 6 estágios 8 estágios • 68000 3 estágios • 68020 5 estágios • Alpha 21264 – 9 estágios – 6 inst/clk – out-of-order exec. – 600 MHz (1997) – 15 milhões trans.

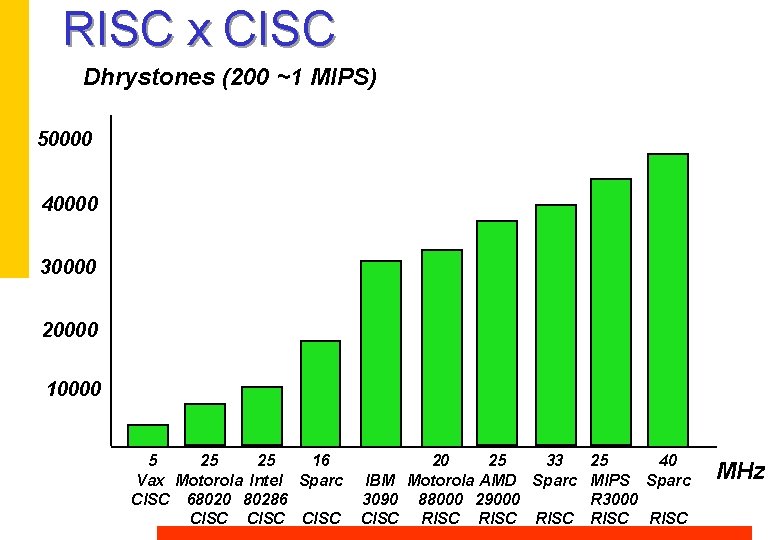

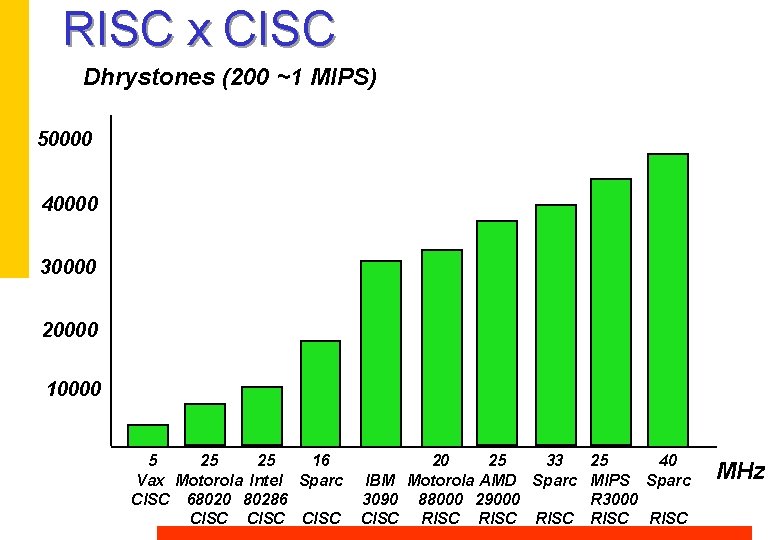

RISC x CISC Dhrystones (200 ~1 MIPS) 50000 40000 30000 20000 10000 25 5 25 16 Vax Motorola Intel Sparc CISC 68020 80286 CISC 20 25 33 25 40 IBM Motorola AMD Sparc MIPS Sparc 3090 88000 29000 R 3000 CISC RISC RISC MHz

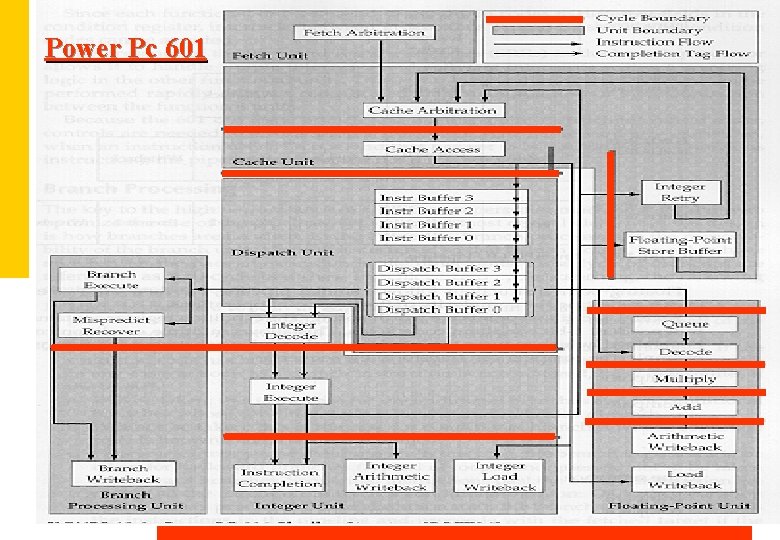

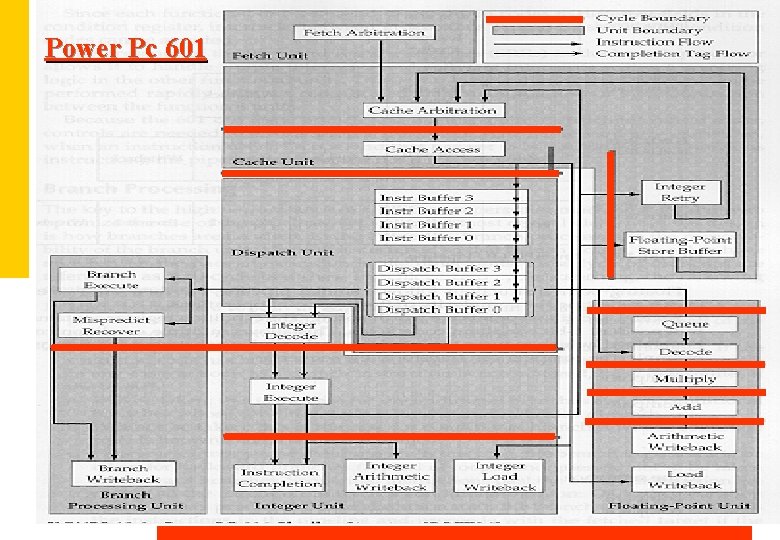

Power Pc 601

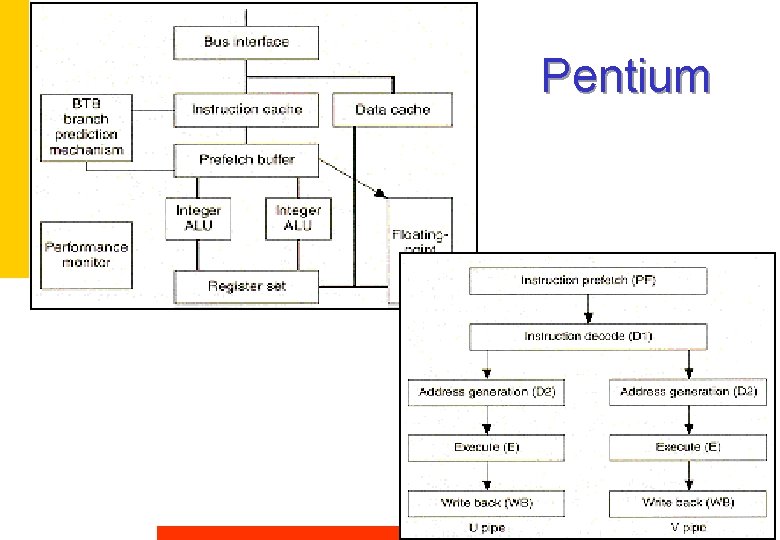

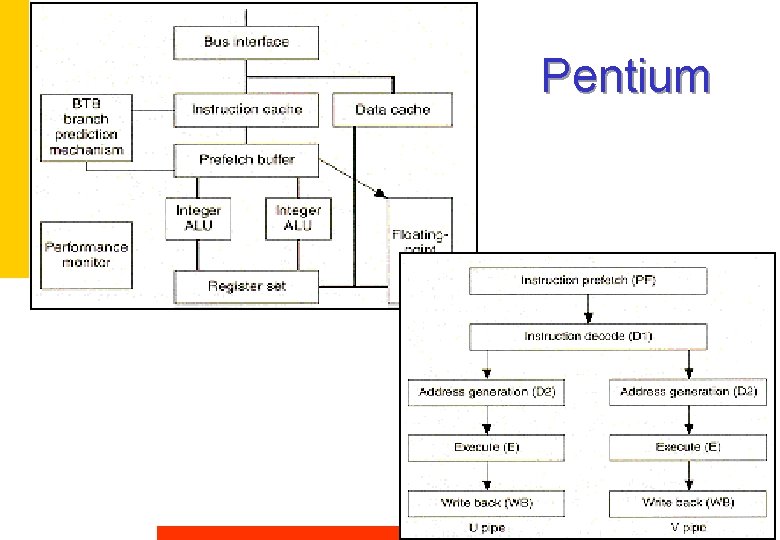

Pentium

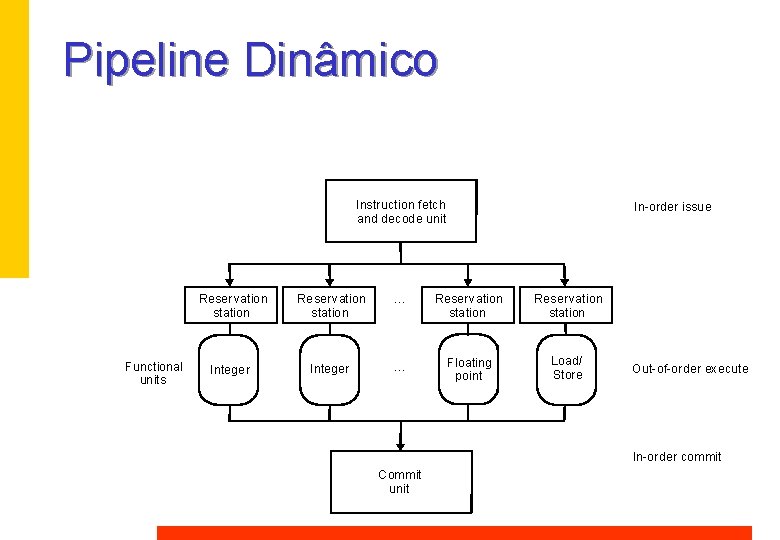

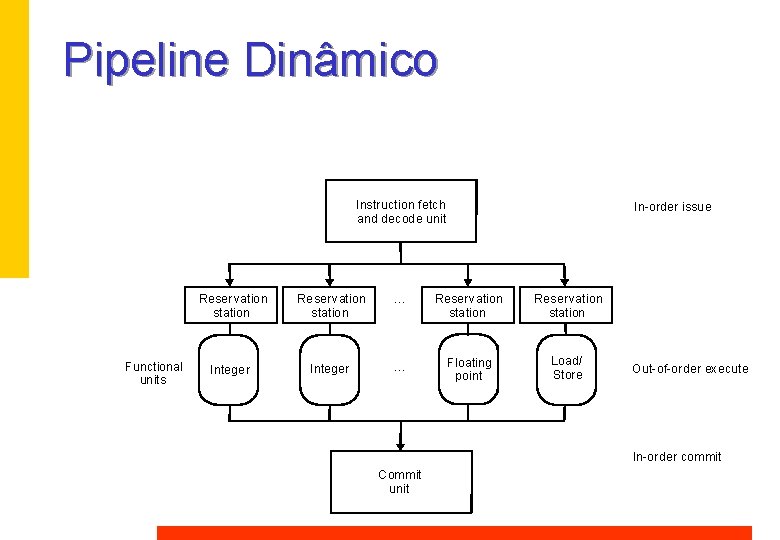

Pipeline Dinâmico Instruction fetch and decode unit Functional units In-order issue Reser vation station … Reser vation station Integer … Floating point Load/ Store Out-of-order execute In-order commit Commit unit

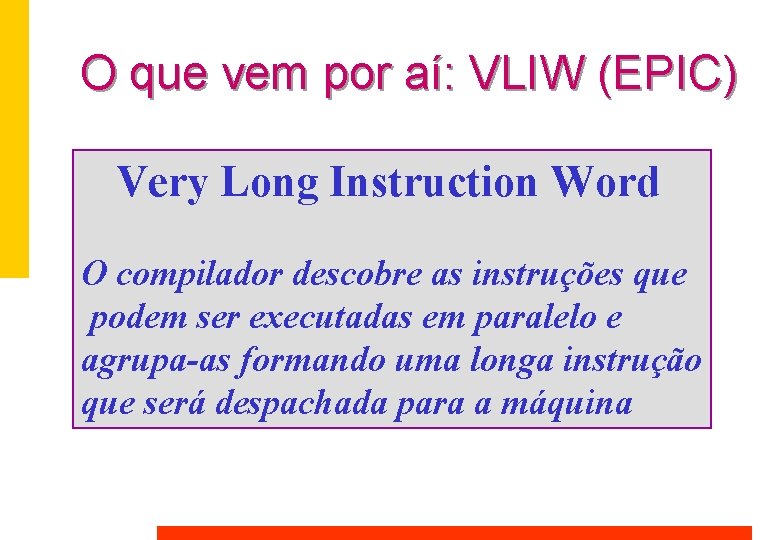

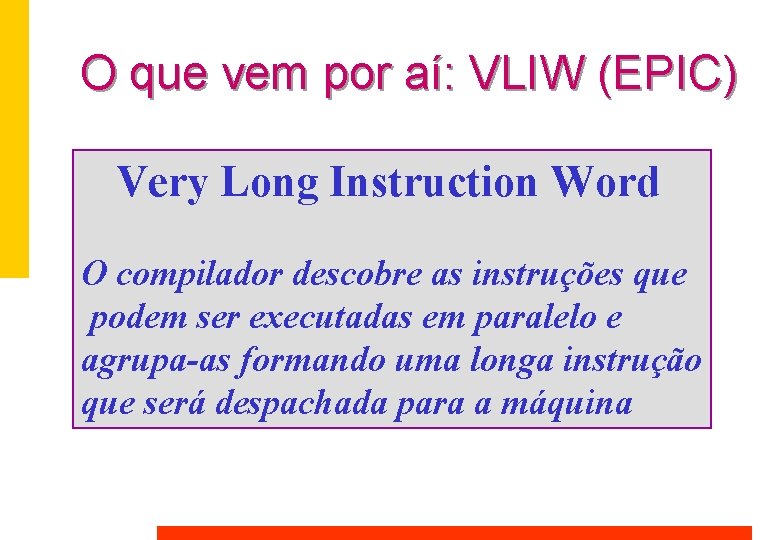

O que vem por aí: VLIW (EPIC) Very Long Instruction Word O compilador descobre as instruções que podem ser executadas em paralelo e agrupa-as formando uma longa instrução que será despachada para a máquina

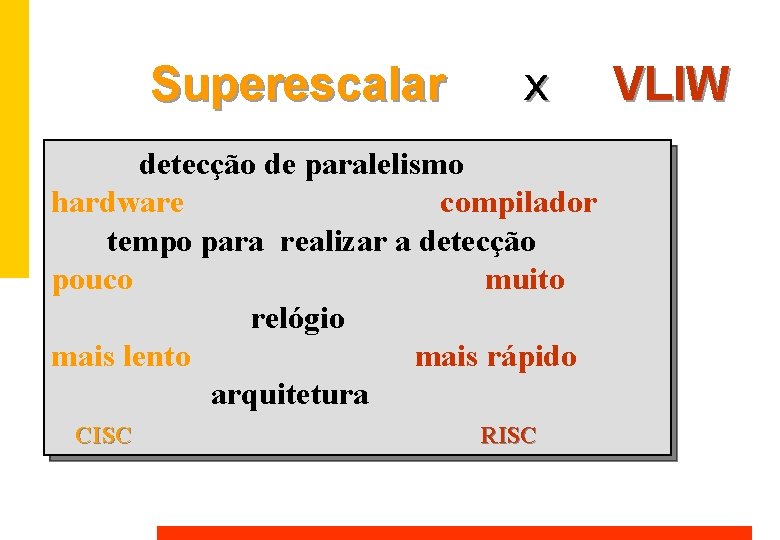

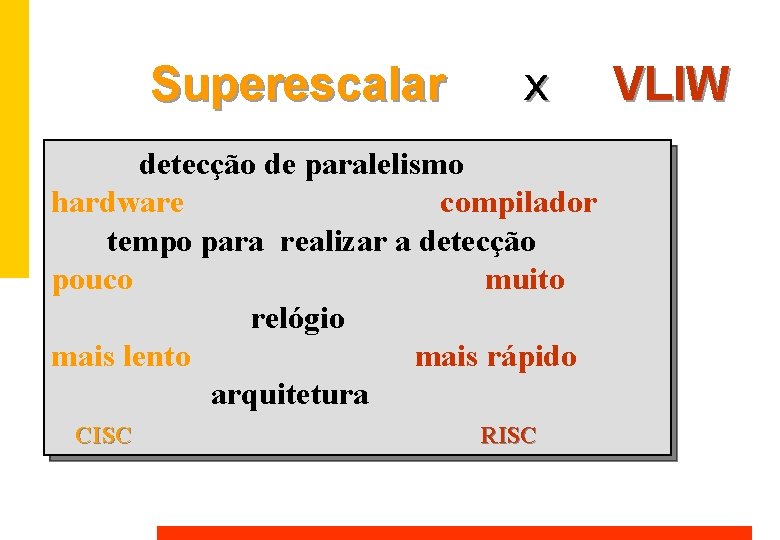

Superescalar x detecção de paralelismo hardware compilador tempo para realizar a detecção pouco muito relógio mais lento mais rápido arquitetura CISC RISC VLIW