DISCIPLINA Arquiteturas e Redes de Computadores PARTE 1

- Slides: 51

DISCIPLINA: Arquiteturas e Redes de Computadores PARTE 1: Arquitetura Bibliografia Principal: John L. Hennessy & David A. Patterson – Computer Architecture – A Quantitative Approach, 4 th Ed. , Morgan Kaufmann Publishers, USA, 2007. Tradução – Editora Campus Complementar: David A. Patterson & John L. Hennessy – Computer Organization & Design – The Hardware/Software Interface, 3 rd Ed. , Morgan Kaufmann Publishers, USA, 2005. Tradução – Editora Campus DAP. S 98 1

AVALIAÇÃO • 1 prova de suficiência • 1 prova no meio do semestre • 1 prova no fim do semestre • (o conceito final é a média com o conceito relativo à matéria de redes) DAP. S 98 2

Aula 1: Tecnologias, Medida de desempenho, Arquiteturas Básicas DAP. S 98 3

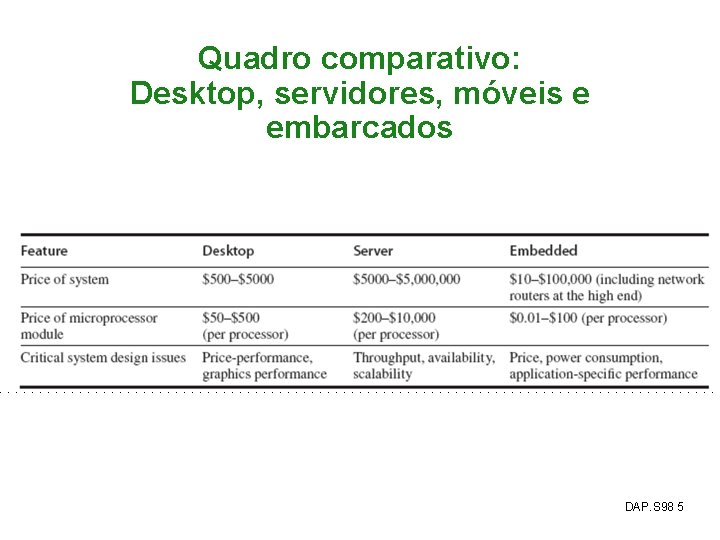

Os laptops de hoje são melhores que os supercomputadores de 1970’s: máquinas comerciais - mainframes & minicomputadores 1980’s: computadores pessoais, mainframes maiores 1990’s: laptop & handheld, supercomputadores usando microprocessadores 2000’s: 3 segmentos dominantes desktop (com pequenas diversidades) servidores (moderadamente diferentes) móveis e embarcados (enorme diversidade) DAP. S 98 4

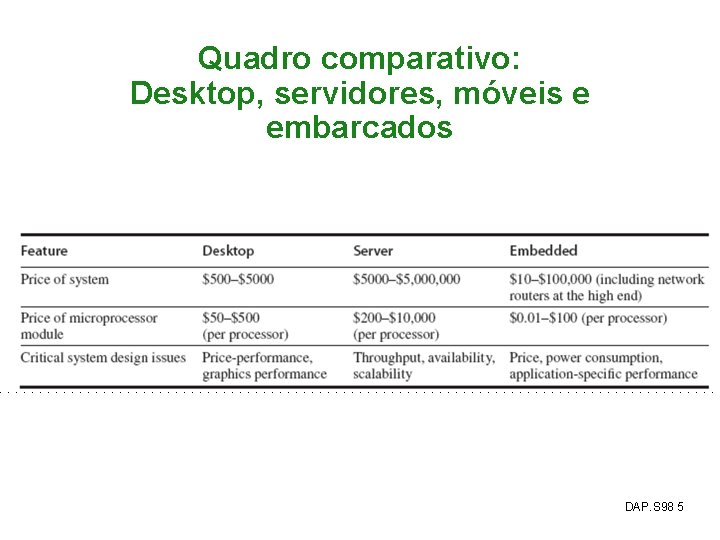

Quadro comparativo: Desktop, servidores, móveis e embarcados DAP. S 98 5

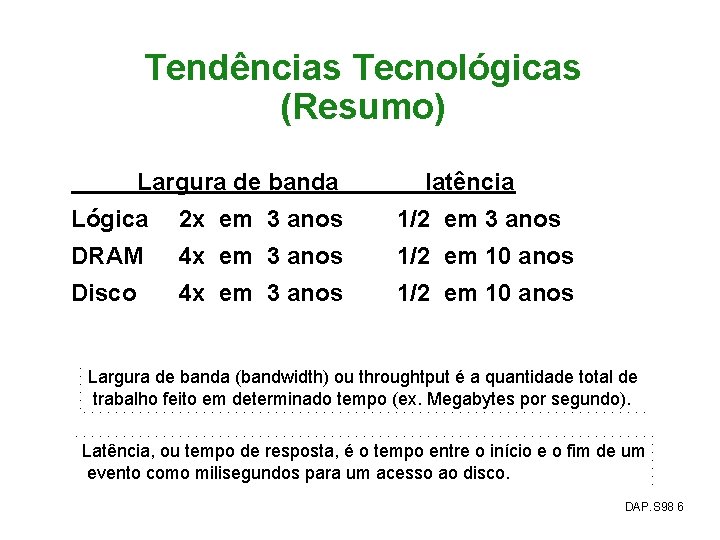

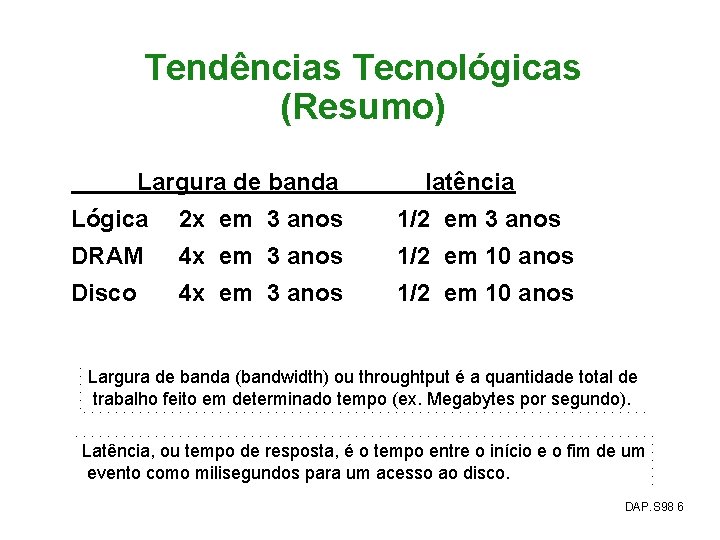

Tendências Tecnológicas (Resumo) Largura de banda latência Lógica 2 x em 3 anos 1/2 em 3 anos DRAM 4 x em 3 anos 1/2 em 10 anos Disco 4 x em 3 anos 1/2 em 10 anos Largura de banda (bandwidth) ou throughtput é a quantidade total de trabalho feito em determinado tempo (ex. Megabytes por segundo). Latência, ou tempo de resposta, é o tempo entre o início e o fim de um evento como milisegundos para um acesso ao disco. DAP. S 98 6

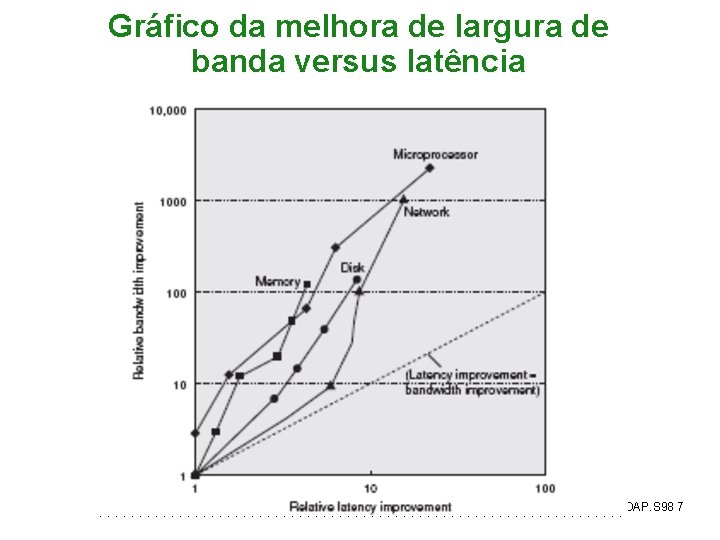

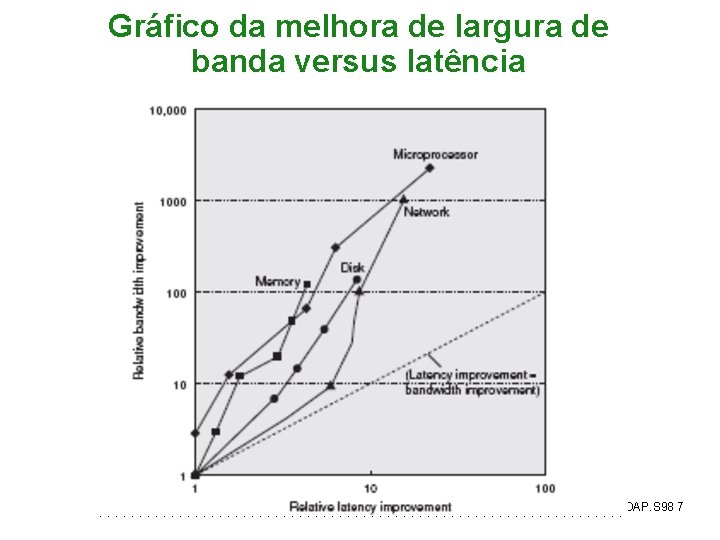

Gráfico da melhora de largura de banda versus latência DAP. S 98 7

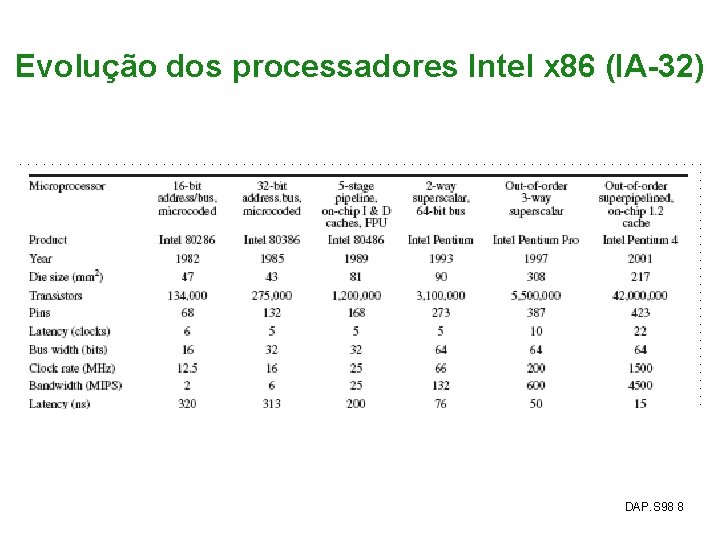

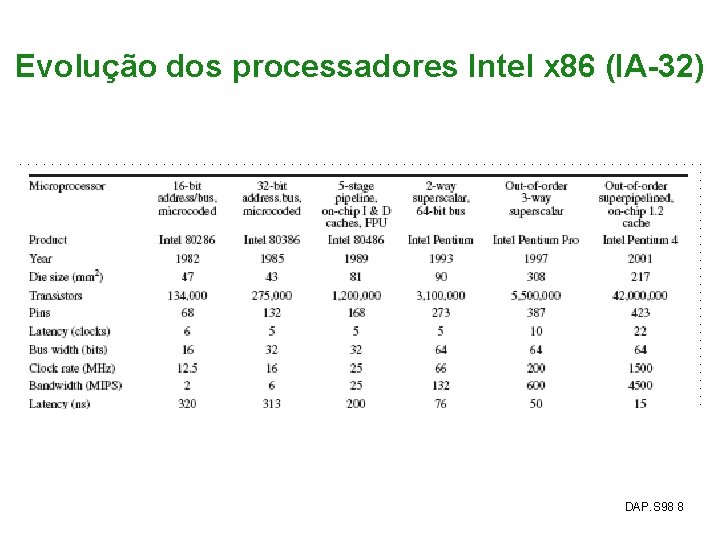

Evolução dos processadores Intel x 86 (IA-32) DAP. S 98 8

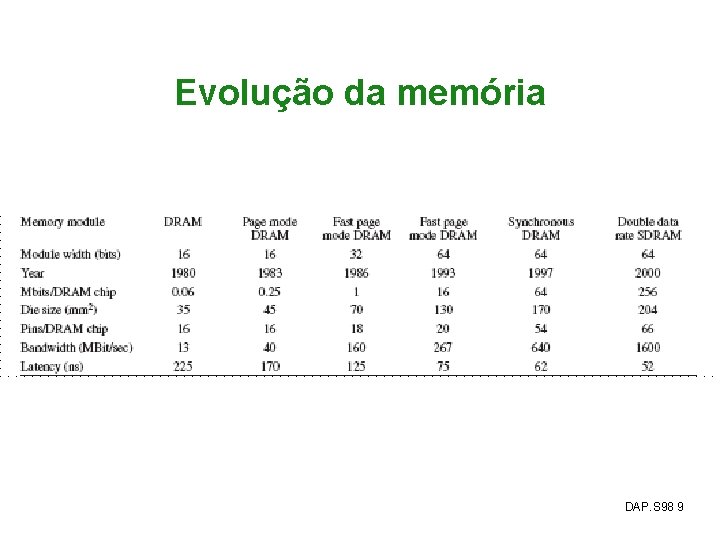

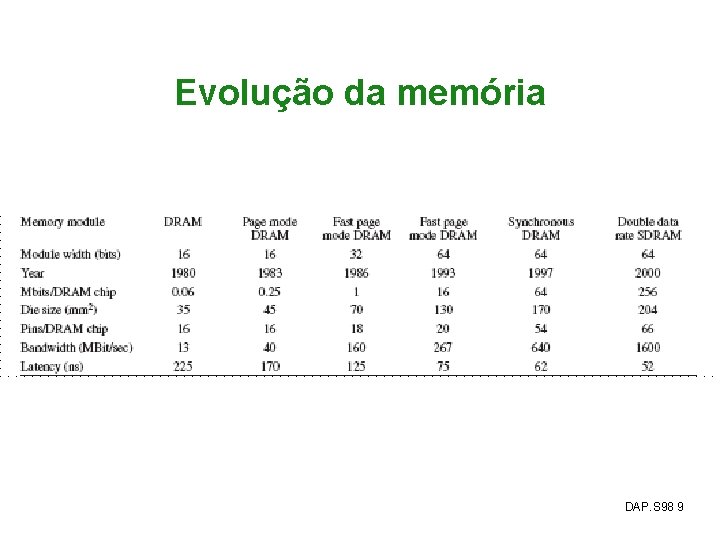

Evolução da memória DAP. S 98 9

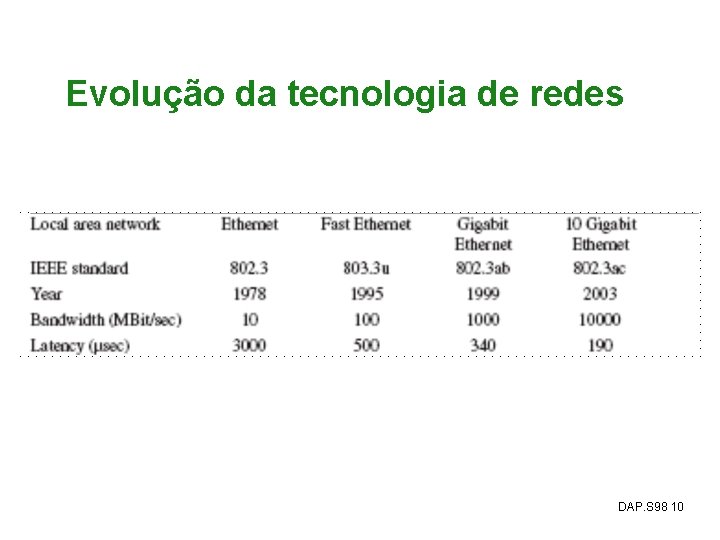

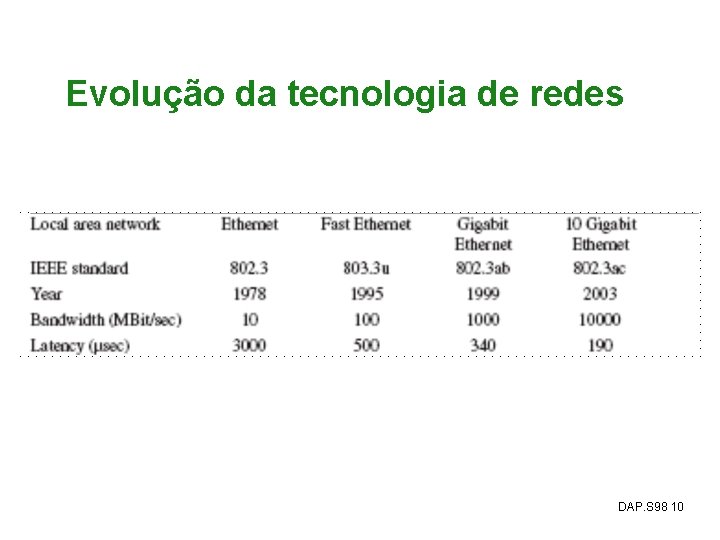

Evolução da tecnologia de redes DAP. S 98 10

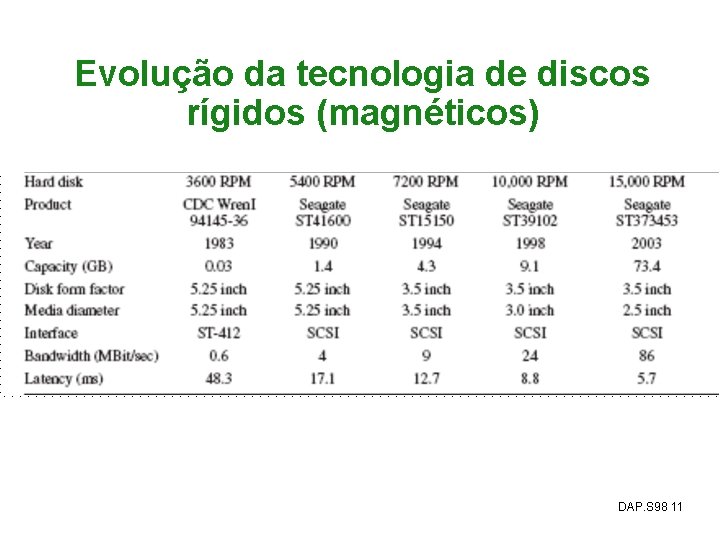

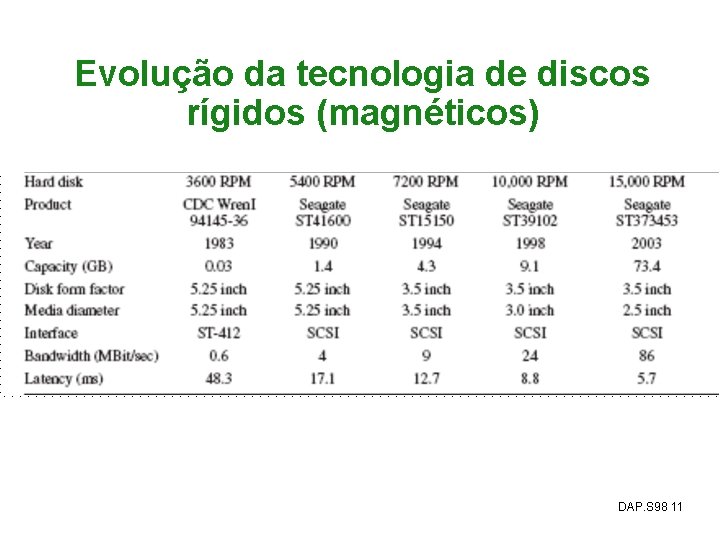

Evolução da tecnologia de discos rígidos (magnéticos) DAP. S 98 11

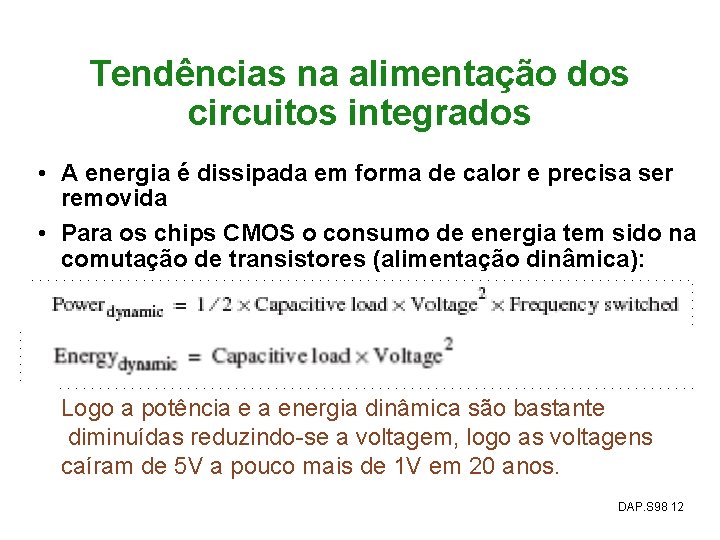

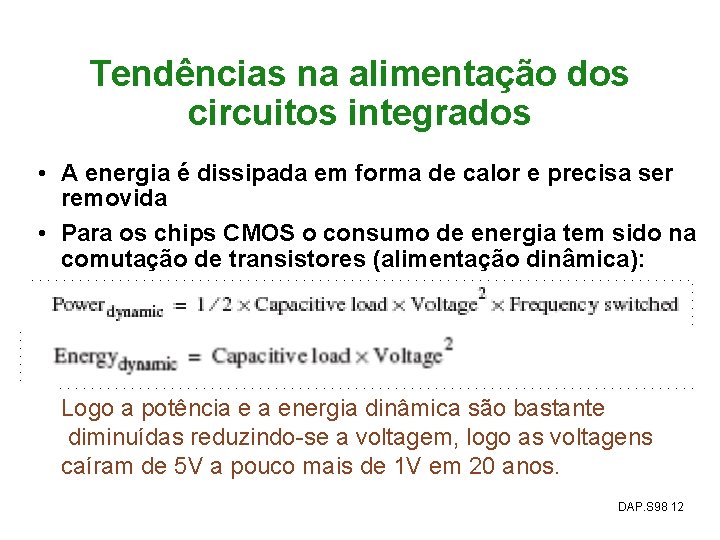

Tendências na alimentação dos circuitos integrados • A energia é dissipada em forma de calor e precisa ser removida • Para os chips CMOS o consumo de energia tem sido na comutação de transistores (alimentação dinâmica): Logo a potência e a energia dinâmica são bastante diminuídas reduzindo-se a voltagem, logo as voltagens caíram de 5 V a pouco mais de 1 V em 20 anos. DAP. S 98 12

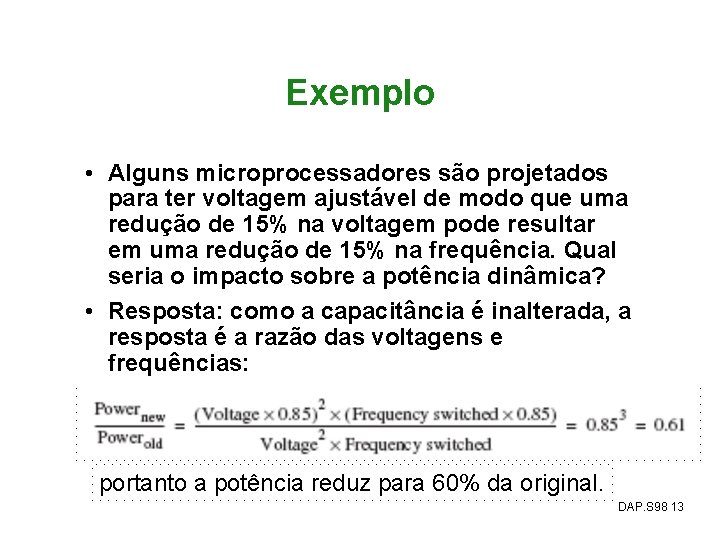

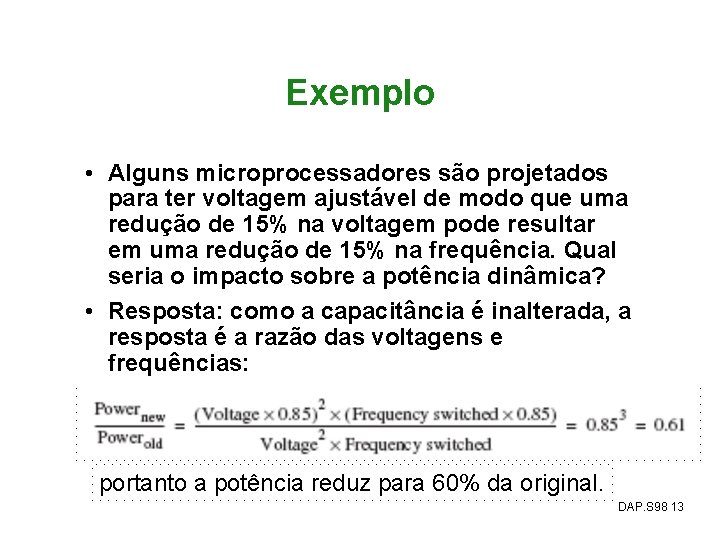

Exemplo • Alguns microprocessadores são projetados para ter voltagem ajustável de modo que uma redução de 15% na voltagem pode resultar em uma redução de 15% na frequência. Qual seria o impacto sobre a potência dinâmica? • Resposta: como a capacitância é inalterada, a resposta é a razão das voltagens e frequências: portanto a potência reduz para 60% da original. DAP. S 98 13

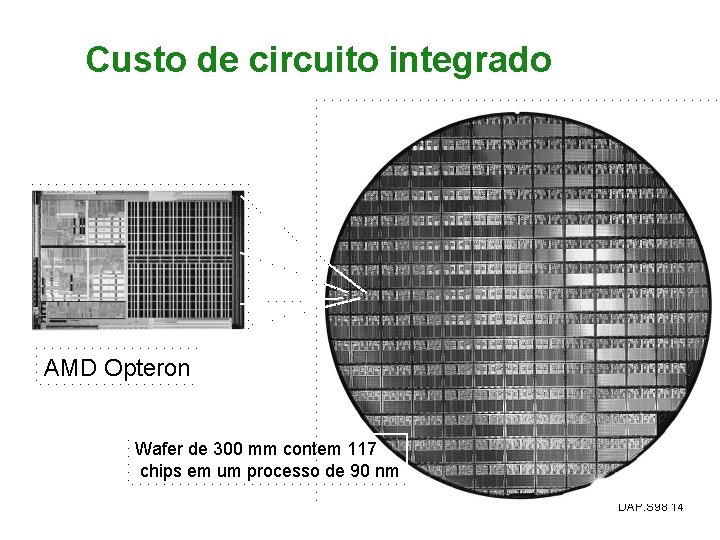

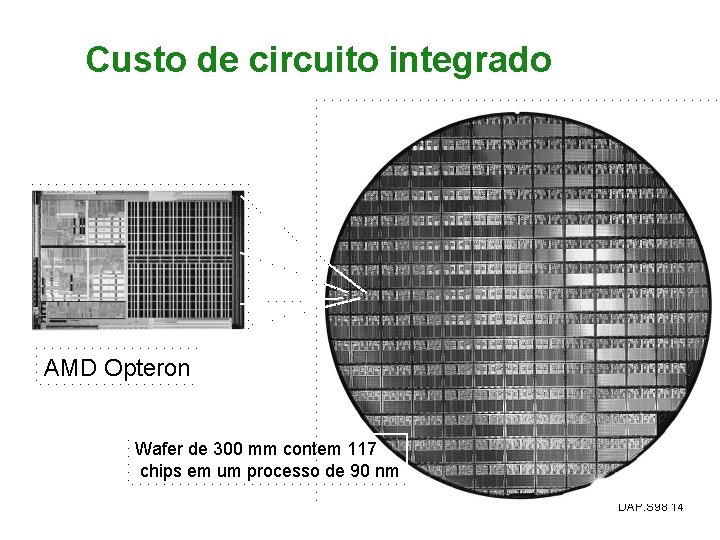

Custo de circuito integrado AMD Opteron Wafer de 300 mm contem 117 chips em um processo de 90 nm DAP. S 98 14

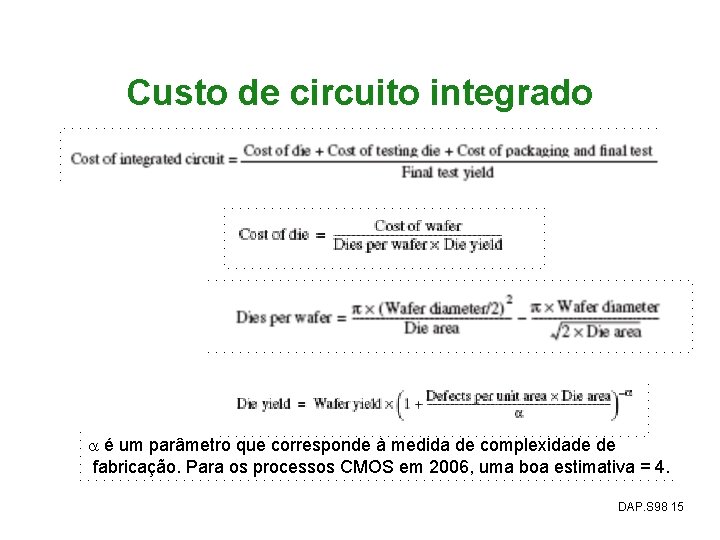

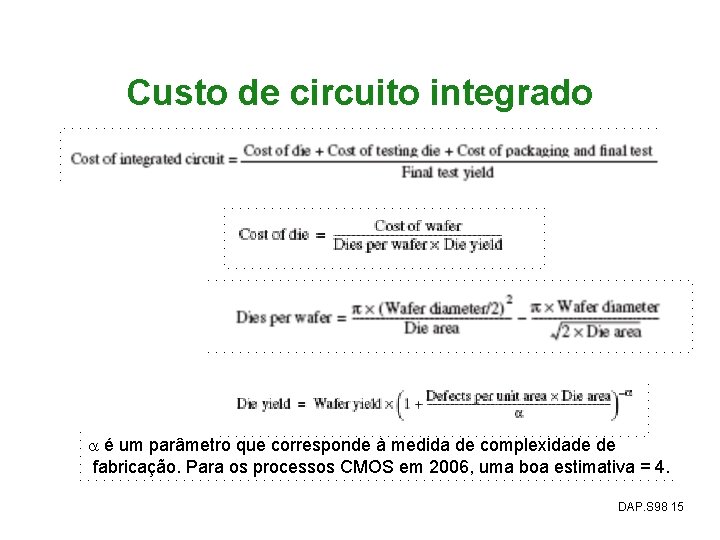

Custo de circuito integrado a é um parâmetro que corresponde à medida de complexidade de fabricação. Para os processos CMOS em 2006, uma boa estimativa = 4. DAP. S 98 15

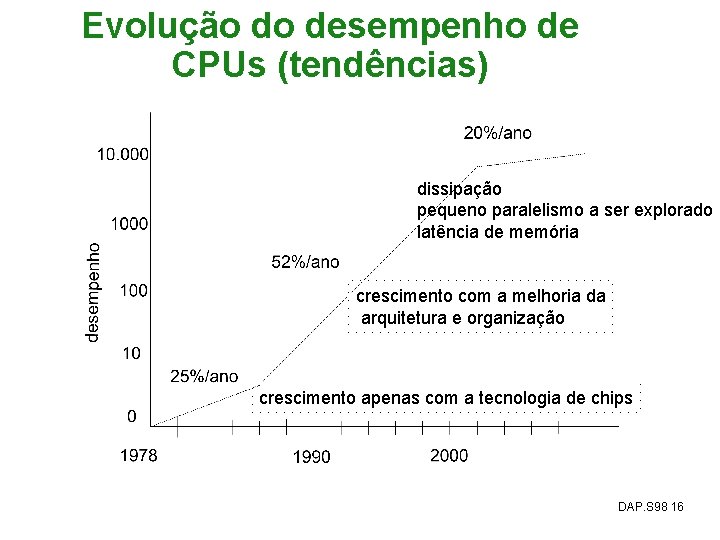

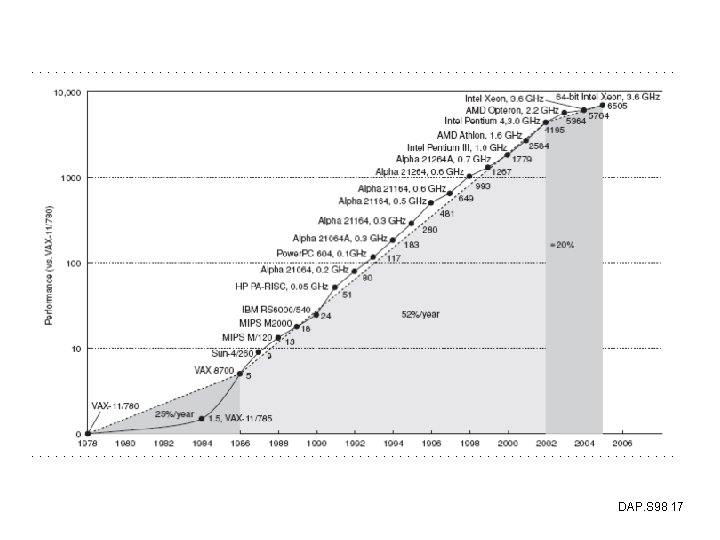

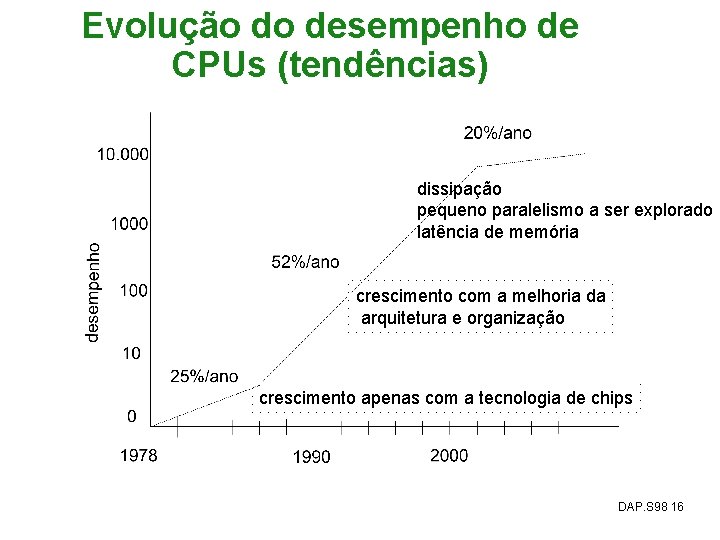

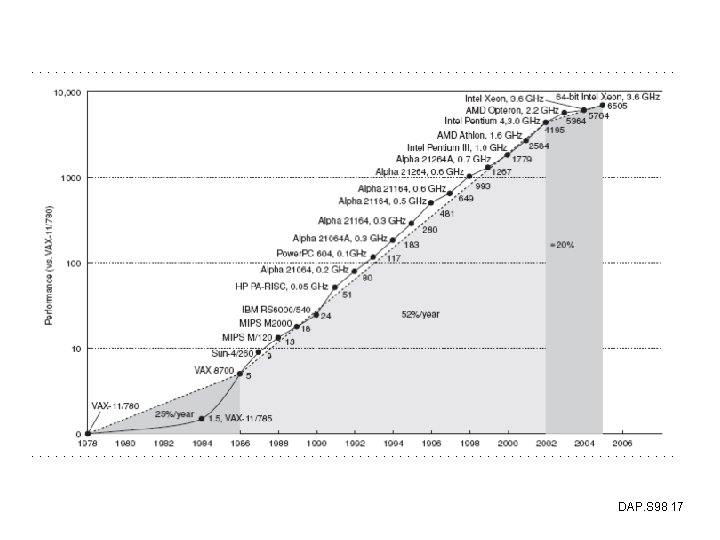

Evolução do desempenho de CPUs (tendências) dissipação pequeno paralelismo a ser explorado latência de memória crescimento com a melhoria da arquitetura e organização crescimento apenas com a tecnologia de chips DAP. S 98 16

DAP. S 98 17

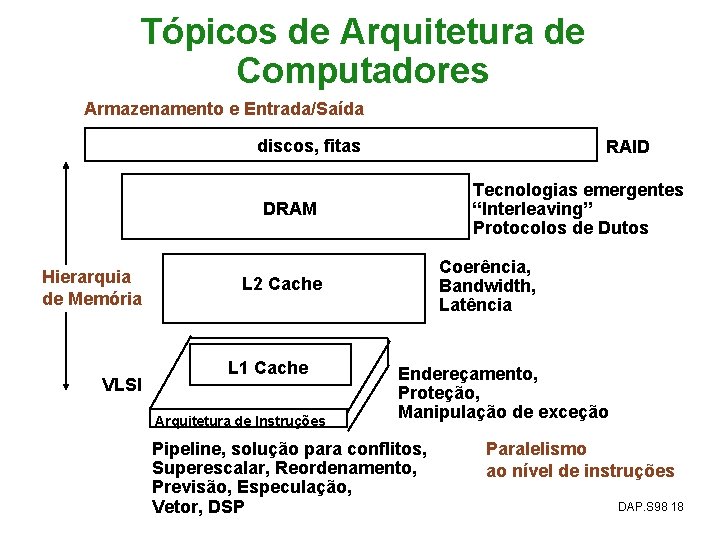

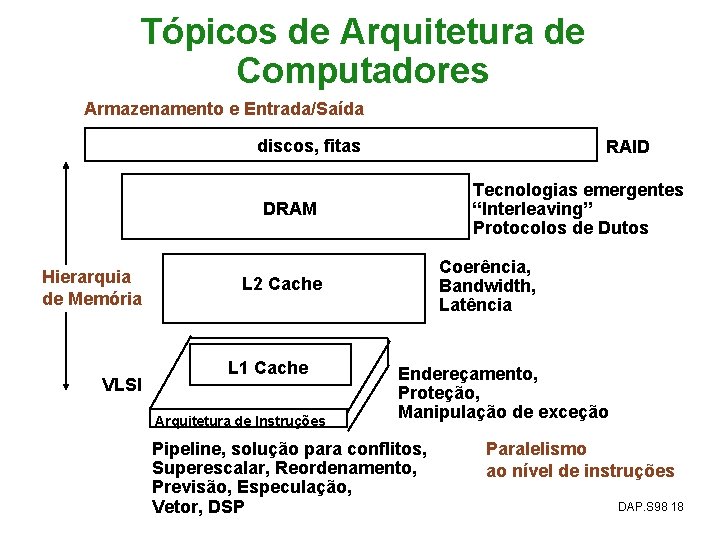

Tópicos de Arquitetura de Computadores Armazenamento e Entrada/Saída discos, fitas RAID Tecnologias emergentes “Interleaving” Protocolos de Dutos DRAM Hierarquia de Memória VLSI Coerência, Bandwidth, Latência L 2 Cache L 1 Cache Arquitetura de Instruções Endereçamento, Proteção, Manipulação de exceção Pipeline, solução para conflitos, Superescalar, Reordenamento, Previsão, Especulação, Vetor, DSP Paralelismo ao nível de instruções DAP. S 98 18

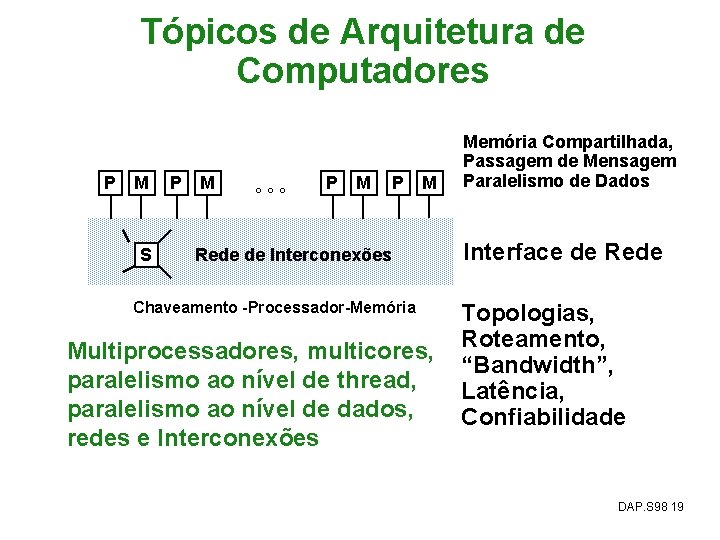

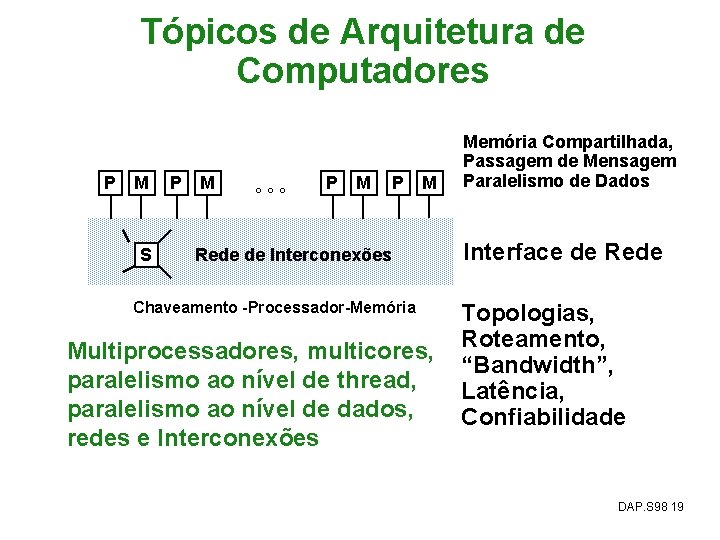

Tópicos de Arquitetura de Computadores P M S P M ° ° ° P M Rede de Interconexões Chaveamento -Processador-Memória Multiprocessadores, multicores, paralelismo ao nível de thread, paralelismo ao nível de dados, redes e Interconexões Memória Compartilhada, Passagem de Mensagem Paralelismo de Dados Interface de Rede Topologias, Roteamento, “Bandwidth”, Latência, Confiabilidade DAP. S 98 19

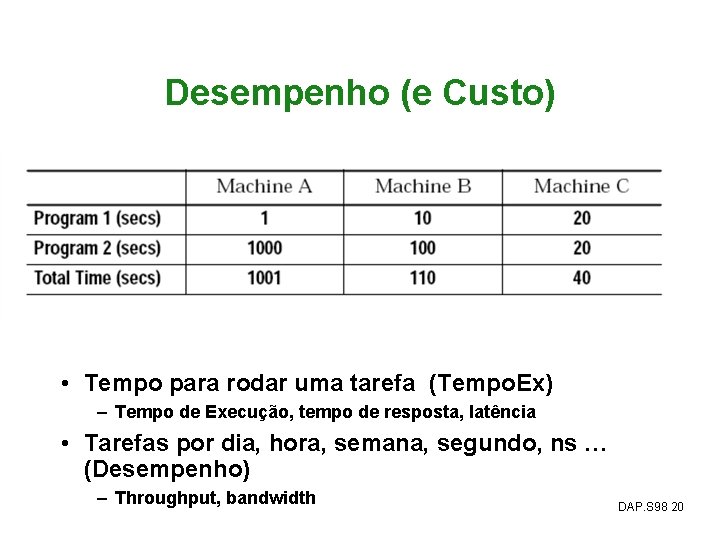

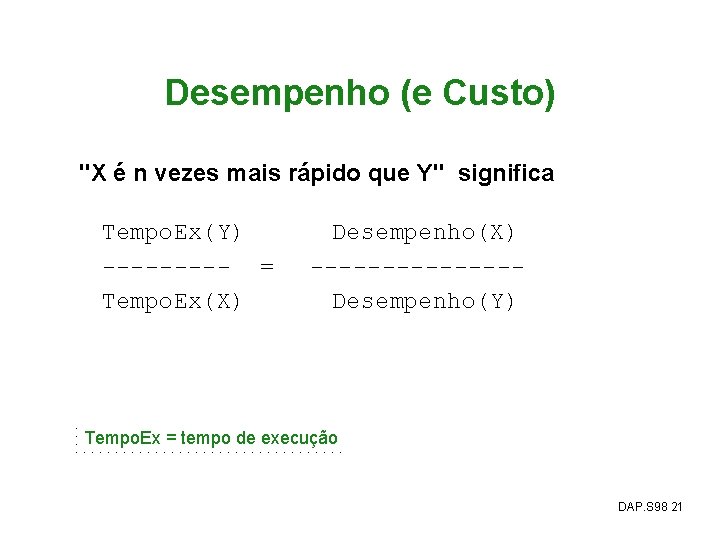

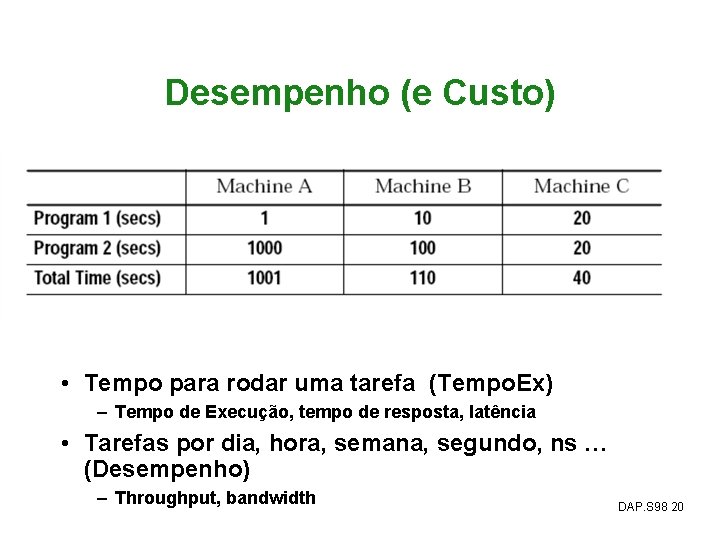

Desempenho (e Custo) • Tempo para rodar uma tarefa (Tempo. Ex) – Tempo de Execução, tempo de resposta, latência • Tarefas por dia, hora, semana, segundo, ns … (Desempenho) – Throughput, bandwidth DAP. S 98 20

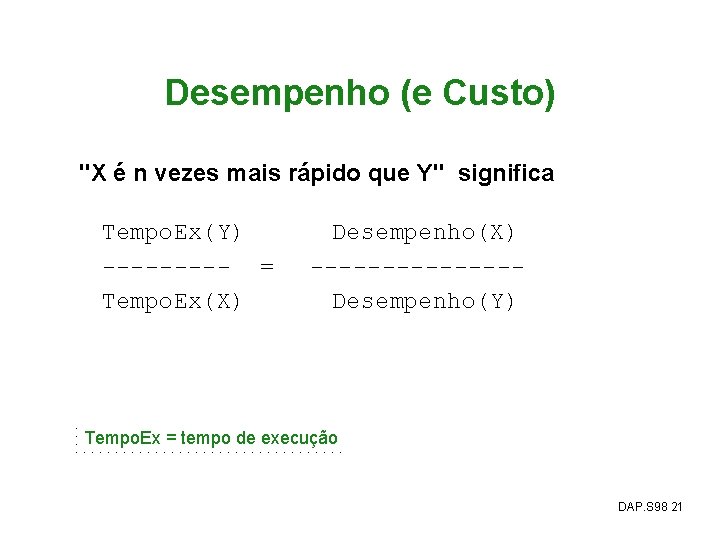

Desempenho (e Custo) "X é n vezes mais rápido que Y" significa Tempo. Ex(Y) ----- = Tempo. Ex(X) Desempenho(X) -------Desempenho(Y) Tempo. Ex = tempo de execução DAP. S 98 21

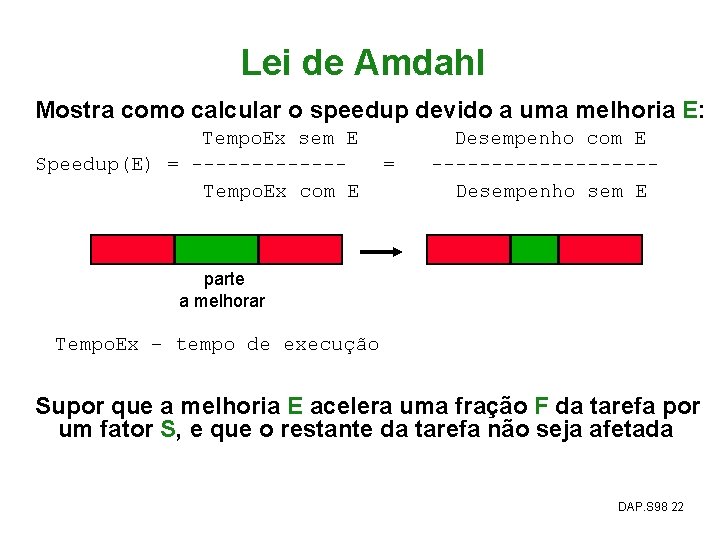

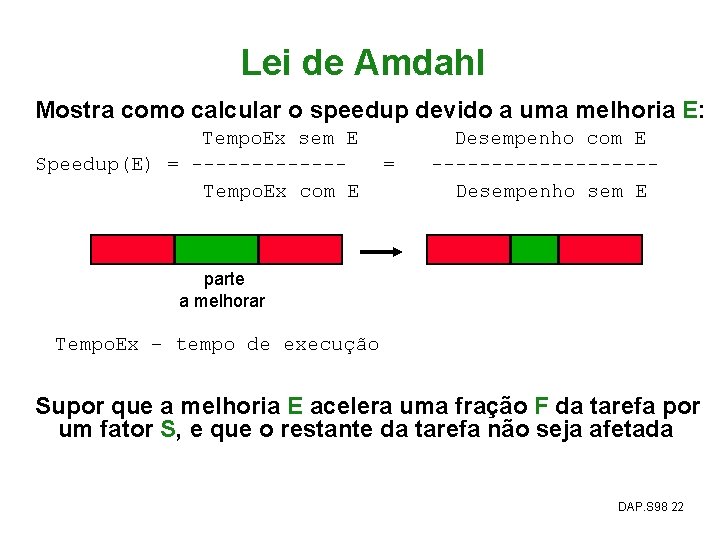

Lei de Amdahl Mostra como calcular o speedup devido a uma melhoria E: Tempo. Ex sem E Speedup(E) = ------Tempo. Ex com E = Desempenho com E ---------Desempenho sem E parte a melhorar Tempo. Ex – tempo de execução Supor que a melhoria E acelera uma fração F da tarefa por um fator S, e que o restante da tarefa não seja afetada DAP. S 98 22

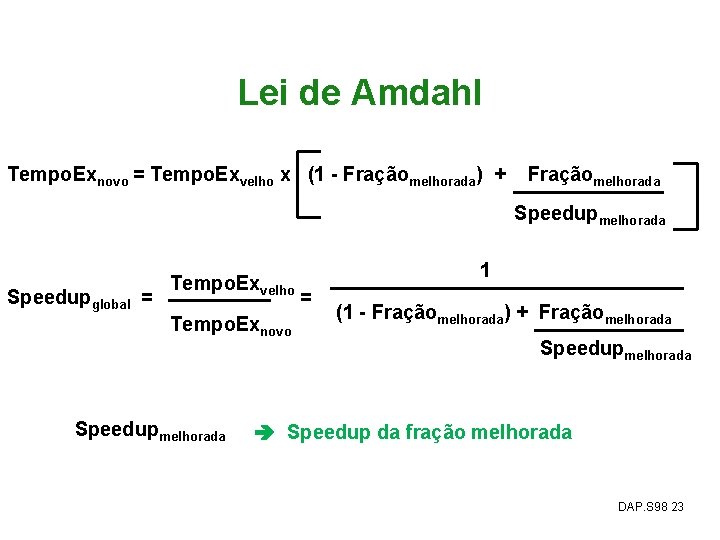

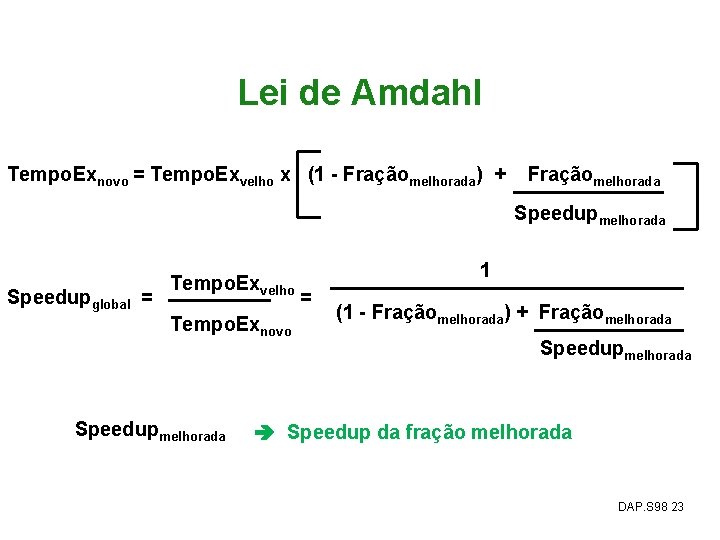

Lei de Amdahl Tempo. Exnovo = Tempo. Exvelho x (1 - Fraçãomelhorada) + Fraçãomelhorada Speedupglobal = Tempo. Exvelho Tempo. Exnovo Speedupmelhorada 1 = (1 - Fraçãomelhorada) + Fraçãomelhorada Speedup da fração melhorada DAP. S 98 23

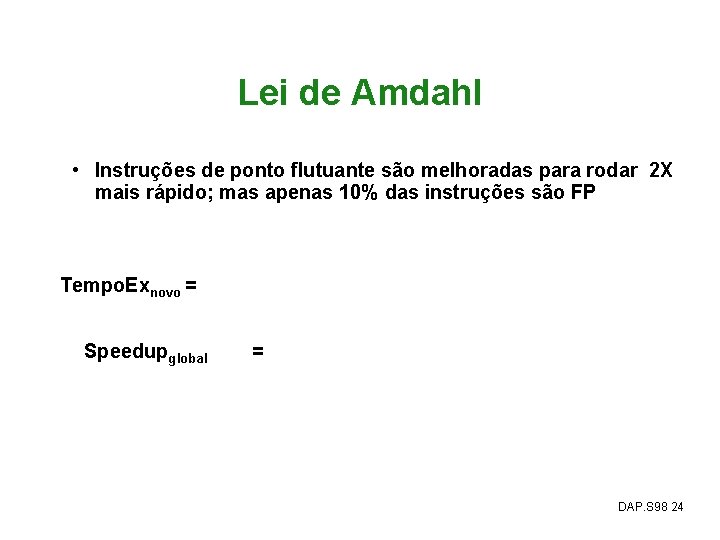

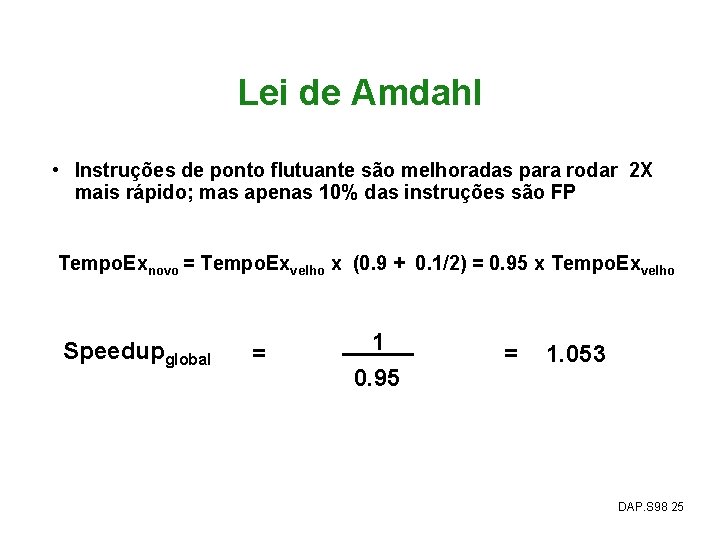

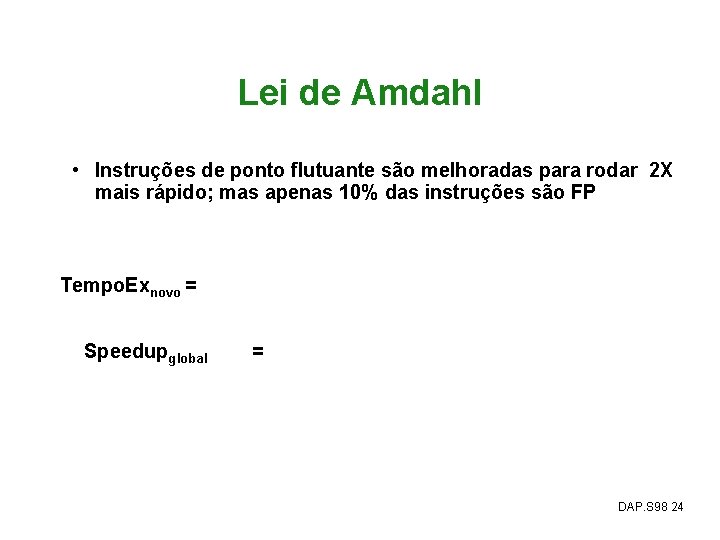

Lei de Amdahl • Instruções de ponto flutuante são melhoradas para rodar 2 X mais rápido; mas apenas 10% das instruções são FP Tempo. Exnovo = Speedupglobal = DAP. S 98 24

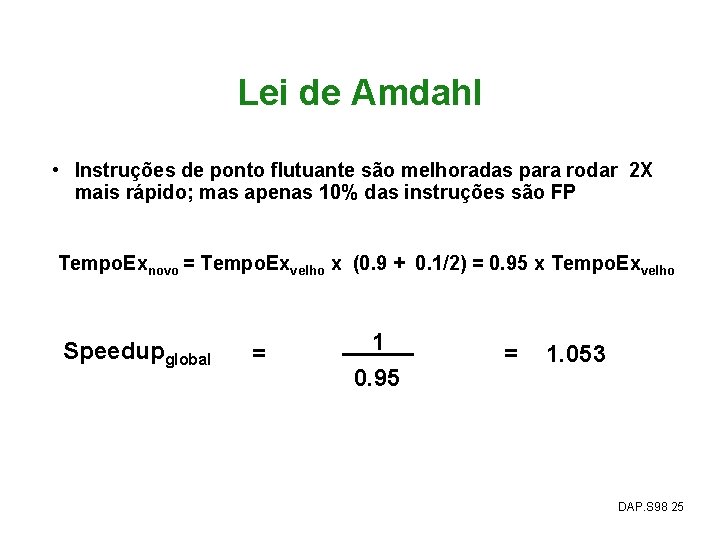

Lei de Amdahl • Instruções de ponto flutuante são melhoradas para rodar 2 X mais rápido; mas apenas 10% das instruções são FP Tempo. Exnovo = Tempo. Exvelho x (0. 9 + 0. 1/2) = 0. 95 x Tempo. Exvelho Speedupglobal = 1 0. 95 = 1. 053 DAP. S 98 25

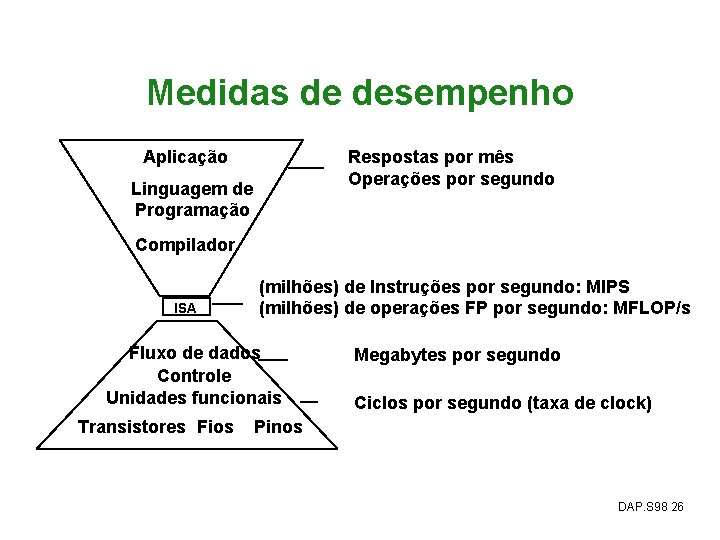

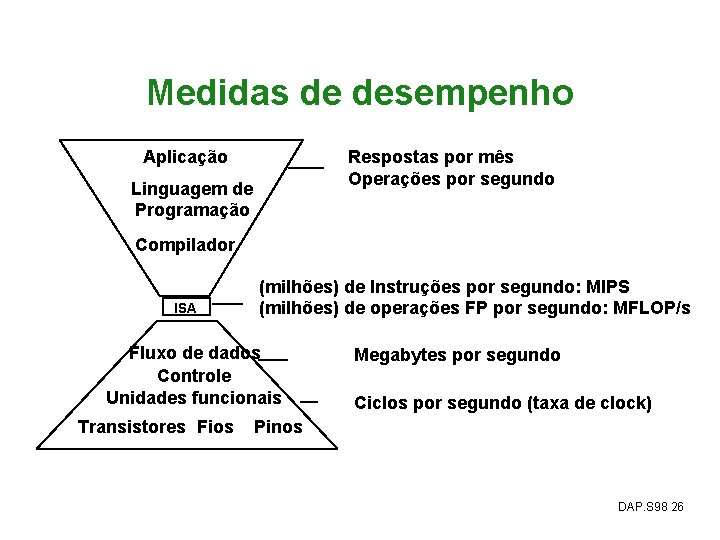

Medidas de desempenho Aplicação Respostas por mês Operações por segundo Linguagem de Programação Compilador ISA (milhões) de Instruções por segundo: MIPS (milhões) de operações FP por segundo: MFLOP/s Fluxo de dados Controle Unidades funcionais Transistores Fios Megabytes por segundo Ciclos por segundo (taxa de clock) Pinos DAP. S 98 26

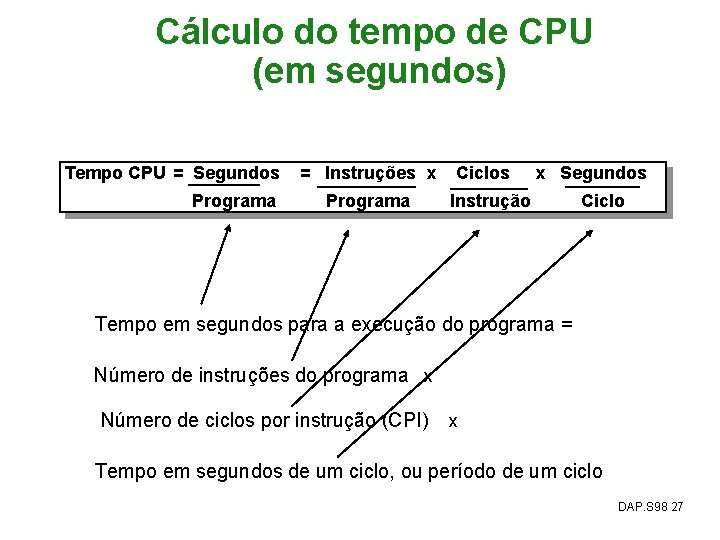

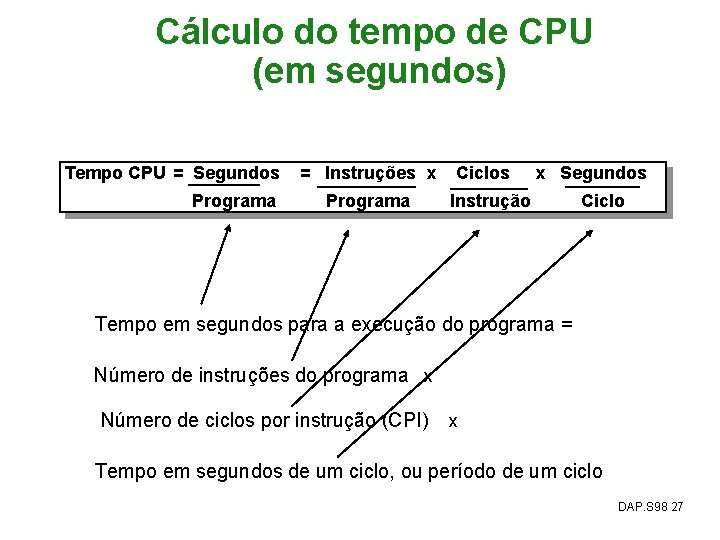

Cálculo do tempo de CPU (em segundos) Tempo CPU = Segundos = Instruções x Ciclos x Segundos Programa Instrução Ciclo Tempo em segundos para a execução do programa = Número de instruções do programa x Número de ciclos por instrução (CPI) x Tempo em segundos de um ciclo, ou período de um ciclo DAP. S 98 27

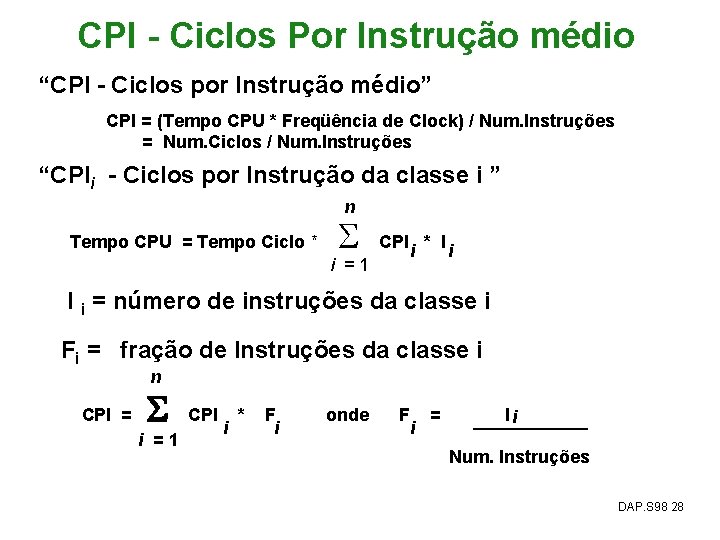

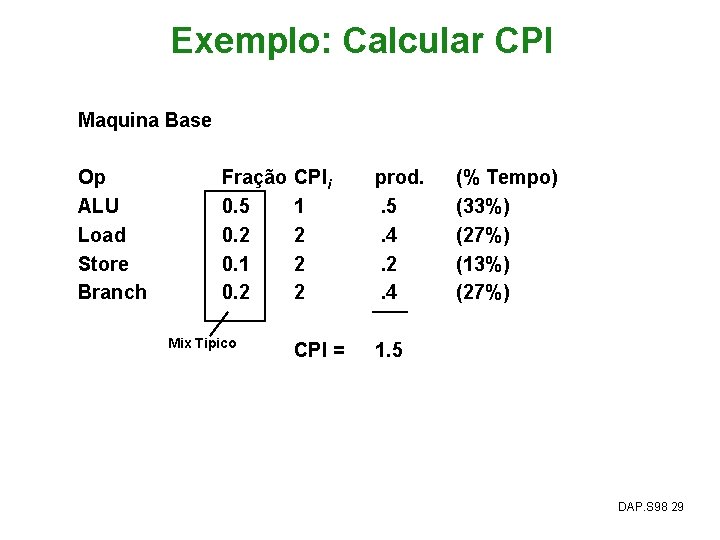

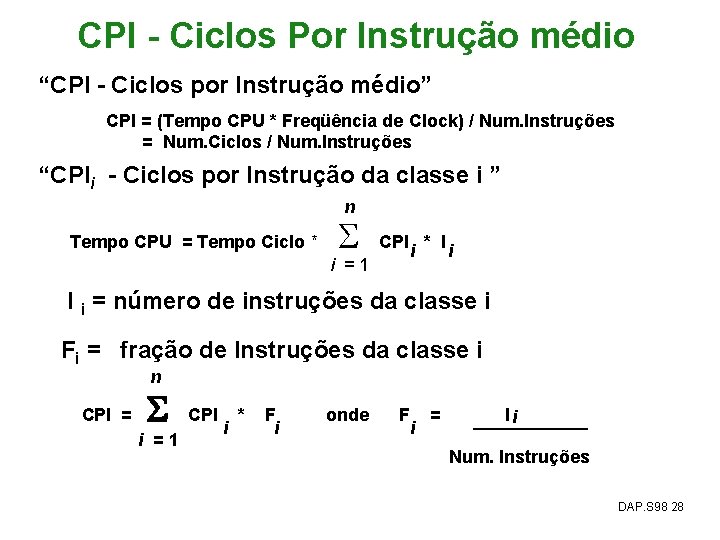

CPI - Ciclos Por Instrução médio “CPI - Ciclos por Instrução médio” CPI = (Tempo CPU * Freqüência de Clock) / Num. Instruções = Num. Ciclos / Num. Instruções “CPIi - Ciclos por Instrução da classe i ” n Tempo CPU = Tempo Ciclo * S i =1 CPI * I i i I i = número de instruções da classe i Fi = fração de Instruções da classe i n S CPI = CPI * F onde F = I i i i = 1 Num. Instruções DAP. S 98 28

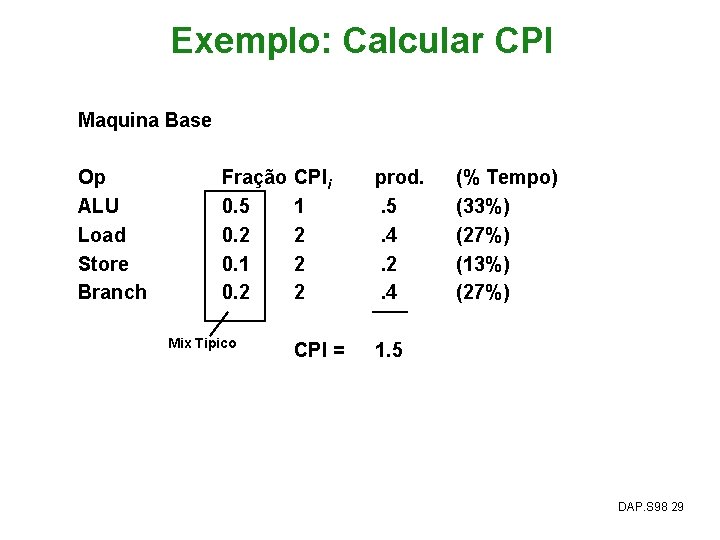

Exemplo: Calcular CPI Maquina Base Op ALU Load Store Branch Fração CPIi 0. 5 1 0. 2 2 0. 1 2 0. 2 2 Mix Tipico CPI = prod. . 5 . 4 . 2 . 4 (% Tempo) (33%) (27%) (13%) (27%) 1. 5 DAP. S 98 29

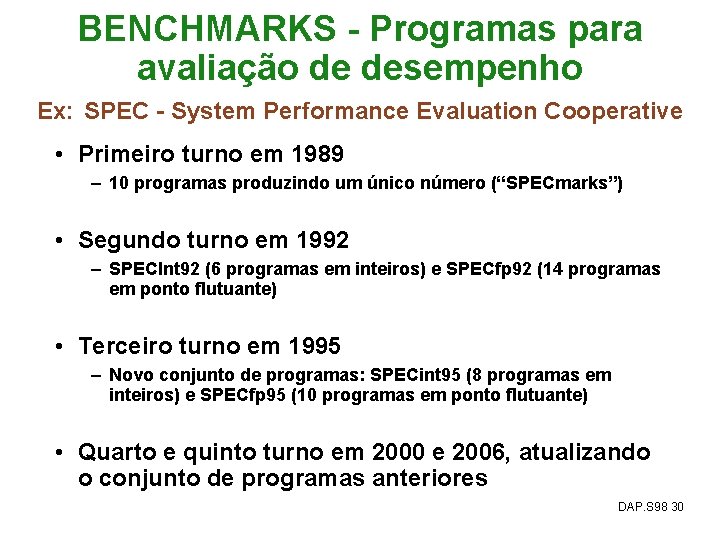

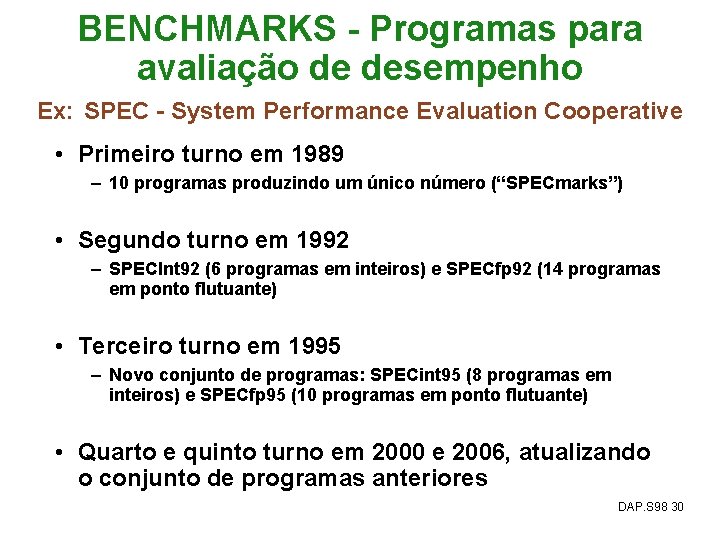

BENCHMARKS - Programas para avaliação de desempenho Ex: SPEC - System Performance Evaluation Cooperative • Primeiro turno em 1989 – 10 programas produzindo um único número (“SPECmarks”) • Segundo turno em 1992 – SPECInt 92 (6 programas em inteiros) e SPECfp 92 (14 programas em ponto flutuante) • Terceiro turno em 1995 – Novo conjunto de programas: SPECint 95 (8 programas em inteiros) e SPECfp 95 (10 programas em ponto flutuante) • Quarto e quinto turno em 2000 e 2006, atualizando o conjunto de programas anteriores DAP. S 98 30

SPEC CPU 2006 • CINT 2006 para medir e comparar o desempenho de processamento de inteiros, e (http: //www. spec. org/cpu 2006/CINT 2006/) • CFP 2006 para medir e comparar o desempenho de processamento pontoflutuante. (http: //www. spec. org/cpu 2006/CFP 2006/) DAP. S 98 31

Instruction Set Architecture (ISA) software instruction set hardware DAP. S 98 32

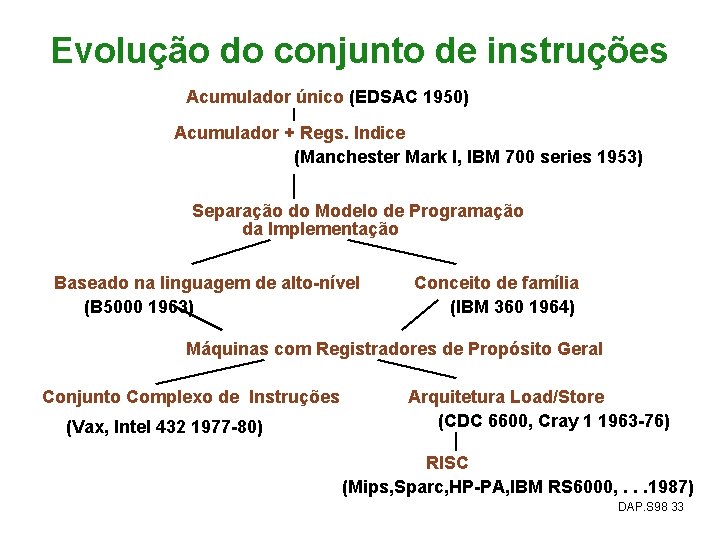

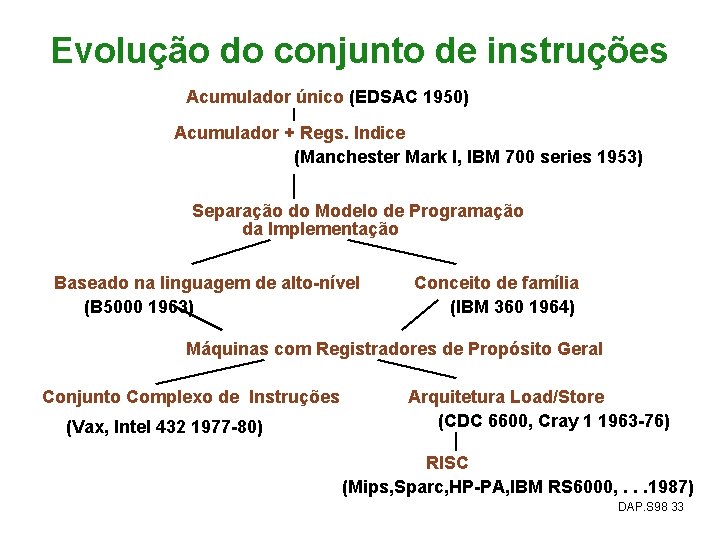

Evolução do conjunto de instruções Acumulador único (EDSAC 1950) Acumulador + Regs. Indice (Manchester Mark I, IBM 700 series 1953) Separação do Modelo de Programação da Implementação Baseado na linguagem de alto-nível (B 5000 1963) Conceito de família (IBM 360 1964) Máquinas com Registradores de Propósito Geral Conjunto Complexo de Instruções (Vax, Intel 432 1977 -80) Arquitetura Load/Store (CDC 6600, Cray 1 1963 -76) RISC (Mips, Sparc, HP-PA, IBM RS 6000, . . . 1987) DAP. S 98 33

Evolução do conjunto de Instruções • Os avanços importantes na arquitetura de computadores são tipicamente associados aos marcos no projeto do conjunto de instruções – Ex: Pilhas vs Registradores de Uso Geral (System 360) • As decisões de projeto devem levar em conta: – – – Tecnologia Organização de máquina Linguagens de programação Tecnologia de compilador Sistemas operacionais • E essas decisões, por seu lado, os influenciam DAP. S 98 34

Tipos de arquiteturas do conjunto de instruções quanto ao uso de operandos em instruções aritméticas a) pilha b) acumulador c) registrador-memória d) registrador-registrador DAP. S 98 35

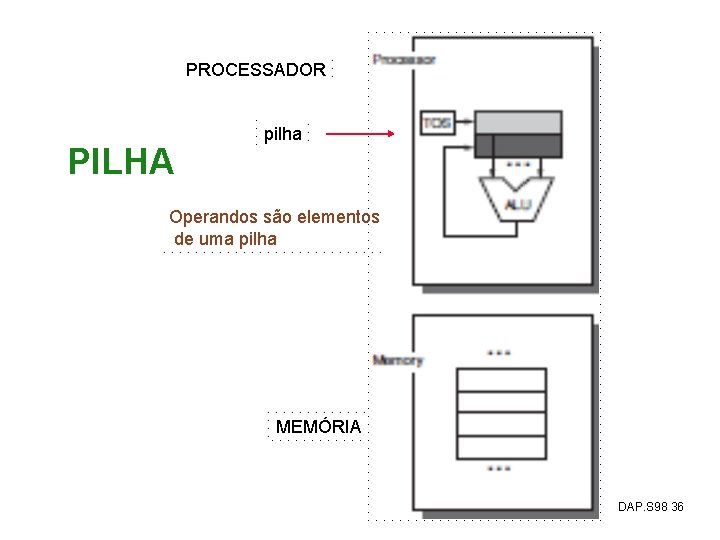

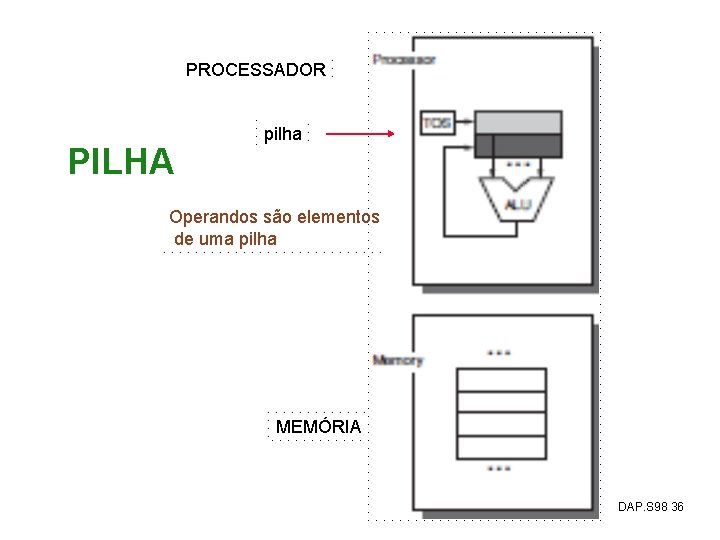

PROCESSADOR PILHA pilha Operandos são elementos de uma pilha MEMÓRIA DAP. S 98 36

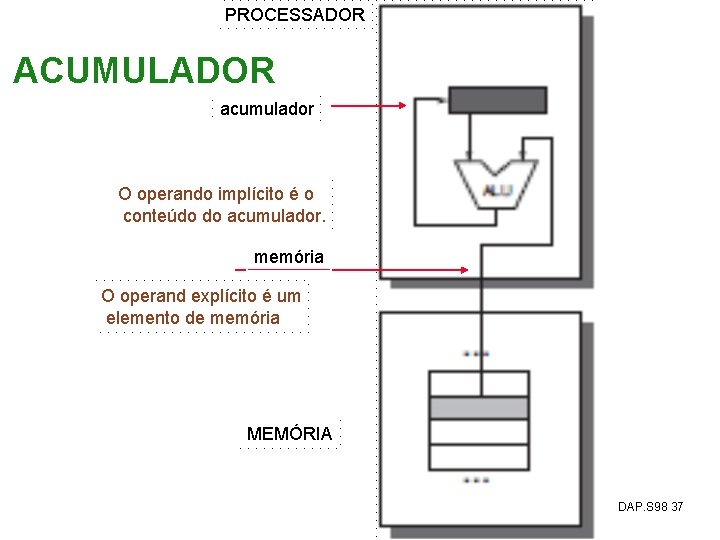

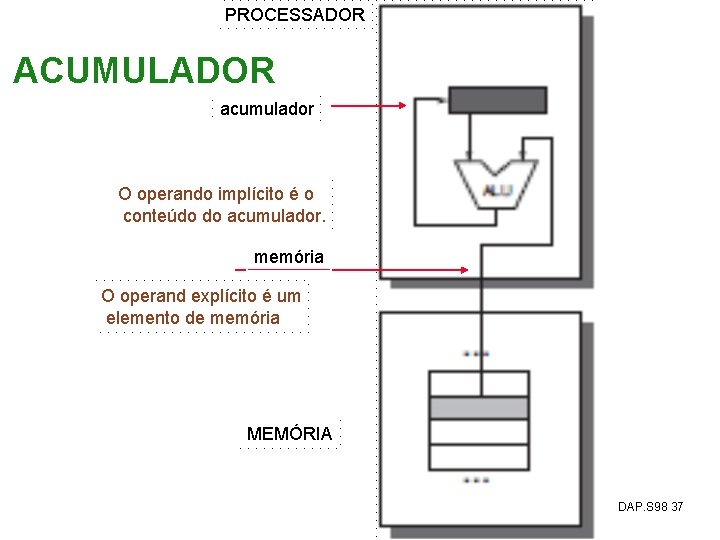

PROCESSADOR ACUMULADOR acumulador O operando implícito é o conteúdo do acumulador. memória O operand explícito é um elemento de memória MEMÓRIA DAP. S 98 37

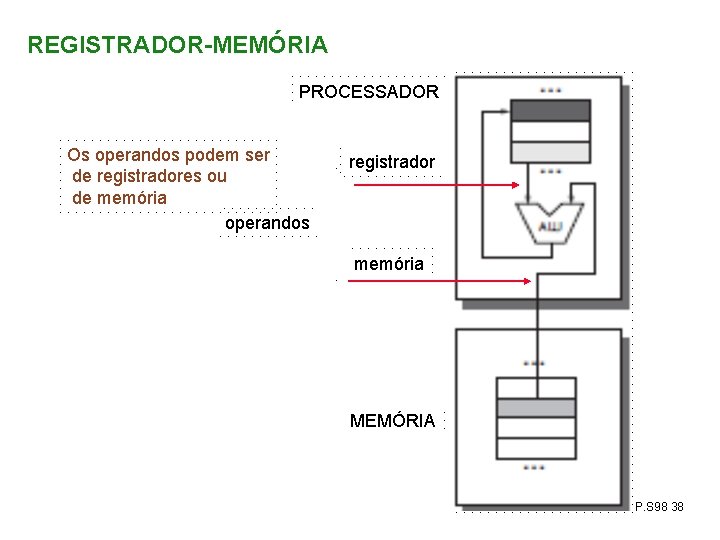

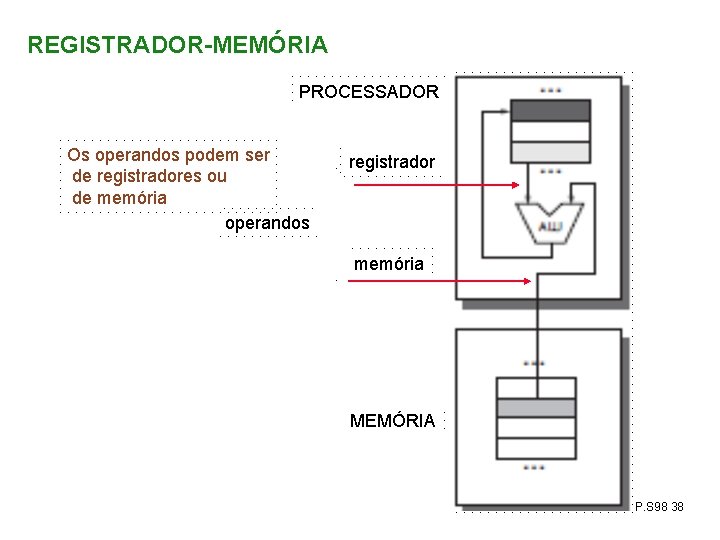

REGISTRADOR-MEMÓRIA PROCESSADOR Os operandos podem ser de registradores ou de memória operandos registrador memória MEMÓRIA DAP. S 98 38

PROCESSADOR Operandos registrador load REGISTRADOR-REGISTRADOR (LOAD-STORE) Os operandos são de registradores MEMÓRIA store DAP. S 98 39

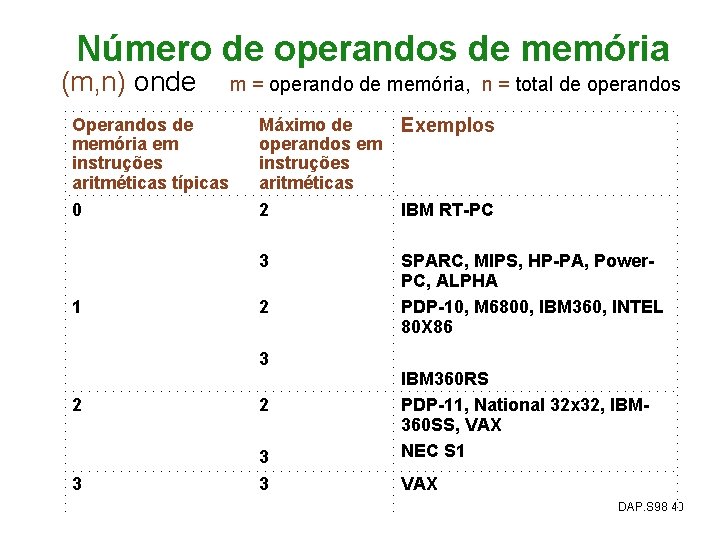

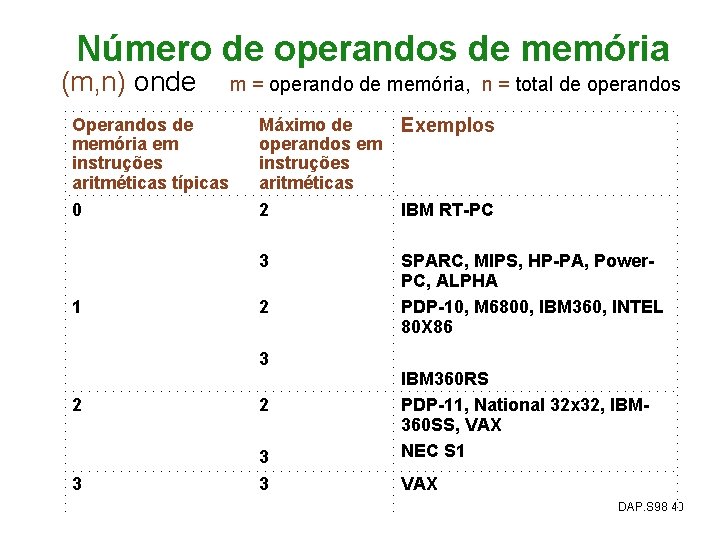

Número de operandos de memória (m, n) onde Operandos de memória em instruções aritméticas típicas 0 m = operando de memória, n = total de operandos Máximo de Exemplos operandos em instruções aritméticas 2 IBM RT-PC 3 1 2 3 2 2 3 3 3 SPARC, MIPS, HP-PA, Power. PC, ALPHA PDP-10, M 6800, IBM 360, INTEL 80 X 86 IBM 360 RS PDP-11, National 32 x 32, IBM 360 SS, VAX NEC S 1 VAX DAP. S 98 40

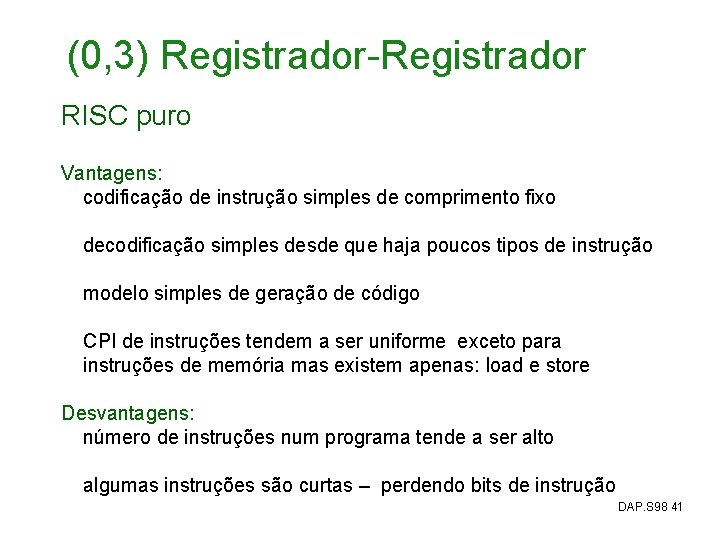

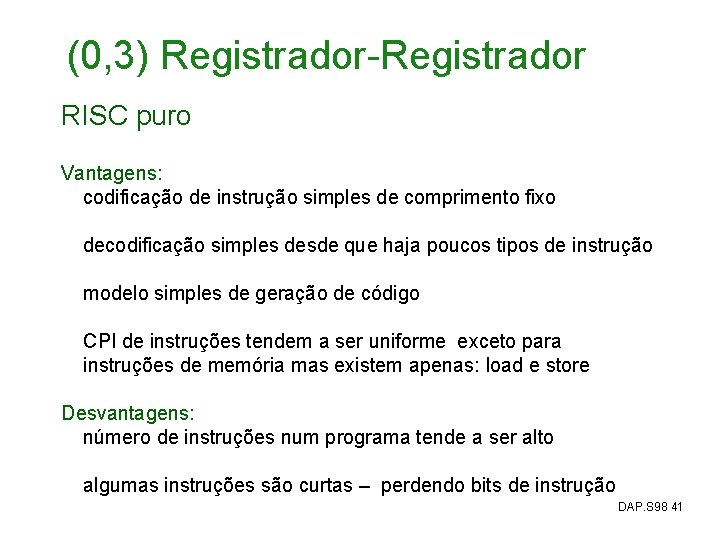

(0, 3) Registrador-Registrador RISC puro Vantagens: codificação de instrução simples de comprimento fixo decodificação simples desde que haja poucos tipos de instrução modelo simples de geração de código CPI de instruções tendem a ser uniforme exceto para instruções de memória mas existem apenas: load e store Desvantagens: número de instruções num programa tende a ser alto algumas instruções são curtas – perdendo bits de instrução DAP. S 98 41

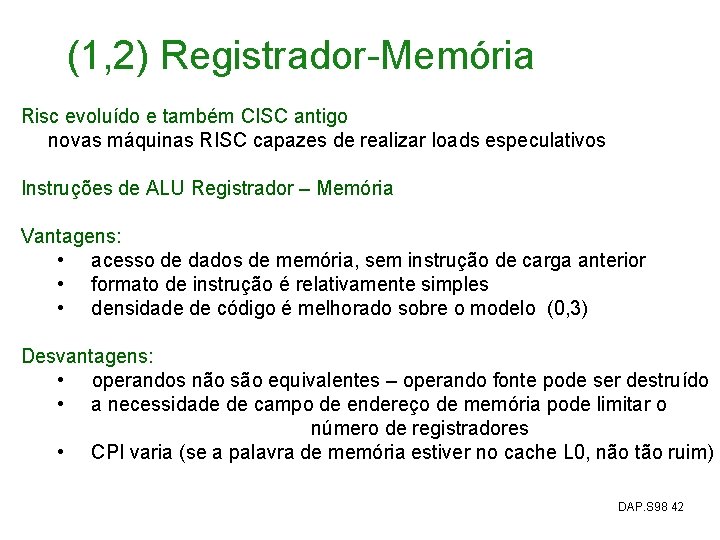

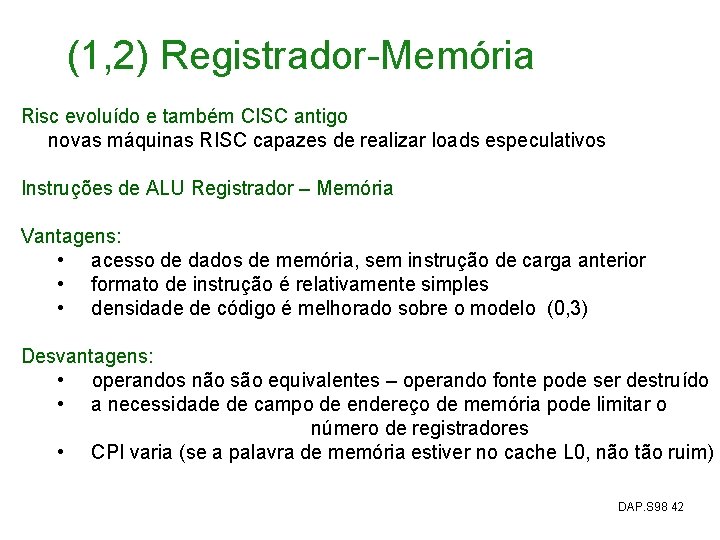

(1, 2) Registrador-Memória Risc evoluído e também CISC antigo novas máquinas RISC capazes de realizar loads especulativos Instruções de ALU Registrador – Memória Vantagens: • acesso de dados de memória, sem instrução de carga anterior • formato de instrução é relativamente simples • densidade de código é melhorado sobre o modelo (0, 3) Desvantagens: • operandos não são equivalentes – operando fonte pode ser destruído • a necessidade de campo de endereço de memória pode limitar o número de registradores • CPI varia (se a palavra de memória estiver no cache L 0, não tão ruim) DAP. S 98 42

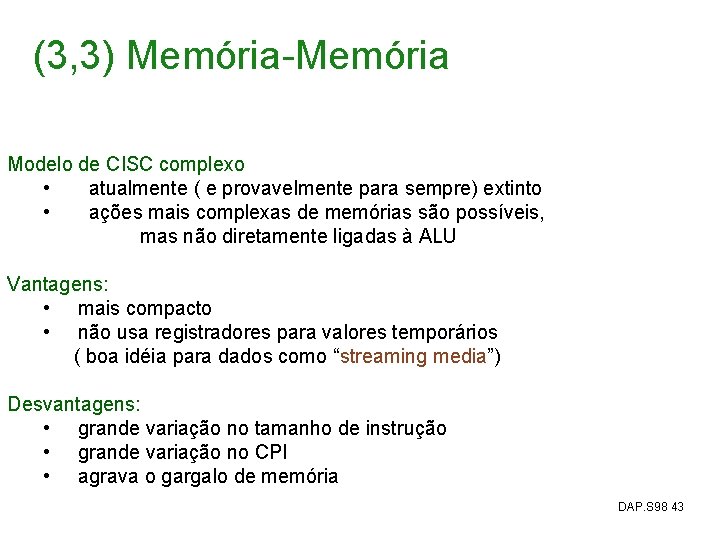

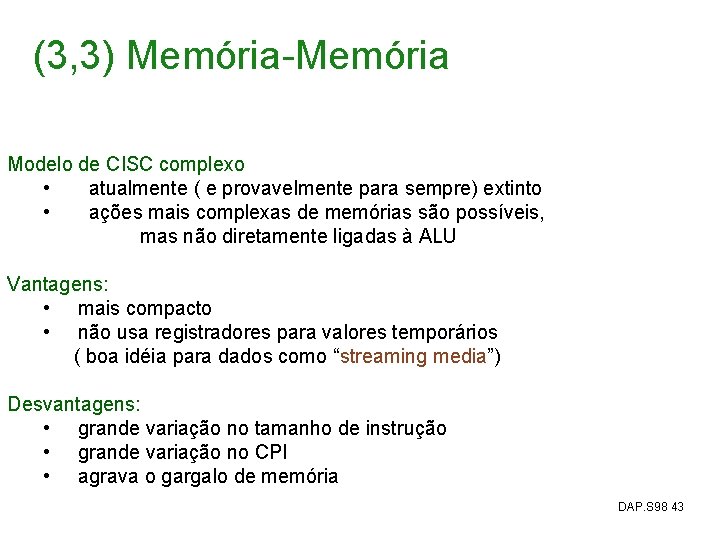

(3, 3) Memória-Memória Modelo de CISC complexo • atualmente ( e provavelmente para sempre) extinto • ações mais complexas de memórias são possíveis, mas não diretamente ligadas à ALU Vantagens: • mais compacto • não usa registradores para valores temporários ( boa idéia para dados como “streaming media”) Desvantagens: • grande variação no tamanho de instrução • grande variação no CPI • agrava o gargalo de memória DAP. S 98 43

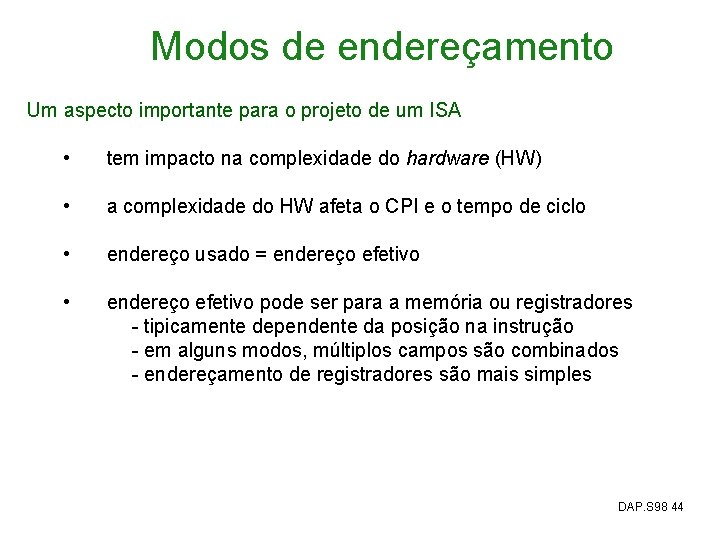

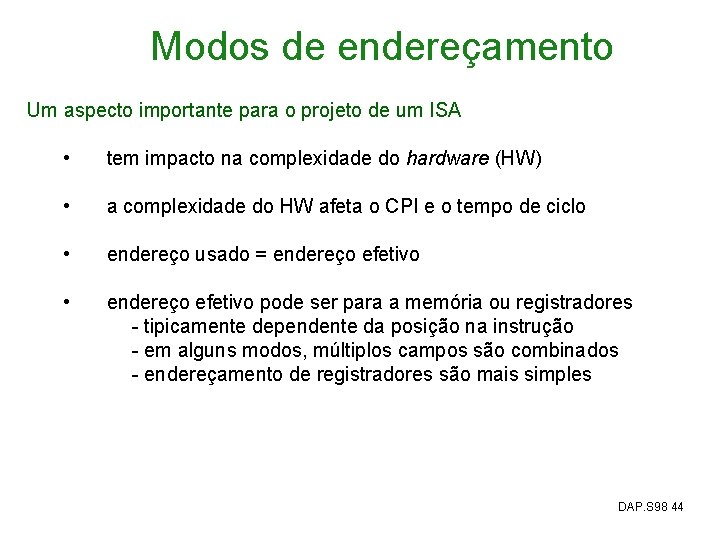

Modos de endereçamento Um aspecto importante para o projeto de um ISA • tem impacto na complexidade do hardware (HW) • a complexidade do HW afeta o CPI e o tempo de ciclo • endereço usado = endereço efetivo • endereço efetivo pode ser para a memória ou registradores - tipicamente dependente da posição na instrução - em alguns modos, múltiplos campos são combinados - endereçamento de registradores são mais simples DAP. S 98 44

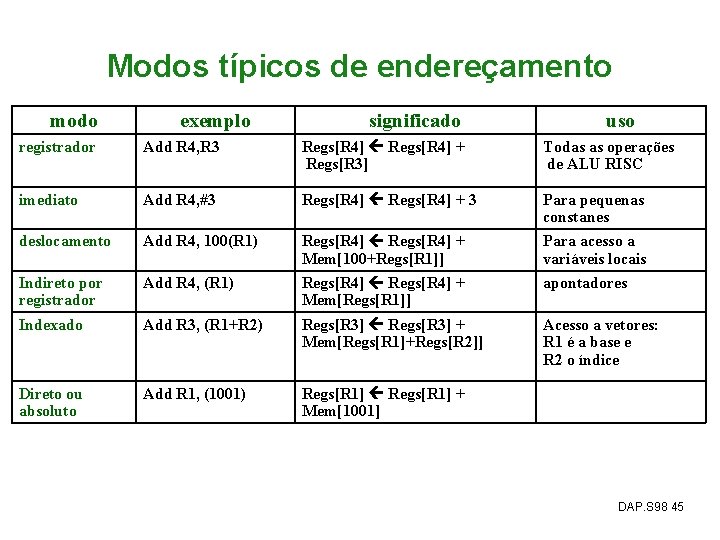

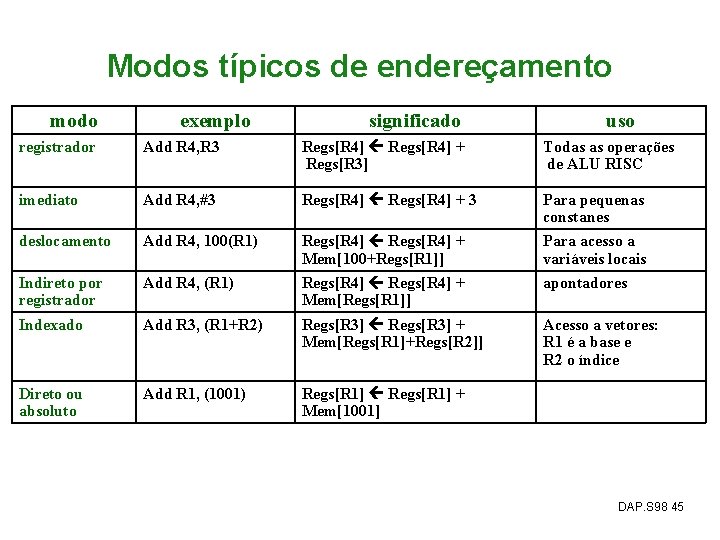

Modos típicos de endereçamento modo exemplo significado uso registrador Add R 4, R 3 Regs[R 4] + Regs[R 3] Todas as operações de ALU RISC imediato Add R 4, #3 Regs[R 4] + 3 Para pequenas constanes deslocamento Add R 4, 100(R 1) Regs[R 4] + Mem[100+Regs[R 1]] Para acesso a variáveis locais Indireto por registrador Add R 4, (R 1) Regs[R 4] + Mem[Regs[R 1]] apontadores Indexado Add R 3, (R 1+R 2) Regs[R 3] + Mem[Regs[R 1]+Regs[R 2]] Acesso a vetores: R 1 é a base e R 2 o índice Direto ou absoluto Add R 1, (1001) Regs[R 1] + Mem[1001] DAP. S 98 45

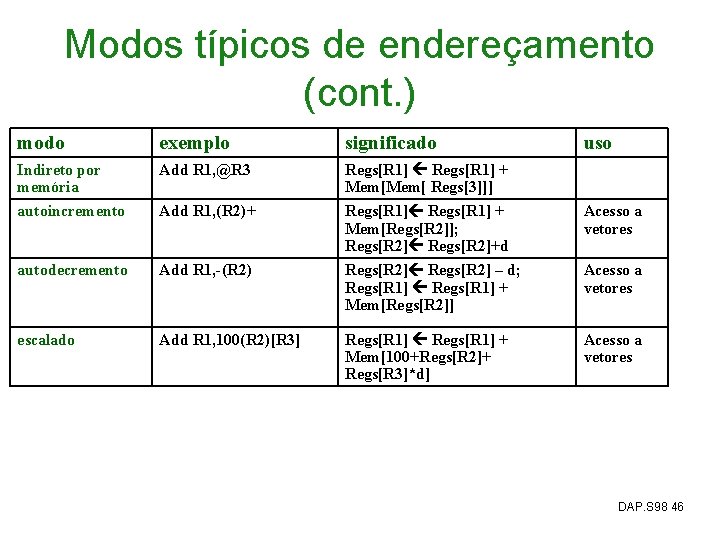

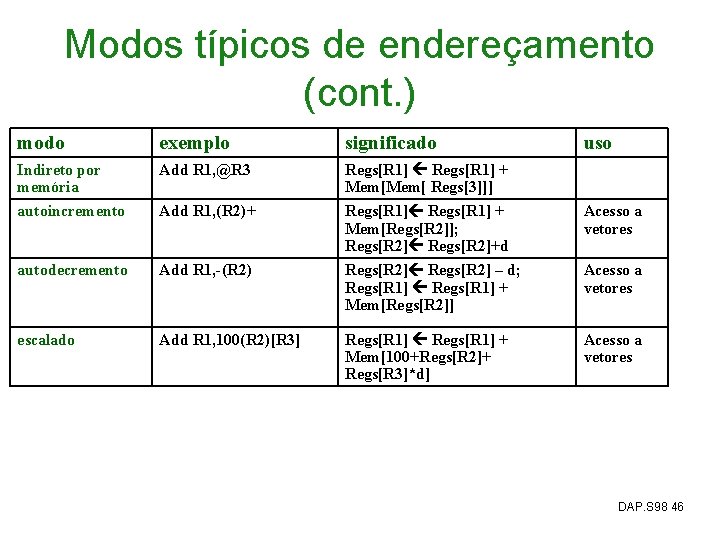

Modos típicos de endereçamento (cont. ) modo exemplo significado uso Indireto por memória Add R 1, @R 3 Regs[R 1] + Mem[ Regs[3]]] autoincremento Add R 1, (R 2)+ Regs[R 1] + Mem[Regs[R 2]]; Regs[R 2]+d Acesso a vetores autodecremento Add R 1, -(R 2) Regs[R 2] – d; Regs[R 1] + Mem[Regs[R 2]] Acesso a vetores escalado Add R 1, 100(R 2)[R 3] Regs[R 1] + Mem[100+Regs[R 2]+ Regs[R 3]*d] Acesso a vetores DAP. S 98 46

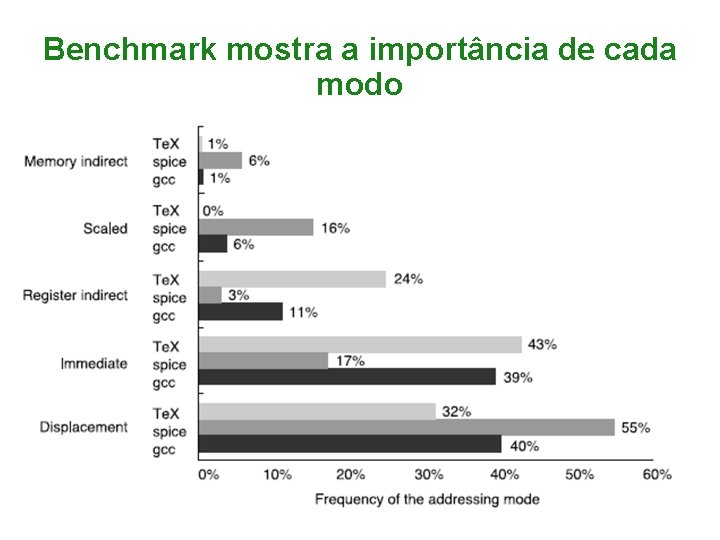

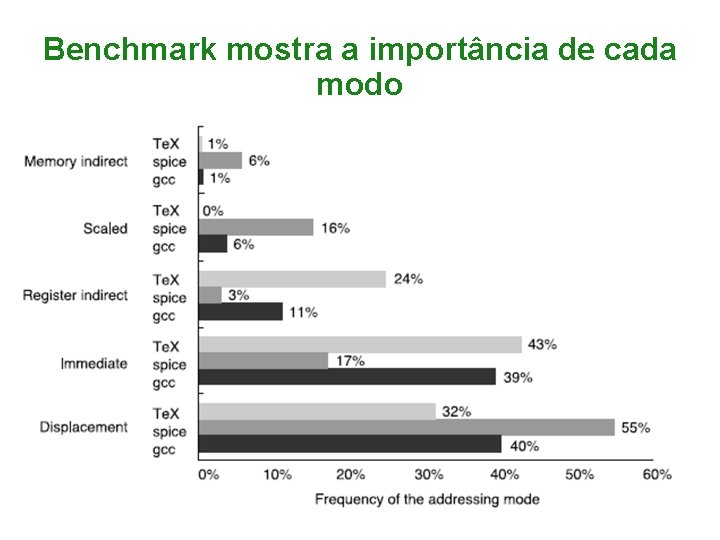

Benchmark mostra a importância de cada modo DAP. S 98 47

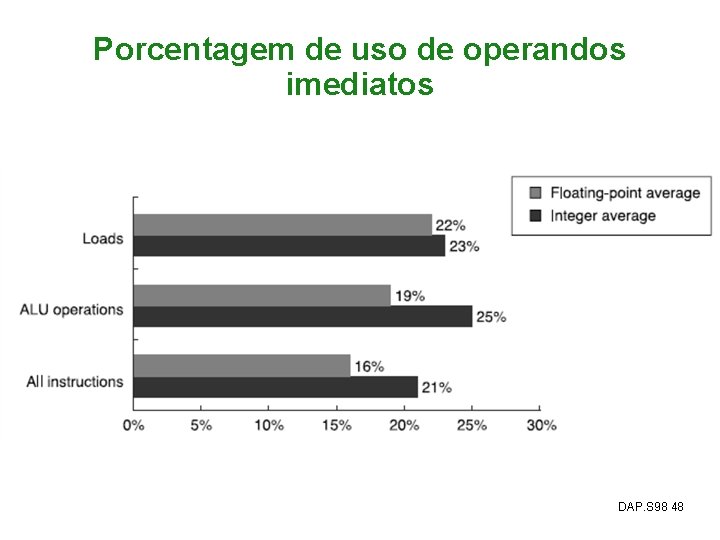

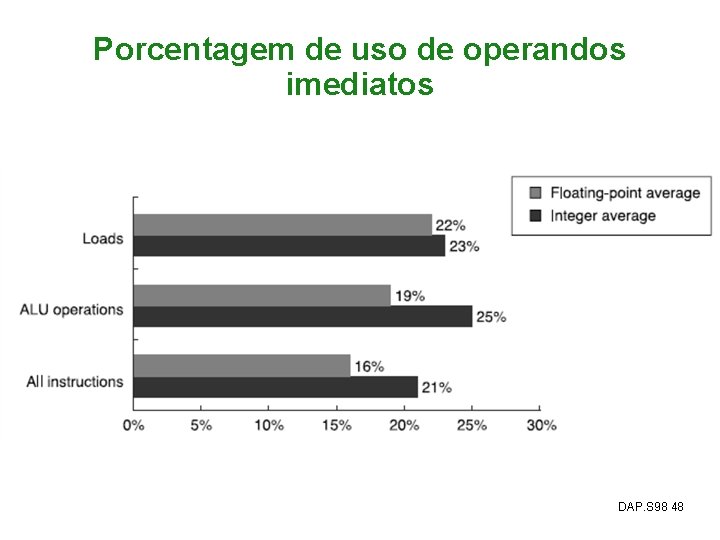

Porcentagem de uso de operandos imediatos DAP. S 98 48

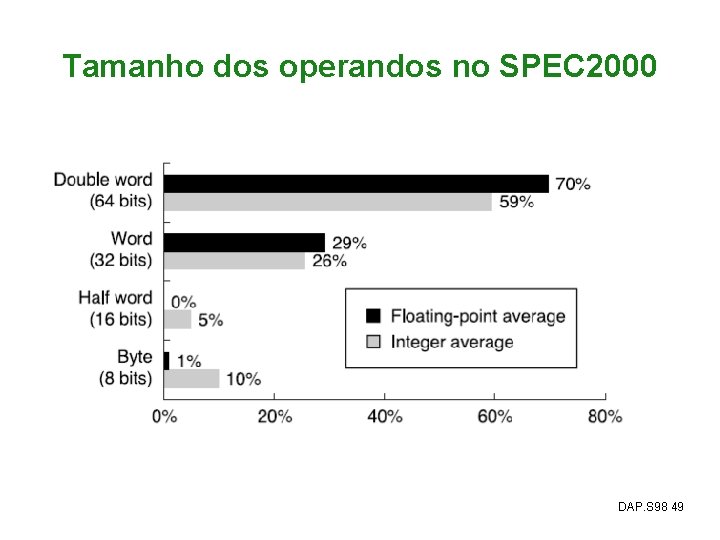

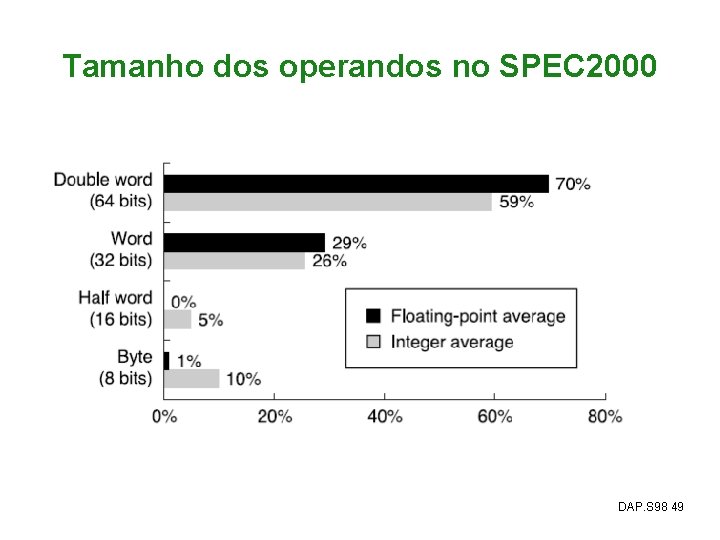

Tamanho dos operandos no SPEC 2000 DAP. S 98 49

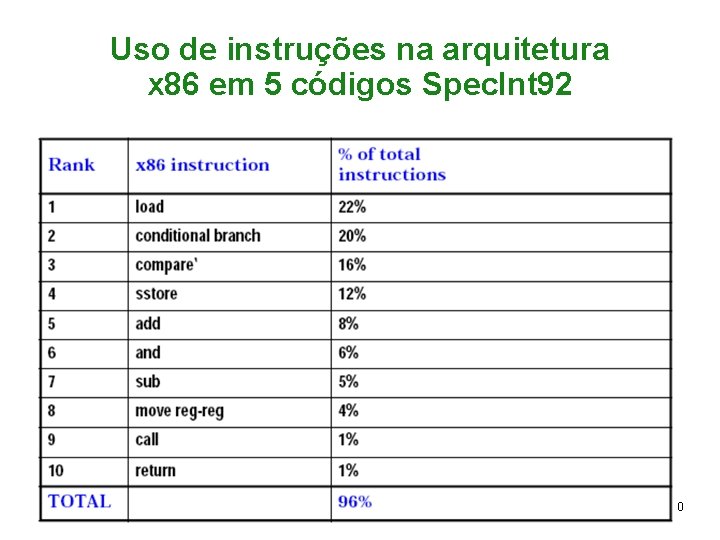

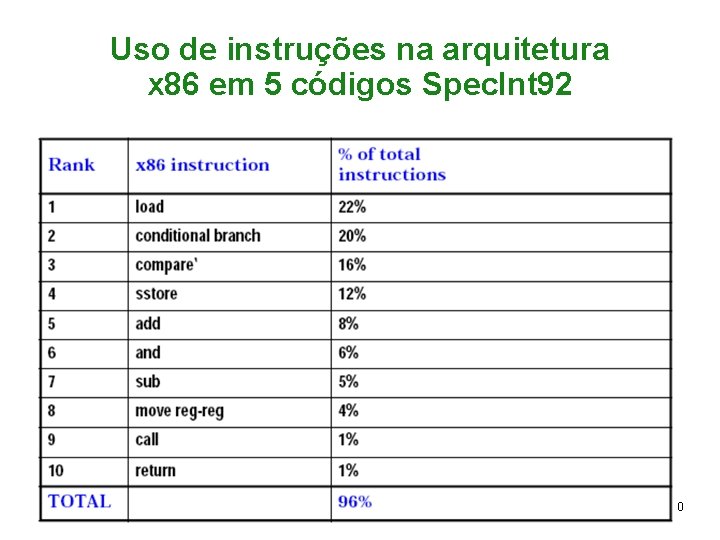

Uso de instruções na arquitetura x 86 em 5 códigos Spec. Int 92 DAP. S 98 50

Conclusão: atualmente predominam as máquinas do tipo registrador-memória Motivo: de certa forma, responsabilidade da IBM • Fabricante dominante nessa fase do campeonato • Existem muitas técnicas de compilação Provavelmente é a escolha certa • Software tem mais tempo de vida que hardware • Softwares existem a décadas • Hardware é substituído a cada 2 a 4 anos Tecnologia de compilações é importante • Atualmente está bem avançado para máquinas registrador-memória DAP. S 98 51