Computer Science 210 Computer Organization The Instruction Execution

![Example: LC-3 ADD Instruction Each instruction has a four-bit opcode in bits [15: 12] Example: LC-3 ADD Instruction Each instruction has a four-bit opcode in bits [15: 12]](https://slidetodoc.com/presentation_image/bd6435b36287133be259dab024b259b5/image-5.jpg)

![Instruction Processing: Decode Identify the opcode: Bits [15: 12] in LC-3 4 -to-16 decoder Instruction Processing: Decode Identify the opcode: Bits [15: 12] in LC-3 4 -to-16 decoder](https://slidetodoc.com/presentation_image/bd6435b36287133be259dab024b259b5/image-11.jpg)

- Slides: 20

Computer Science 210 Computer Organization The Instruction Execution Cycle

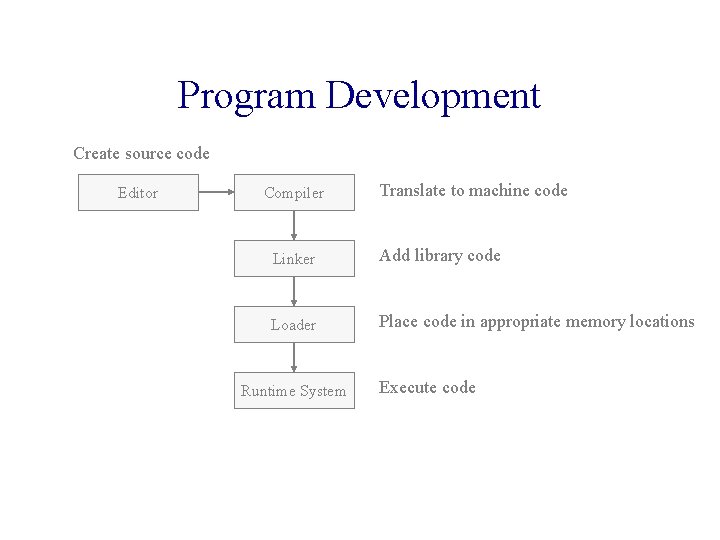

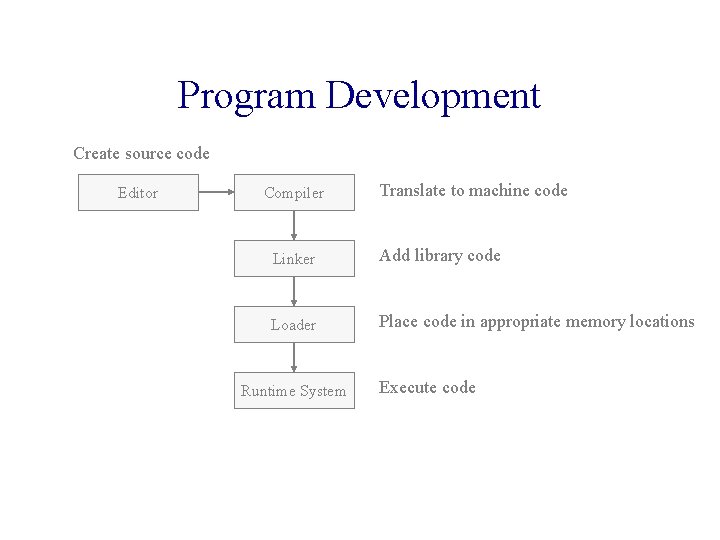

Program Development Create source code Editor Compiler Translate to machine code Linker Add library code Loader Place code in appropriate memory locations Runtime System Execute code

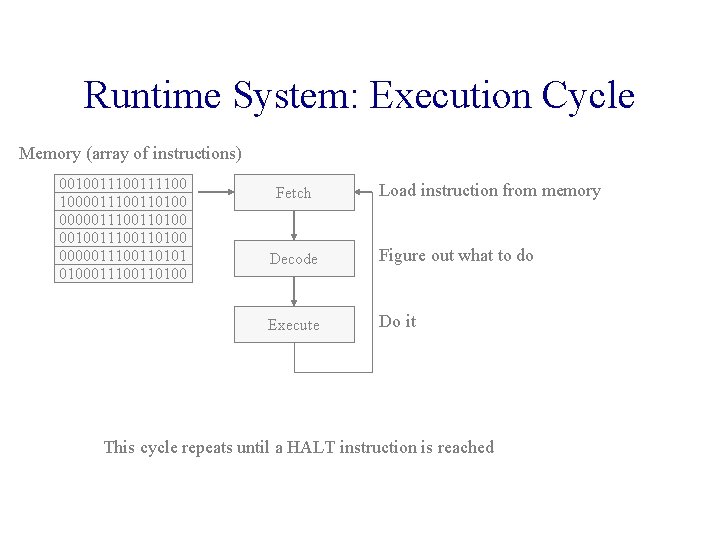

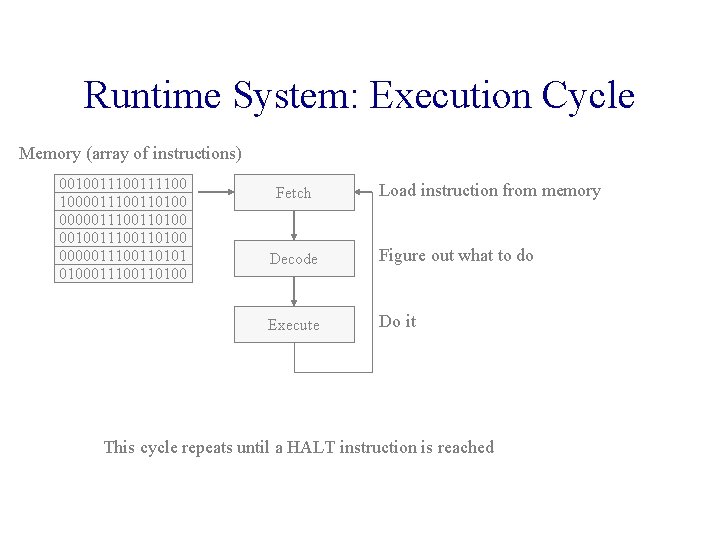

Runtime System: Execution Cycle Memory (array of instructions) 00100111100 1000011100110100 00100110100 0000011100110101 0100011100110100 Fetch Load instruction from memory Decode Figure out what to do Execute Do it This cycle repeats until a HALT instruction is reached

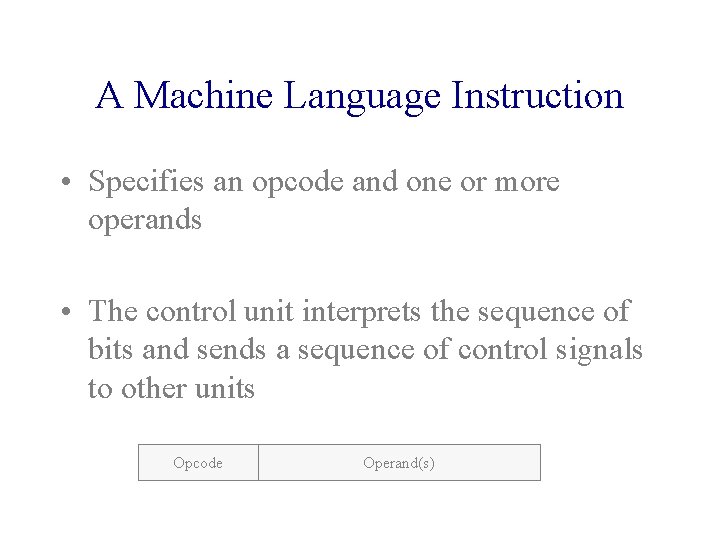

A Machine Language Instruction • Specifies an opcode and one or more operands • The control unit interprets the sequence of bits and sends a sequence of control signals to other units Opcode Operand(s)

![Example LC3 ADD Instruction Each instruction has a fourbit opcode in bits 15 12 Example: LC-3 ADD Instruction Each instruction has a four-bit opcode in bits [15: 12]](https://slidetodoc.com/presentation_image/bd6435b36287133be259dab024b259b5/image-5.jpg)

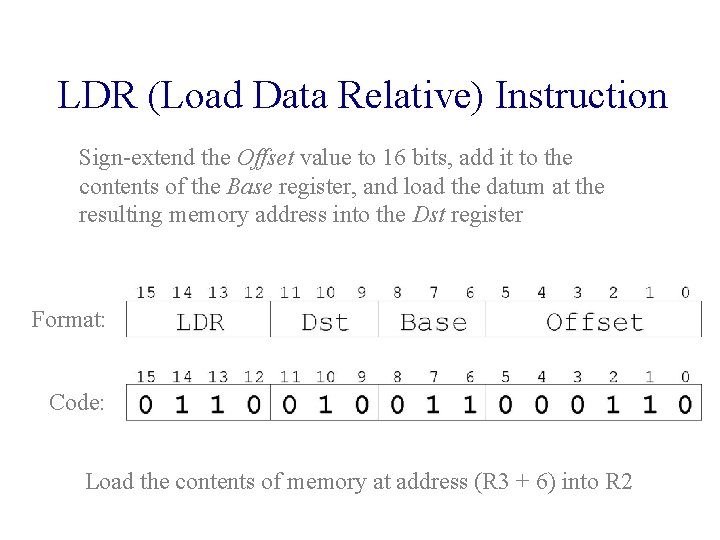

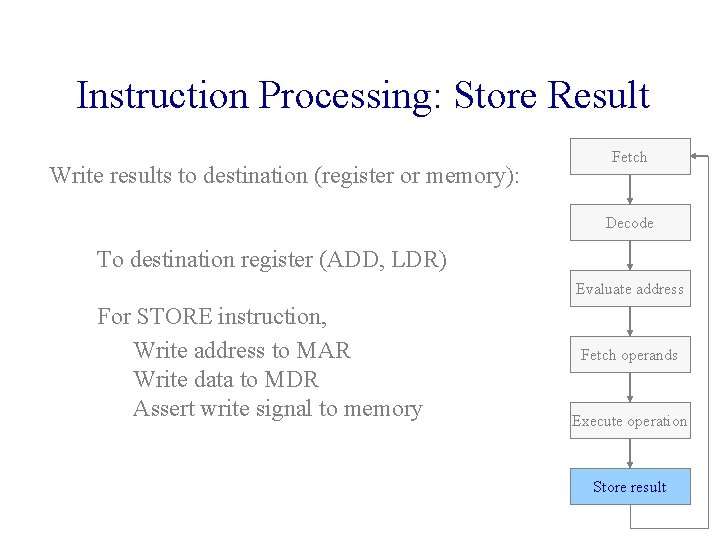

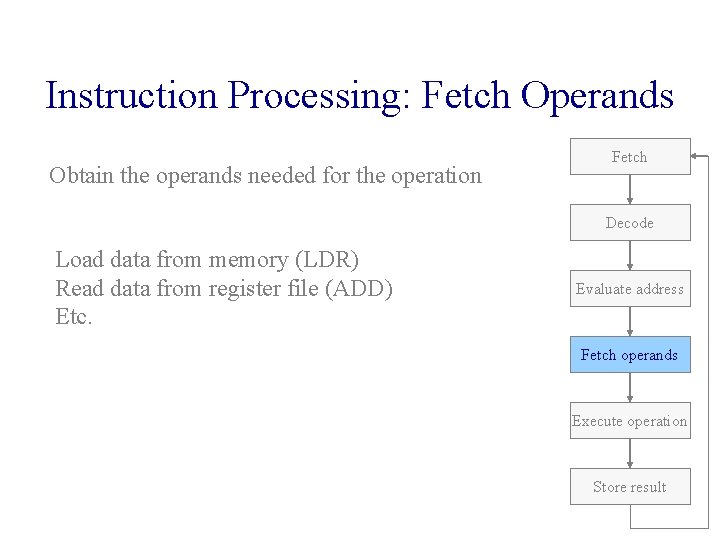

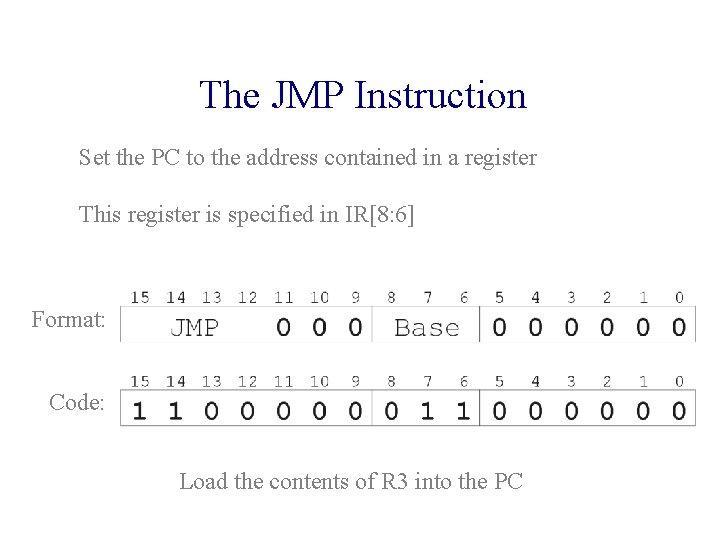

Example: LC-3 ADD Instruction Each instruction has a four-bit opcode in bits [15: 12] This instruction also specifies two source registers and one destination register Format: Code: Add the contents of R 2 and R 6 and store the result in R 6

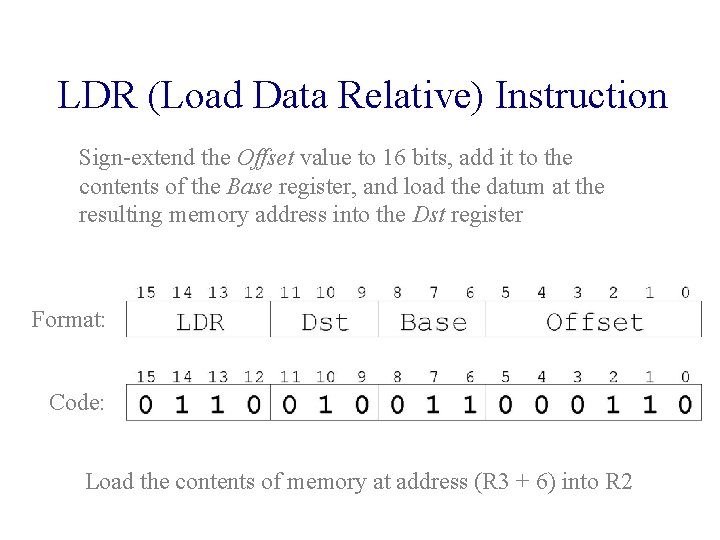

LDR (Load Data Relative) Instruction Sign-extend the Offset value to 16 bits, add it to the contents of the Base register, and load the datum at the resulting memory address into the Dst register Format: Code: Load the contents of memory at address (R 3 + 6) into R 2

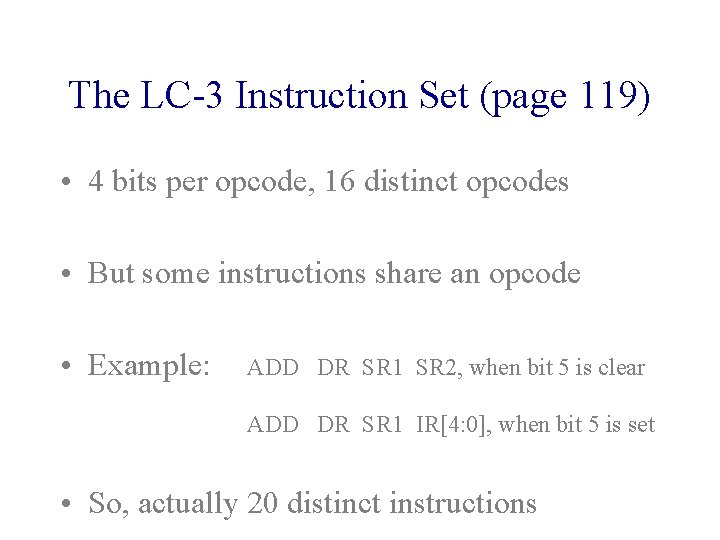

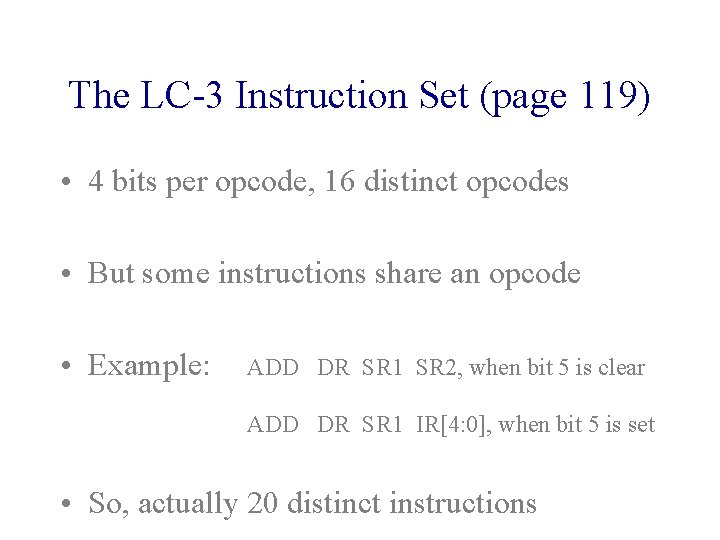

The LC-3 Instruction Set (page 119) • 4 bits per opcode, 16 distinct opcodes • But some instructions share an opcode • Example: ADD DR SR 1 SR 2, when bit 5 is clear ADD DR SR 1 IR[4: 0], when bit 5 is set • So, actually 20 distinct instructions

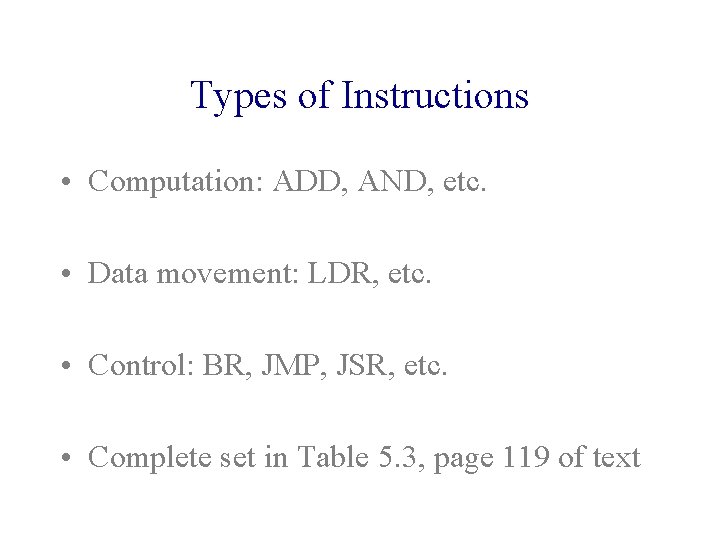

Types of Instructions • Computation: ADD, AND, etc. • Data movement: LDR, etc. • Control: BR, JMP, JSR, etc. • Complete set in Table 5. 3, page 119 of text

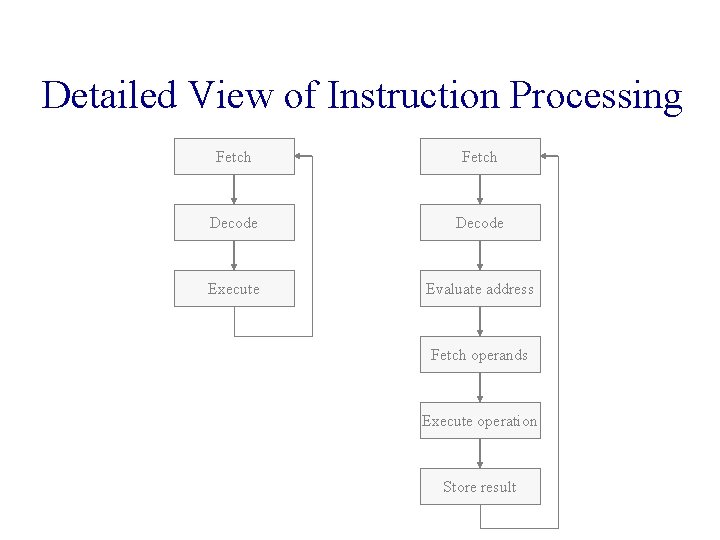

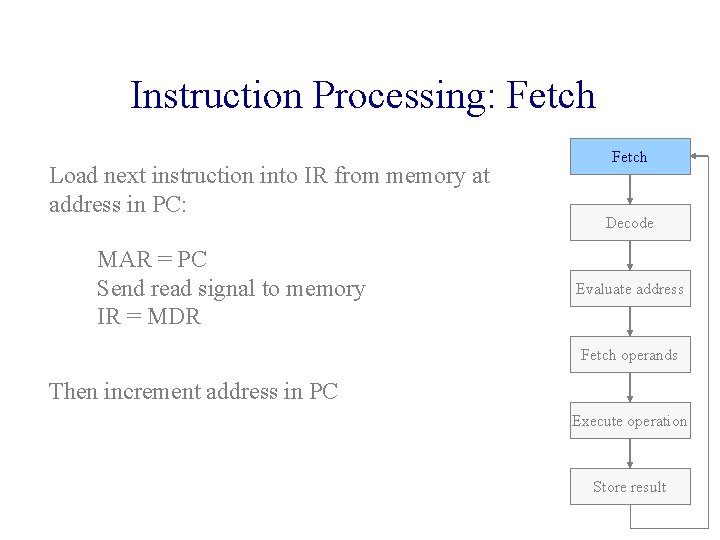

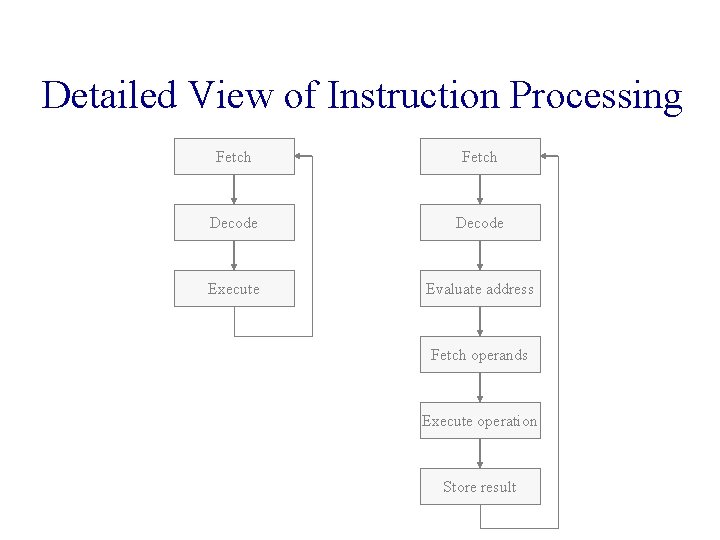

Detailed View of Instruction Processing Fetch Decode Execute Evaluate address Fetch operands Execute operation Store result

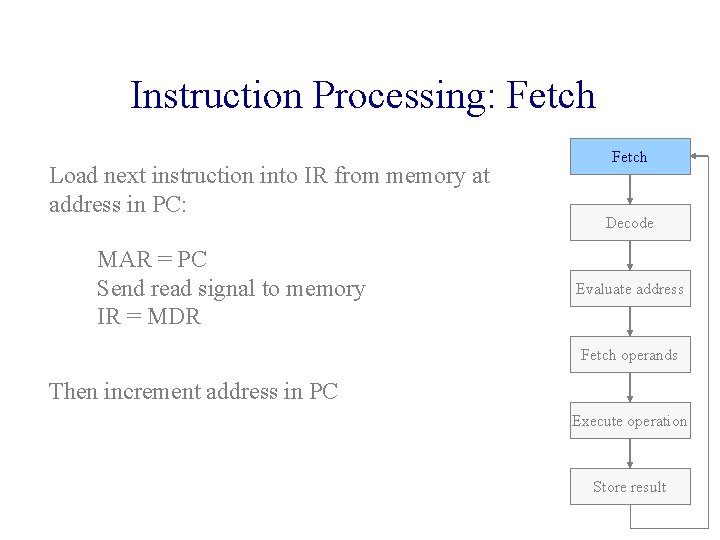

Instruction Processing: Fetch Load next instruction into IR from memory at address in PC: MAR = PC Send read signal to memory IR = MDR Fetch Decode Evaluate address Fetch operands Then increment address in PC Execute operation Store result

![Instruction Processing Decode Identify the opcode Bits 15 12 in LC3 4 to16 decoder Instruction Processing: Decode Identify the opcode: Bits [15: 12] in LC-3 4 -to-16 decoder](https://slidetodoc.com/presentation_image/bd6435b36287133be259dab024b259b5/image-11.jpg)

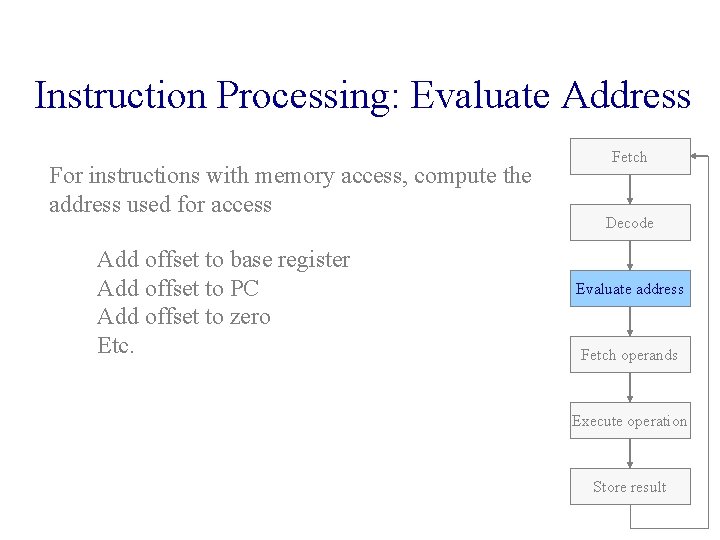

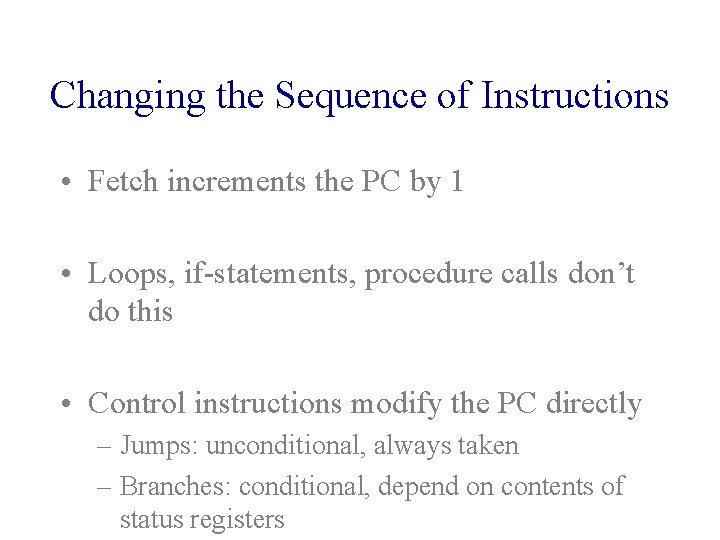

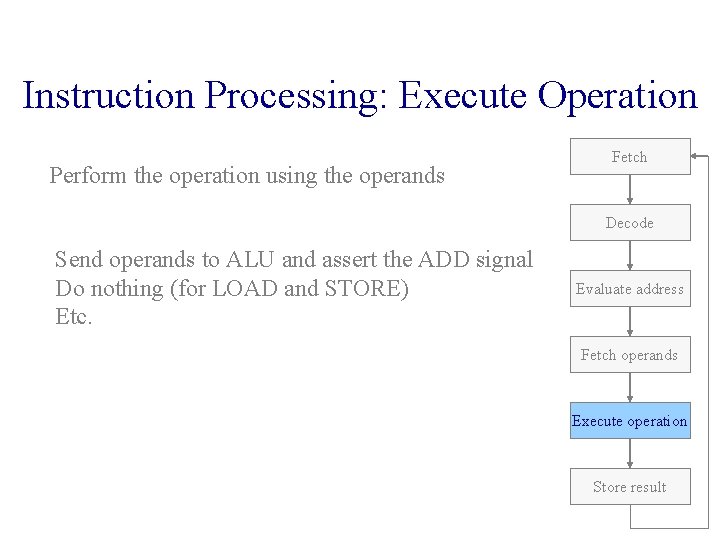

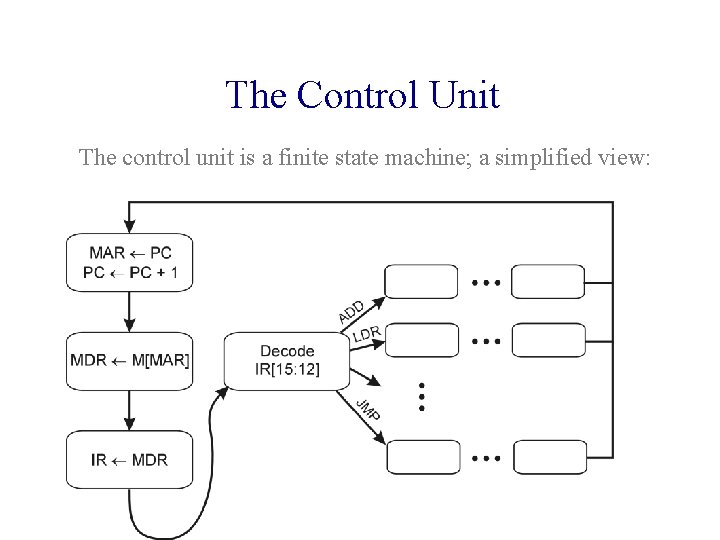

Instruction Processing: Decode Identify the opcode: Bits [15: 12] in LC-3 4 -to-16 decoder asserts a control line Fetch Decode Evaluate address Depending on the opcode, identify the other operands from the remaining bits For the first ADD, bits [11: 9] = Destination register bits [8: 6] = Source register 1 bits [2: 0] = Source register 2 Fetch operands Execute operation Store result

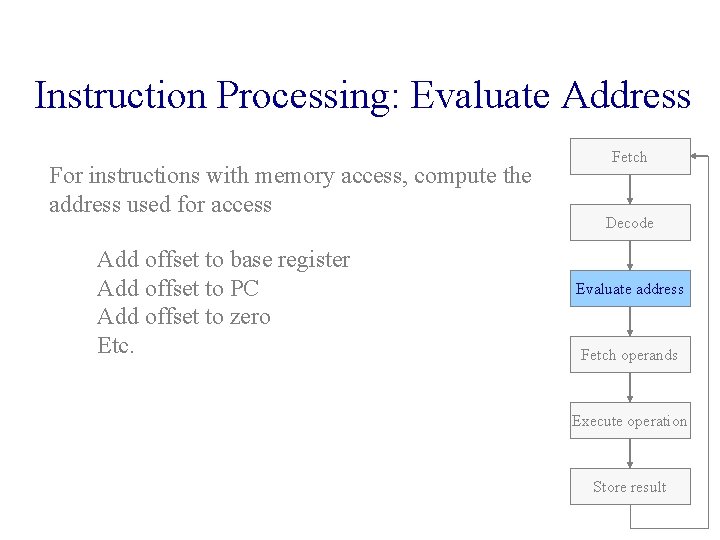

Instruction Processing: Evaluate Address For instructions with memory access, compute the address used for access Add offset to base register Add offset to PC Add offset to zero Etc. Fetch Decode Evaluate address Fetch operands Execute operation Store result

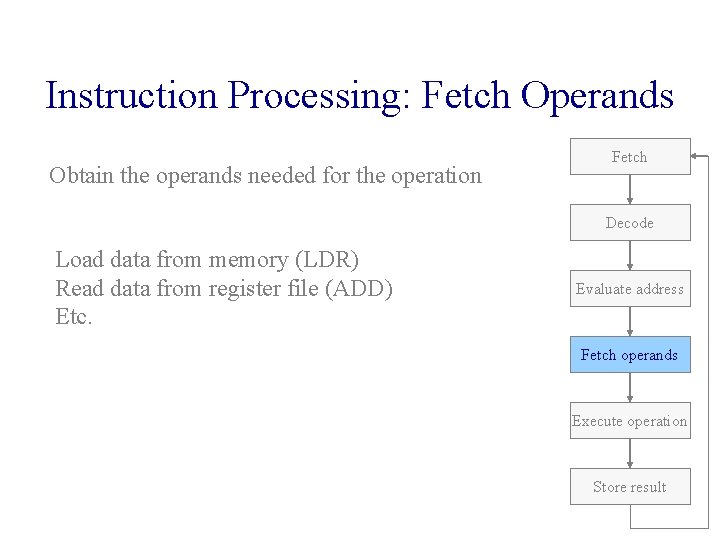

Instruction Processing: Fetch Operands Obtain the operands needed for the operation Fetch Decode Load data from memory (LDR) Read data from register file (ADD) Etc. Evaluate address Fetch operands Execute operation Store result

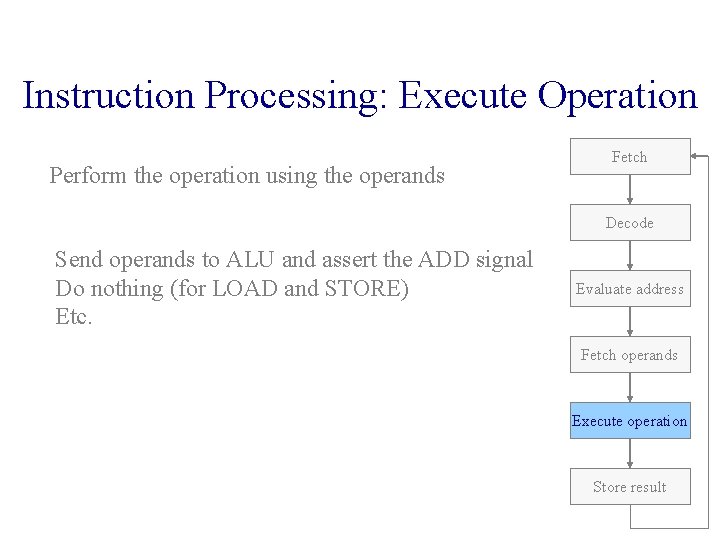

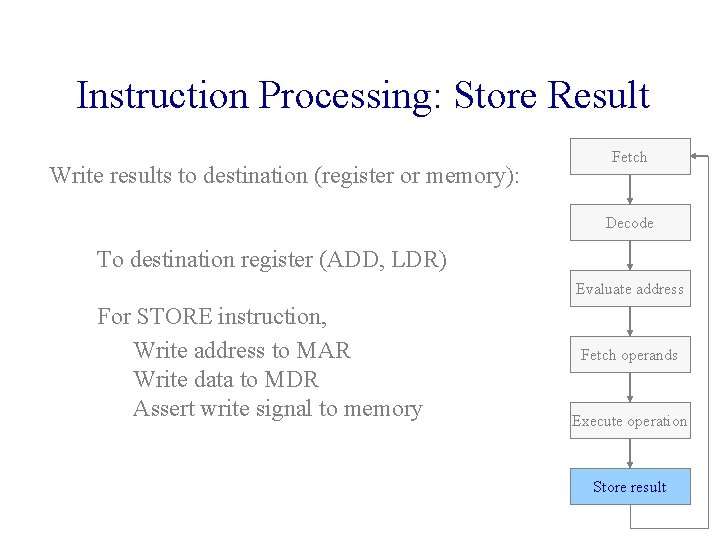

Instruction Processing: Execute Operation Perform the operation using the operands Fetch Decode Send operands to ALU and assert the ADD signal Do nothing (for LOAD and STORE) Etc. Evaluate address Fetch operands Execute operation Store result

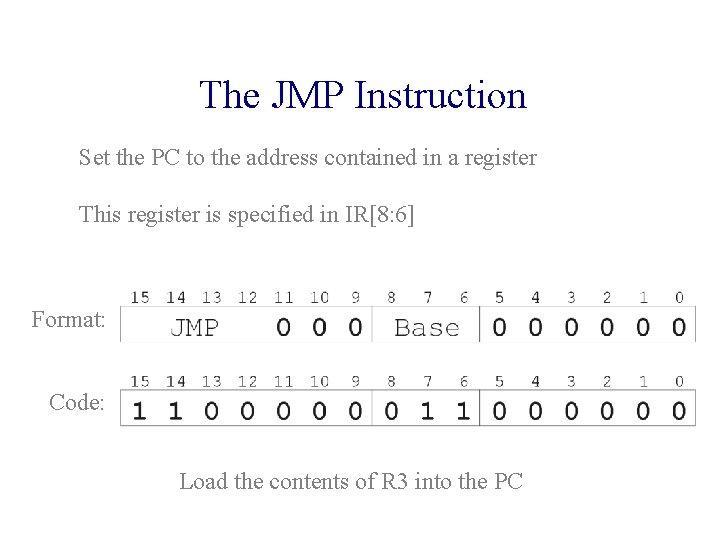

Instruction Processing: Store Result Write results to destination (register or memory): Fetch Decode To destination register (ADD, LDR) Evaluate address For STORE instruction, Write address to MAR Write data to MDR Assert write signal to memory Fetch operands Execute operation Store result

Changing the Sequence of Instructions • Fetch increments the PC by 1 • Loops, if-statements, procedure calls don’t do this • Control instructions modify the PC directly – Jumps: unconditional, always taken – Branches: conditional, depend on contents of status registers

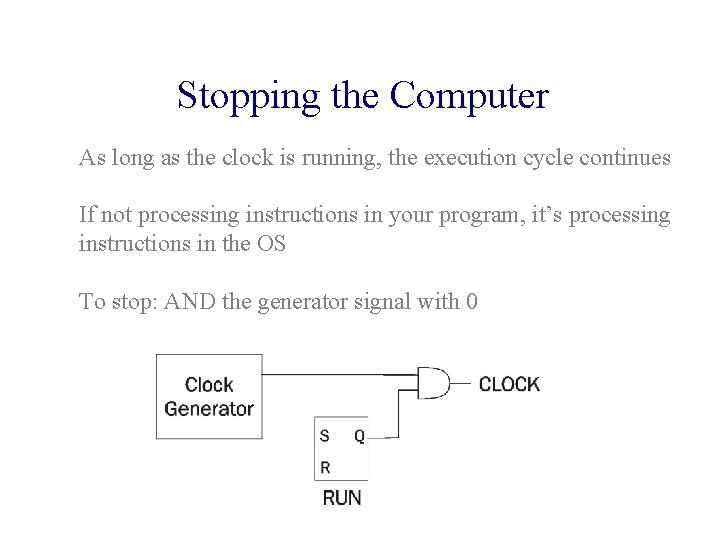

The JMP Instruction Set the PC to the address contained in a register This register is specified in IR[8: 6] Format: Code: Load the contents of R 3 into the PC

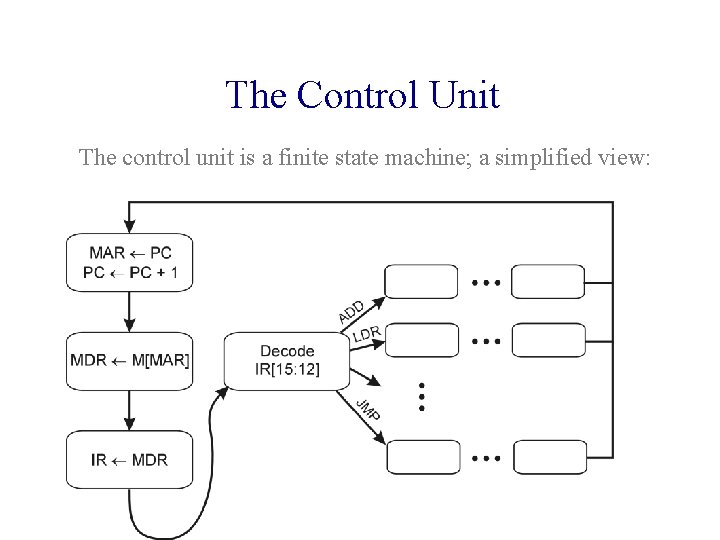

The Control Unit The control unit is a finite state machine; a simplified view:

Stopping the Computer As long as the clock is running, the execution cycle continues If not processing instructions in your program, it’s processing instructions in the OS To stop: AND the generator signal with 0

For Monday Machine language instructions for calculations