Building Asynchronous Circuits With JBits Eric Keller eric

Building Asynchronous Circuits With JBits Eric Keller eric. keller@xilinx. com FPL 2001

JBits Background w A Java API to configure Xilinx FPGA bitstreams w Provides complete design control — Routing — CLB configuration w Supports run-time reconfiguration w Allows for tools to built upon it wjbits. set(row, Example col, low-level configuration S 1 F 1, S 1 F 1. SINGLE_EAST 0)call: www. xilinx. com

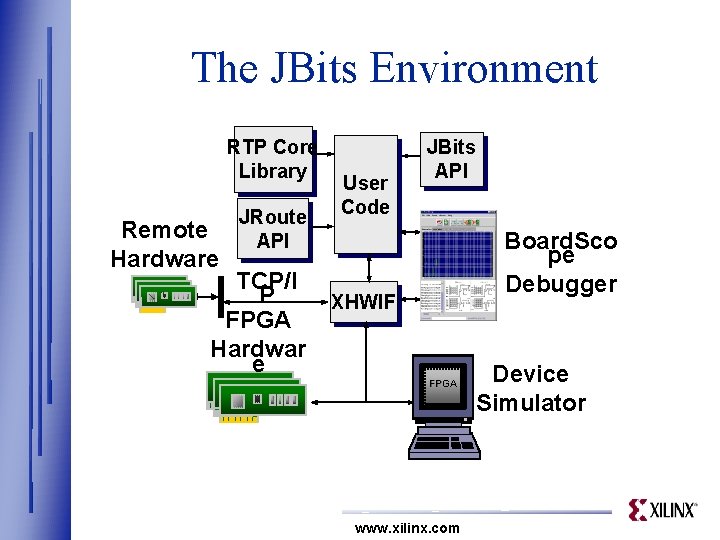

The JBits Environment RTP Core Library Remote Hardware JRoute API TCP/I P FPGA Hardwar e User Code JBits API Board. Sco pe Debugger XHWIF FPGA www. xilinx. com Device Simulator

Asynchronous Advantages w Modularity w Low power w Average-case performance w No clock distribution w Adapt to environmental conditions www. xilinx. com

Why use JBits? w Complete control over circuit w Have some fixed routes and others autorouted — Can pre-route modules to meet any delay constraint w Use templates to add delay to a net w Clean HDL for dual-rail cores w Combine asynchronous design and RTR www. xilinx. com

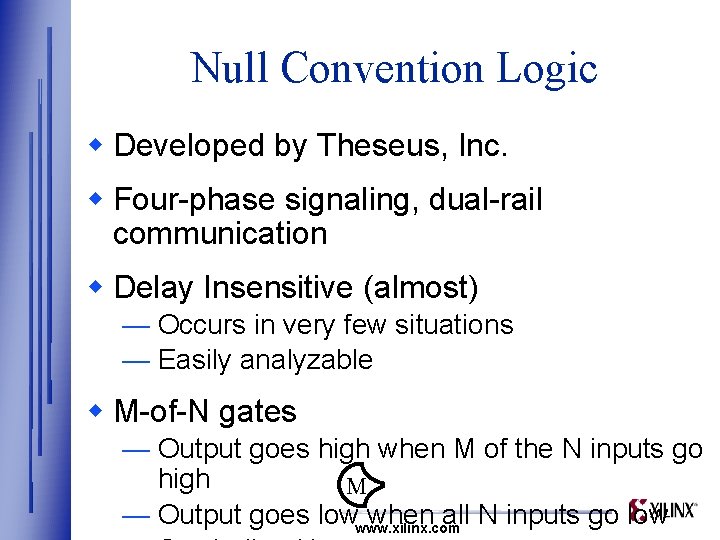

Null Convention Logic w Developed by Theseus, Inc. w Four-phase signaling, dual-rail communication w Delay Insensitive (almost) — Occurs in very few situations — Easily analyzable w M-of-N gates — Output goes high when M of the N inputs go high M — Output goes lowwww. xilinx. com when all N inputs go low

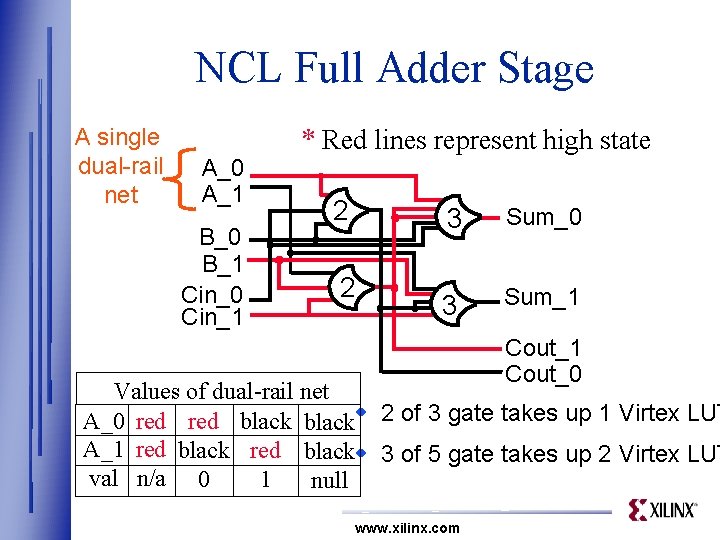

NCL Full Adder Stage A single dual-rail net A_0 A_1 B_0 B_1 Cin_0 Cin_1 * Red lines represent high state 2 2 3 Sum_0 3 Sum_1 Cout_0 Values of dual-rail net A_0 red blackw 2 of 3 gate takes up 1 Virtex LUT A_1 red blackw 3 of 5 gate takes up 2 Virtex LUT val n/a 0 1 null www. xilinx. com

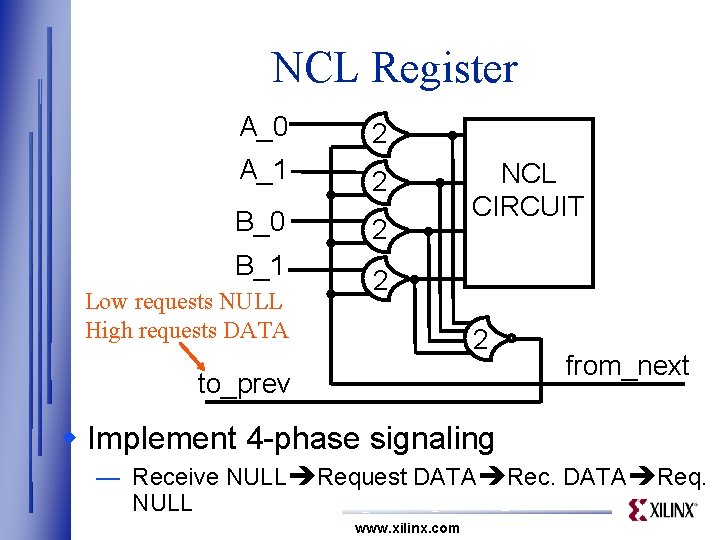

NCL Register A_0 2 A_1 2 B_0 2 B_1 Low requests NULL High requests DATA NCL CIRCUIT 2 2 to_prev from_next w Implement 4 -phase signaling — Receive NULL Request DATA Rec. DATA Req. NULL www. xilinx. com

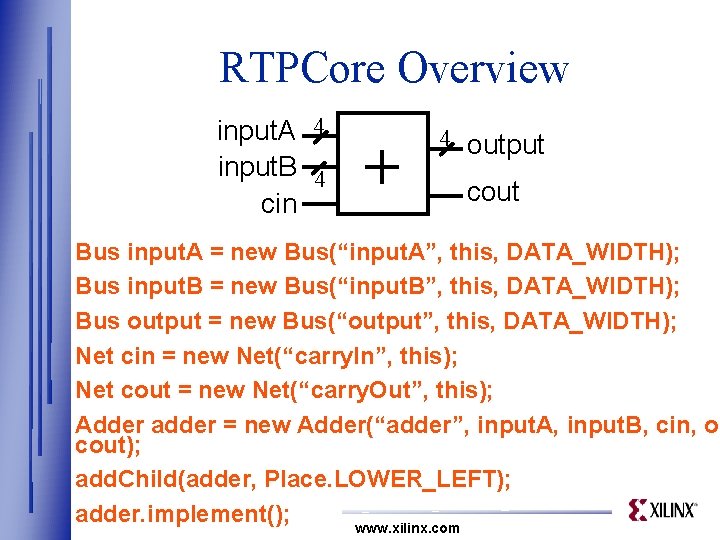

RTPCore Overview input. A 4 input. B 4 cin + 4 output cout Bus input. A = new Bus(“input. A”, this, DATA_WIDTH); Bus input. B = new Bus(“input. B”, this, DATA_WIDTH); Bus output = new Bus(“output”, this, DATA_WIDTH); Net cin = new Net(“carry. In”, this); Net cout = new Net(“carry. Out”, this); Adder adder = new Adder(“adder”, input. A, input. B, cin, ou cout); add. Child(adder, Place. LOWER_LEFT); adder. implement(); www. xilinx. com

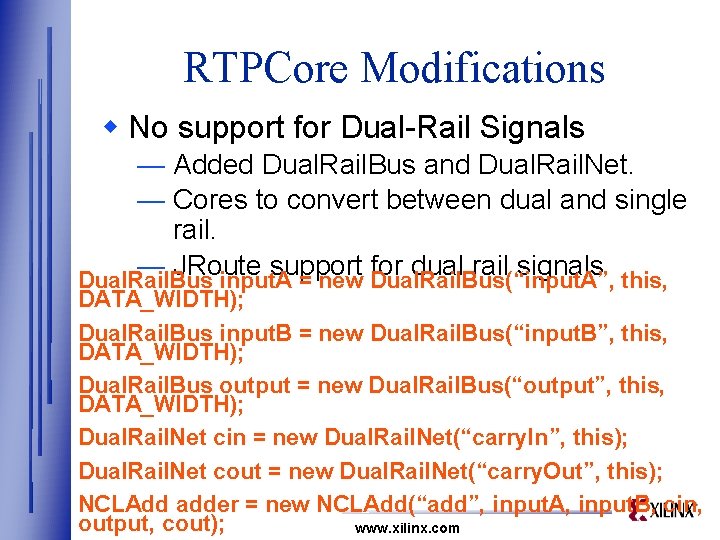

RTPCore Modifications w No support for Dual-Rail Signals — Added Dual. Rail. Bus and Dual. Rail. Net. — Cores to convert between dual and single rail. — JRoute support for dual rail signals Dual. Rail. Bus input. A = new Dual. Rail. Bus(“input. A”, this, DATA_WIDTH); Dual. Rail. Bus input. B = new Dual. Rail. Bus(“input. B”, this, DATA_WIDTH); Dual. Rail. Bus output = new Dual. Rail. Bus(“output”, this, DATA_WIDTH); Dual. Rail. Net cin = new Dual. Rail. Net(“carry. In”, this); Dual. Rail. Net cout = new Dual. Rail. Net(“carry. Out”, this); NCLAdd adder = new NCLAdd(“add”, input. A, input. B, cin, output, cout); www. xilinx. com

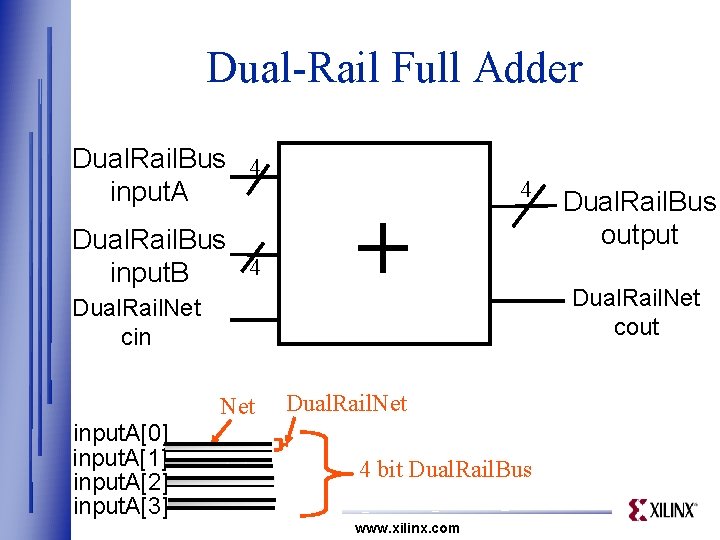

Dual-Rail Full Adder Dual. Rail. Bus 4 input. A Dual. Rail. Bus 4 input. B Dual. Rail. Net cin Net input. A[0] input. A[1] input. A[2] input. A[3] + 4 Dual. Rail. Net 4 bit Dual. Rail. Bus www. xilinx. com Dual. Rail. Bus output Dual. Rail. Net cout

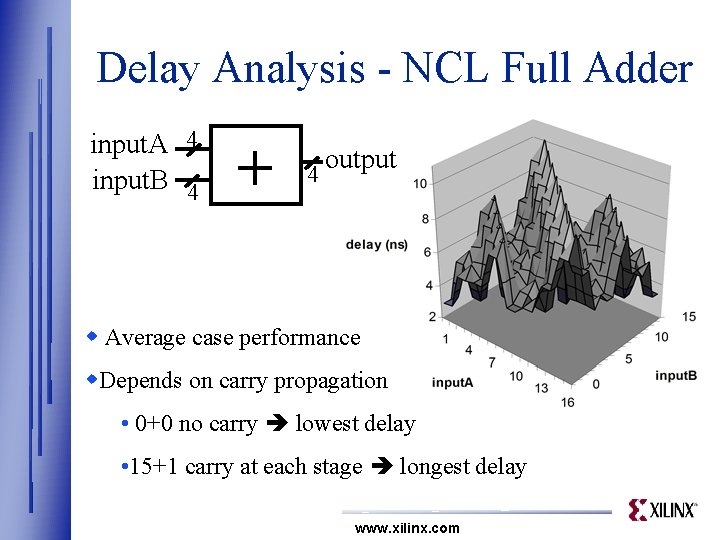

Delay Analysis - NCL Full Adder input. A 4 input. B 4 + 4 output w Average case performance w. Depends on carry propagation • 0+0 no carry lowest delay • 15+1 carry at each stage longest delay www. xilinx. com

Future Work w Defect Tolerance — Work around a defect on an FPGA — No timing analysis because of delay insensitive — Can place modules anywhere and they work w Other methodologies — Add support in JRoute for isochronic forks – symmetric and asymmetric w Examine FPGAs targeted to asynchronous design www. xilinx. com

- Slides: 13