Blackfin SPI Compatible Interface Design and implementation details

Blackfin SPI Compatible Interface Design and implementation details on the way to a valid SPI-LCD interface driver SPI Initialization , Copyright M. Smith, ECE,

To be tackled today l l What is SPI? What is the SPI “master slave” relationship? How do you send commands from the Blackfin to a LCD device? What commands are necessary to control the LCD device -- HD 44780? 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 2

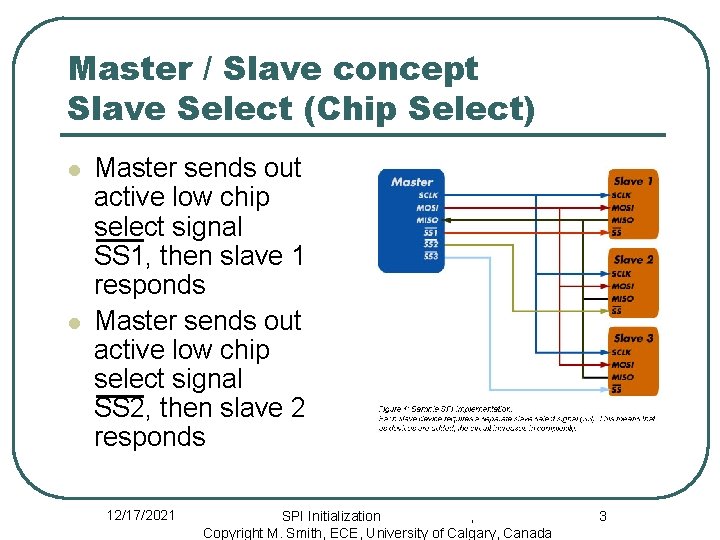

Master / Slave concept Slave Select (Chip Select) l l Master sends out active low chip select signal SS 1, then slave 1 responds Master sends out active low chip select signal SS 2, then slave 2 responds 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 3

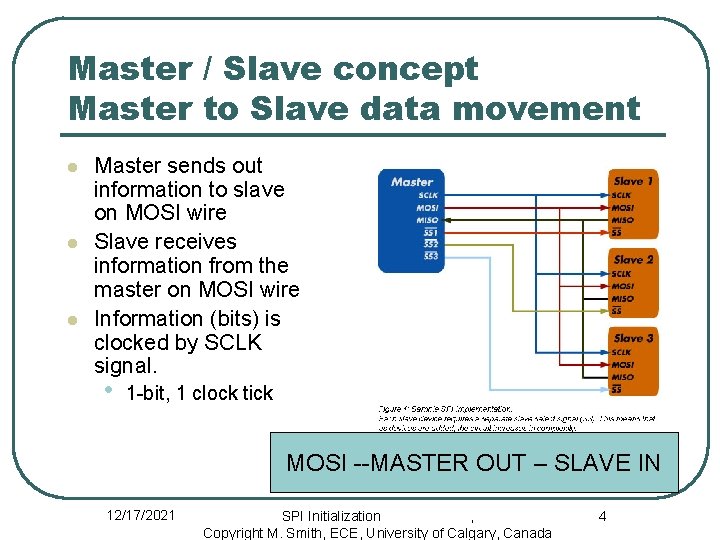

Master / Slave concept Master to Slave data movement l l l Master sends out information to slave on MOSI wire Slave receives information from the master on MOSI wire Information (bits) is clocked by SCLK signal. • 1 -bit, 1 clock tick MOSI --MASTER OUT – SLAVE IN 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 4

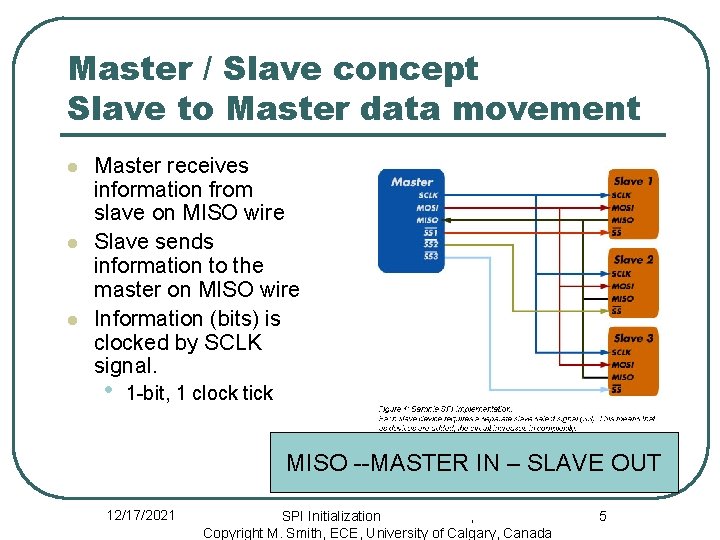

Master / Slave concept Slave to Master data movement l l l Master receives information from slave on MISO wire Slave sends information to the master on MISO wire Information (bits) is clocked by SCLK signal. • 1 -bit, 1 clock tick MISO --MASTER IN – SLAVE OUT 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 5

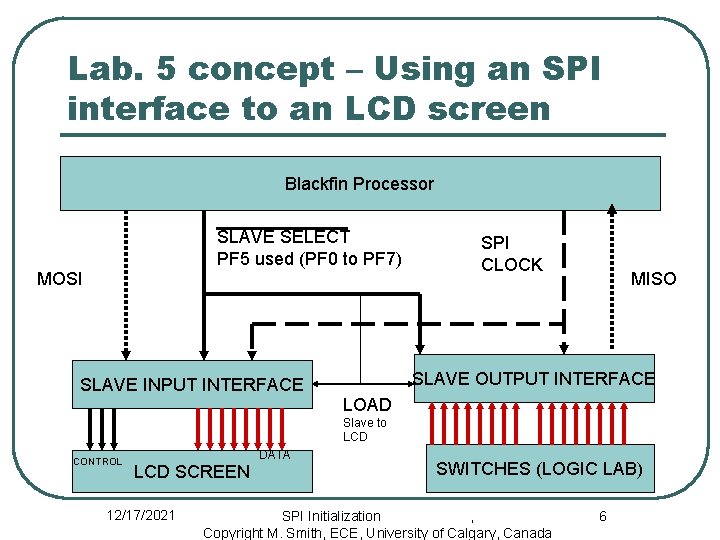

Lab. 5 concept – Using an SPI interface to an LCD screen Blackfin Processor SLAVE SELECT PF 5 used (PF 0 to PF 7) MOSI SPI CLOCK MISO SLAVE OUTPUT INTERFACE SLAVE INPUT INTERFACE LOAD Slave to LCD CONTROL LCD SCREEN 12/17/2021 DATA SWITCHES (LOGIC LAB) SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 6

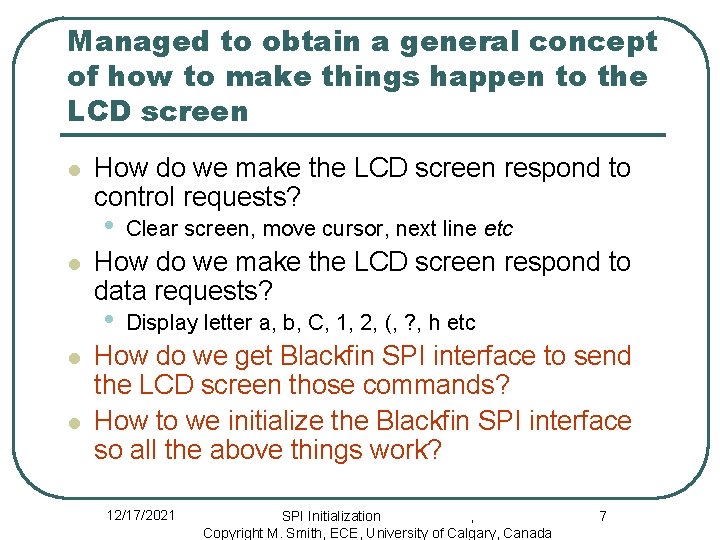

Managed to obtain a general concept of how to make things happen to the LCD screen l How do we make the LCD screen respond to control requests? • l How do we make the LCD screen respond to data requests? • l l Clear screen, move cursor, next line etc Display letter a, b, C, 1, 2, (, ? , h etc How do we get Blackfin SPI interface to send the LCD screen those commands? How to we initialize the Blackfin SPI interface so all the above things work? 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 7

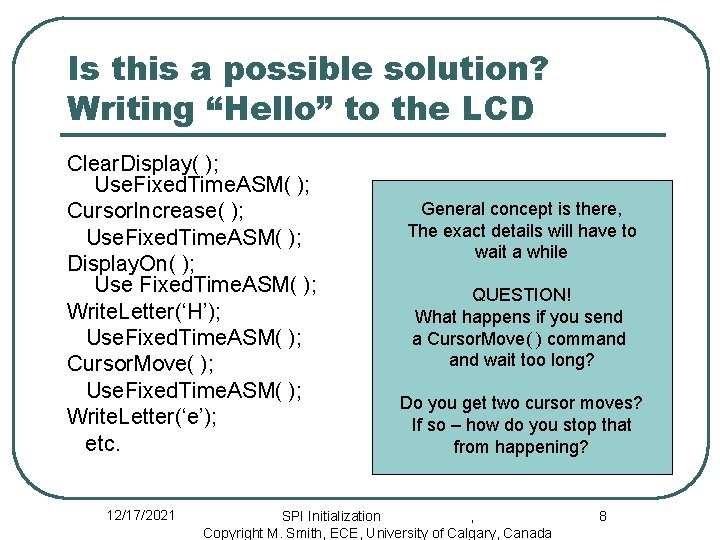

Is this a possible solution? Writing “Hello” to the LCD Clear. Display( ); Use. Fixed. Time. ASM( ); Cursor. Increase( ); Use. Fixed. Time. ASM( ); Display. On( ); Use Fixed. Time. ASM( ); Write. Letter(‘H’); Use. Fixed. Time. ASM( ); Cursor. Move( ); Use. Fixed. Time. ASM( ); Write. Letter(‘e’); etc. 12/17/2021 General concept is there, The exact details will have to wait a while QUESTION! What happens if you send a Cursor. Move( ) command wait too long? Do you get two cursor moves? If so – how do you stop that from happening? SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 8

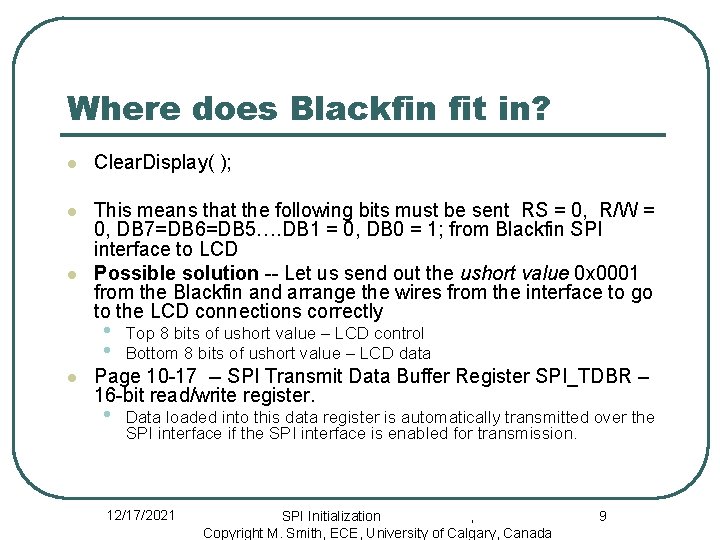

Where does Blackfin fit in? l Clear. Display( ); l This means that the following bits must be sent RS = 0, R/W = 0, DB 7=DB 6=DB 5…. DB 1 = 0, DB 0 = 1; from Blackfin SPI interface to LCD Possible solution -- Let us send out the ushort value 0 x 0001 from the Blackfin and arrange the wires from the interface to go to the LCD connections correctly l l • • Top 8 bits of ushort value – LCD control Bottom 8 bits of ushort value – LCD data • Data loaded into this data register is automatically transmitted over the SPI interface if the SPI interface is enabled for transmission. Page 10 -17 -- SPI Transmit Data Buffer Register SPI_TDBR – 16 -bit read/write register. 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 9

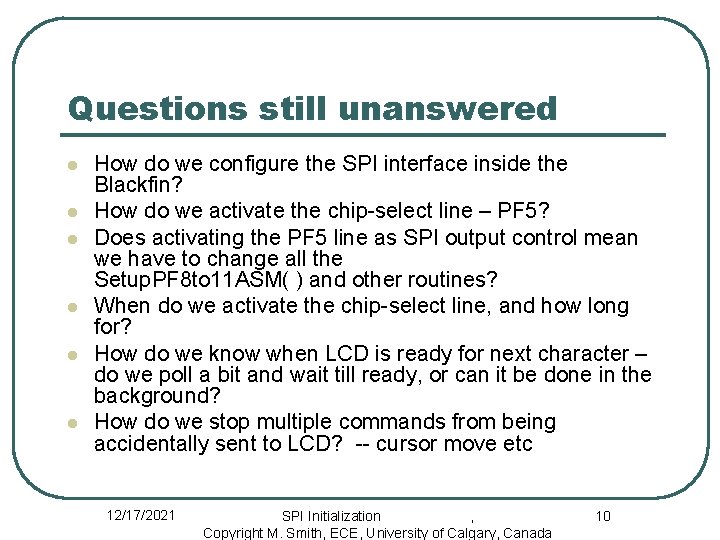

Questions still unanswered l l l How do we configure the SPI interface inside the Blackfin? How do we activate the chip-select line – PF 5? Does activating the PF 5 line as SPI output control mean we have to change all the Setup. PF 8 to 11 ASM( ) and other routines? When do we activate the chip-select line, and how long for? How do we know when LCD is ready for next character – do we poll a bit and wait till ready, or can it be done in the background? How do we stop multiple commands from being accidentally sent to LCD? -- cursor move etc 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 10

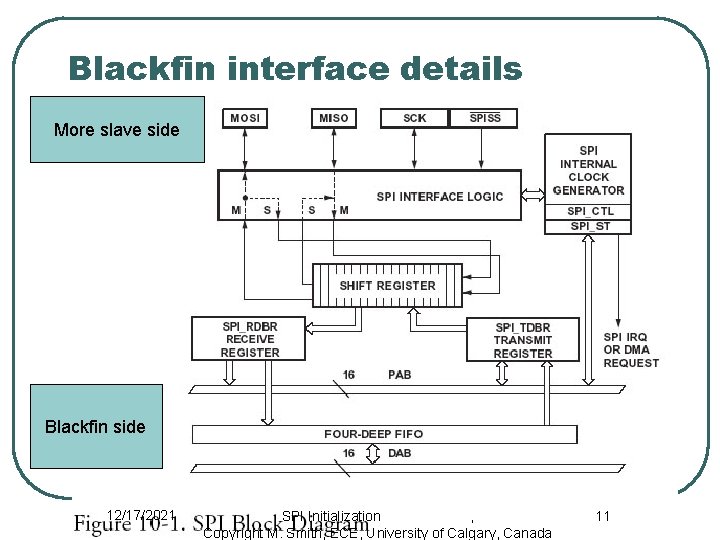

Blackfin interface details More slave side Blackfin side 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 11

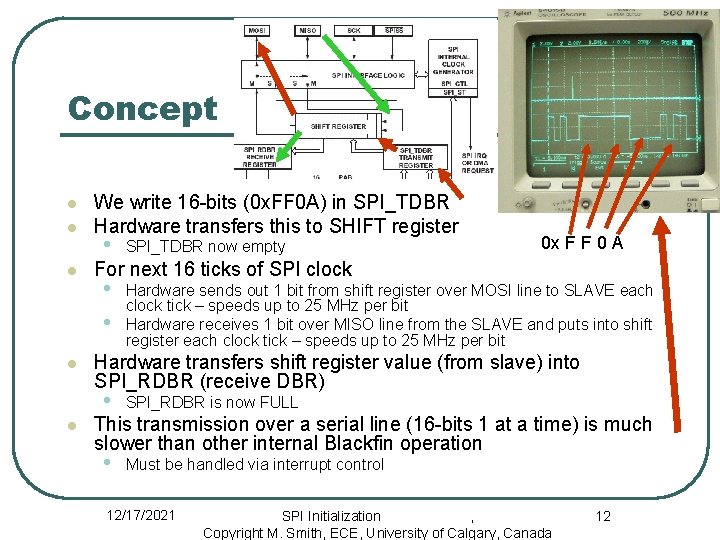

Concept l l We write 16 -bits (0 x. FF 0 A) in SPI_TDBR Hardware transfers this to SHIFT register • 0 x F F 0 A For next 16 ticks of SPI clock • • Hardware sends out 1 bit from shift register over MOSI line to SLAVE each clock tick – speeds up to 25 MHz per bit Hardware receives 1 bit over MISO line from the SLAVE and puts into shift register each clock tick – speeds up to 25 MHz per bit Hardware transfers shift register value (from slave) into SPI_RDBR (receive DBR) • l SPI_TDBR now empty SPI_RDBR is now FULL This transmission over a serial line (16 -bits 1 at a time) is much slower than other internal Blackfin operation • Must be handled via interrupt control 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 12

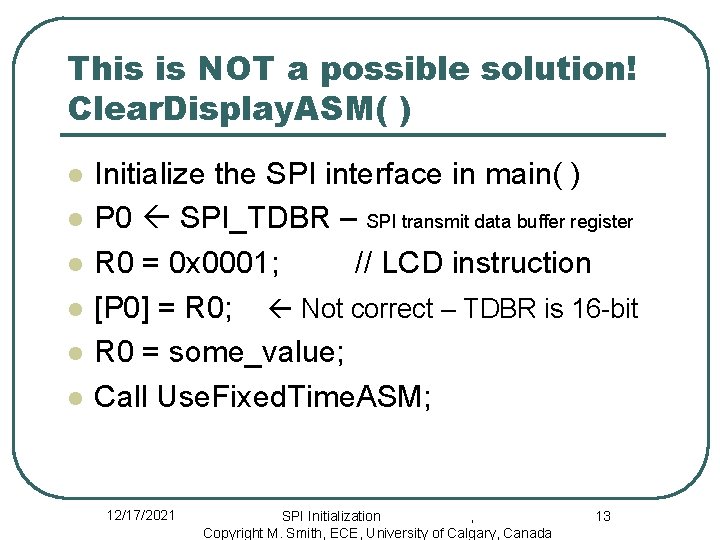

This is NOT a possible solution! Clear. Display. ASM( ) l l l Initialize the SPI interface in main( ) P 0 SPI_TDBR – SPI transmit data buffer register R 0 = 0 x 0001; // LCD instruction [P 0] = R 0; Not correct – TDBR is 16 -bit R 0 = some_value; Call Use. Fixed. Time. ASM; 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 13

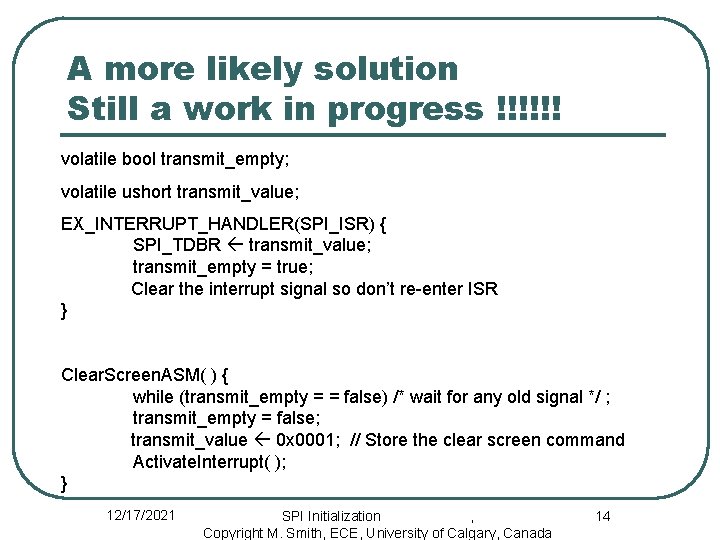

A more likely solution Still a work in progress !!!!!! volatile bool transmit_empty; volatile ushort transmit_value; EX_INTERRUPT_HANDLER(SPI_ISR) { SPI_TDBR transmit_value; transmit_empty = true; Clear the interrupt signal so don’t re-enter ISR } Clear. Screen. ASM( ) { while (transmit_empty = = false) /* wait for any old signal */ ; transmit_empty = false; transmit_value 0 x 0001; // Store the clear screen command Activate. Interrupt( ); } 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 14

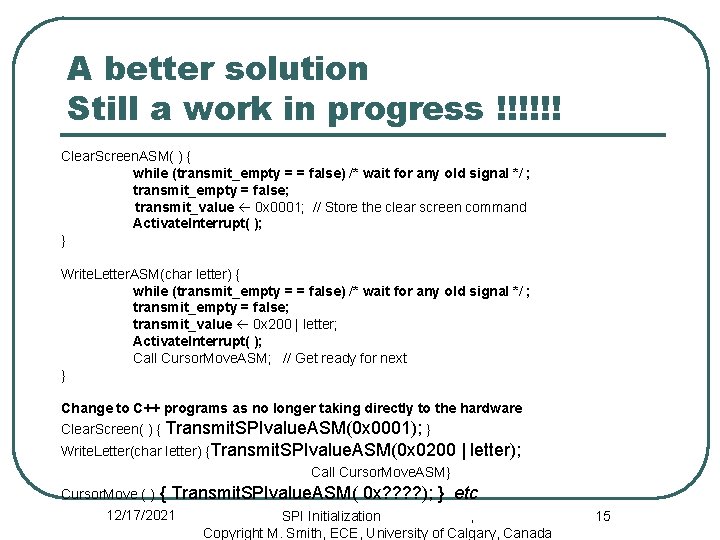

A better solution Still a work in progress !!!!!! Clear. Screen. ASM( ) { while (transmit_empty = = false) /* wait for any old signal */ ; transmit_empty = false; transmit_value 0 x 0001; // Store the clear screen command Activate. Interrupt( ); } Write. Letter. ASM(char letter) { while (transmit_empty = = false) /* wait for any old signal */ ; transmit_empty = false; transmit_value 0 x 200 | letter; Activate. Interrupt( ); Call Cursor. Move. ASM; // Get ready for next } Change to C++ programs as no longer taking directly to the hardware Clear. Screen( ) { Transmit. SPIvalue. ASM(0 x 0001); } Write. Letter(char letter) {Transmit. SPIvalue. ASM(0 x 0200 | letter); Call Cursor. Move. ASM} Cursor. Move ( ) { Transmit. SPIvalue. ASM( 0 x? ? ); } etc 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 15

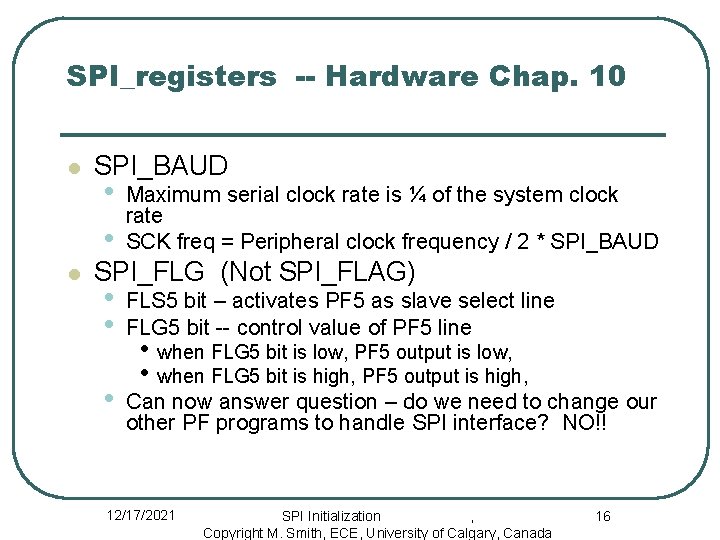

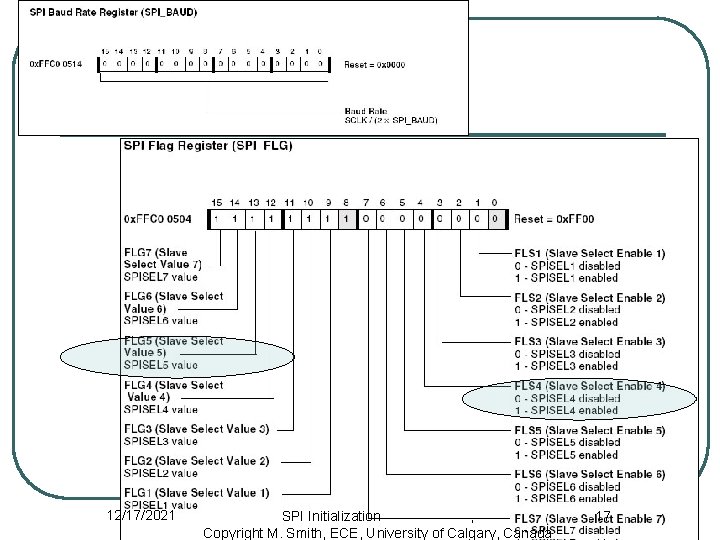

SPI_registers -- Hardware Chap. 10 l l SPI_BAUD • • Maximum serial clock rate is ¼ of the system clock rate SCK freq = Peripheral clock frequency / 2 * SPI_BAUD • • FLS 5 bit – activates PF 5 as slave select line FLG 5 bit -- control value of PF 5 line • Can now answer question – do we need to change our other PF programs to handle SPI interface? NO!! SPI_FLG (Not SPI_FLAG) • when FLG 5 bit is low, PF 5 output is low, • when FLG 5 bit is high, PF 5 output is high, 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 16

12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 17

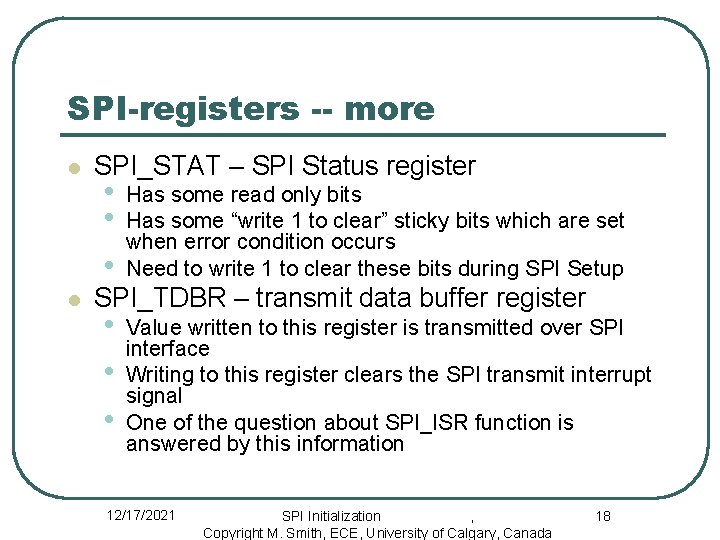

SPI-registers -- more l l SPI_STAT – SPI Status register • • • Has some read only bits Has some “write 1 to clear” sticky bits which are set when error condition occurs Need to write 1 to clear these bits during SPI Setup • • • Value written to this register is transmitted over SPI interface Writing to this register clears the SPI transmit interrupt signal One of the question about SPI_ISR function is answered by this information SPI_TDBR – transmit data buffer register 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 18

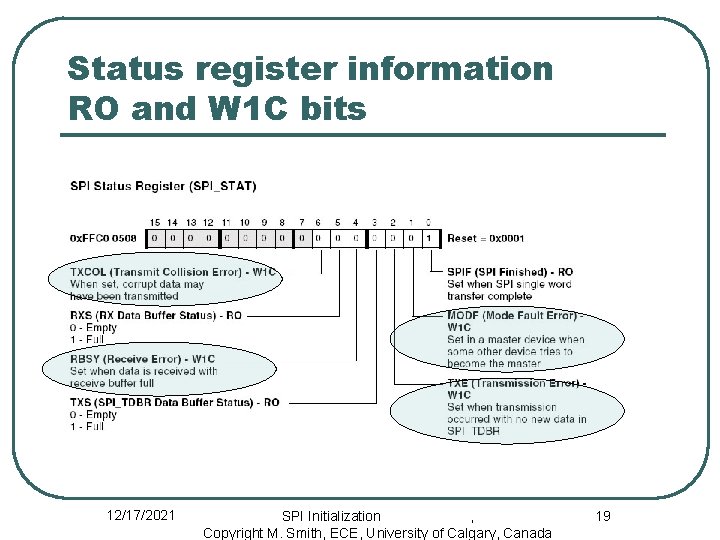

Status register information RO and W 1 C bits 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 19

12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 20

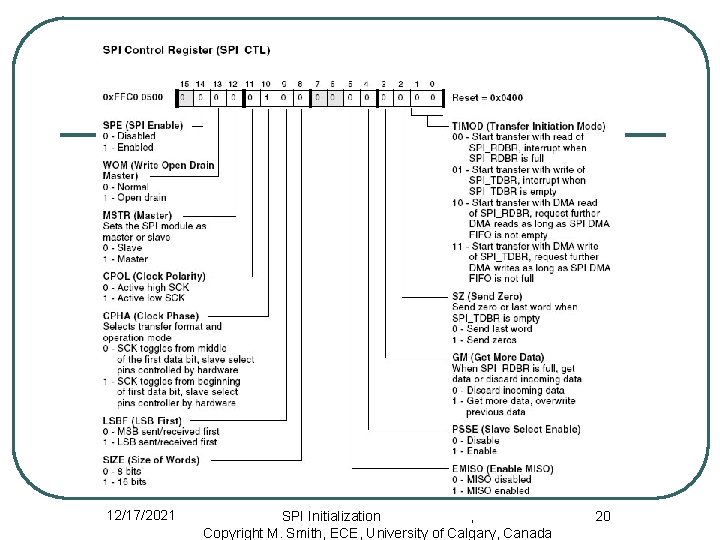

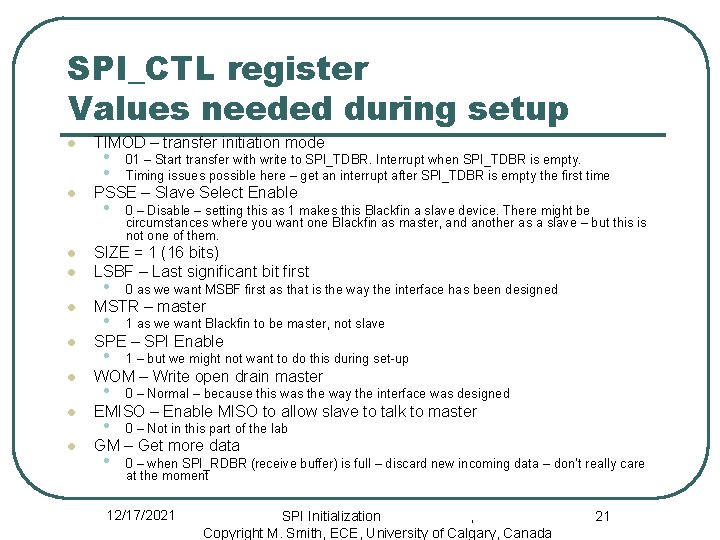

SPI_CTL register Values needed during setup l l l l l TIMOD – transfer initiation mode • • 01 – Start transfer with write to SPI_TDBR. Interrupt when SPI_TDBR is empty. Timing issues possible here – get an interrupt after SPI_TDBR is empty the first time • 0 – Disable – setting this as 1 makes this Blackfin a slave device. There might be circumstances where you want one Blackfin as master, and another as a slave – but this is not one of them. PSSE – Slave Select Enable SIZE = 1 (16 bits) LSBF – Last significant bit first • 0 as we want MSBF first as that is the way the interface has been designed • 1 as we want Blackfin to be master, not slave • 1 – but we might not want to do this during set-up • 0 – Normal – because this was the way the interface was designed • 0 – Not in this part of the lab • 0 – when SPI_RDBR (receive buffer) is full – discard new incoming data – don’t really care at the moment MSTR – master SPE – SPI Enable WOM – Write open drain master EMISO – Enable MISO to allow slave to talk to master GM – Get more data 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 21

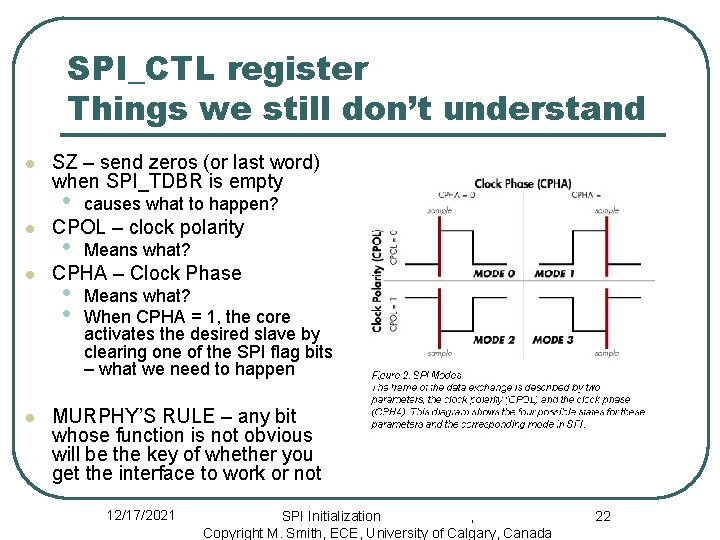

SPI_CTL register Things we still don’t understand l l SZ – send zeros (or last word) when SPI_TDBR is empty • causes what to happen? • Means what? • • Means what? When CPHA = 1, the core activates the desired slave by clearing one of the SPI flag bits – what we need to happen CPOL – clock polarity CPHA – Clock Phase MURPHY’S RULE – any bit whose function is not obvious will be the key of whether you get the interface to work or not 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 22

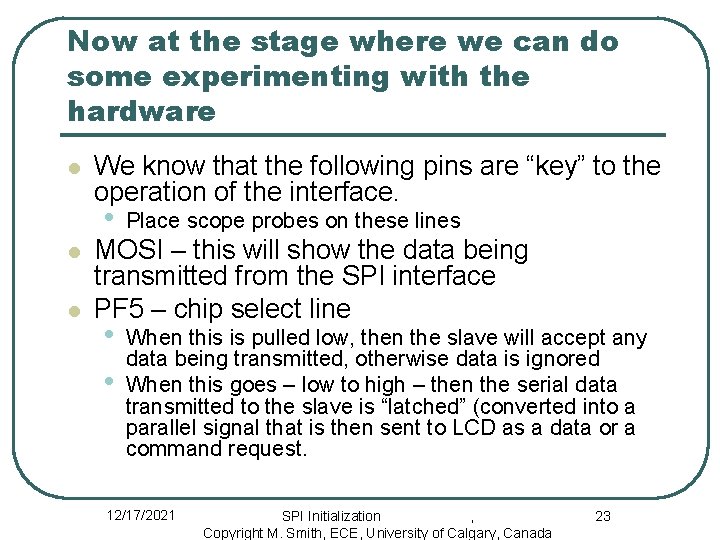

Now at the stage where we can do some experimenting with the hardware l l l We know that the following pins are “key” to the operation of the interface. • Place scope probes on these lines • • When this is pulled low, then the slave will accept any data being transmitted, otherwise data is ignored When this goes – low to high – then the serial data transmitted to the slave is “latched” (converted into a parallel signal that is then sent to LCD as a data or a command request. MOSI – this will show the data being transmitted from the SPI interface PF 5 – chip select line 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 23

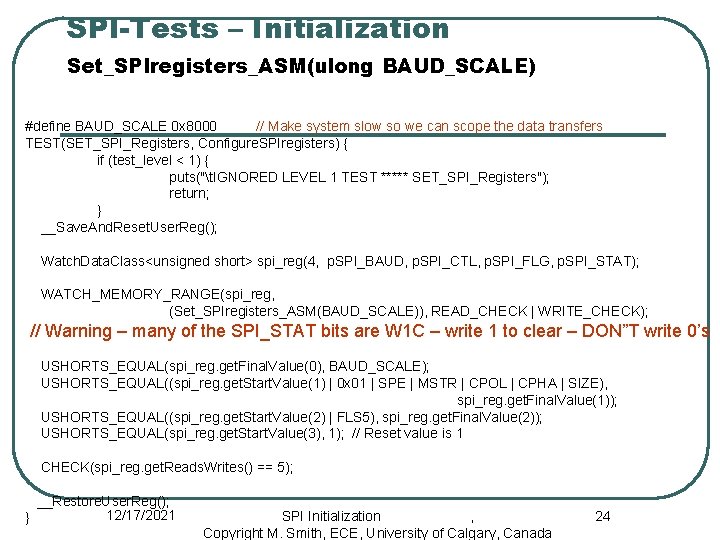

SPI-Tests – Initialization Set_SPIregisters_ASM(ulong BAUD_SCALE) #define BAUD_SCALE 0 x 8000 // Make system slow so we can scope the data transfers TEST(SET_SPI_Registers, Configure. SPIregisters) { if (test_level < 1) { puts("t. IGNORED LEVEL 1 TEST ***** SET_SPI_Registers"); return; } __Save. And. Reset. User. Reg(); Watch. Data. Class<unsigned short> spi_reg(4, p. SPI_BAUD, p. SPI_CTL, p. SPI_FLG, p. SPI_STAT); WATCH_MEMORY_RANGE(spi_reg, (Set_SPIregisters_ASM(BAUD_SCALE)), READ_CHECK | WRITE_CHECK); // Warning – many of the SPI_STAT bits are W 1 C – write 1 to clear – DON”T write 0’s USHORTS_EQUAL(spi_reg. get. Final. Value(0), BAUD_SCALE); USHORTS_EQUAL((spi_reg. get. Start. Value(1) | 0 x 01 | SPE | MSTR | CPOL | CPHA | SIZE), spi_reg. get. Final. Value(1)); USHORTS_EQUAL((spi_reg. get. Start. Value(2) | FLS 5), spi_reg. get. Final. Value(2)); USHORTS_EQUAL(spi_reg. get. Start. Value(3), 1); // Reset value is 1 CHECK(spi_reg. get. Reads. Writes() == 5); __Restore. User. Reg(); 12/17/2021 } SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 24

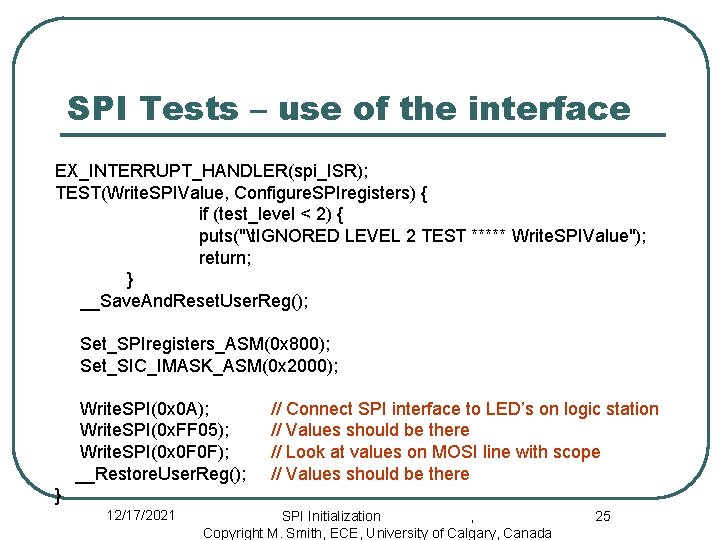

SPI Tests – use of the interface EX_INTERRUPT_HANDLER(spi_ISR); TEST(Write. SPIValue, Configure. SPIregisters) { if (test_level < 2) { puts("t. IGNORED LEVEL 2 TEST ***** Write. SPIValue"); return; } __Save. And. Reset. User. Reg(); Set_SPIregisters_ASM(0 x 800); Set_SIC_IMASK_ASM(0 x 2000); Write. SPI(0 x 0 A); Write. SPI(0 x. FF 05); Write. SPI(0 x 0 F 0 F); __Restore. User. Reg(); // Connect SPI interface to LED’s on logic station // Values should be there // Look at values on MOSI line with scope // Values should be there } 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 25

l Information taken from Analog Devices On-line Manuals with permission http: //www. analog. com/processors/resources/technical. Library/manuals/ l Information furnished by Analog Devices is believed to be accurate and reliable. However, Analog Devices assumes no responsibility for its use or for any infringement of any patent other rights of any third party which may result from its use. No license is granted by implication or otherwise under any patent or patent right of Analog Devices. Copyright Analog Devices, Inc. All rights reserved. 12/17/2021 SPI Initialization , Copyright M. Smith, ECE, University of Calgary, Canada 26

- Slides: 26