BITS Pilani Campus ES C 263 INSTRCSEEE F

BITS Pilani Campus ES C 263 INSTR/CS/EEE F 241 Microprocessor Programming and Interfacing Pawan Sharma Lecture 8 -9 19/22 -01 -2013

Last Lecture Ø Disk Organization Ø Ø Interpretation of Boot sector File Allocation Table Root Directory Example BITS Pilani, Pilani Campus

Today’s Lecture Ø 8086 architecture Ø Programmers Model BITS Pilani, Pilani Campus

8086 Architecture BITS Pilani, Pilani Campus

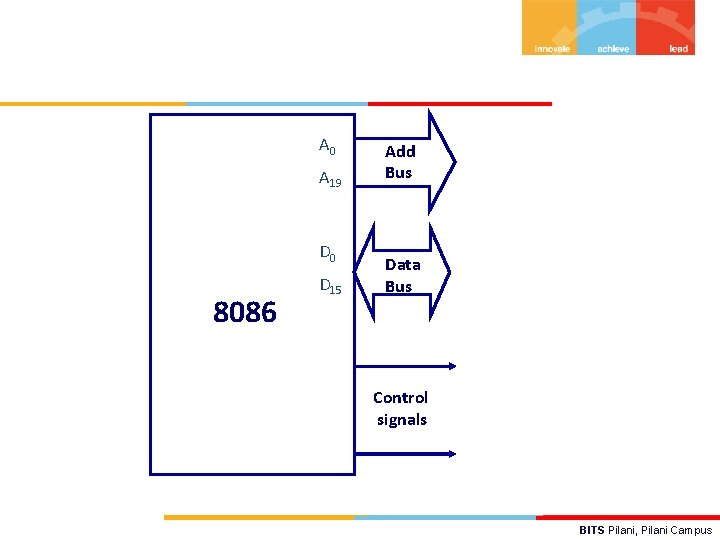

A 0 A 19 D 0 8086 D 15 Add Bus Data Bus Control signals BITS Pilani, Pilani Campus

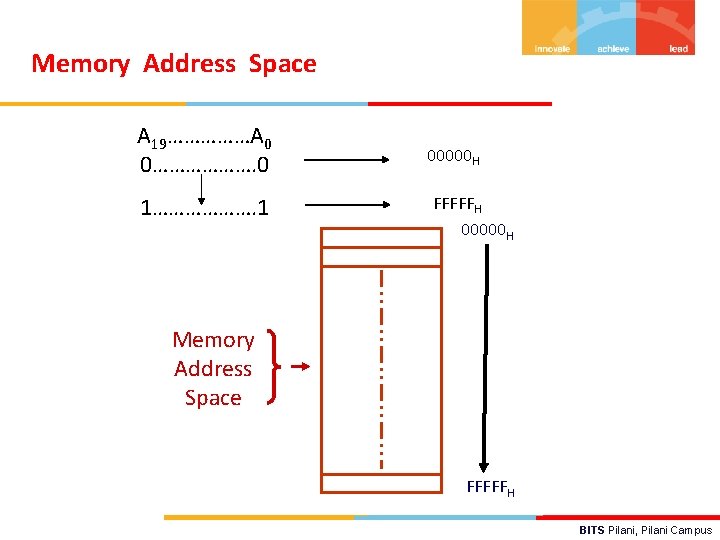

Memory Address Space A 19……………A 0 0………………. 0 1………………. 1 00000 H FFFFFH 00000 H Memory Address Space FFFFFH BITS Pilani, Pilani Campus

Real Mode Memory Addressing Ø Allows the microprocessor to address only the first 1 MB of memory space, even if it is Core 2 or i 5 or i 7 microprocessor. Ø First 1 MB of memory is called the DOS memory system. DOS requires the CPU to work in real mode. Ø Real mode is characterized by a 20 bit segmented memory address space (giving exactly 1 MB of addressable memory) and unlimited direct software access to all memory (no protection), I/O addresses and peripheral hardware. BITS Pilani, Pilani Campus

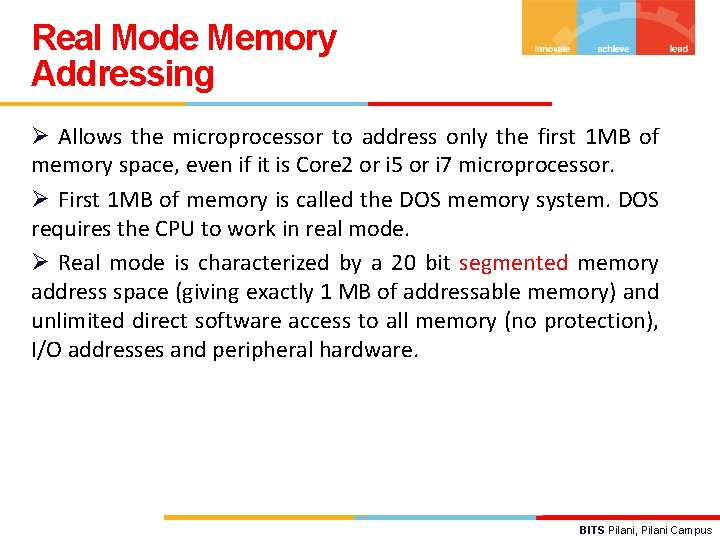

System Block Diagram Address bus BIU ROM RAM I/o Ports Discs Video Data Bus ALU CLK Control & Timing EU BITS Pilani, Pilani Campus

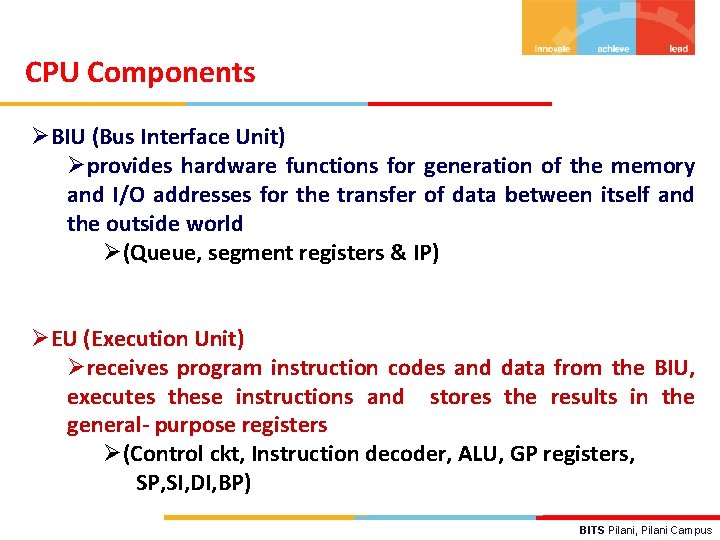

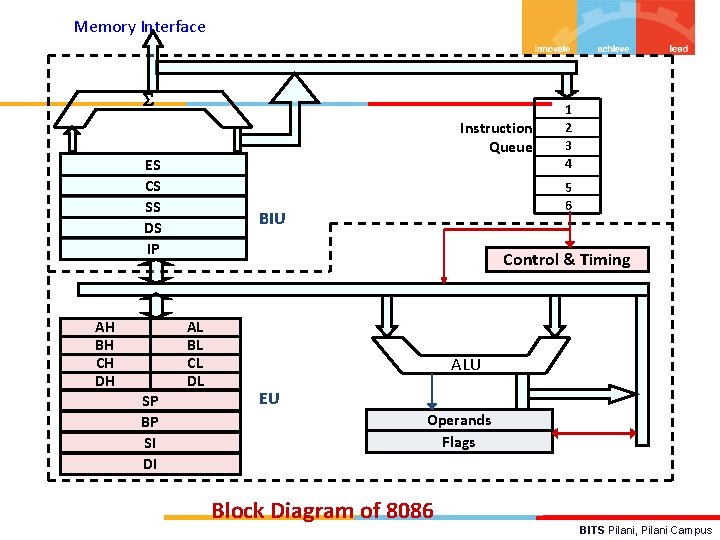

CPU Components ØBIU (Bus Interface Unit) Øprovides hardware functions for generation of the memory and I/O addresses for the transfer of data between itself and the outside world Ø(Queue, segment registers & IP) ØEU (Execution Unit) Øreceives program instruction codes and data from the BIU, executes these instructions and stores the results in the general- purpose registers Ø(Control ckt, Instruction decoder, ALU, GP registers, SP, SI, DI, BP) BITS Pilani, Pilani Campus

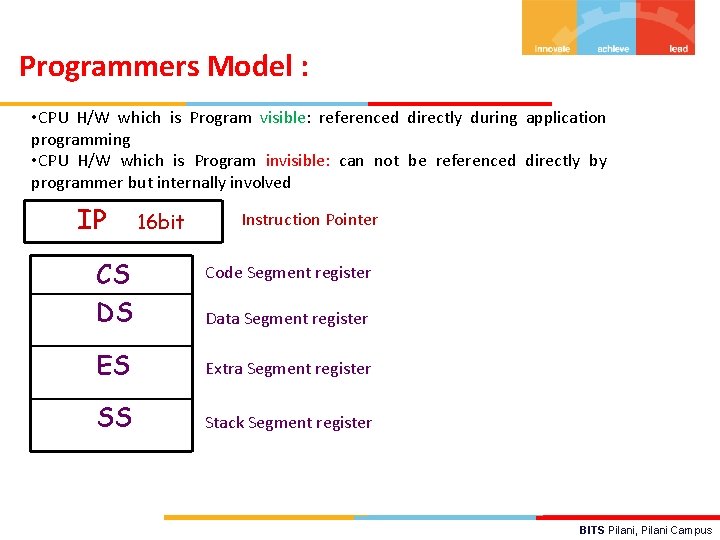

Programmers Model : • CPU H/W which is Program visible: referenced directly during application programming • CPU H/W which is Program invisible: can not be referenced directly by programmer but internally involved IP 16 bit Instruction Pointer CS DS Data Segment register ES Extra Segment register SS Stack Segment register Code Segment register BITS Pilani, Pilani Campus

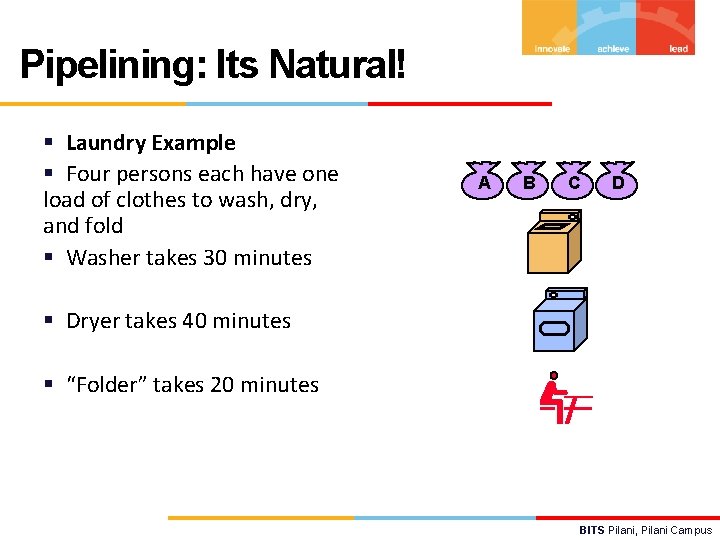

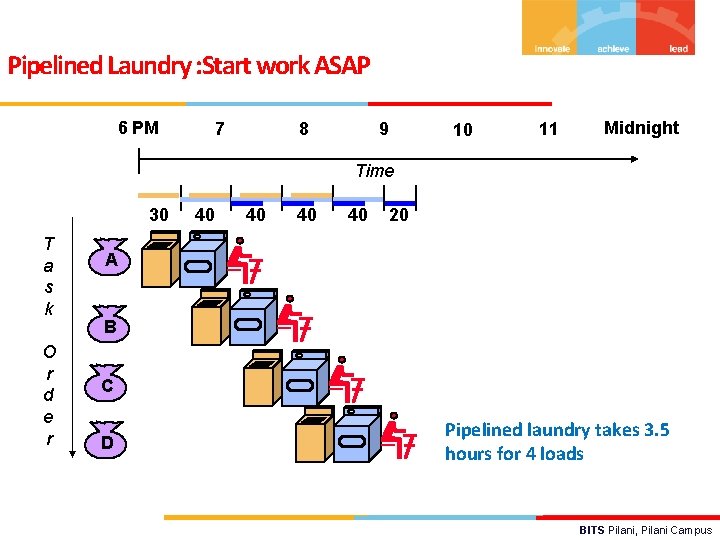

Pipelining: Its Natural! § Laundry Example § Four persons each have one load of clothes to wash, dry, and fold § Washer takes 30 minutes A B C D § Dryer takes 40 minutes § “Folder” takes 20 minutes BITS Pilani, Pilani Campus

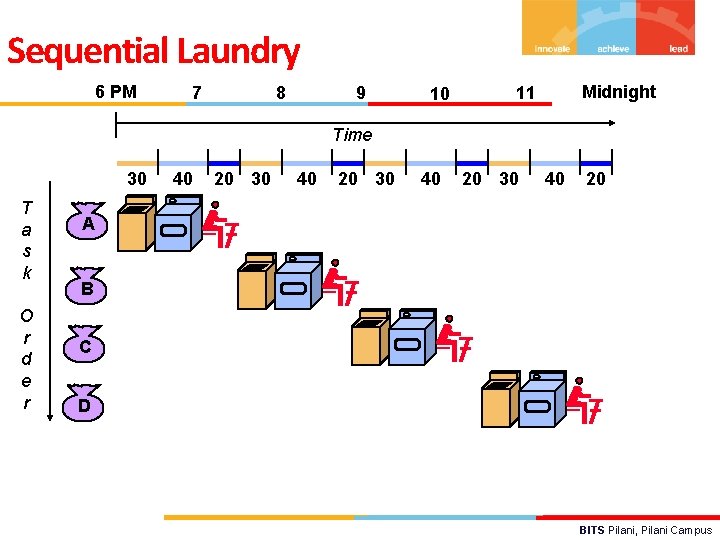

Sequential Laundry 6 PM 7 8 9 10 Midnight 11 Time 30 T a s k O r d e r 40 20 30 40 20 A B C D BITS Pilani, Pilani Campus

Pipelined Laundry : Start work ASAP 6 PM 7 8 9 10 11 Midnight Time 30 T a s k O r d e r 40 40 20 A B C D Pipelined laundry takes 3. 5 hours for 4 loads BITS Pilani, Pilani Campus

Key Definitions ØPipelining is a key implementation technique used to build fast processors. It allows the execution of multiple instructions to overlap in time. ØThe throughput of an instruction pipeline is the measure of how often an instruction exits the pipeline. BITS Pilani, Pilani Campus

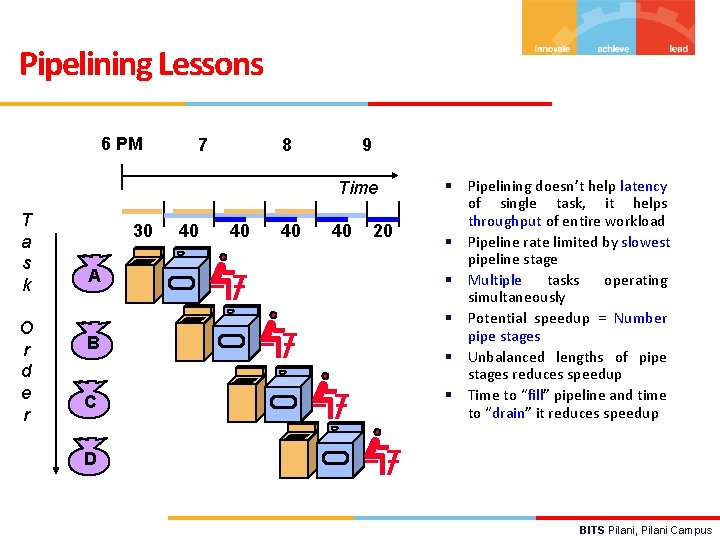

Pipelining Lessons 6 PM 7 8 9 Time T a s k O r d e r 30 A B C 40 40 20 § Pipelining doesn’t help latency of single task, it helps throughput of entire workload § Pipeline rate limited by slowest pipeline stage § Multiple tasks operating simultaneously § Potential speedup = Number pipe stages § Unbalanced lengths of pipe stages reduces speedup § Time to “fill” pipeline and time to “drain” it reduces speedup D BITS Pilani, Pilani Campus

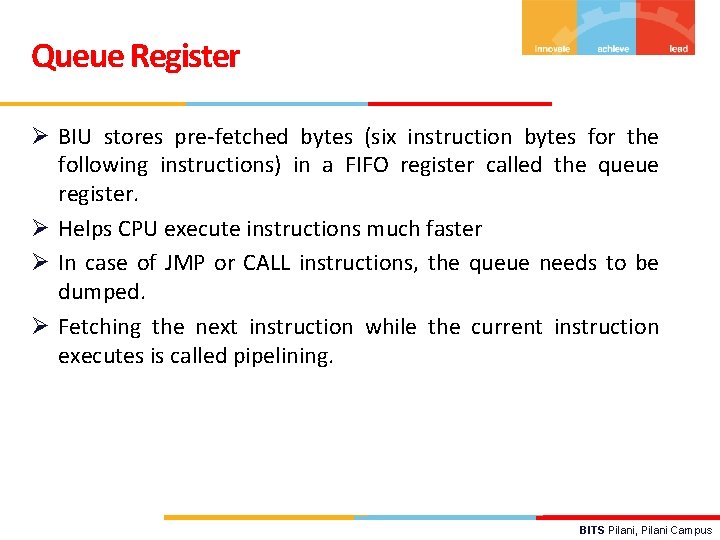

Queue Register Ø BIU stores pre-fetched bytes (six instruction bytes for the following instructions) in a FIFO register called the queue register. Ø Helps CPU execute instructions much faster Ø In case of JMP or CALL instructions, the queue needs to be dumped. Ø Fetching the next instruction while the current instruction executes is called pipelining. BITS Pilani, Pilani Campus

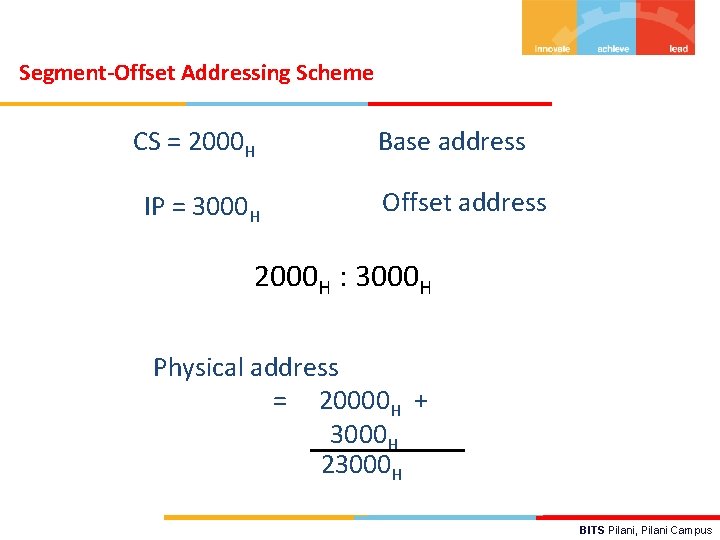

Segment-Offset Addressing Scheme CS = 2000 H IP = 3000 H Base address Offset address 2000 H : 3000 H Physical address = 20000 H + 3000 H 23000 H BITS Pilani, Pilani Campus

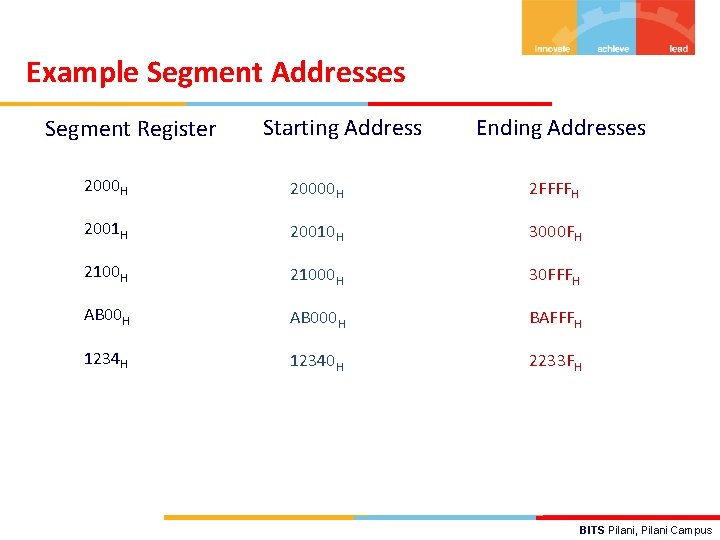

Example Segment Addresses Segment Register Starting Address Ending Addresses 2000 H 20000 H 2 FFFFH 20010 H 3000 FH 21000 H 30 FFFH AB 000 H BAFFFH 12340 H 2233 FH BITS Pilani, Pilani Campus

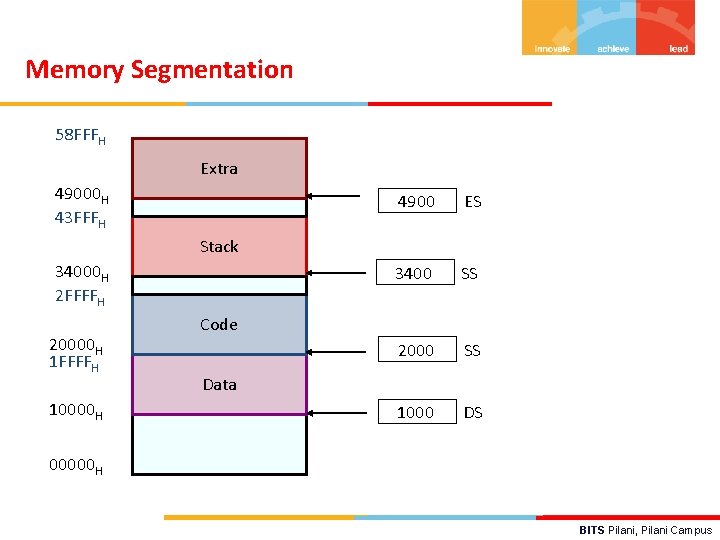

Memory Segmentation 58 FFFH Extra 49000 H 43 FFFH 4900 ES 3400 SS 2000 SS 1000 DS Stack 34000 H 2 FFFFH 20000 H 1 FFFFH 10000 H Code Data 00000 H BITS Pilani, Pilani Campus

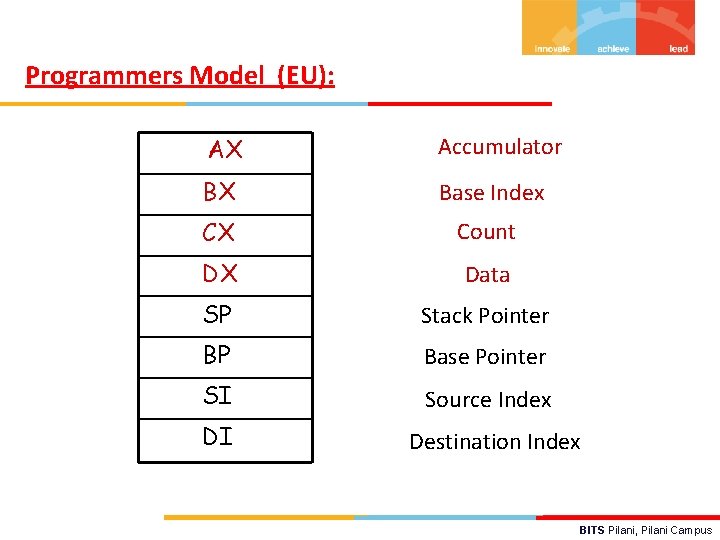

Programmers Model (EU): AX Accumulator BX Base Index CX Count DX Data SP Stack Pointer BP Base Pointer SI Source Index DI Destination Index BITS Pilani, Pilani Campus

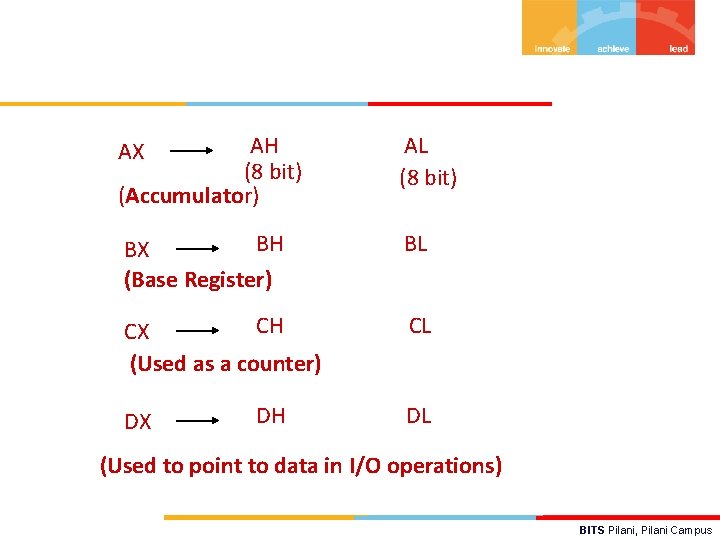

AX AH (8 bit) (Accumulator) AL (8 bit) BH BX (Base Register) BL CH CX (Used as a counter) CL DX DH DL (Used to point to data in I/O operations) BITS Pilani, Pilani Campus

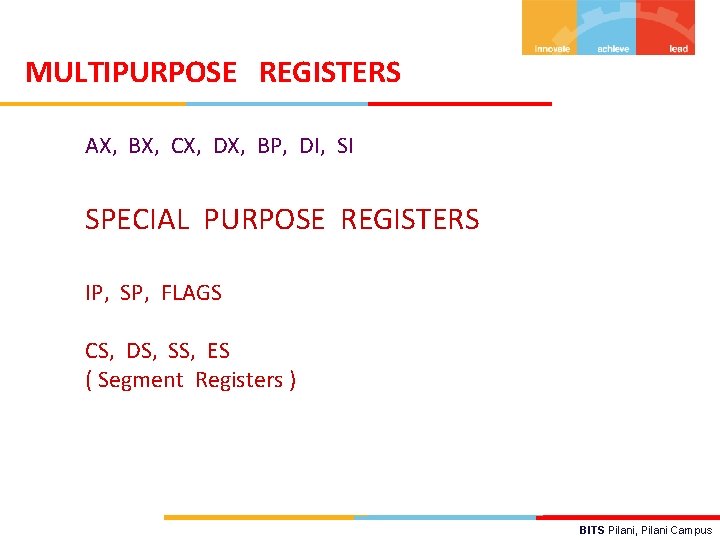

MULTIPURPOSE REGISTERS AX, BX, CX, DX, BP, DI, SI SPECIAL PURPOSE REGISTERS IP, SP, FLAGS CS, DS, SS, ES ( Segment Registers ) BITS Pilani, Pilani Campus

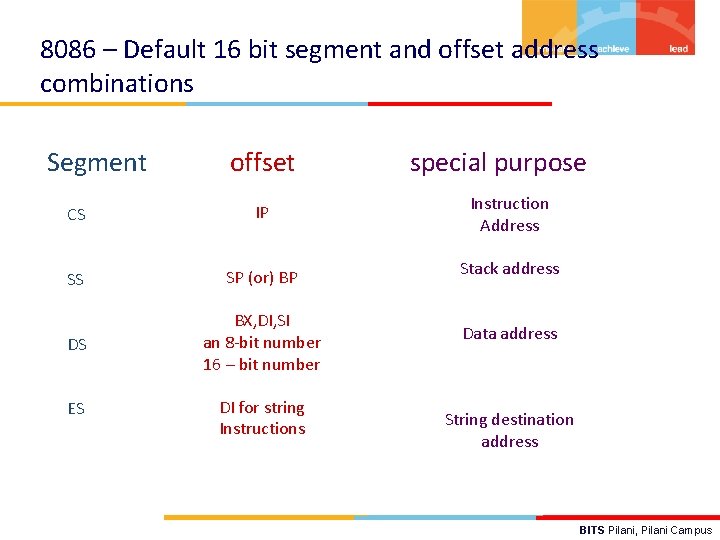

8086 – Default 16 bit segment and offset address combinations Segment offset CS IP SS SP (or) BP DS BX, DI, SI an 8 -bit number 16 – bit number ES DI for string Instructions special purpose Instruction Address Stack address Data address String destination address BITS Pilani, Pilani Campus

32 -bit registers in 80386 through Core 2 EAX AX EBX BX ECX CX EDX DX ESP SP EBP BP BITS Pilani, Pilani Campus

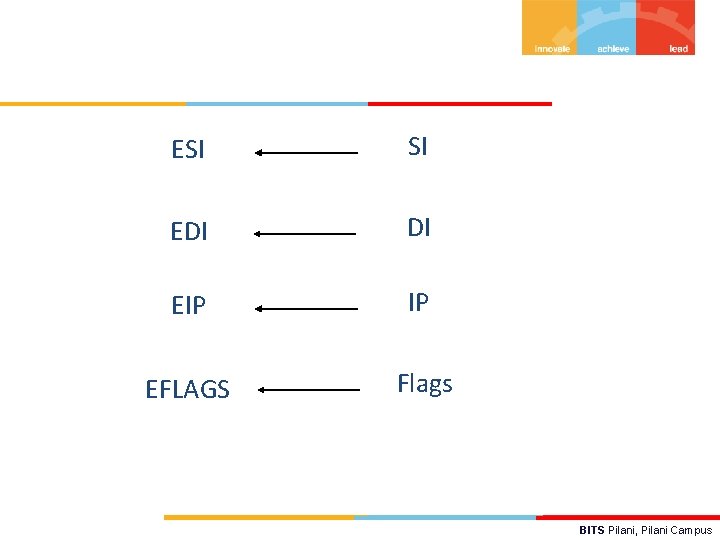

ESI SI EDI DI EIP IP EFLAGS Flags BITS Pilani, Pilani Campus

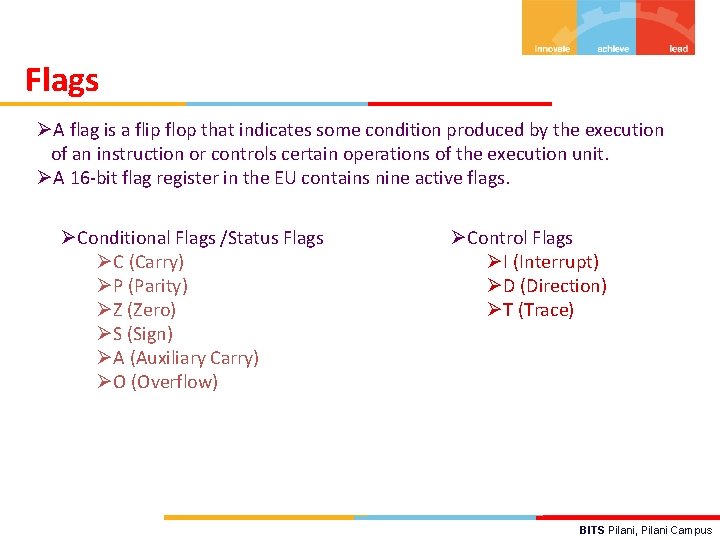

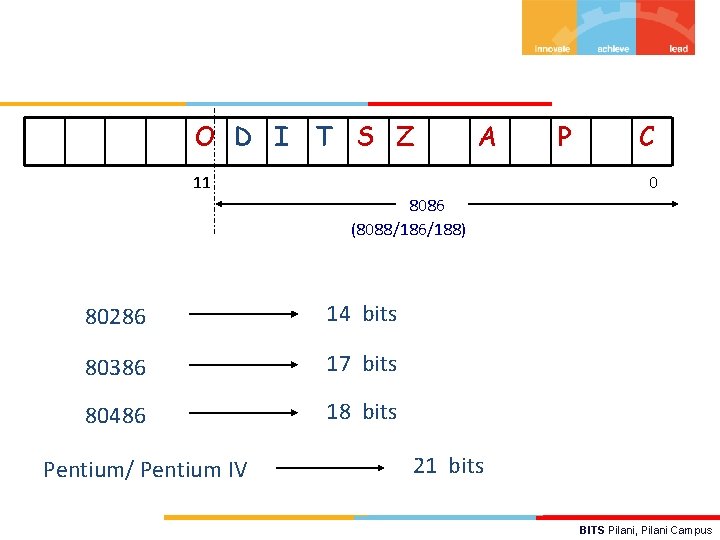

Flags ØA flag is a flip flop that indicates some condition produced by the execution of an instruction or controls certain operations of the execution unit. ØA 16 -bit flag register in the EU contains nine active flags. ØConditional Flags /Status Flags ØC (Carry) ØP (Parity) ØZ (Zero) ØS (Sign) ØA (Auxiliary Carry) ØO (Overflow) ØControl Flags ØI (Interrupt) ØD (Direction) ØT (Trace) BITS Pilani, Pilani Campus

O D I T S Z A 11 P C 0 8086 (8088/186/188) 80286 14 bits 80386 17 bits 80486 18 bits Pentium/ Pentium IV 21 bits BITS Pilani, Pilani Campus

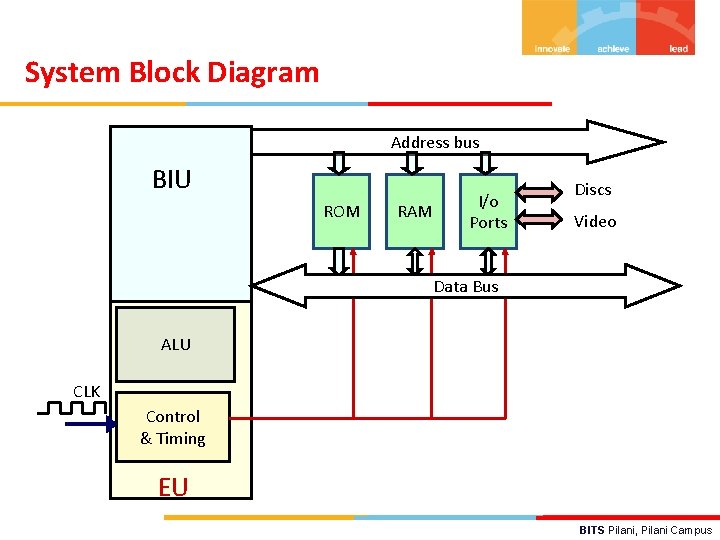

Memory Interface Instruction Queue ES CS SS DS IP AH BH CH DH SP BP SI DI 1 2 3 4 5 6 BIU Control & Timing AL BL CL DL ALU EU Operands Flags Block Diagram of 8086 BITS Pilani, Pilani Campus

- Slides: 28