A Closer Look at Instruction Set Architectures Chapter

- Slides: 19

A Closer Look at Instruction Set Architectures Chapter 5 1 Dr. Clincy

Introduction • In Ch 4, we learned that machine instructions consist of opcodes and operands. Opcodes specify the operations to be executed; operands specify register or memory locations of data. • Sections 5. 1 and 5. 2 builds upon the ideas in Chapter 4 and looks more closer at Instruction Set Architecture (ISA) – specifically, the instruction format • We will look at different instruction formats • We will see the interrelation between machine organization and instruction formats. • By understanding a high-level language’s low-level instruction set architecture and format, this leads to a deeper understanding of the computer’s architecture in general. • As a computer scientist, in understanding the computer’s architecture in more detail, you can build more efficient and reliable programsm • When a computer architecture is in the design phase, the instruction set format must be determined first – it must match the architecture and last for years Dr. Clincy 2

Instruction Formats Instruction sets are differentiated by the following: • Number of bits per instruction (16, 32, 64). • How the data is stored (Stack-based or register-based). • Number of explicit operands per instruction (0, 1, 2 or 3). • Operand location (instructions can be classified as register-to-register, register-to-memory or memory-tomemory). • Types of operations (or instructions) and which instructions can access memory or not. • Type and size of operands (operands can be addresses, numbers or characters). 3 Dr. Clincy

Instruction Formats As mentioned earlier, when a computer architecture is in the design phase, the instruction set format must be determined first – it must match the architecture and last for years. Instruction set architectures are measured several factors: • the amount of space a program requires. • Instruction complexity (ie. decoding required). • Instruction length (in bits). • total number of instructions in the instruction set. 4 Dr. Clincy

Instruction Formats Issues to consider when designing an instruction set: • Instruction length. – Whether short, long, or variable. – Short uses less space but is limited – Fixed size is easier to decode but wastes space • Memory organization. – Whether byte- or word addressable. – If memory has words and not byte-addressable, it could be difficult to access a single character (4 bits) • Number of operands. • How should operands be stored in the CPU • Number of addressable registers. • How many registers ? • How should the registers be organized ? • Addressing modes. – Choose any or all: direct, indirect or indexed. For example, MARIE used the direct and indirect addressing modes – Given a byte-addressable machine, should the least significant byte be stored at the highest or lowest byte address ? Little Endian Vs Big Endian debate) 5 Dr. Clincy

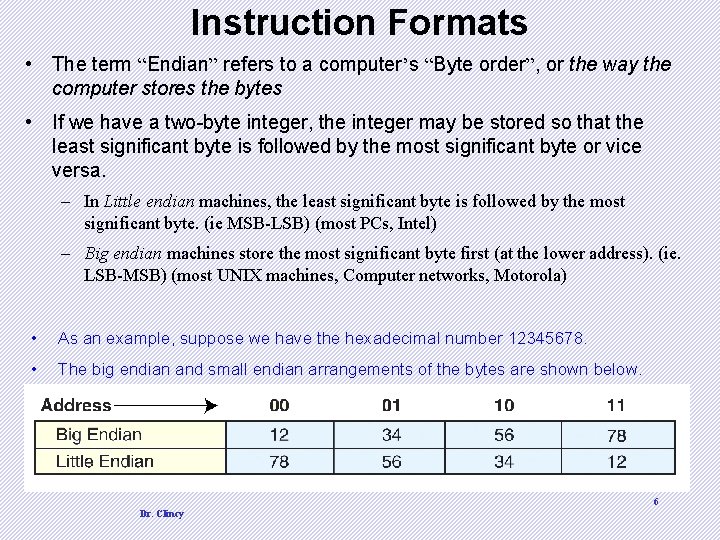

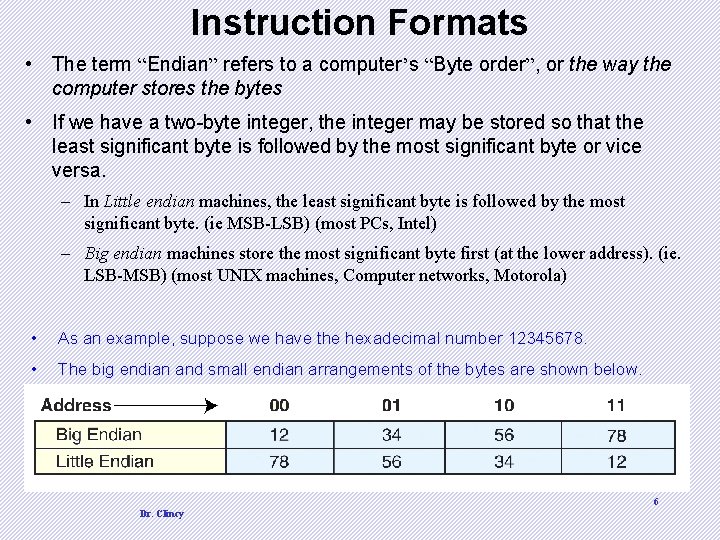

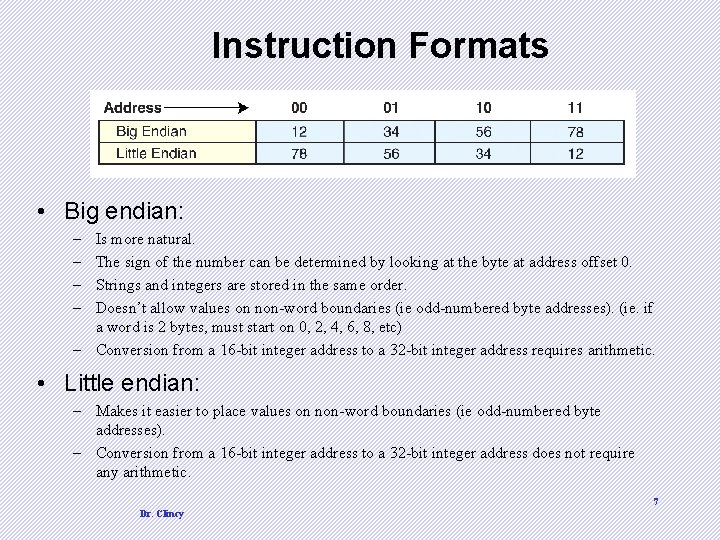

Instruction Formats • The term “Endian” refers to a computer’s “Byte order”, or the way the computer stores the bytes • If we have a two-byte integer, the integer may be stored so that the least significant byte is followed by the most significant byte or vice versa. – In Little endian machines, the least significant byte is followed by the most significant byte. (ie MSB-LSB) (most PCs, Intel) – Big endian machines store the most significant byte first (at the lower address). (ie. LSB-MSB) (most UNIX machines, Computer networks, Motorola) • As an example, suppose we have the hexadecimal number 12345678. • The big endian and small endian arrangements of the bytes are shown below. 6 Dr. Clincy

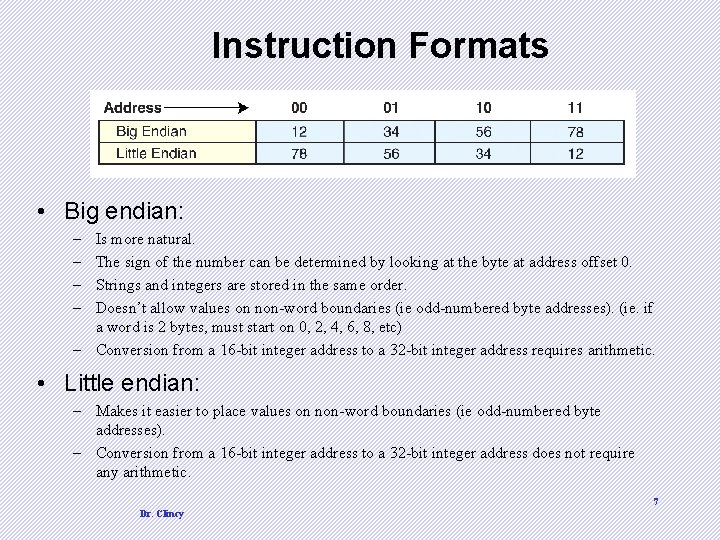

Instruction Formats • Big endian: – – Is more natural. The sign of the number can be determined by looking at the byte at address offset 0. Strings and integers are stored in the same order. Doesn’t allow values on non-word boundaries (ie odd-numbered byte addresses). (ie. if a word is 2 bytes, must start on 0, 2, 4, 6, 8, etc) – Conversion from a 16 -bit integer address to a 32 -bit integer address requires arithmetic. • Little endian: – Makes it easier to place values on non-word boundaries (ie odd-numbered byte addresses). – Conversion from a 16 -bit integer address to a 32 -bit integer address does not require any arithmetic. 7 Dr. Clincy

Instruction Formats • Once the designer decides on how the bytes should be ordered in memory, • the next consideration for the architecture design is how the CPU will store data. • We have three choices: 1. A stack architecture 2. An accumulator architecture 3. A general purpose register architecture. • In choosing one over the other, the tradeoffs are simplicity (and cost) of hardware design with execution speed and ease of use. 8 Dr. Clincy

Instruction Formats • In a stack architecture, instructions and operands are implicitly taken from the stack. – A stack cannot be accessed randomly. • In an accumulator architecture, one operand of a binary operation is implicitly in the accumulator. – One operand is in memory, creating lots of bus traffic. • In a general purpose register (GPR) architecture, registers can be used instead of memory. – Faster than accumulator architecture. – Efficient implementation for compilers. – Results in longer instructions. 9 Dr. Clincy

Instruction Formats • Most systems today are GPR systems. • There are three types: – Memory-memory where two or three operands may be in memory. – Register-memory where at least one operand must be in a register. – Load-store where no operands may be in memory. • The number of operands and the number of available registers has a direct affect on instruction length. 10 Dr. Clincy

Instruction Formats • Machine instructions that have no operands must use a stack (last in, first out (LIFO)) • Stack architectures make use of “push” and “pop” instructions. – Push X places the data in memory location X onto the stack – Pop X removes the top element in the stack and stores it at location X. • Stack architectures require us to think about arithmetic expressions a little differently. • We are accustomed to writing expressions using infix notation, such as: Z = X + Y. • Stack arithmetic requires that we use postfix notation: Z = XY+. – This is also called reverse Polish notation, (somewhat) in honor of its Polish inventor, Jan Lukasiewicz (1878 - 1956). – places the operator after the operands 11 Dr. Clincy

Instruction Formats • Example 1 – Adding use a stack – CPU adds the top two elements of the stack, popping them both – And then push the sum onto the top of the stack • Example 2 – Subtracting use a stack – The top stack element is subtracted from the next-to-the top element, both are popped – And the result is pushed onto the top of the stack 12 Dr. Clincy

Instruction Formats • The principal advantage of postfix notation is that parentheses are not used. • The infix expression “ 3 + 4” is the postfix equivalent of “ 3 4 +” • For example, the infix expression, Z = (X Y) + (W U), becomes: Z = X Y W U + in postfix notation. 13 Dr. Clincy

Instruction Formats • Example: Convert the infix expression (2+3) - 6/3 to postfix: 2 3+ - 6 3/ The division operator takes next precedence; we replace 6/3 with 6 3 /. 2 3+ 6 3/ - The quotient 6/3 is subtracted from the sum of 2 + 3, so we move the - operator to the end. 14 Dr. Clincy

Instruction Formats • We have seen how instruction length is affected by the number of operands supported by the ISA. • In any instruction set, not all instructions require the same number of operands. • Operations that require no operands, such as HALT, necessarily waste some space when fixed-length instructions are used. • One way to recover some of this space is to use expanding opcodes. 15 Dr. Clincy

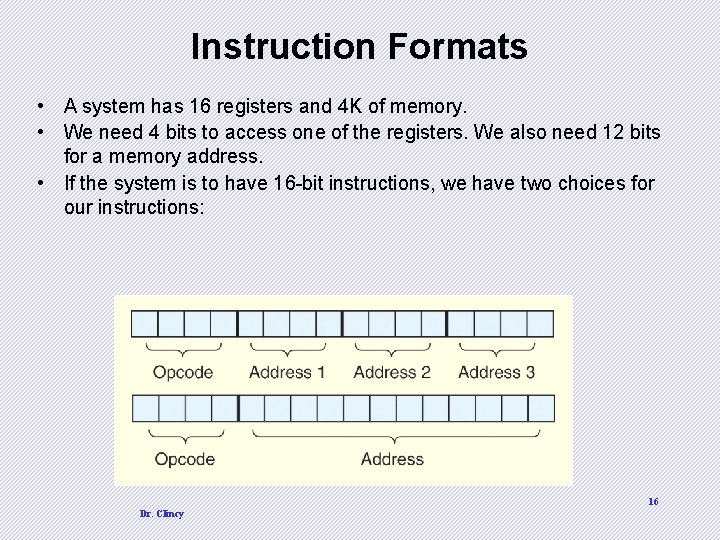

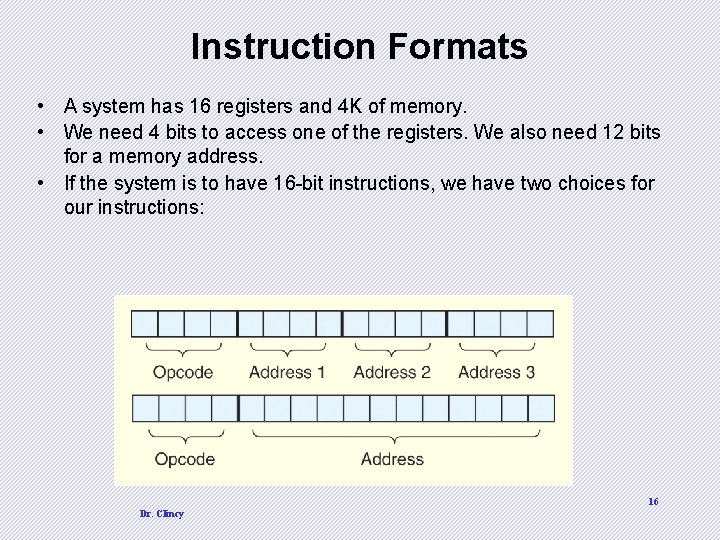

Instruction Formats • A system has 16 registers and 4 K of memory. • We need 4 bits to access one of the registers. We also need 12 bits for a memory address. • If the system is to have 16 -bit instructions, we have two choices for our instructions: 16 Dr. Clincy

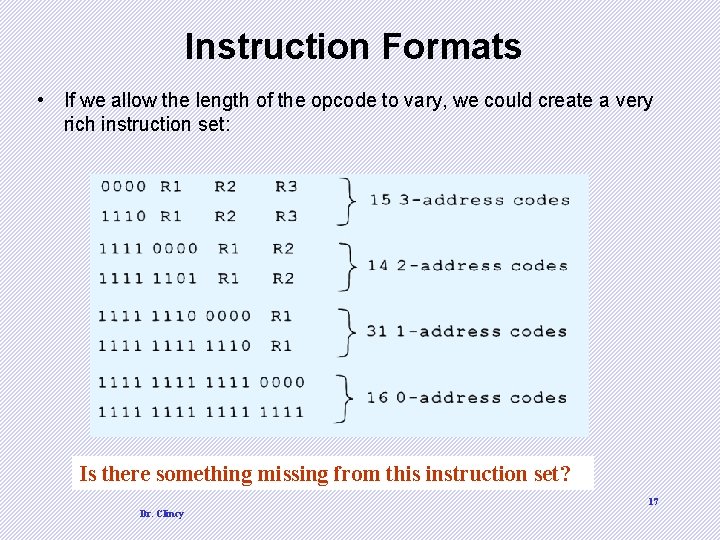

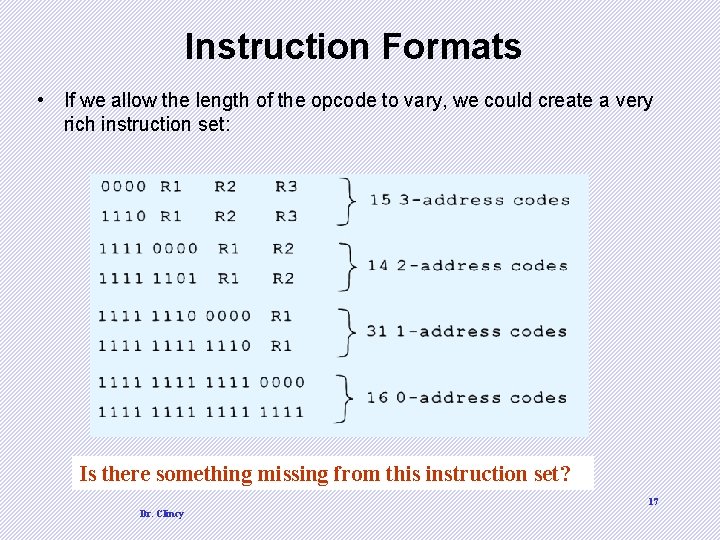

Instruction Formats • If we allow the length of the opcode to vary, we could create a very rich instruction set: Is there something missing from this instruction set? 17 Dr. Clincy

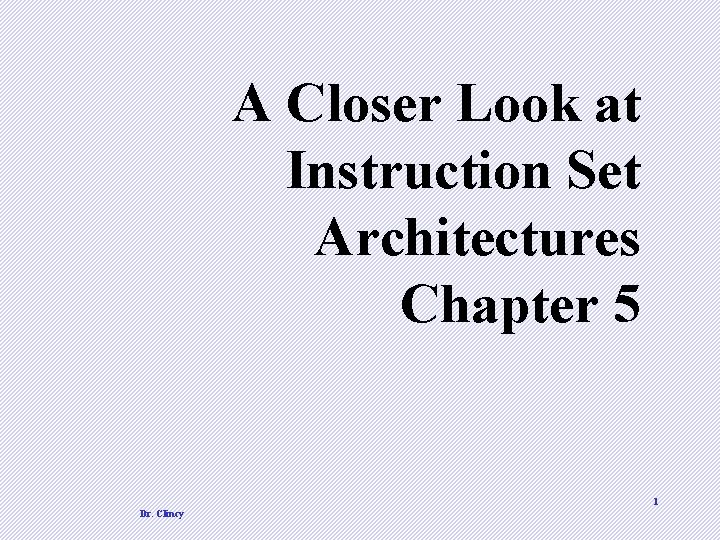

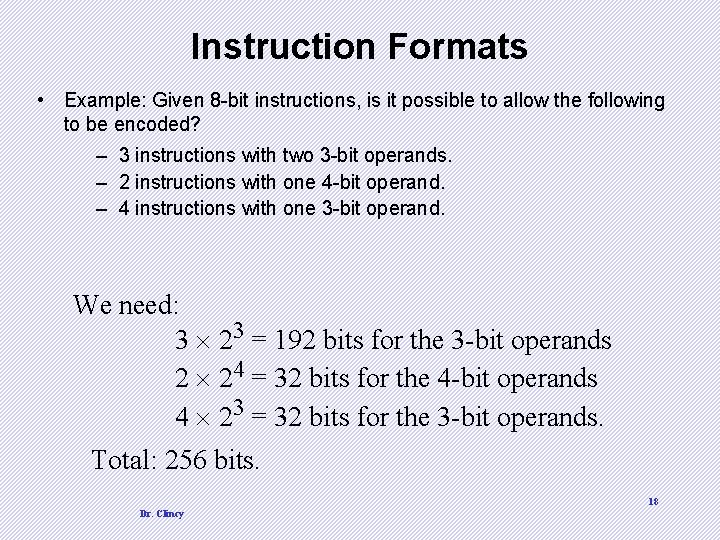

Instruction Formats • Example: Given 8 -bit instructions, is it possible to allow the following to be encoded? – 3 instructions with two 3 -bit operands. – 2 instructions with one 4 -bit operand. – 4 instructions with one 3 -bit operand. We need: 3 23 = 192 bits for the 3 -bit operands 2 24 = 32 bits for the 4 -bit operands 4 23 = 32 bits for the 3 -bit operands. Total: 256 bits. 18 Dr. Clincy

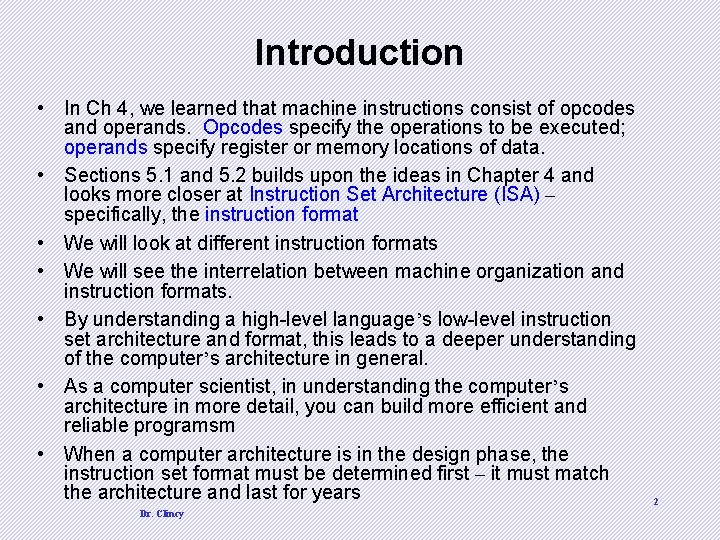

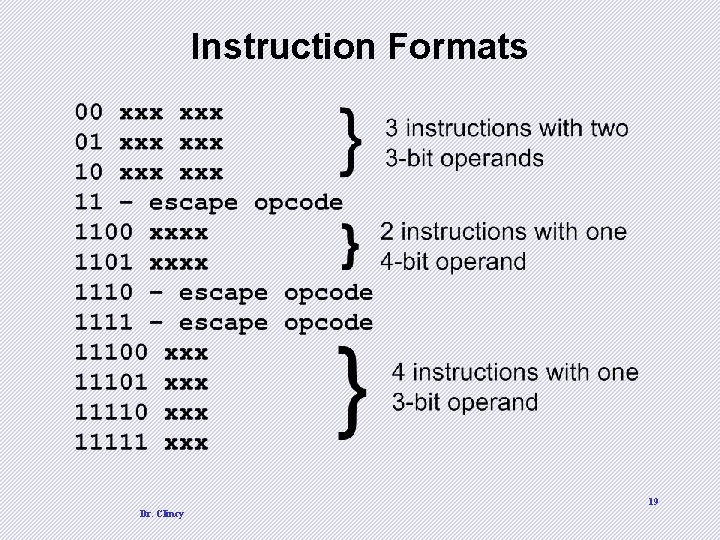

Instruction Formats 19 Dr. Clincy