Verilog Tutorial Part II Structural descriptions Structural descriptions

- Slides: 7

Verilog Tutorial – Part II

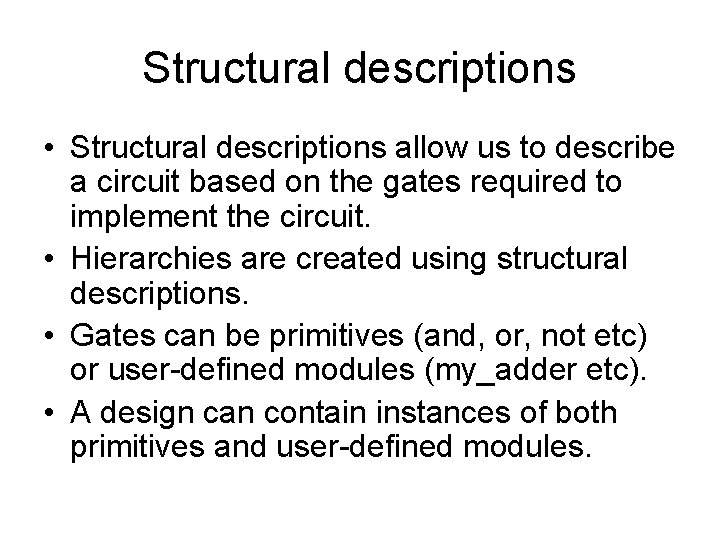

Structural descriptions • Structural descriptions allow us to describe a circuit based on the gates required to implement the circuit. • Hierarchies are created using structural descriptions. • Gates can be primitives (and, or, not etc) or user-defined modules (my_adder etc). • A design can contain instances of both primitives and user-defined modules.

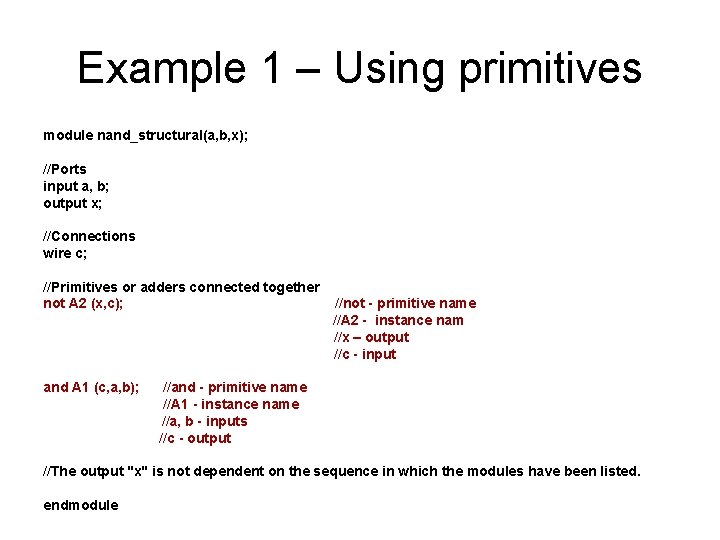

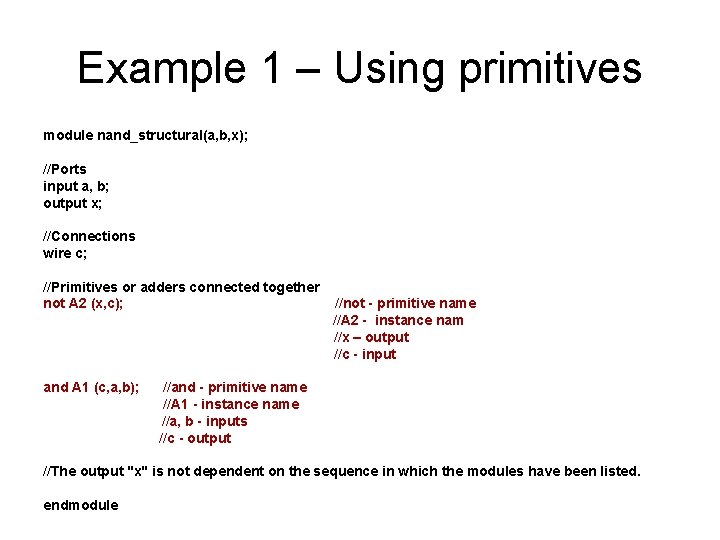

Example 1 – Using primitives module nand_structural(a, b, x); //Ports input a, b; output x; //Connections wire c; //Primitives or adders connected together not A 2 (x, c); and A 1 (c, a, b); //not - primitive name //A 2 - instance nam //x – output //c - input //and - primitive name //A 1 - instance name //a, b - inputs //c - output //The output "x" is not dependent on the sequence in which the modules have been listed. endmodule

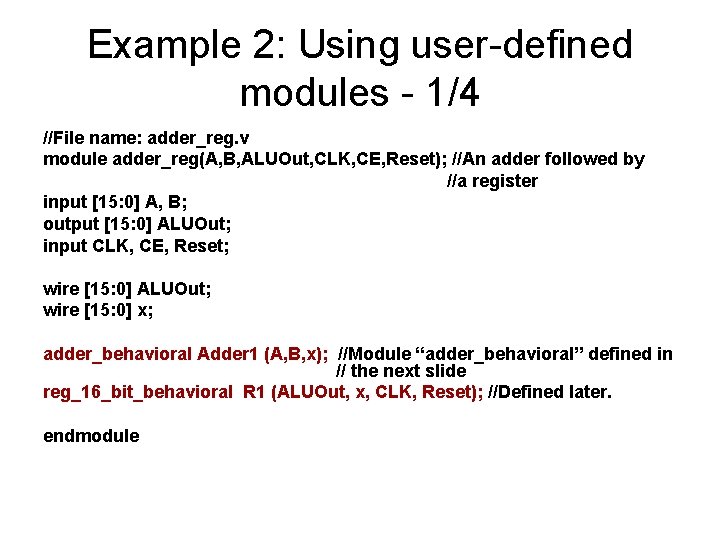

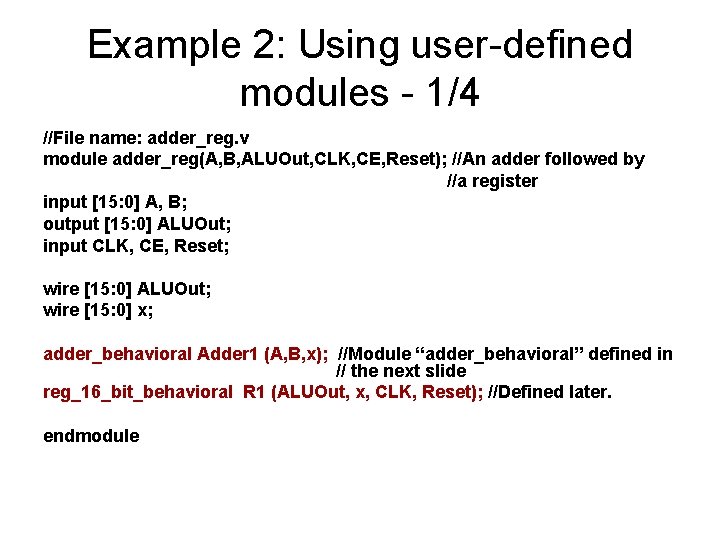

Example 2: Using user-defined modules - 1/4 //File name: adder_reg. v module adder_reg(A, B, ALUOut, CLK, CE, Reset); //An adder followed by //a register input [15: 0] A, B; output [15: 0] ALUOut; input CLK, CE, Reset; wire [15: 0] ALUOut; wire [15: 0] x; adder_behavioral Adder 1 (A, B, x); //Module “adder_behavioral” defined in // the next slide reg_16_bit_behavioral R 1 (ALUOut, x, CLK, Reset); //Defined later. endmodule

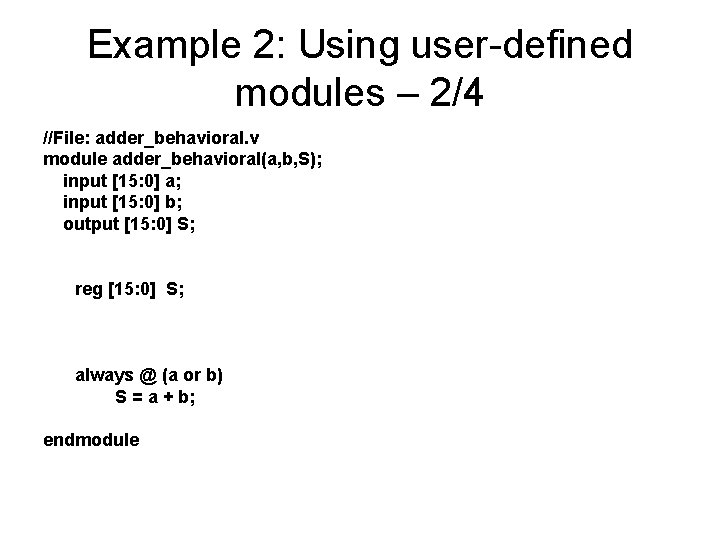

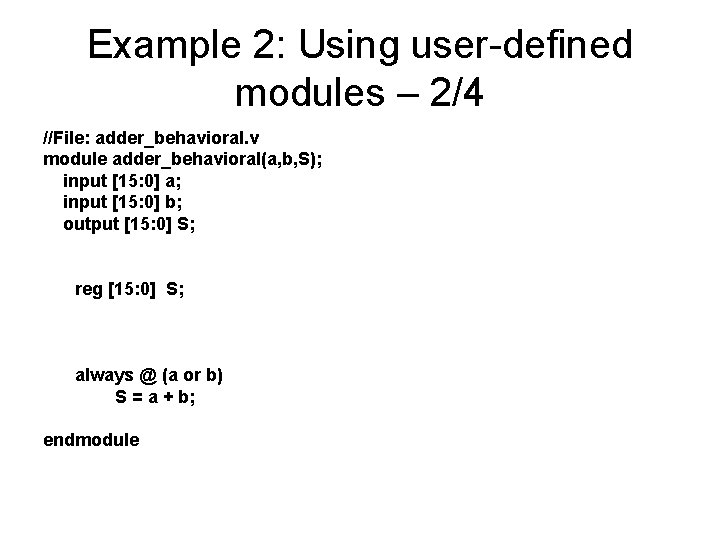

Example 2: Using user-defined modules – 2/4 //File: adder_behavioral. v module adder_behavioral(a, b, S); input [15: 0] a; input [15: 0] b; output [15: 0] S; reg [15: 0] S; always @ (a or b) S = a + b; endmodule

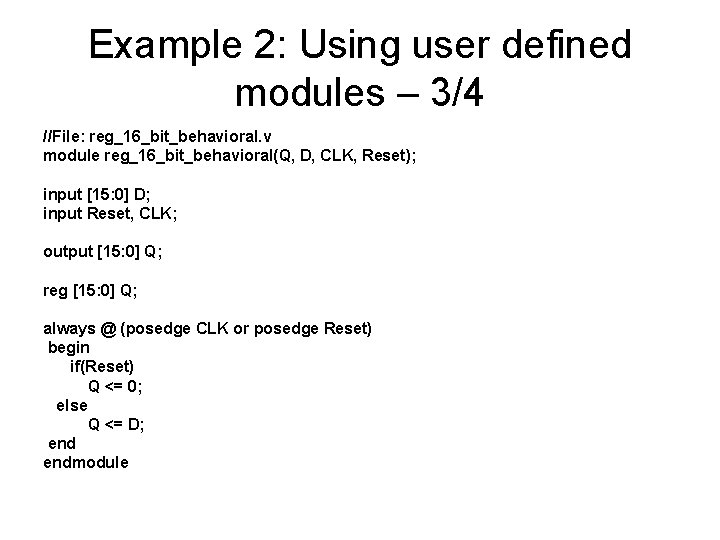

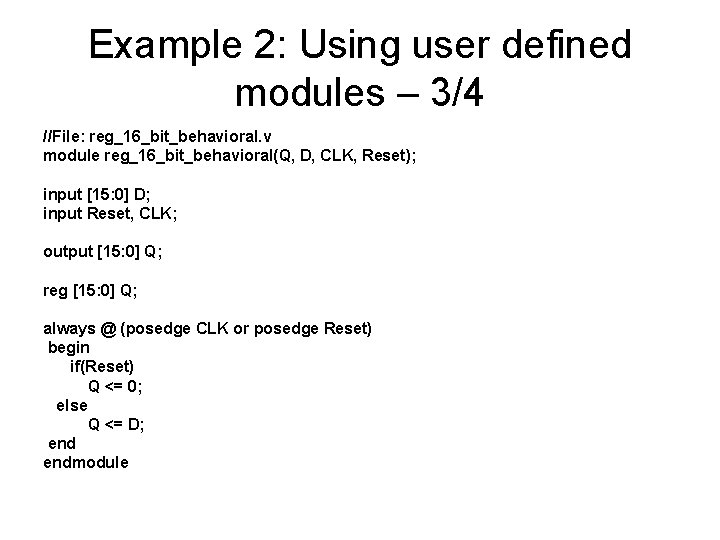

Example 2: Using user defined modules – 3/4 //File: reg_16_bit_behavioral. v module reg_16_bit_behavioral(Q, D, CLK, Reset); input [15: 0] D; input Reset, CLK; output [15: 0] Q; reg [15: 0] Q; always @ (posedge CLK or posedge Reset) begin if(Reset) Q <= 0; else Q <= D; endmodule

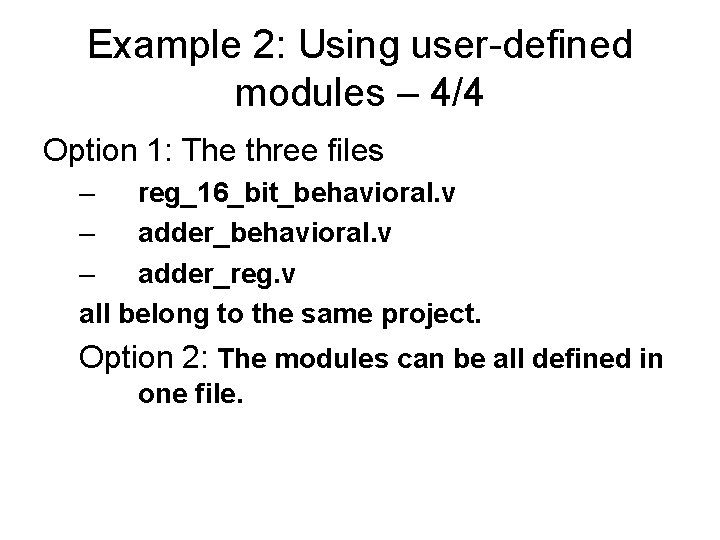

Example 2: Using user-defined modules – 4/4 Option 1: The three files – reg_16_bit_behavioral. v – adder_reg. v all belong to the same project. Option 2: The modules can be all defined in one file.