Behavioral Modeling I 1 Structural vs Behavioral Descriptions

Behavioral Modeling I 1

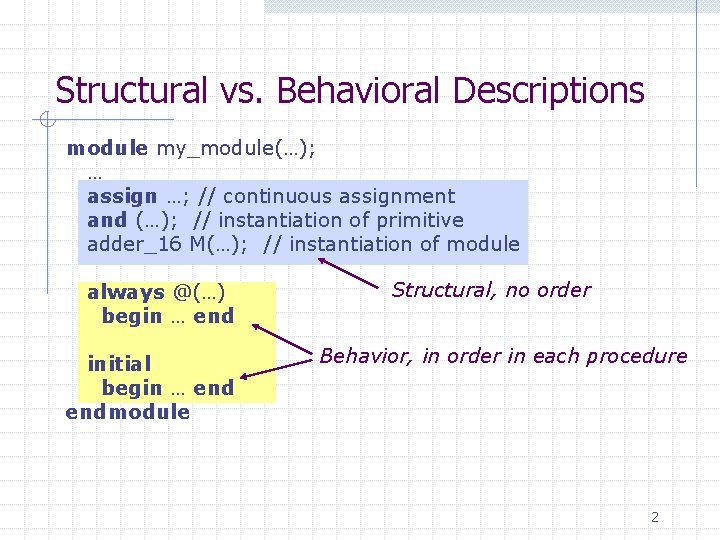

Structural vs. Behavioral Descriptions module my_module(…); … assign …; // continuous assignment and (…); // instantiation of primitive adder_16 M(…); // instantiation of module always @(…) begin … end initial begin … endmodule Structural, no order Behavior, in order in each procedure 2

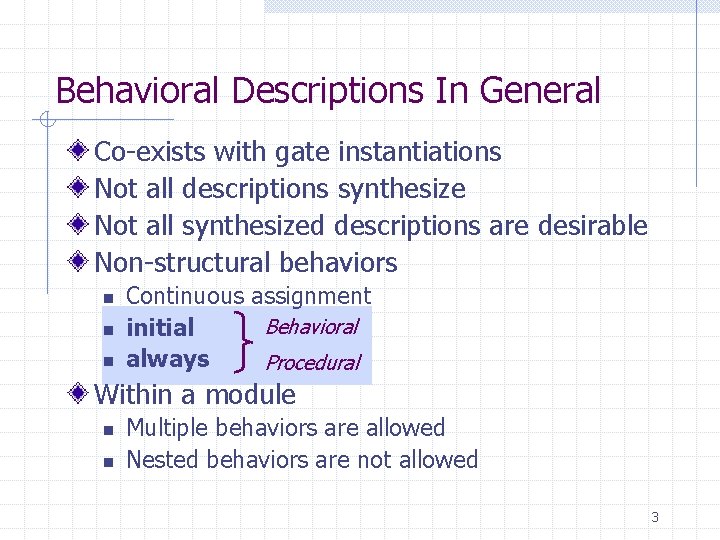

Behavioral Descriptions In General Co-exists with gate instantiations Not all descriptions synthesize Not all synthesized descriptions are desirable Non-structural behaviors n n n Continuous assignment Behavioral initial always Procedural Within a module n n Multiple behaviors are allowed Nested behaviors are not allowed 3

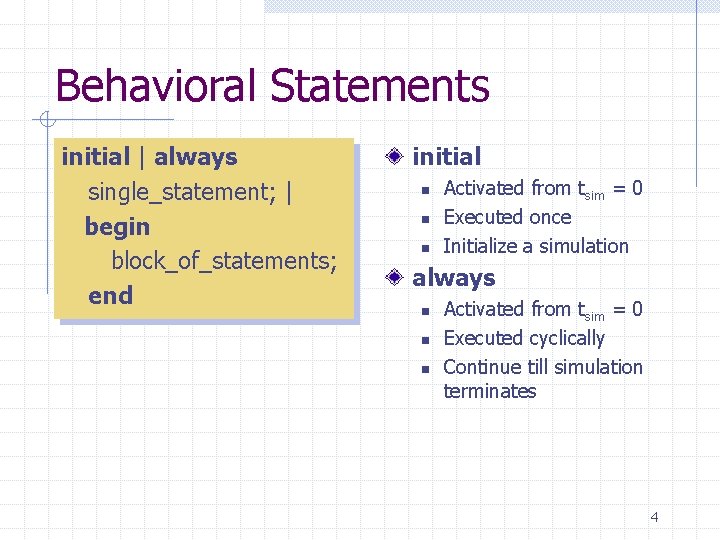

Behavioral Statements initial | always single_statement; | begin block_of_statements; end initial n n n Activated from tsim = 0 Executed once Initialize a simulation always n n n Activated from tsim = 0 Executed cyclically Continue till simulation terminates 4

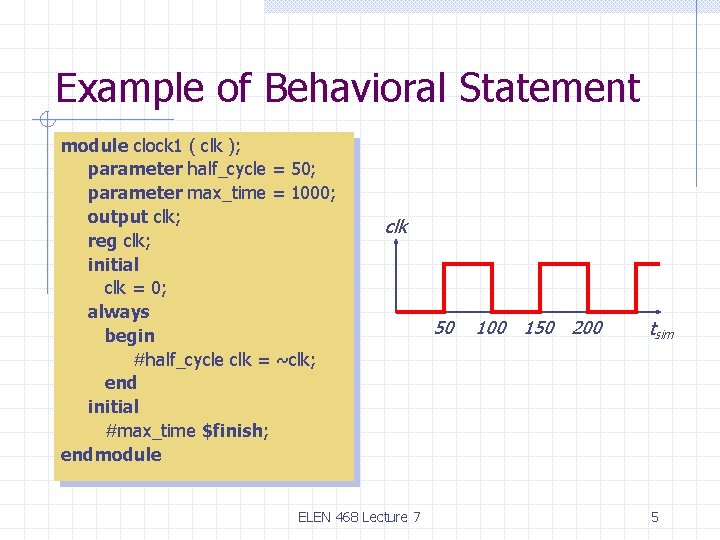

Example of Behavioral Statement module clock 1 ( clk ); parameter half_cycle = 50; parameter max_time = 1000; output clk; reg clk; initial clk = 0; always begin #half_cycle clk = ~clk; end initial #max_time $finish; endmodule clk ELEN 468 Lecture 7 50 100 150 200 tsim 5

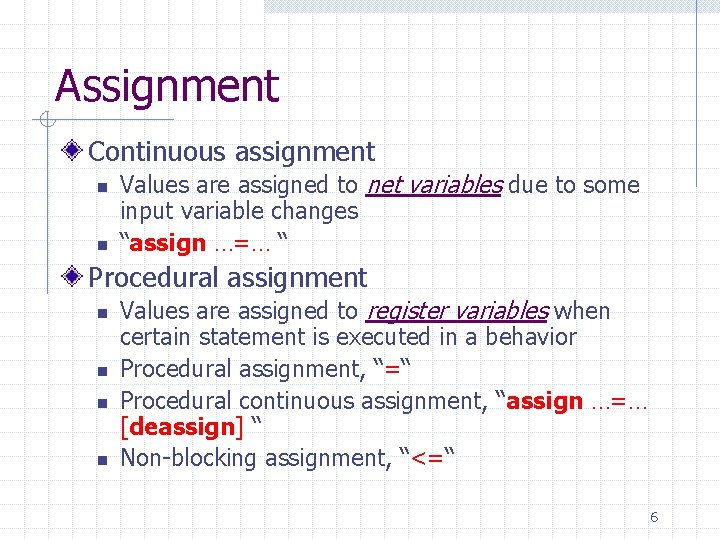

Assignment Continuous assignment n n Values are assigned to net variables due to some input variable changes “assign …=… “ Procedural assignment n n Values are assigned to register variables when certain statement is executed in a behavior Procedural assignment, “=“ Procedural continuous assignment, “assign …=… [deassign] “ Non-blocking assignment, “<=“ 6

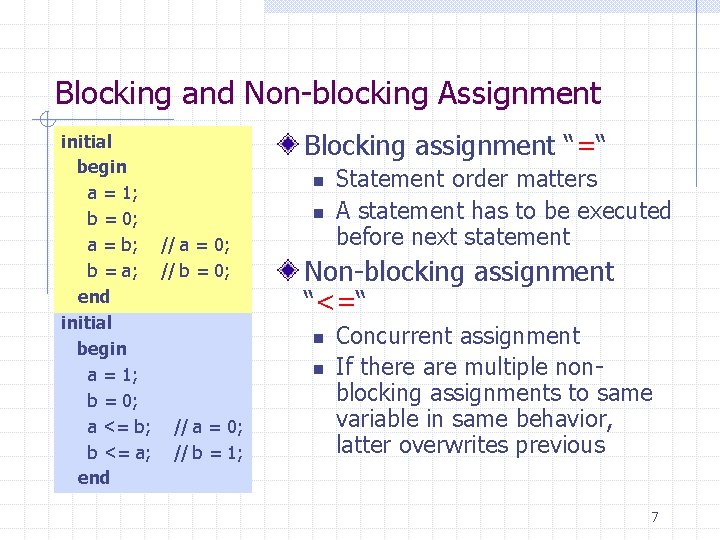

Blocking and Non-blocking Assignment initial begin a = 1; b = 0; a = b; // a = 0; b = a; // b = 0; end initial begin a = 1; b = 0; a <= b; // a = 0; b <= a; // b = 1; end Blocking assignment “=“ n n Statement order matters A statement has to be executed before next statement Non-blocking assignment “<=“ n n Concurrent assignment If there are multiple nonblocking assignments to same variable in same behavior, latter overwrites previous 7

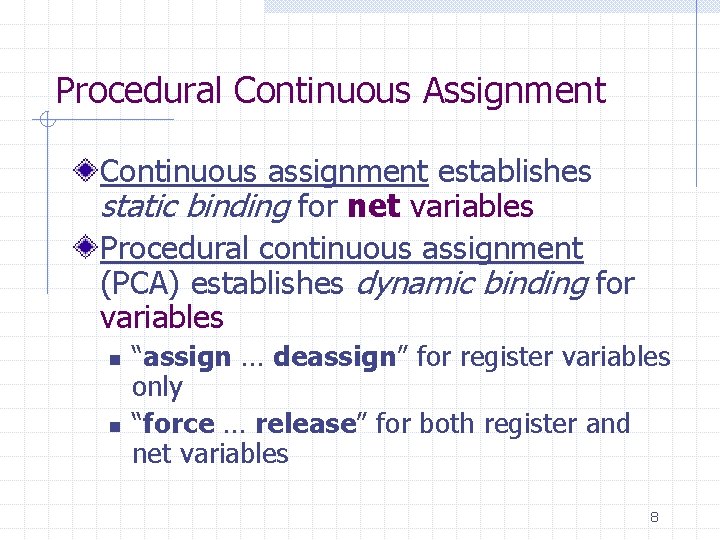

Procedural Continuous Assignment Continuous assignment establishes static binding for net variables Procedural continuous assignment (PCA) establishes dynamic binding for variables n n “assign … deassign” for register variables only “force … release” for both register and net variables 8

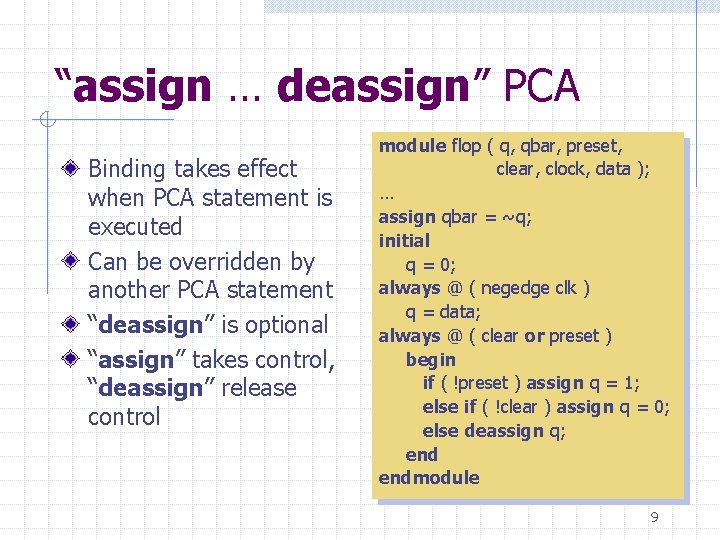

“assign … deassign” PCA Binding takes effect when PCA statement is executed Can be overridden by another PCA statement “deassign” is optional “assign” takes control, “deassign” release control module flop ( q, qbar, preset, clear, clock, data ); … assign qbar = ~q; initial q = 0; always @ ( negedge clk ) q = data; always @ ( clear or preset ) begin if ( !preset ) assign q = 1; else if ( !clear ) assign q = 0; else deassign q; endmodule 9

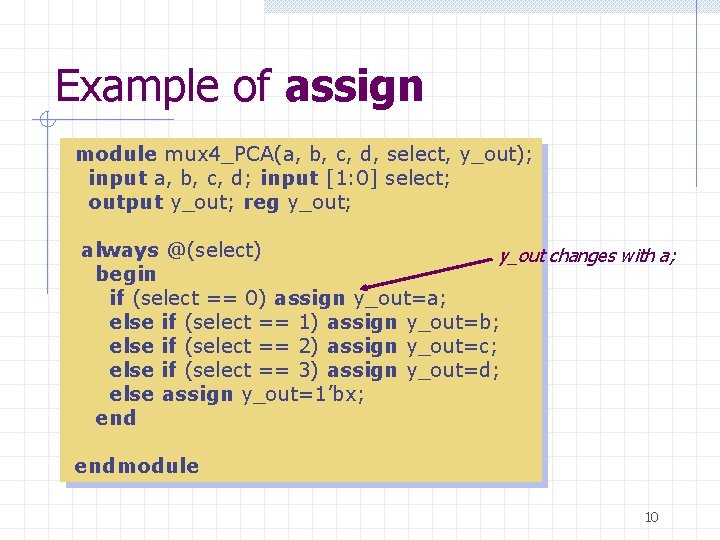

Example of assign module mux 4_PCA(a, b, c, d, select, y_out); input a, b, c, d; input [1: 0] select; output y_out; reg y_out; always @(select) y_out changes with a; begin if (select == 0) assign y_out=a; else if (select == 1) assign y_out=b; else if (select == 2) assign y_out=c; else if (select == 3) assign y_out=d; else assign y_out=1’bx; endmodule 10

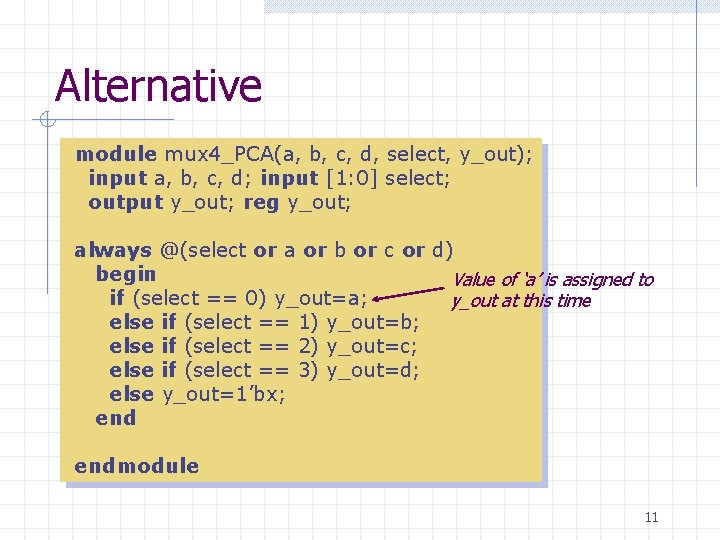

Alternative module mux 4_PCA(a, b, c, d, select, y_out); input a, b, c, d; input [1: 0] select; output y_out; reg y_out; always @(select or a or b or c or d) begin Value of ‘a’ is assigned to if (select == 0) y_out=a; y_out at this time else if (select == 1) y_out=b; else if (select == 2) y_out=c; else if (select == 3) y_out=d; else y_out=1’bx; endmodule 11

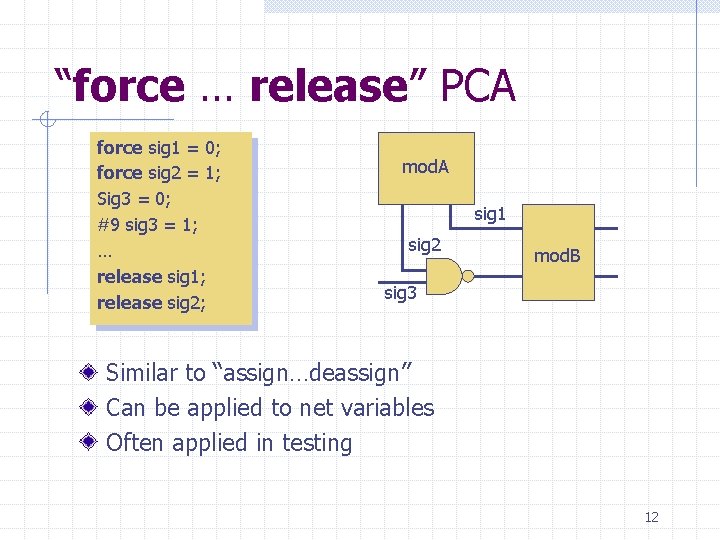

“force … release” PCA force sig 1 = 0; force sig 2 = 1; Sig 3 = 0; #9 sig 3 = 1; … release sig 1; release sig 2; mod. A sig 1 sig 2 mod. B sig 3 Similar to “assign…deassign” Can be applied to net variables Often applied in testing 12

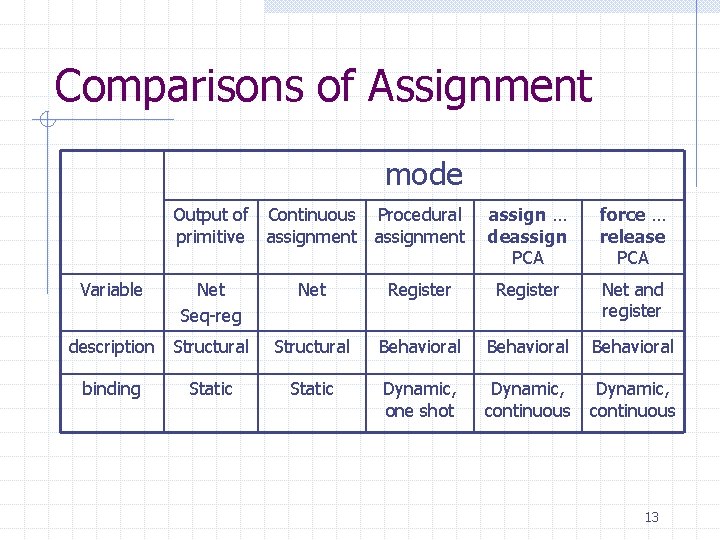

Comparisons of Assignment mode Output of Continuous Procedural primitive assignment Variable Net Seq-reg description Structural binding Static assign … deassign PCA force … release PCA Net Register Net and register Structural Behavioral Static Dynamic, one shot Dynamic, continuous 13

Behavioral Descriptions II 14

Procedural Timing Control Delay control Event control Named events “wait” construct 15

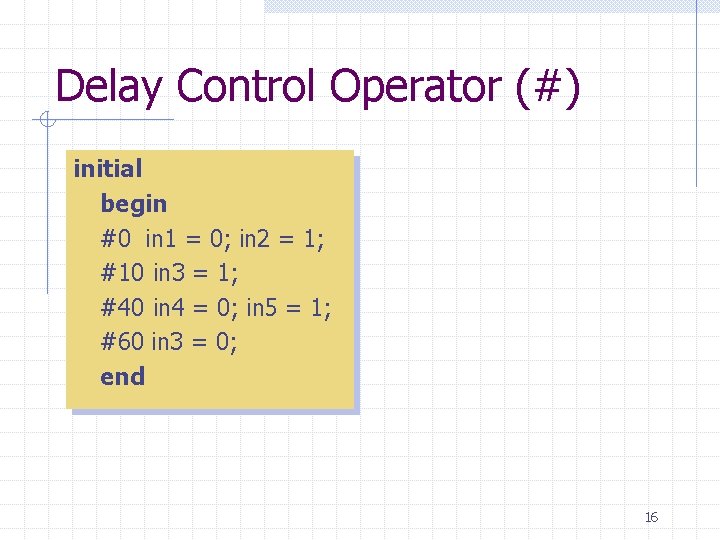

Delay Control Operator (#) initial begin #0 in 1 = 0; in 2 = 1; #10 in 3 = 1; #40 in 4 = 0; in 5 = 1; #60 in 3 = 0; end 16

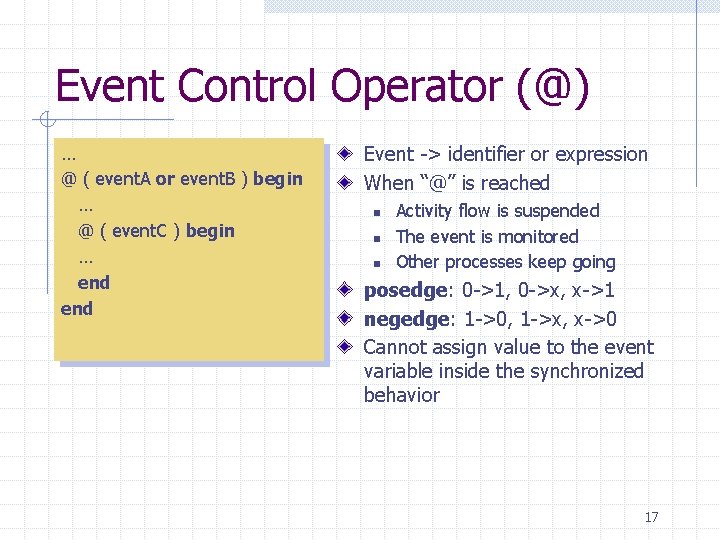

Event Control Operator (@) … @ ( event. A or event. B ) begin … @ ( event. C ) begin … end Event -> identifier or expression When “@” is reached n n n Activity flow is suspended The event is monitored Other processes keep going posedge: 0 ->1, 0 ->x, x->1 negedge: 1 ->0, 1 ->x, x->0 Cannot assign value to the event variable inside the synchronized behavior 17

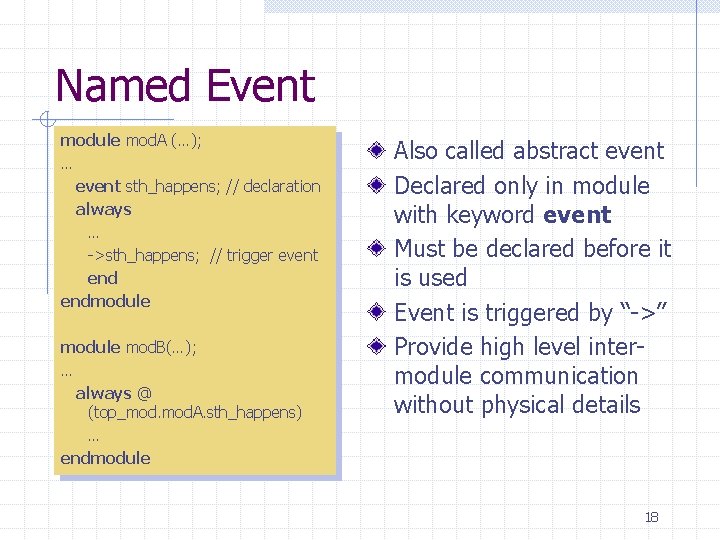

Named Event module mod. A (…); … event sth_happens; // declaration always … ->sth_happens; // trigger event endmodule mod. B(…); … always @ (top_mod. A. sth_happens) … endmodule Also called abstract event Declared only in module with keyword event Must be declared before it is used Event is triggered by “->” Provide high level intermodule communication without physical details 18

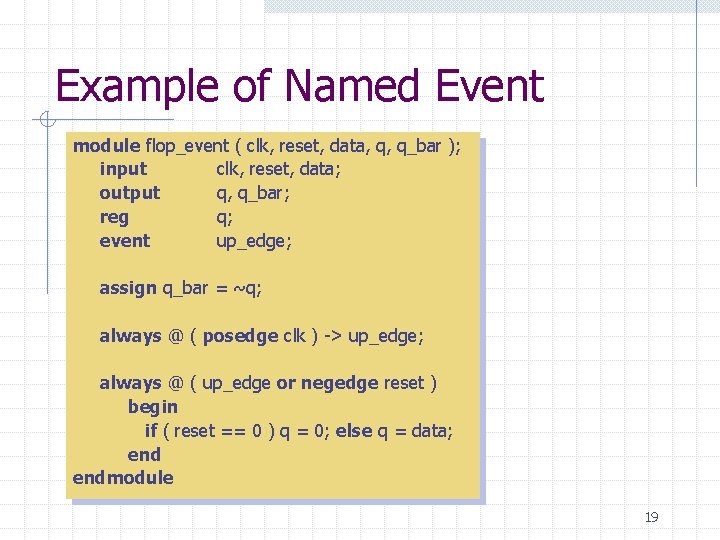

Example of Named Event module flop_event ( clk, reset, data, q, q_bar ); input clk, reset, data; output q, q_bar; reg q; event up_edge; assign q_bar = ~q; always @ ( posedge clk ) -> up_edge; always @ ( up_edge or negedge reset ) begin if ( reset == 0 ) q = 0; else q = data; endmodule 19

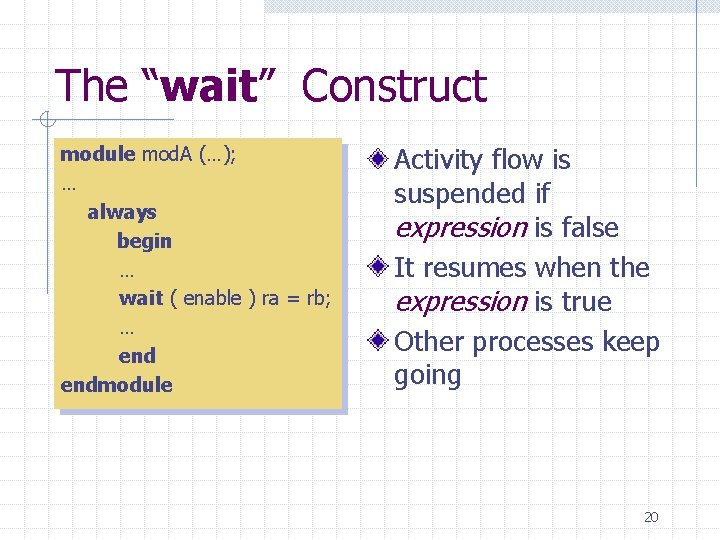

The “wait” Construct module mod. A (…); … always begin … wait ( enable ) ra = rb; … endmodule Activity flow is suspended if expression is false It resumes when the expression is true Other processes keep going 20

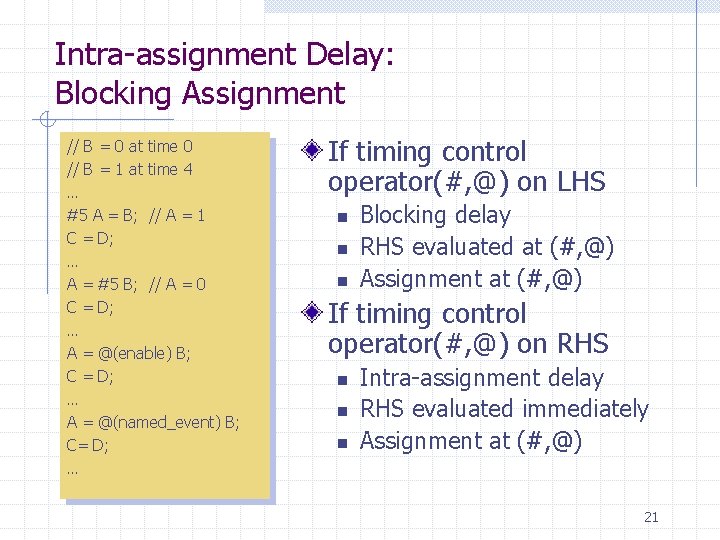

Intra-assignment Delay: Blocking Assignment // B = 0 at time 0 // B = 1 at time 4 … #5 A = B; // A = 1 C = D; … A = #5 B; // A = 0 C = D; … A = @(enable) B; C = D; … A = @(named_event) B; C= D; … If timing control operator(#, @) on LHS n n n Blocking delay RHS evaluated at (#, @) Assignment at (#, @) If timing control operator(#, @) on RHS n n n Intra-assignment delay RHS evaluated immediately Assignment at (#, @) 21

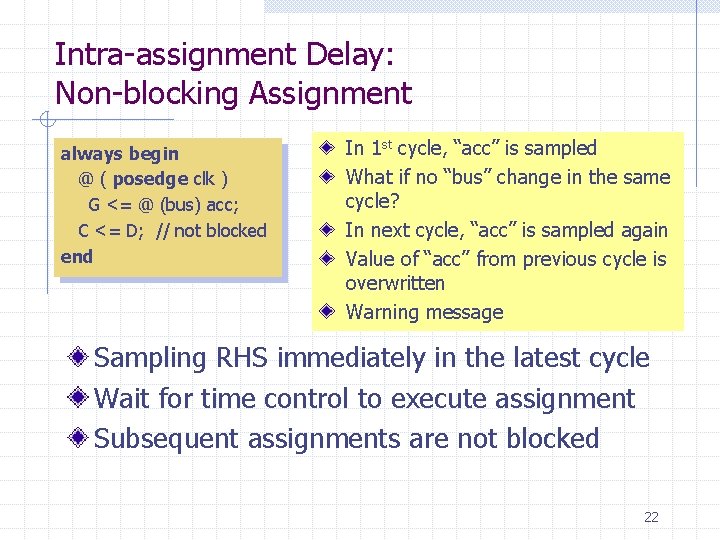

Intra-assignment Delay: Non-blocking Assignment always begin @ ( posedge clk ) G <= @ (bus) acc; C <= D; // not blocked end In 1 st cycle, “acc” is sampled What if no “bus” change in the same cycle? In next cycle, “acc” is sampled again Value of “acc” from previous cycle is overwritten Warning message Sampling RHS immediately in the latest cycle Wait for time control to execute assignment Subsequent assignments are not blocked 22

![Be Cautious module or 8( y, a, b ); input [7: 0] a, b; Be Cautious module or 8( y, a, b ); input [7: 0] a, b;](http://slidetodoc.com/presentation_image_h/30f6f219859917721811cc86a4a7b68a/image-23.jpg)

Be Cautious module or 8( y, a, b ); input [7: 0] a, b; output [7: 0] y; reg [7: 0] y; initial begin assign y = a | b; endmodule Model combinational logic by one-shot (initial) behavior Valid Not preferred Not accepted by synthesis tool 23

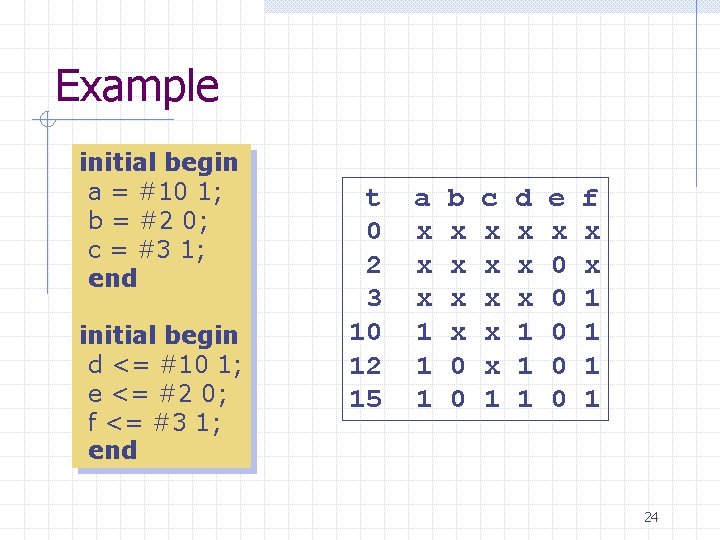

Example initial begin a = #10 1; b = #2 0; c = #3 1; end initial begin d <= #10 1; e <= #2 0; f <= #3 1; end t 0 2 3 10 12 15 a x x x 1 1 1 b x x 0 0 c x x x 1 d x x x 1 1 1 e x 0 0 0 f x x 1 1 24

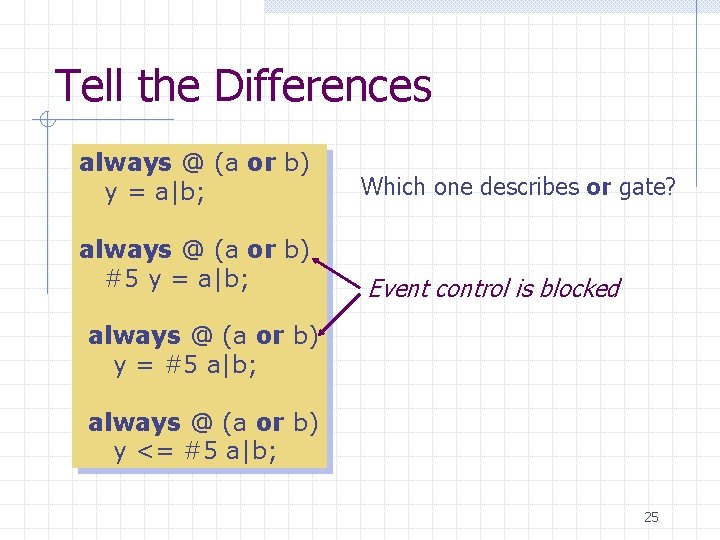

Tell the Differences always @ (a or b) y = a|b; Which one describes or gate? always @ (a or b) #5 y = a|b; Event control is blocked always @ (a or b) y = #5 a|b; always @ (a or b) y <= #5 a|b; 25

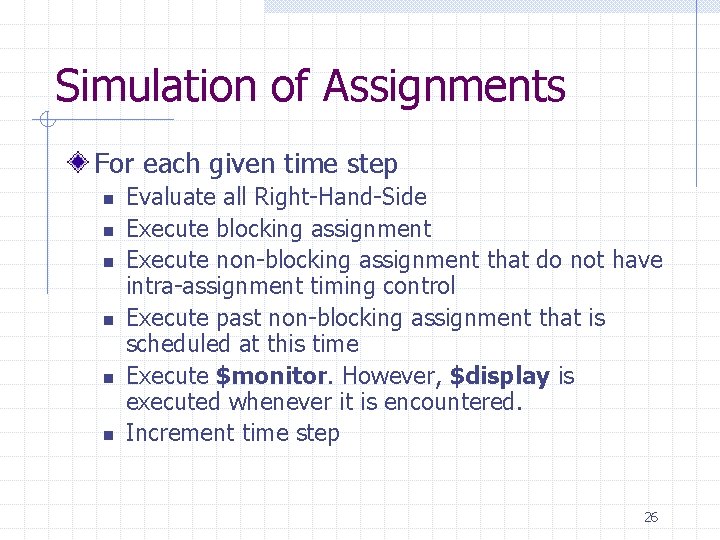

Simulation of Assignments For each given time step n n n Evaluate all Right-Hand-Side Execute blocking assignment Execute non-blocking assignment that do not have intra-assignment timing control Execute past non-blocking assignment that is scheduled at this time Execute $monitor. However, $display is executed whenever it is encountered. Increment time step 26

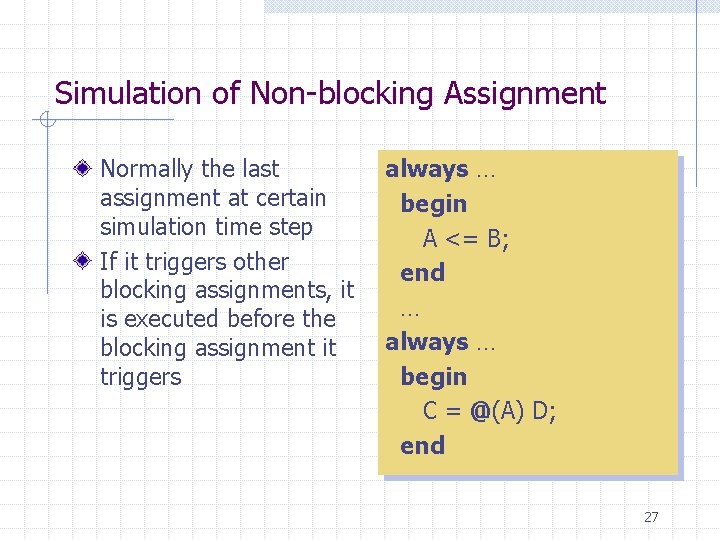

Simulation of Non-blocking Assignment Normally the last assignment at certain simulation time step If it triggers other blocking assignments, it is executed before the blocking assignment it triggers always … begin A <= B; end … always … begin C = @(A) D; end 27

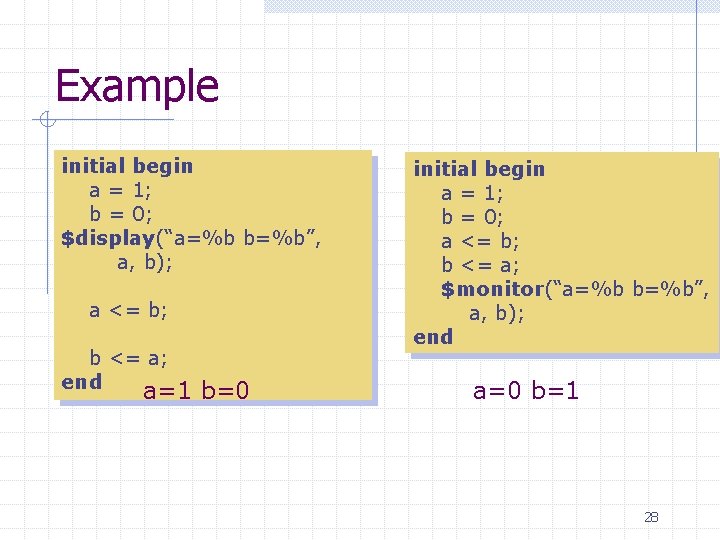

Example initial begin a = 1; b = 0; $display(“a=%b b=%b”, a, b); a <= b; b <= a; end a=1 b=0 initial begin a = 1; b = 0; a <= b; b <= a; $monitor(“a=%b b=%b”, a, b); end a=0 b=1 28

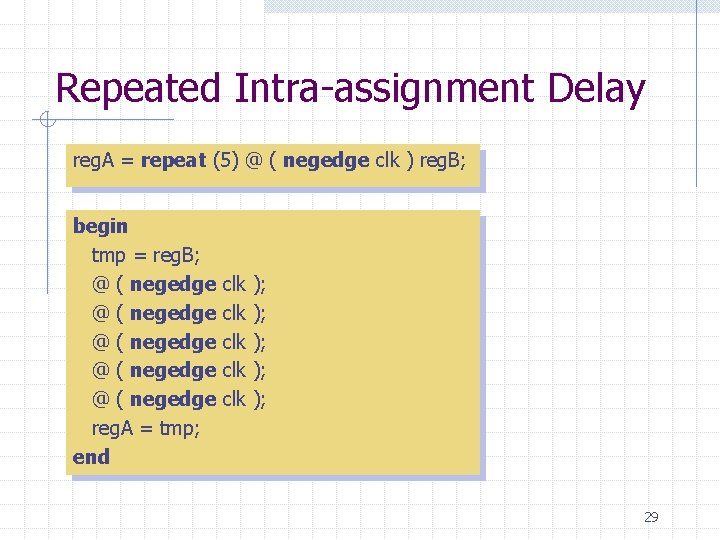

Repeated Intra-assignment Delay reg. A = repeat (5) @ ( negedge clk ) reg. B; begin tmp = reg. B; @ ( negedge @ ( negedge reg. A = tmp; end clk clk clk ); ); ); 29

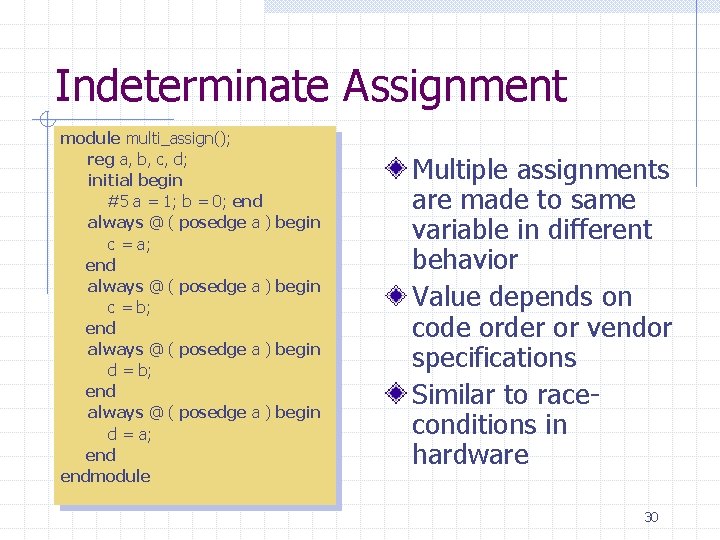

Indeterminate Assignment module multi_assign(); reg a, b, c, d; initial begin #5 a = 1; b = 0; end always @ ( posedge a ) c = a; end always @ ( posedge a ) c = b; end always @ ( posedge a ) d = a; endmodule begin Multiple assignments are made to same variable in different behavior Value depends on code order or vendor specifications Similar to raceconditions in hardware 30

Behavioral Descriptions III 31

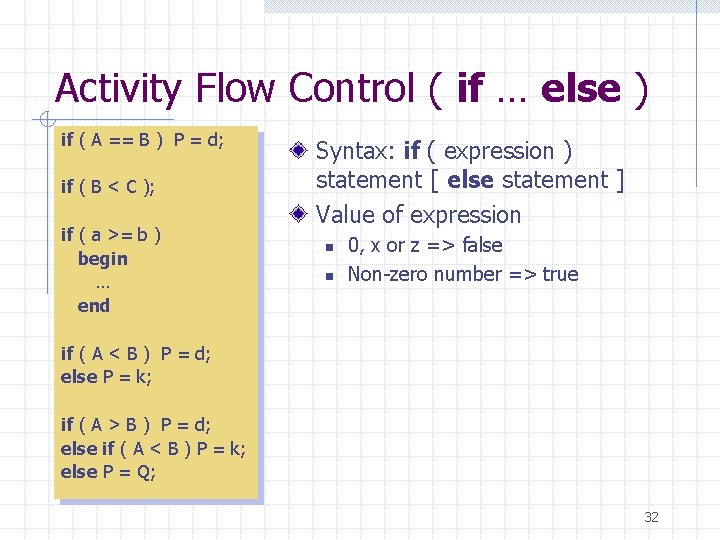

Activity Flow Control ( if … else ) if ( A == B ) P = d; if ( B < C ); if ( a >= b ) begin … end Syntax: if ( expression ) statement [ else statement ] Value of expression n n 0, x or z => false Non-zero number => true if ( A < B ) P = d; else P = k; if ( A > B ) P = d; else if ( A < B ) P = k; else P = Q; 32

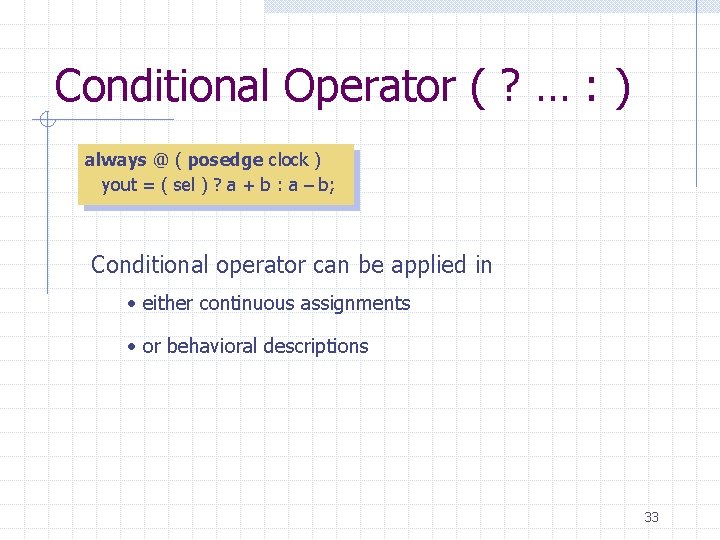

Conditional Operator ( ? … : ) always @ ( posedge clock ) yout = ( sel ) ? a + b : a – b; Conditional operator can be applied in • either continuous assignments • or behavioral descriptions 33

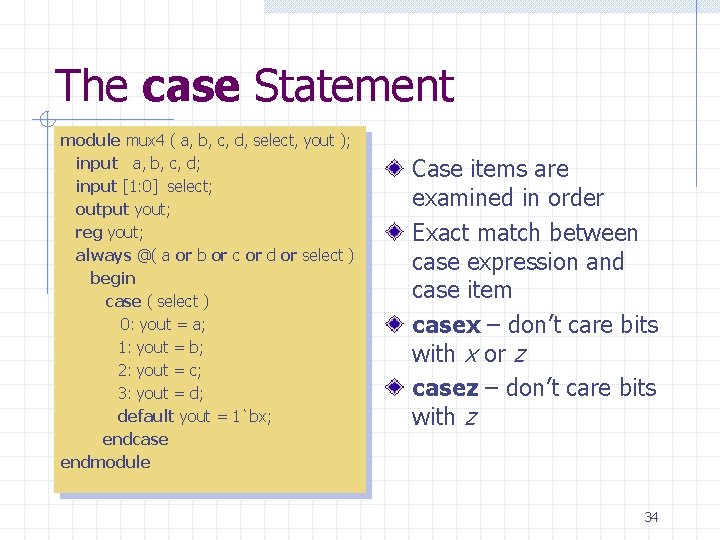

The case Statement module mux 4 ( a, b, c, d, select, yout ); input a, b, c, d; input [1: 0] select; output yout; reg yout; always @( a or b or c or d or select ) begin case ( select ) 0: yout = a; 1: yout = b; 2: yout = c; 3: yout = d; default yout = 1`bx; endcase endmodule Case items are examined in order Exact match between case expression and case item casex – don’t care bits with x or z casez – don’t care bits with z 34

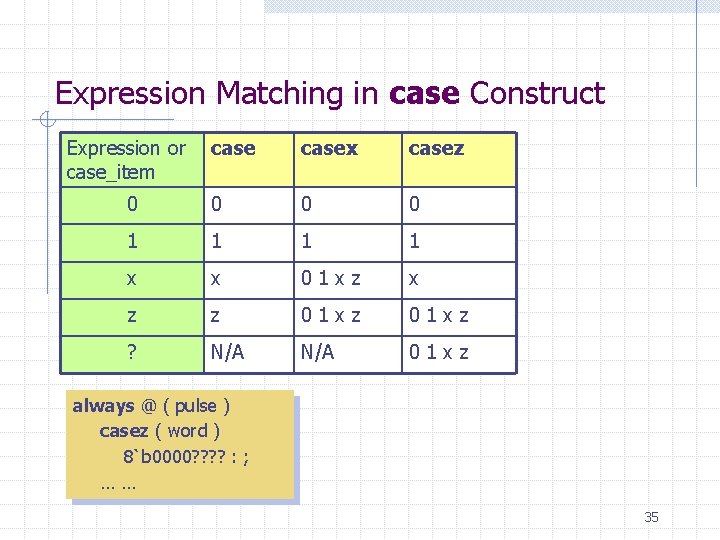

Expression Matching in case Construct Expression or case_item casex casez 0 0 1 1 x x 01 xz x z z 01 xz ? N/A 01 xz always @ ( pulse ) casez ( word ) 8`b 0000? ? : ; …… 35

Loops repeat for loop while loop forever disable 36

![The repeat Loop … word_address = 0; repeat ( memory_size ) begin memory [word_address] The repeat Loop … word_address = 0; repeat ( memory_size ) begin memory [word_address]](http://slidetodoc.com/presentation_image_h/30f6f219859917721811cc86a4a7b68a/image-37.jpg)

The repeat Loop … word_address = 0; repeat ( memory_size ) begin memory [word_address] = 0; word_address = word_address + 1; end … 37

![The for Loop reg [15: 0] reg. A; integer k; … for ( k The for Loop reg [15: 0] reg. A; integer k; … for ( k](http://slidetodoc.com/presentation_image_h/30f6f219859917721811cc86a4a7b68a/image-38.jpg)

The for Loop reg [15: 0] reg. A; integer k; … for ( k = 4; k; k = k – 1 ) begin reg. A [ k+10 ] = 0; reg. A [ k+2 ] = 1; end … Loop variables have to be either integer or reg 38

![The while Loop begin cnt 1 s reg [7: 0] tmp; cnt = 0; The while Loop begin cnt 1 s reg [7: 0] tmp; cnt = 0;](http://slidetodoc.com/presentation_image_h/30f6f219859917721811cc86a4a7b68a/image-39.jpg)

The while Loop begin cnt 1 s reg [7: 0] tmp; cnt = 0; tmp = reg. A; while ( tmp ) begin cnt = cnt + tmp[0]; tmp = tmp >> 1; end Loop activities suspend external activities module sth ( external. Sig ); input external. Sig; always begin while ( external. Sig ); endmodule Replacement for while ? 39

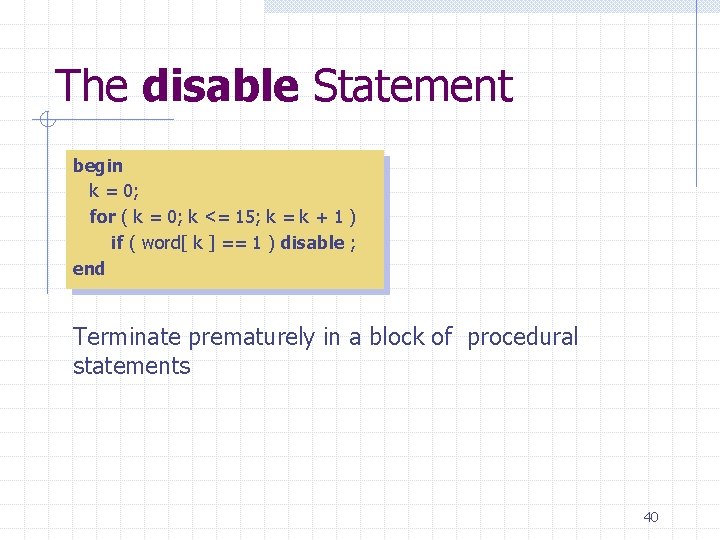

The disable Statement begin k = 0; for ( k = 0; k <= 15; k = k + 1 ) if ( word[ k ] == 1 ) disable ; end Terminate prematurely in a block of procedural statements 40

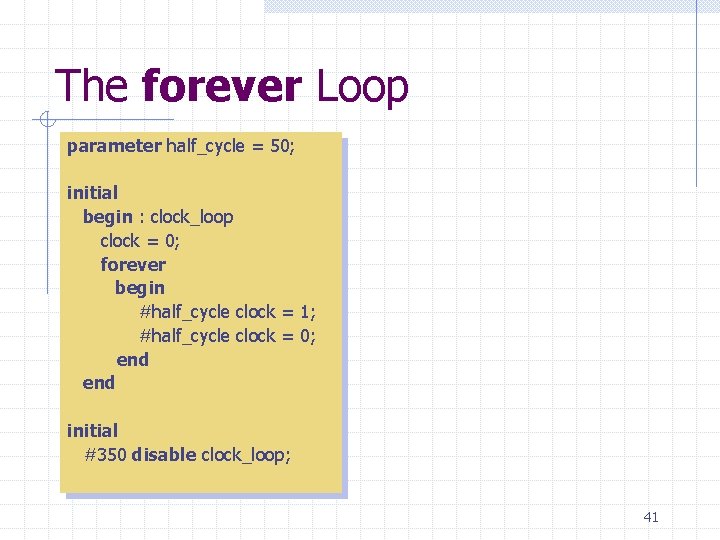

The forever Loop parameter half_cycle = 50; initial begin : clock_loop clock = 0; forever begin #half_cycle clock = 1; #half_cycle clock = 0; end initial #350 disable clock_loop; 41

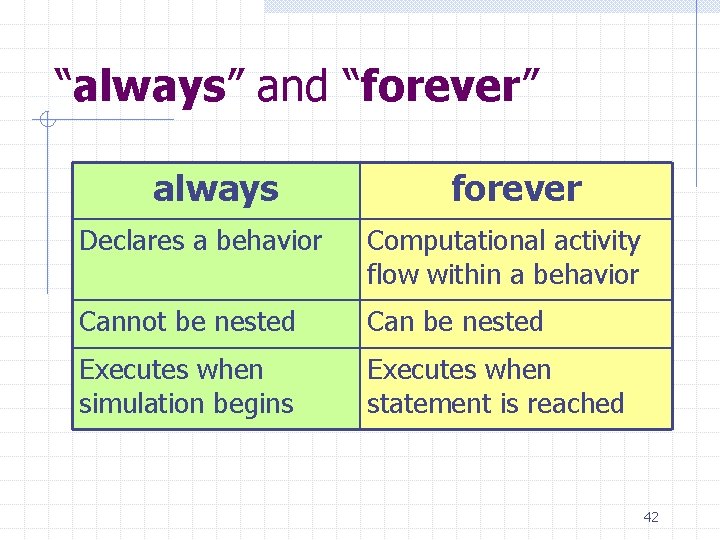

“always” and “forever” always forever Declares a behavior Computational activity flow within a behavior Cannot be nested Can be nested Executes when simulation begins Executes when statement is reached 42

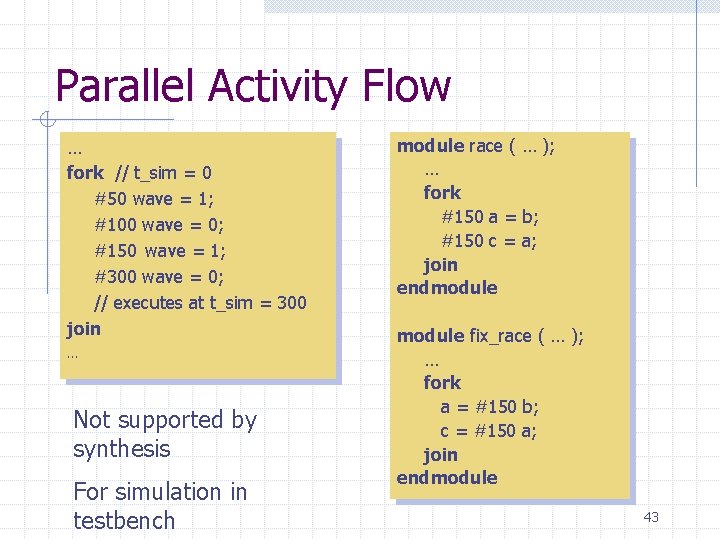

Parallel Activity Flow … fork // t_sim = 0 #50 wave = 1; #100 wave = 0; #150 wave = 1; #300 wave = 0; // executes at t_sim = 300 join … Not supported by synthesis For simulation in testbench module race ( … ); … fork #150 a = b; #150 c = a; join endmodule fix_race ( … ); … fork a = #150 b; c = #150 a; join endmodule 43

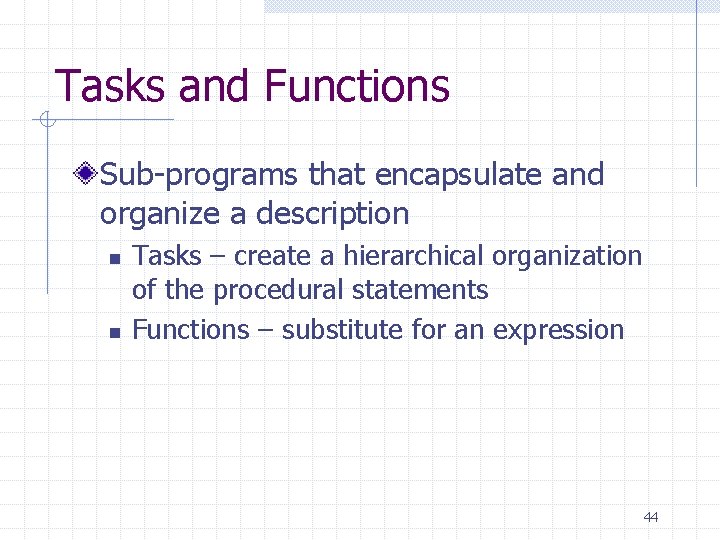

Tasks and Functions Sub-programs that encapsulate and organize a description n n Tasks – create a hierarchical organization of the procedural statements Functions – substitute for an expression 44

Tasks Declared within a module Referenced in a behavior n n In module where the task is declared From any module through hierarchical de-referencing All arguments to the task are passed by value, not pointer Parameters can be passed to a task, variables and parameters within the parent module of a task are visible to the task A task may not be used within an expression Statements in a task may contain delay and event control A task can call itself 45

![Example of Task module bit_counter (data, count); input [7: 0] data; output [3: 0] Example of Task module bit_counter (data, count); input [7: 0] data; output [3: 0]](http://slidetodoc.com/presentation_image_h/30f6f219859917721811cc86a4a7b68a/image-46.jpg)

Example of Task module bit_counter (data, count); input [7: 0] data; output [3: 0] count; reg [3: 0] count; always @(data) t(data, count); task t; input [7: 0] a; output [3: 0] c; reg [7: 0] tmp; begin c = 0; tmp = a; while (tmp) begin c = c + tmp[0]; tmp = tmp >> 1; end endtask endmodule ELEN 468 Lecture 9 46

Functions Implement only combinational behavior Compute and return a value for given parameters Have no timing/event control May call other functions, not itself Can be referenced anywhere an expression can exist May not declare any output or inout port Must have at least one input port ELEN 468 Lecture 9 47

![Example of Function module word_aligner (w_in, w_out); input [7: 0] w_in; output [7: 0] Example of Function module word_aligner (w_in, w_out); input [7: 0] w_in; output [7: 0]](http://slidetodoc.com/presentation_image_h/30f6f219859917721811cc86a4a7b68a/image-48.jpg)

Example of Function module word_aligner (w_in, w_out); input [7: 0] w_in; output [7: 0] w_out; assign w_out = align (w_in); function [7: 0] align; input [7: 0] word; begin align = word; if (align != 0) ELEN 468== Lecture 9 while (align[7] 48

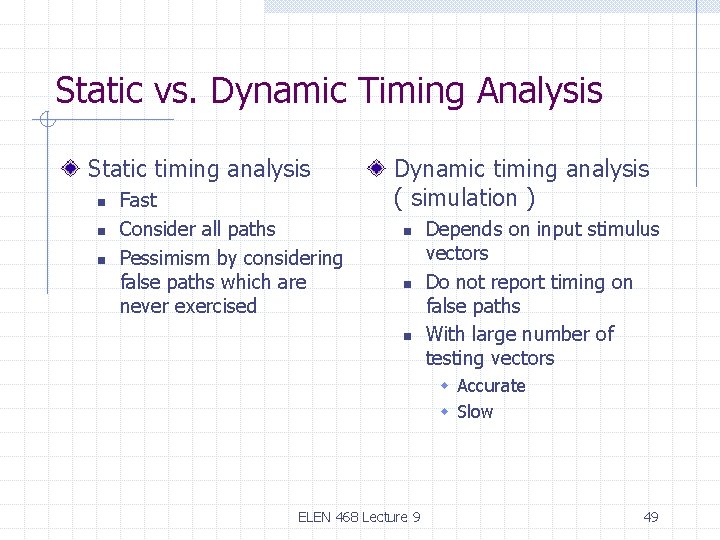

Static vs. Dynamic Timing Analysis Static timing analysis n n n Fast Consider all paths Pessimism by considering false paths which are never exercised Dynamic timing analysis ( simulation ) n n n Depends on input stimulus vectors Do not report timing on false paths With large number of testing vectors w Accurate w Slow ELEN 468 Lecture 9 49

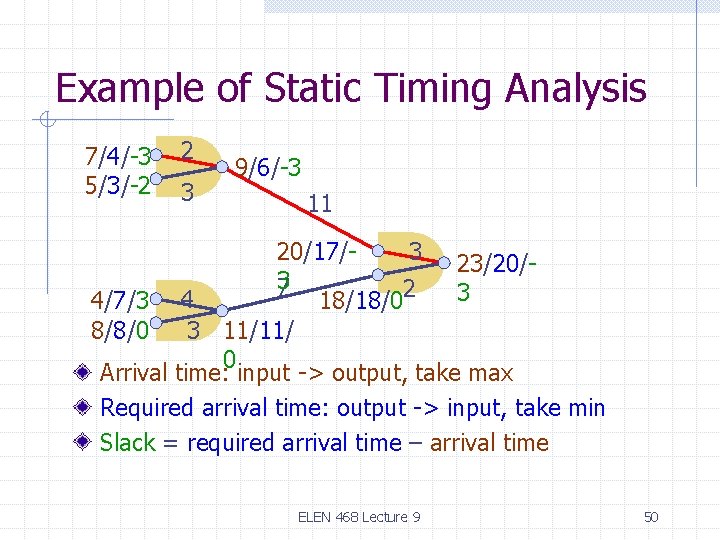

Example of Static Timing Analysis 7/4/-3 5/3/-2 2 3 9/6/-3 11 20/17/3 23/20/3 7 3 4/7/3 4 18/18/02 8/8/0 3 11/11/ 0 Arrival time: input -> output, take max Required arrival time: output -> input, take min Slack = required arrival time – arrival time ELEN 468 Lecture 9 50

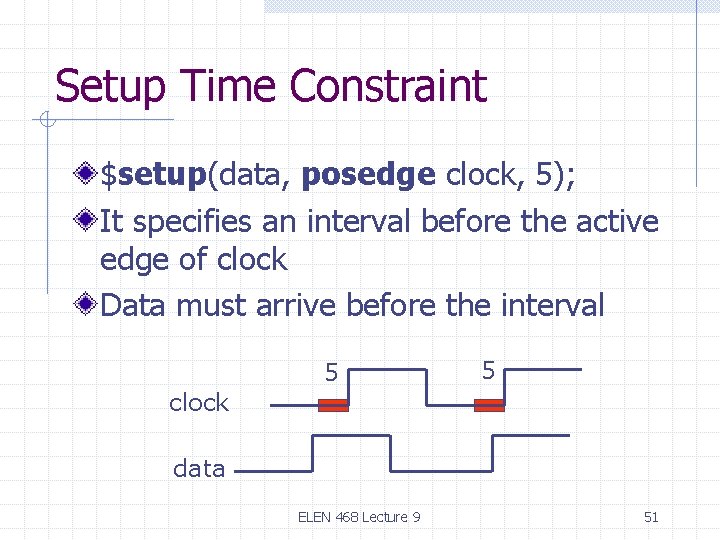

Setup Time Constraint $setup(data, posedge clock, 5); It specifies an interval before the active edge of clock Data must arrive before the interval 5 5 clock data ELEN 468 Lecture 9 51

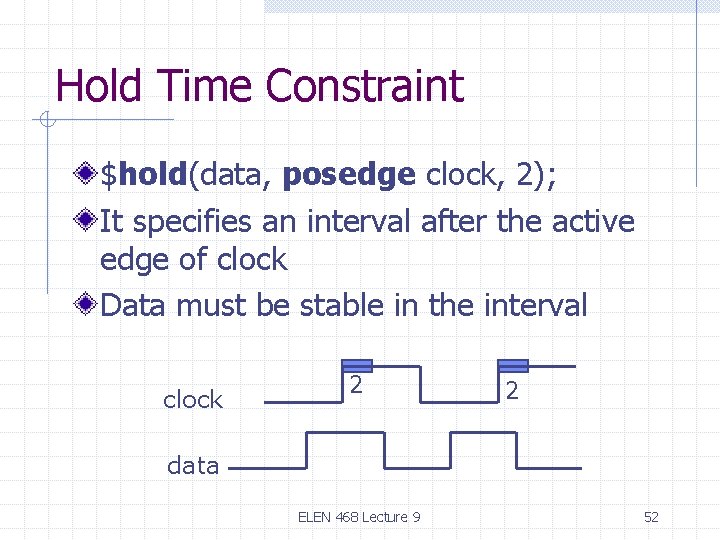

Hold Time Constraint $hold(data, posedge clock, 2); It specifies an interval after the active edge of clock Data must be stable in the interval clock 2 2 data ELEN 468 Lecture 9 52

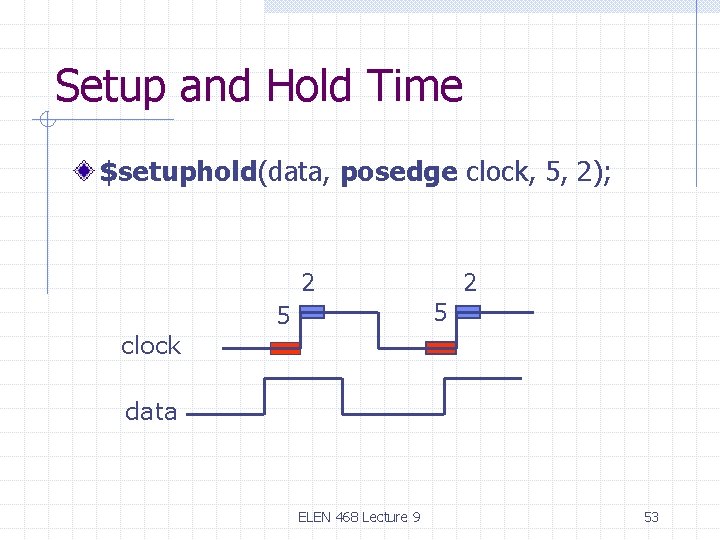

Setup and Hold Time $setuphold(data, posedge clock, 5, 2); 2 2 5 5 clock data ELEN 468 Lecture 9 53

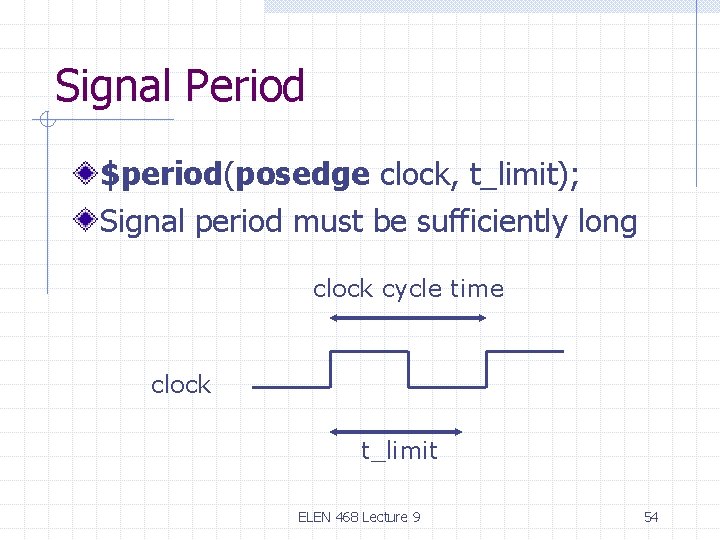

Signal Period $period(posedge clock, t_limit); Signal period must be sufficiently long clock cycle time clock t_limit ELEN 468 Lecture 9 54

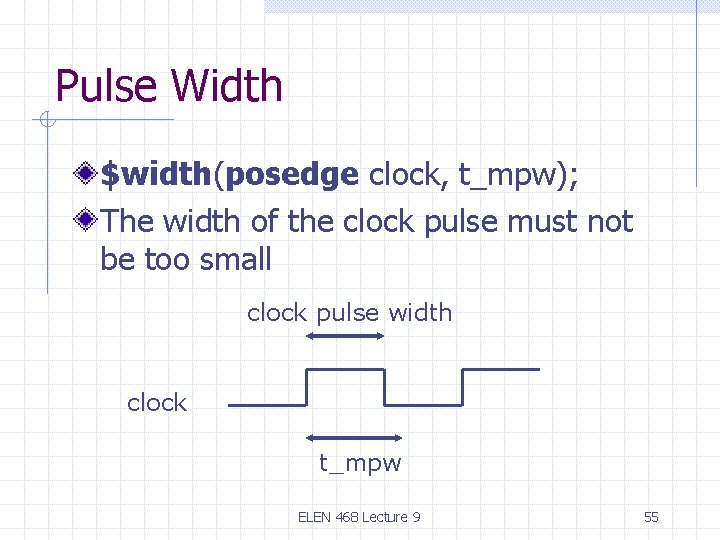

Pulse Width $width(posedge clock, t_mpw); The width of the clock pulse must not be too small clock pulse width clock t_mpw ELEN 468 Lecture 9 55

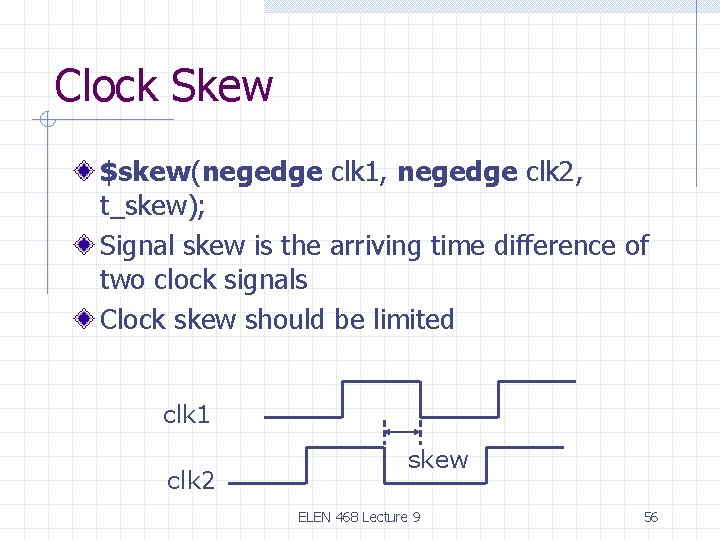

Clock Skew $skew(negedge clk 1, negedge clk 2, t_skew); Signal skew is the arriving time difference of two clock signals Clock skew should be limited clk 1 clk 2 skew ELEN 468 Lecture 9 56

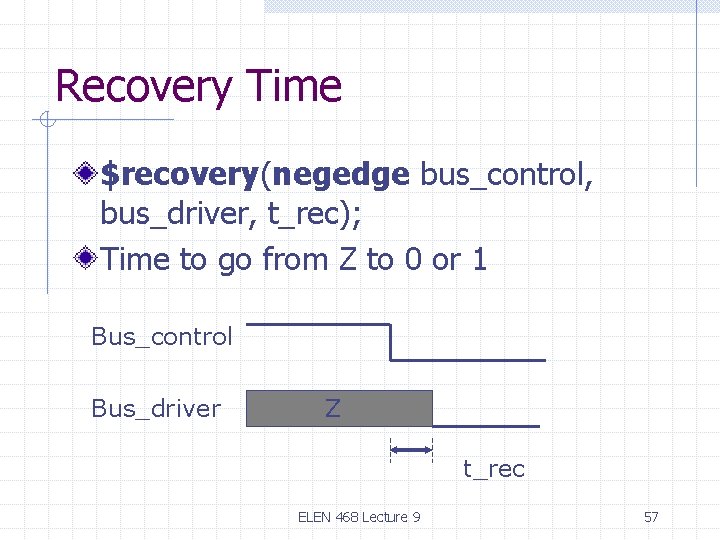

Recovery Time $recovery(negedge bus_control, bus_driver, t_rec); Time to go from Z to 0 or 1 Bus_control Bus_driver Z t_rec ELEN 468 Lecture 9 57

No Signal Change $nochange(posedge clk, data, -5, 2); Equivalent to n $setuphold(data, posedge clk, 5, 2); ELEN 468 Lecture 9 58

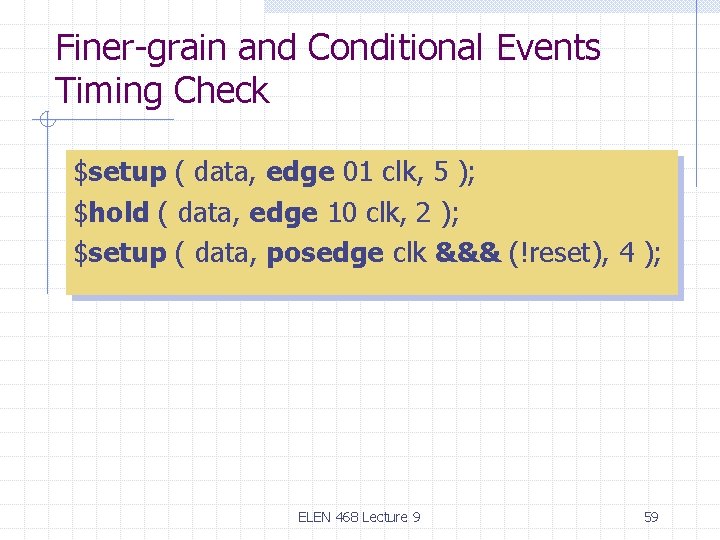

Finer-grain and Conditional Events Timing Check $setup ( data, edge 01 clk, 5 ); $hold ( data, edge 10 clk, 2 ); $setup ( data, posedge clk &&& (!reset), 4 ); ELEN 468 Lecture 9 59

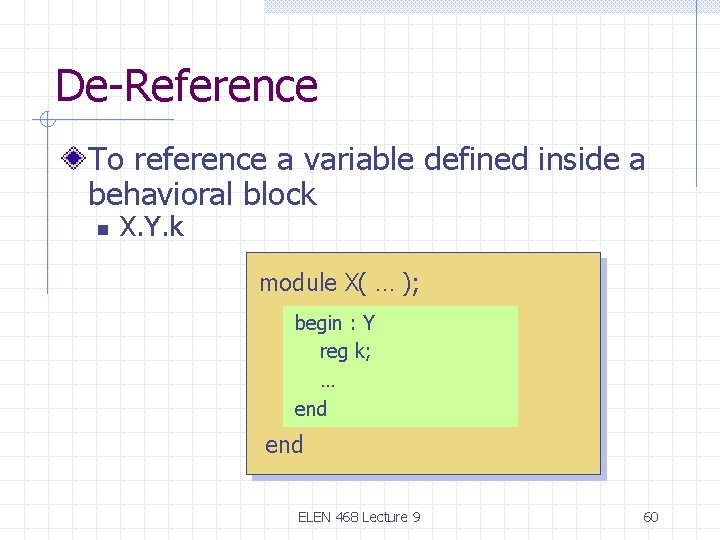

De-Reference To reference a variable defined inside a behavioral block n X. Y. k module X( … ); begin : Y reg k; … end ELEN 468 Lecture 9 60

ELEN 468 Advanced Logic Design Lecture 10 Behavioral Descriptions IV ELEN 468 Lecture 10 61

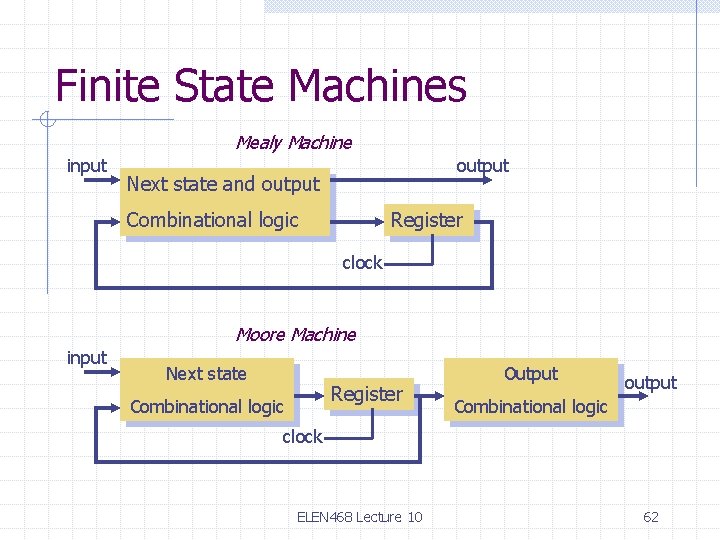

Finite State Machines Mealy Machine input output Next state and output Register Combinational logic clock Moore Machine input Next state Register Combinational logic Output output Combinational logic clock ELEN 468 Lecture 10 62

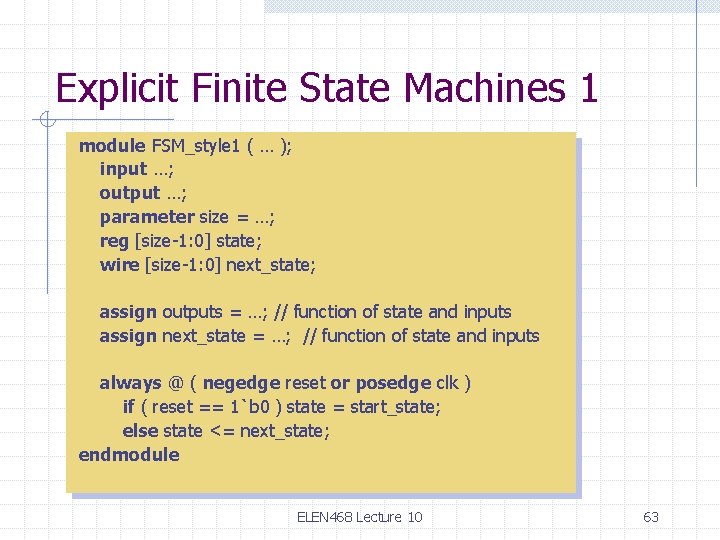

Explicit Finite State Machines 1 module FSM_style 1 ( … ); input …; output …; parameter size = …; reg [size-1: 0] state; wire [size-1: 0] next_state; assign outputs = …; // function of state and inputs assign next_state = …; // function of state and inputs always @ ( negedge reset or posedge clk ) if ( reset == 1`b 0 ) state = start_state; else state <= next_state; endmodule ELEN 468 Lecture 10 63

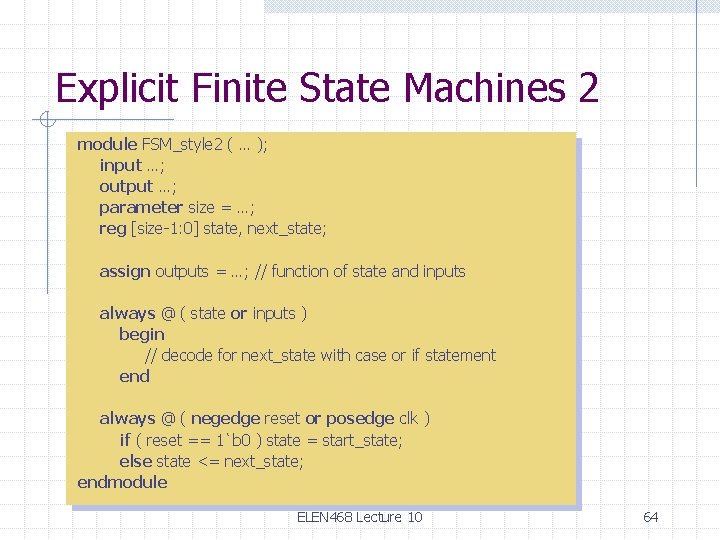

Explicit Finite State Machines 2 module FSM_style 2 ( … ); input …; output …; parameter size = …; reg [size-1: 0] state, next_state; assign outputs = …; // function of state and inputs always @ ( state or inputs ) begin // decode for next_state with case or if statement end always @ ( negedge reset or posedge clk ) if ( reset == 1`b 0 ) state = start_state; else state <= next_state; endmodule ELEN 468 Lecture 10 64

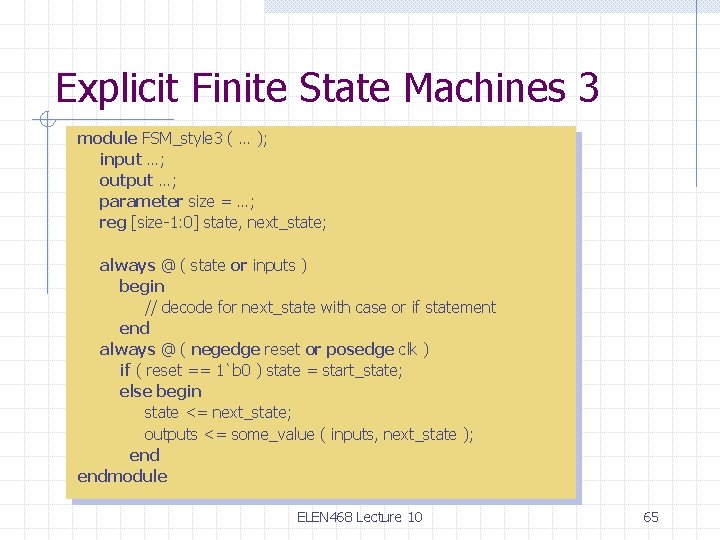

Explicit Finite State Machines 3 module FSM_style 3 ( … ); input …; output …; parameter size = …; reg [size-1: 0] state, next_state; always @ ( state or inputs ) begin // decode for next_state with case or if statement end always @ ( negedge reset or posedge clk ) if ( reset == 1`b 0 ) state = start_state; else begin state <= next_state; outputs <= some_value ( inputs, next_state ); endmodule ELEN 468 Lecture 10 65

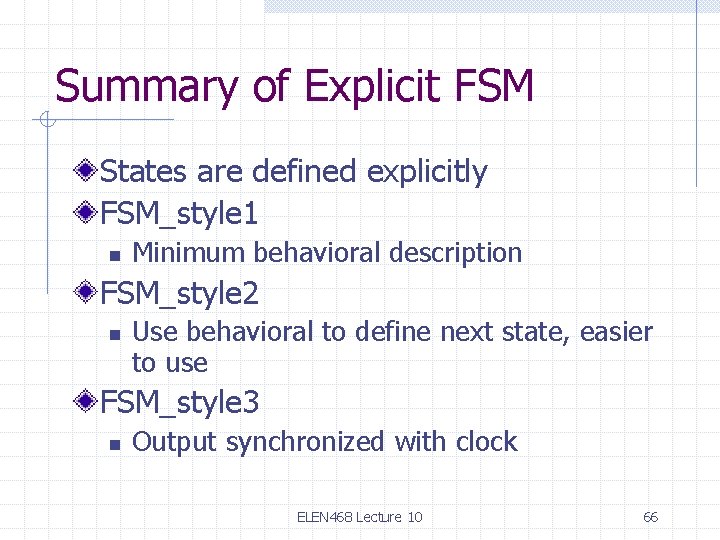

Summary of Explicit FSM States are defined explicitly FSM_style 1 n Minimum behavioral description FSM_style 2 n Use behavioral to define next state, easier to use FSM_style 3 n Output synchronized with clock ELEN 468 Lecture 10 66

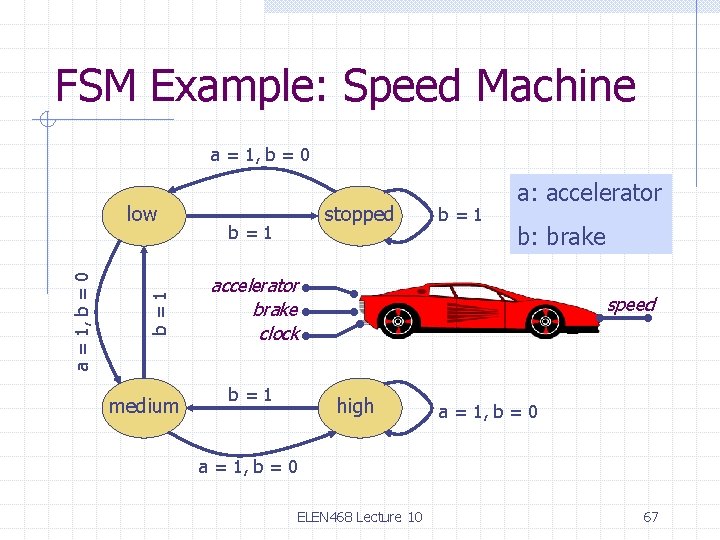

FSM Example: Speed Machine a = 1, b = 0 b=1 a = 1, b = 0 low medium stopped b=1 a: accelerator b: brake accelerator brake clock b=1 speed high a = 1, b = 0 ELEN 468 Lecture 10 67

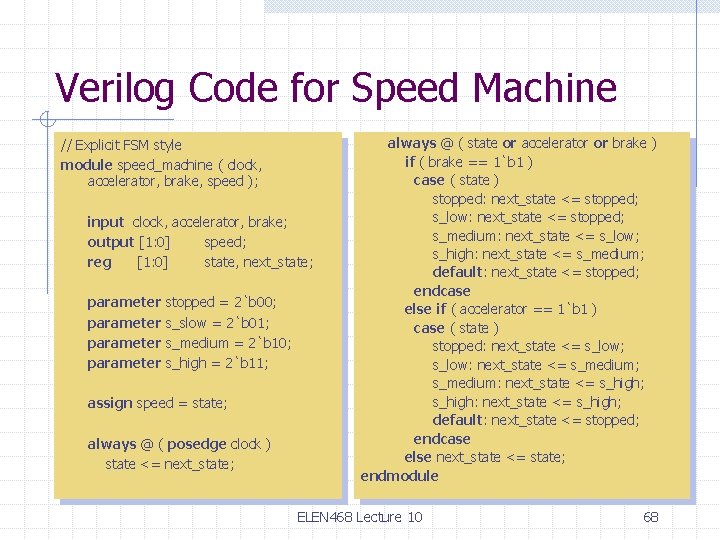

Verilog Code for Speed Machine // Explicit FSM style module speed_machine ( clock, accelerator, brake, speed ); input clock, accelerator, brake; output [1: 0] speed; reg [1: 0] state, next_state; parameter stopped = 2`b 00; s_slow = 2`b 01; s_medium = 2`b 10; s_high = 2`b 11; assign speed = state; always @ ( posedge clock ) state <= next_state; always @ ( state or accelerator or brake ) if ( brake == 1`b 1 ) case ( state ) stopped: next_state <= stopped; s_low: next_state <= stopped; s_medium: next_state <= s_low; s_high: next_state <= s_medium; default: next_state <= stopped; endcase else if ( accelerator == 1`b 1 ) case ( state ) stopped: next_state <= s_low; s_low: next_state <= s_medium; s_medium: next_state <= s_high; s_high: next_state <= s_high; default: next_state <= stopped; endcase else next_state <= state; endmodule ELEN 468 Lecture 10 68

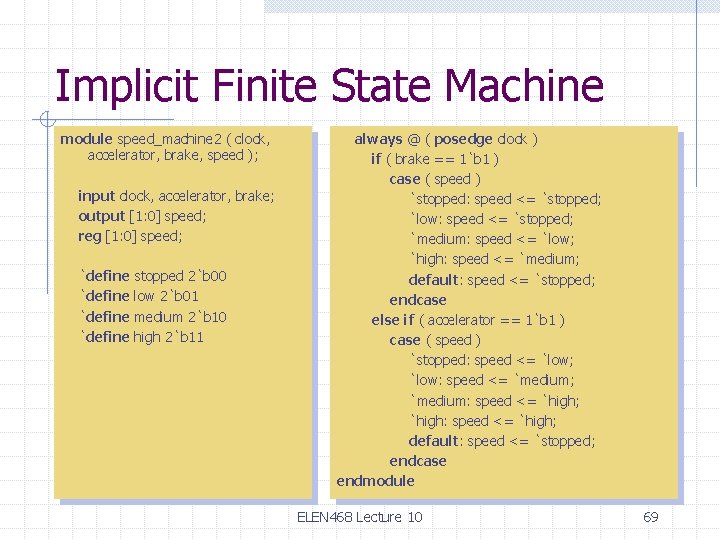

Implicit Finite State Machine module speed_machine 2 ( clock, accelerator, brake, speed ); input clock, accelerator, brake; output [1: 0] speed; reg [1: 0] speed; `define stopped 2`b 00 `define low 2`b 01 `define medium 2`b 10 `define high 2`b 11 always @ ( posedge clock ) if ( brake == 1`b 1 ) case ( speed ) `stopped: speed <= `stopped; `low: speed <= `stopped; `medium: speed <= `low; `high: speed <= `medium; default: speed <= `stopped; endcase else if ( accelerator == 1`b 1 ) case ( speed ) `stopped: speed <= `low; `low: speed <= `medium; `medium: speed <= `high; `high: speed <= `high; default: speed <= `stopped; endcase endmodule ELEN 468 Lecture 10 69

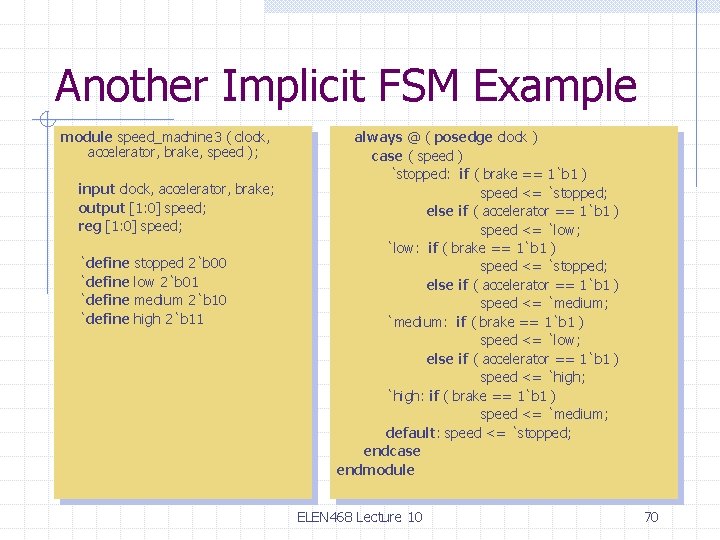

Another Implicit FSM Example module speed_machine 3 ( clock, accelerator, brake, speed ); input clock, accelerator, brake; output [1: 0] speed; reg [1: 0] speed; `define stopped 2`b 00 `define low 2`b 01 `define medium 2`b 10 `define high 2`b 11 always @ ( posedge clock ) case ( speed ) `stopped: if ( brake == 1`b 1 ) speed <= `stopped; else if ( accelerator == 1`b 1 ) speed <= `low; `low: if ( brake == 1`b 1 ) speed <= `stopped; else if ( accelerator == 1`b 1 ) speed <= `medium; `medium: if ( brake == 1`b 1 ) speed <= `low; else if ( accelerator == 1`b 1 ) speed <= `high; `high: if ( brake == 1`b 1 ) speed <= `medium; default: speed <= `stopped; endcase endmodule ELEN 468 Lecture 10 70

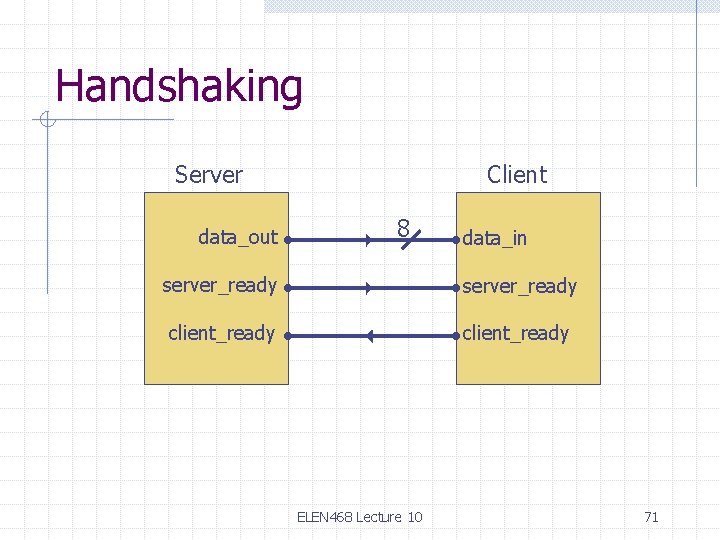

Handshaking Server data_out Client 8 data_in server_ready client_ready ELEN 468 Lecture 10 71

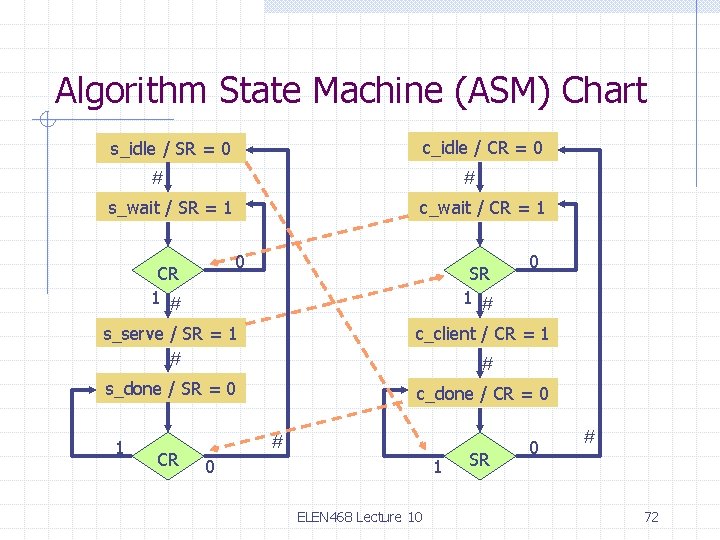

Algorithm State Machine (ASM) Chart c_idle / CR = 0 s_idle / SR = 0 # # s_wait / SR = 1 c_wait / CR = 1 0 CR 1 # SR 1 # 0 s_serve / SR = 1 # c_client / CR = 1 s_done / SR = 0 c_done / CR = 0 1 CR # # 0 1 ELEN 468 Lecture 10 SR 0 # 72

![Verilog Code for Handshaking module server ( d_out, s_ready, c_ready ); output [3: 0] Verilog Code for Handshaking module server ( d_out, s_ready, c_ready ); output [3: 0]](http://slidetodoc.com/presentation_image_h/30f6f219859917721811cc86a4a7b68a/image-73.jpg)

Verilog Code for Handshaking module server ( d_out, s_ready, c_ready ); output [3: 0] d_out; output s_ready; input c_ready; reg s_ready; reg [3: 0] d_out; task pause; reg [3: 0] delay; begin delay = $random; if ( delay == 0 ) delay = 1; #delay; endtask always forever begin s_ready = 0; pause; s_ready = 1; wait ( c_ready ) pause; d_out = $random; pause; s_ready = 0; wait ( !c_ready ) pause; endmodule client ( d_in, s_ready, c_ready ); input [3: 0] d_in; input s_ready; output c_ready; reg [3: 0] data_reg; task pause; reg [3: 0] delay; begin delay = $random; if ( delay == 0 ) delay = 1; #delay; endtask always begin c_ready = 0; pause; c_ready = 1; forever begin wait ( s_ready ) pause; data_reg = d_in; pause; c_ready = 0; wait ( !s_ready ) pause; c_ready = 1; end endmodule ELEN 468 Lecture 10 73

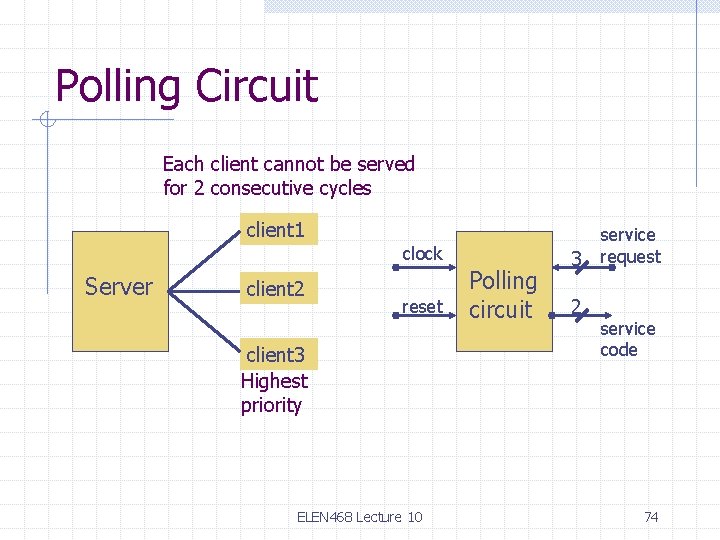

Polling Circuit Each client cannot be served for 2 consecutive cycles client 1 clock Server client 2 reset client 3 Highest priority ELEN 468 Lecture 10 Polling circuit 3 2 service request service code 74

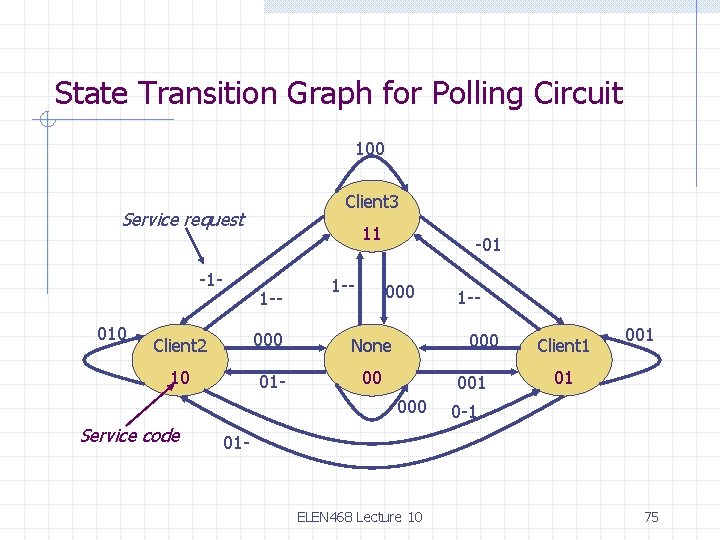

State Transition Graph for Polling Circuit 100 Client 3 Service request -1010 11 1 -- -01 000 Client 2 000 None 10 01 - 00 001 000 Service code 1 -Client 1 001 01 0 -1 01 - ELEN 468 Lecture 10 75

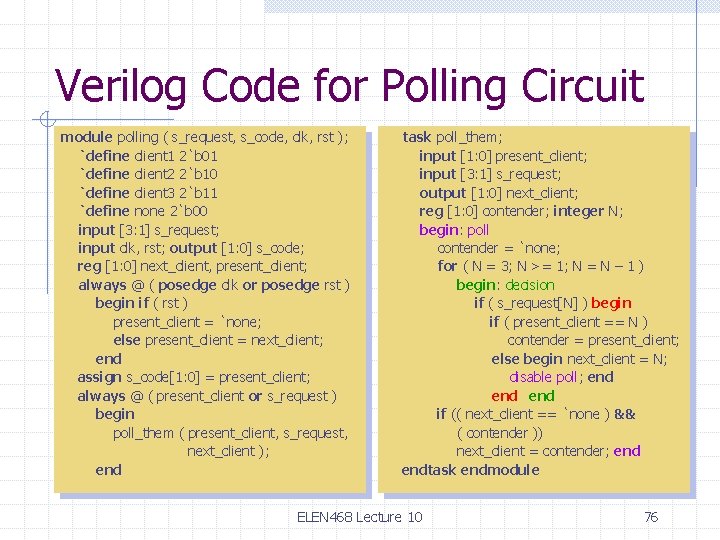

Verilog Code for Polling Circuit module polling ( s_request, s_code, clk, rst ); `define client 1 2`b 01 `define client 2 2`b 10 `define client 3 2`b 11 `define none 2`b 00 input [3: 1] s_request; input clk, rst; output [1: 0] s_code; reg [1: 0] next_client, present_client; always @ ( posedge clk or posedge rst ) begin if ( rst ) present_client = `none; else present_client = next_client; end assign s_code[1: 0] = present_client; always @ ( present_client or s_request ) begin poll_them ( present_client, s_request, next_client ); end task poll_them; input [1: 0] present_client; input [3: 1] s_request; output [1: 0] next_client; reg [1: 0] contender; integer N; begin: poll contender = `none; for ( N = 3; N >= 1; N = N – 1 ) begin: decision if ( s_request[N] ) begin if ( present_client == N ) contender = present_client; else begin next_client = N; disable poll; end end if (( next_client == `none ) && ( contender )) next_client = contender; endtask endmodule ELEN 468 Lecture 10 76

![Test Bench for Polling Circuit moduel test_polling; reg [3: 1] s_request; reg clk, rst; Test Bench for Polling Circuit moduel test_polling; reg [3: 1] s_request; reg clk, rst;](http://slidetodoc.com/presentation_image_h/30f6f219859917721811cc86a4a7b68a/image-77.jpg)

Test Bench for Polling Circuit moduel test_polling; reg [3: 1] s_request; reg clk, rst; wire [1: 0] s_code; wire sreq 3 = M 1. s_request[3]; wire sreq 2 = M 1. s_request[2]; wire sreq 1 = M 1. s_request[1]; wire [1: 0] NC = M 1. next_client; wire [1: 0] PC = M 1. present_client; wire [3: 1] s_req = s_request; wire [1: 0] s_cd = s_code; polling M 1 ( s_request, s_code, clk, rst ); initial begin clk = 0; forever #10 clk = ~clk; end initial #400 finish; initial begin rst = 1`bx; #25 rst = 1; #75 rst = 0; end initial begin #20 s_request = 3`b 100; #20 s_request = 3`b 010; #20 s_request = 3`b 001; #20 s_request = 3`b 100; #40 s_request = 3`b 010; #40 s_request = 3`b 001; end initial begin #180 s_request = 3`b 111; #60 s_request = 3`b 101; #60 s_request = 3`b 011; #60 s_request = 3`b 111; #20 rst = 1; endmodule ELEN 468 Lecture 10 77

Exercise 2 ELEN 468 Lecture 10 78

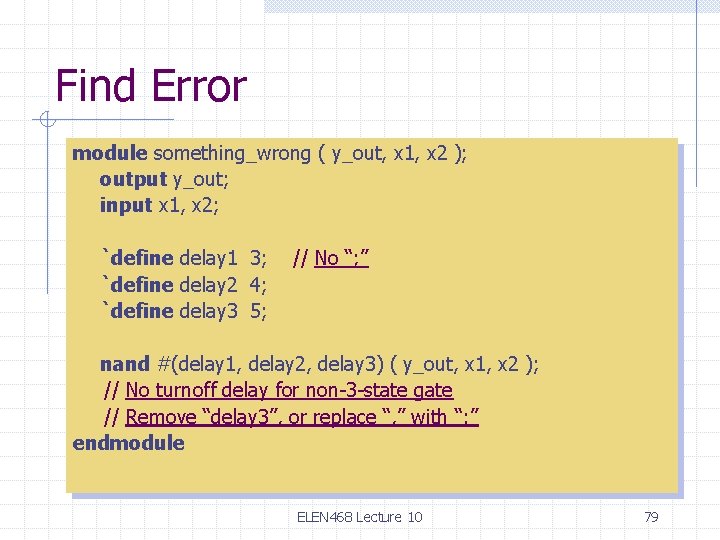

Find Error module something_wrong ( y_out, x 1, x 2 ); output y_out; input x 1, x 2; `define delay 1 3; `define delay 2 4; `define delay 3 5; // No “; ” nand #(delay 1, delay 2, delay 3) ( y_out, x 1, x 2 ); // No turnoff delay for non-3 -state gate // Remove “delay 3”, or replace “, ” with “: ” endmodule ELEN 468 Lecture 10 79

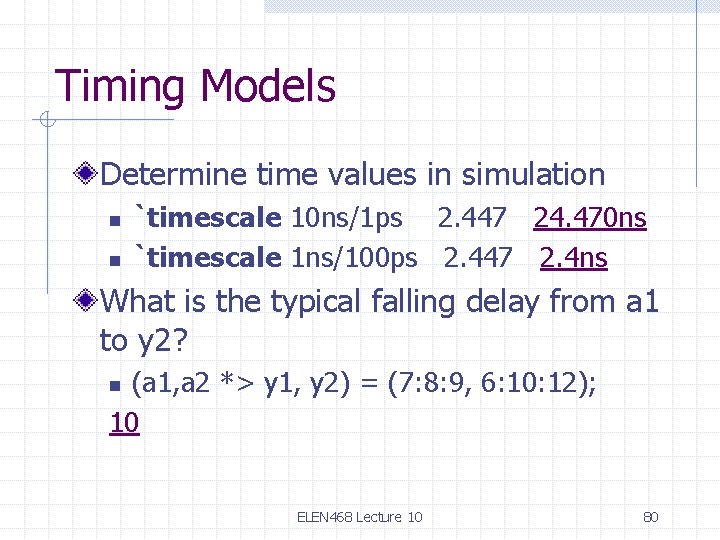

Timing Models Determine time values in simulation n n `timescale 10 ns/1 ps 2. 447 24. 470 ns `timescale 1 ns/100 ps 2. 447 2. 4 ns What is the typical falling delay from a 1 to y 2? (a 1, a 2 *> y 1, y 2) = (7: 8: 9, 6: 10: 12); 10 n ELEN 468 Lecture 10 80

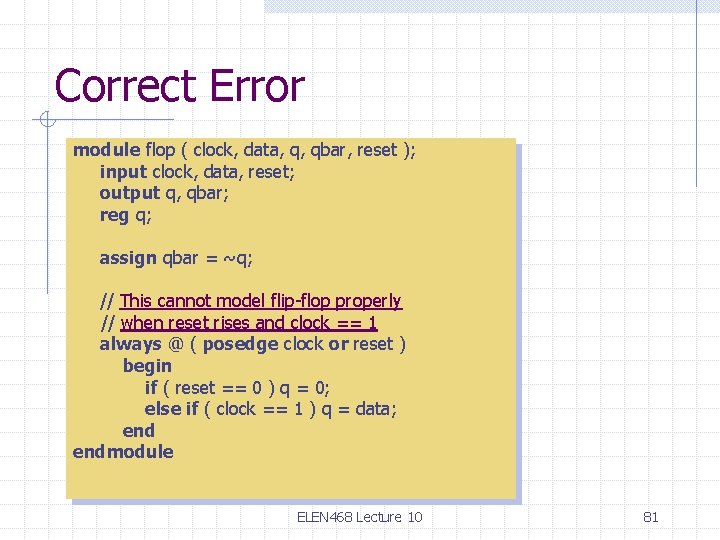

Correct Error module flop ( clock, data, q, qbar, reset ); input clock, data, reset; output q, qbar; reg q; assign qbar = ~q; // This cannot model flip-flop properly // when reset rises and clock == 1 always @ ( posedge clock or reset ) begin if ( reset == 0 ) q = 0; else if ( clock == 1 ) q = data; endmodule ELEN 468 Lecture 10 81

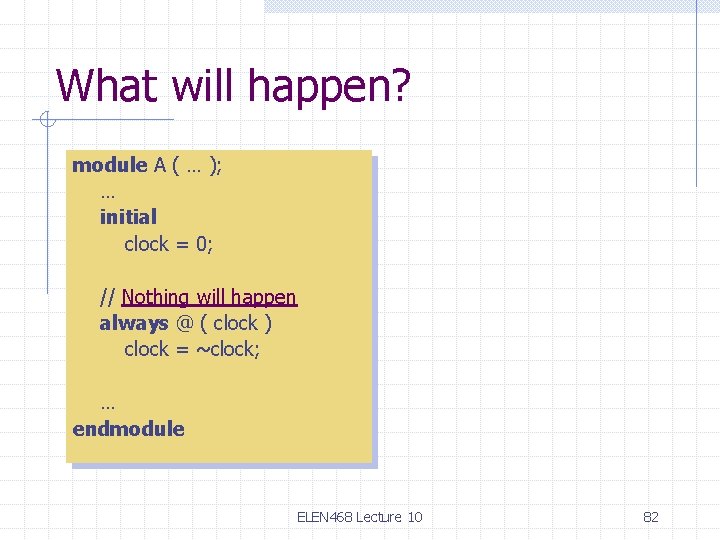

What will happen? module A ( … ); … initial clock = 0; // Nothing will happen always @ ( clock ) clock = ~clock; … endmodule ELEN 468 Lecture 10 82

- Slides: 82