UNIT IV System Organization SYSTEM ORGANIZATION InputOutput Systems

- Slides: 20

UNIT – IV – System Organization SYSTEM ORGANIZATION: Input-Output Systems – Programmed IO, DMA and Interrupts, IO Processors

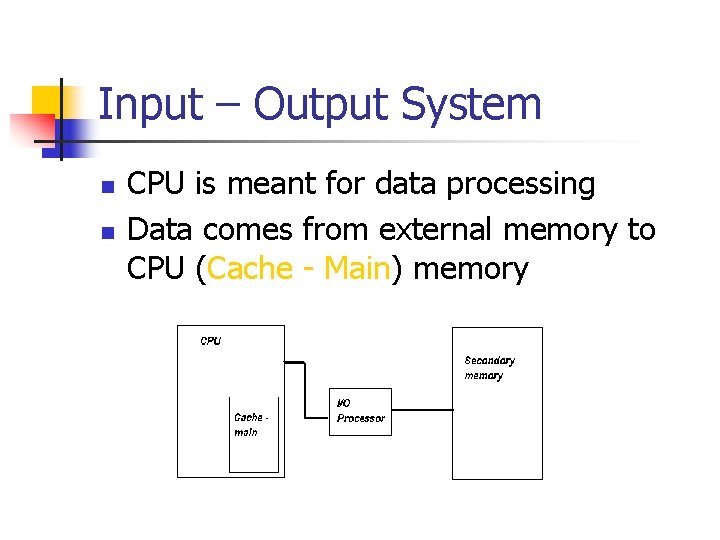

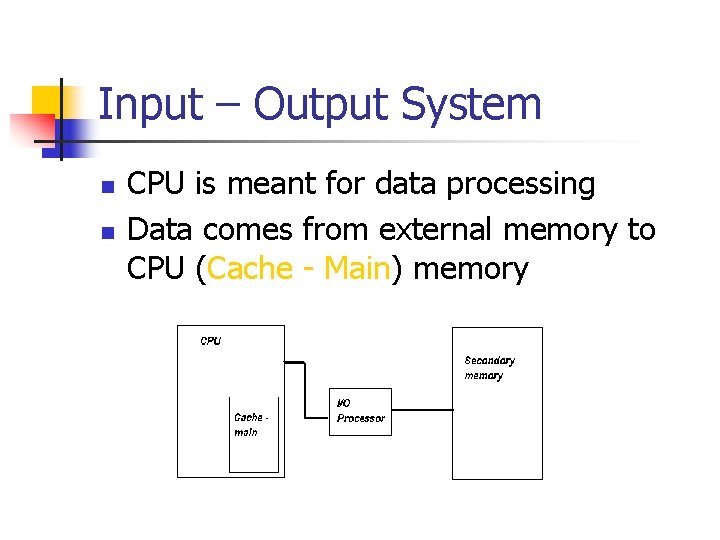

Input – Output System n n CPU is meant for data processing Data comes from external memory to CPU (Cache - Main) memory

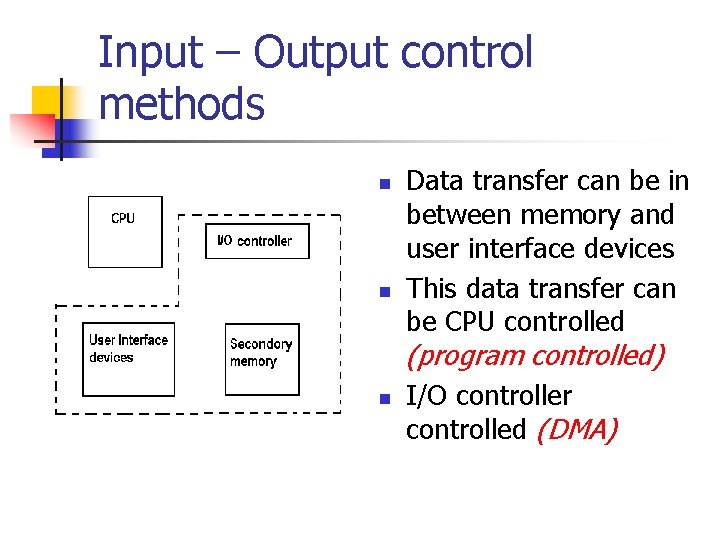

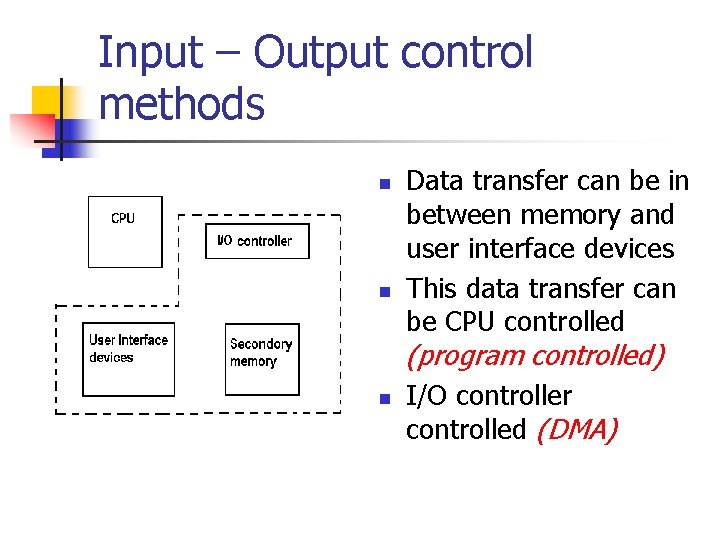

Input – Output control methods n n Data transfer can be in between memory and user interface devices This data transfer can be CPU controlled (program controlled) n I/O controller controlled (DMA)

Program Controlled n CPU is completely responsible n n n Initiate Direct and Terminate CPU executes a program Little or no specialized hardware is required Disadvantage – CPU has to spend a lot of time ( like checking status of IO device)

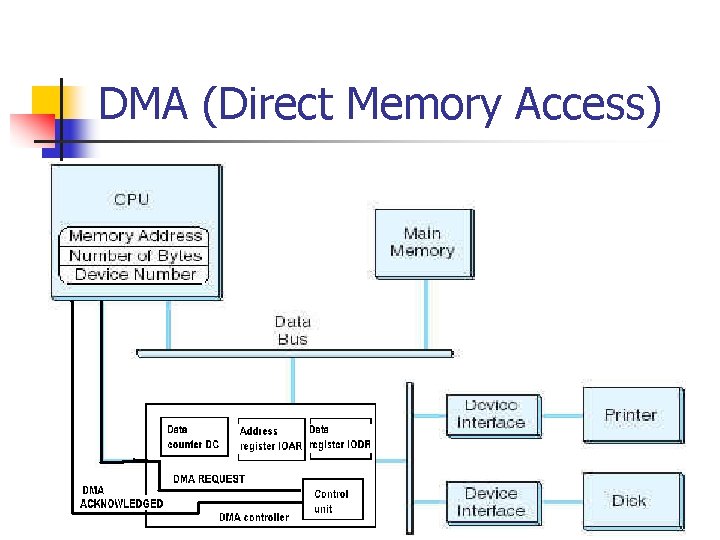

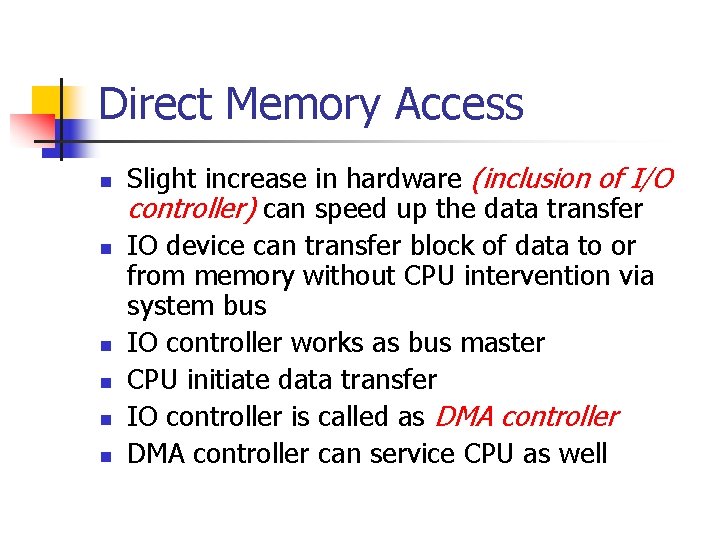

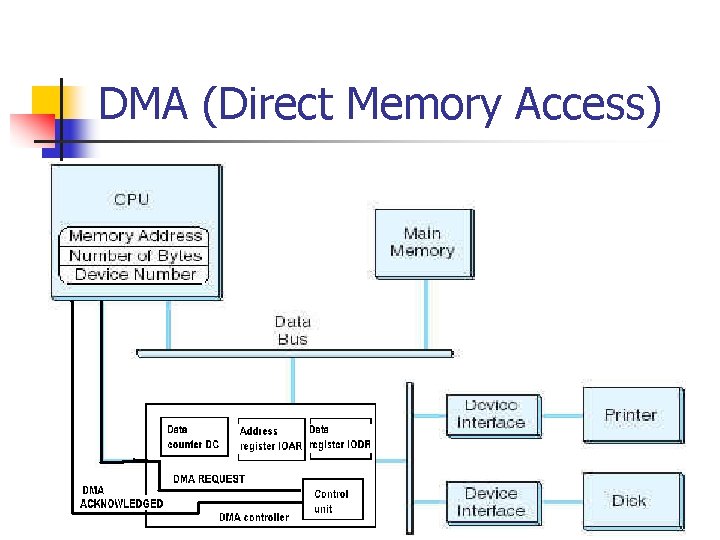

Direct Memory Access n n n Slight increase in hardware (inclusion of I/O controller) can speed up the data transfer IO device can transfer block of data to or from memory without CPU intervention via system bus IO controller works as bus master CPU initiate data transfer IO controller is called as DMA controller can service CPU as well

Interrupts n An IO device can request CPU to execute a specific program this is called as interrupt and specific program is known as interrupt handler program

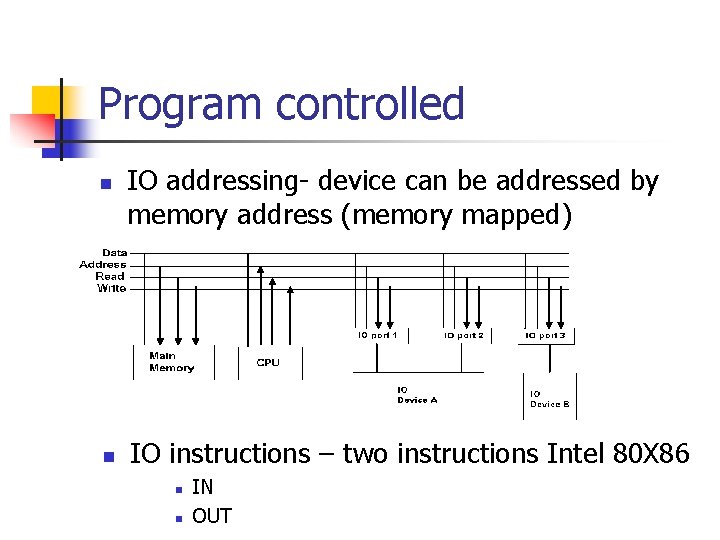

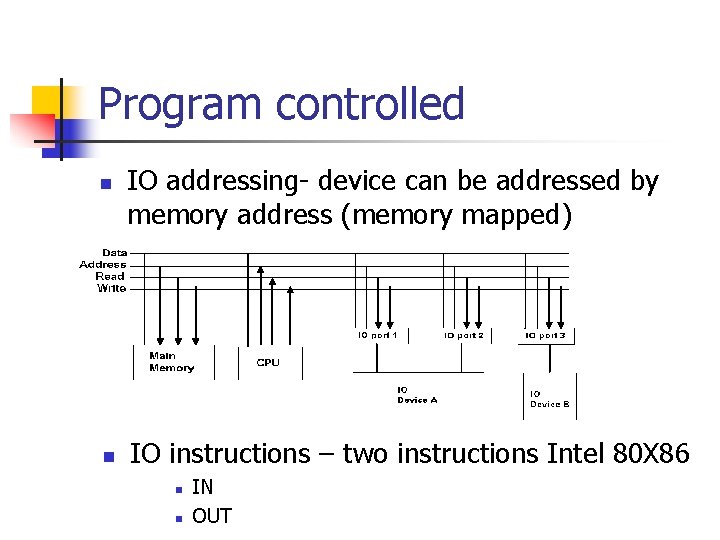

Program controlled n n IO addressing- device can be addressed by memory address (memory mapped) IO instructions – two instructions Intel 80 X 86 n n IN OUT

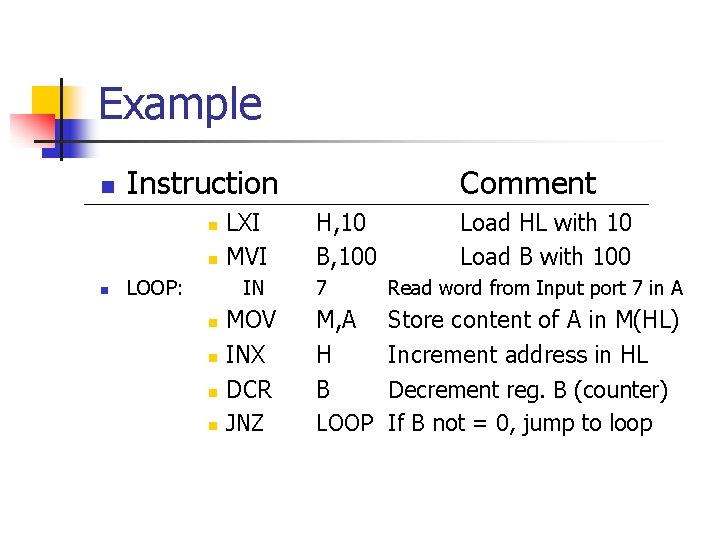

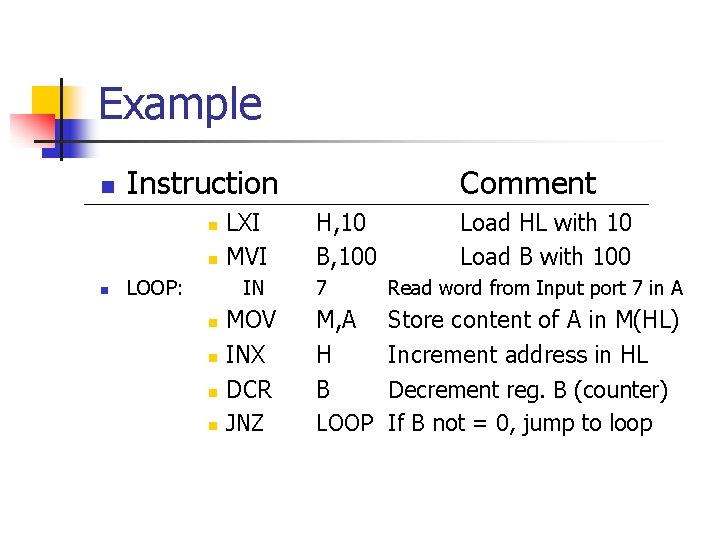

Example n Instruction n LOOP: LXI MVI IN n n MOV INX DCR JNZ Comment H, 10 B, 100 Load HL with 10 Load B with 100 7 Read word from Input port 7 in A M, A H B LOOP Store content of A in M(HL) Increment address in HL Decrement reg. B (counter) If B not = 0, jump to loop

DMA (Direct Memory Access) n Shortcomings of programmed IO are n n n CPU is busy all time CPU has to check all IO devices DMA and interrupts can speed up the data transfer n n In this INTR request and DMA request signals are sent to CPU Without the need of CPU instruction IO device can use system buses for data transfer in DMA

DMA (Direct Memory Access)

Interrupt n When CPU receives a interrupt signal from IO device it suspends is current work and execute a interrupt handler program summarized in following steps 1. Identification of source of interrupt n n Multiple interrupt line Software poll Daisy chaining (hardware poll, vectored) Bus arbitration (vectored)

2. CPU obtains the memory address of required interrupt handler program 3. The Program counter and status of CPU is saved as in subroutine call 4. The PC is loaded with address of interrupt handler. Execution proceeds until return instruction

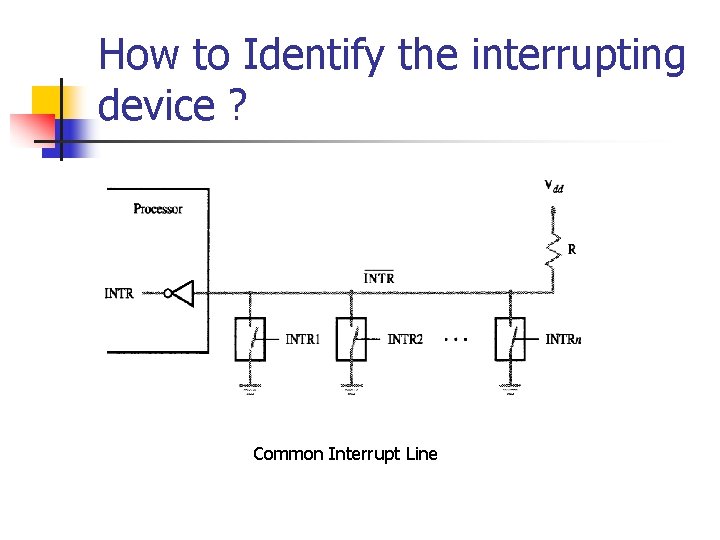

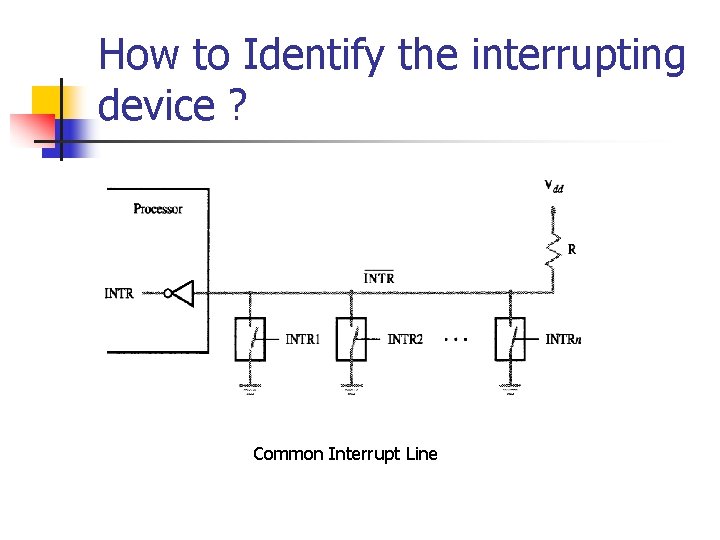

How to Identify the interrupting device ? Common Interrupt Line

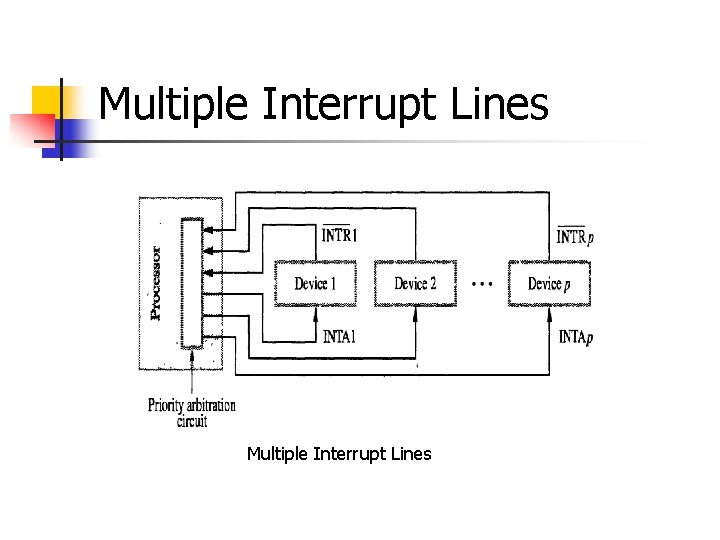

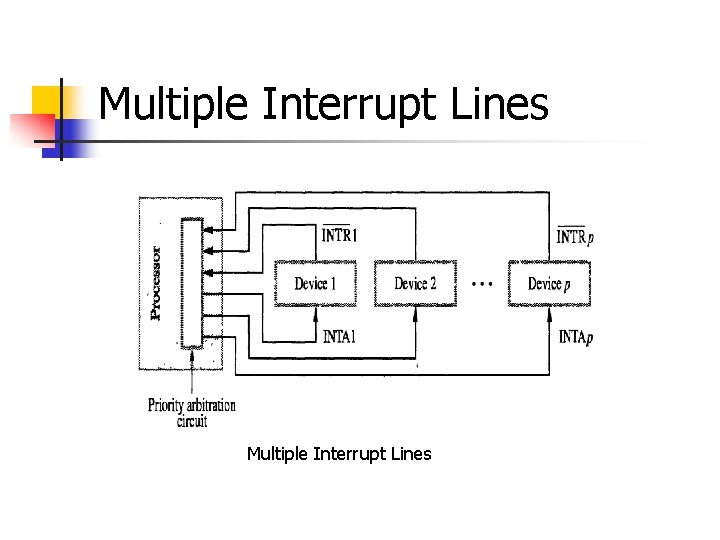

Multiple Interrupt Lines

Software poll n CPU execute a instruction TEST IO (IO address) and interrupting device respond positively

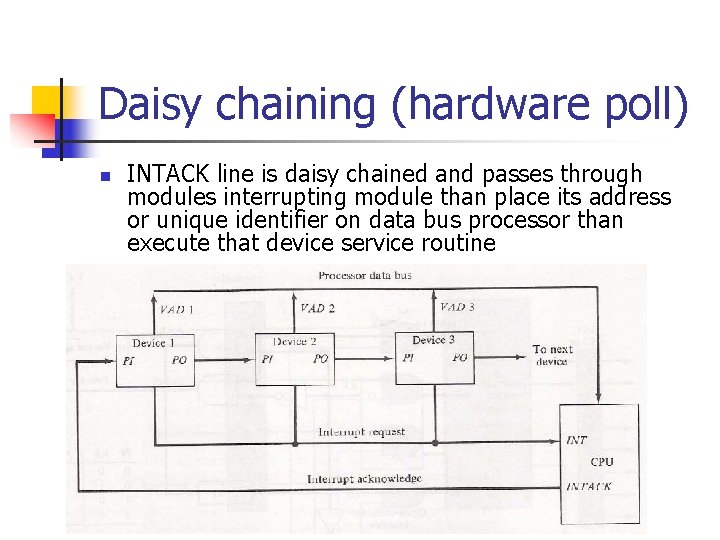

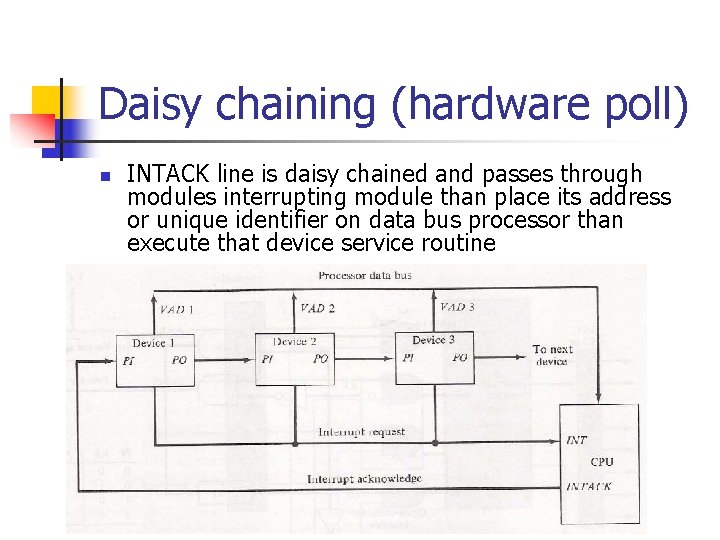

Daisy chaining (hardware poll) n INTACK line is daisy chained and passes through modules interrupting module than place its address or unique identifier on data bus processor than execute that device service routine

Bus arbitration (vectored) n Bus arbitration : in this first interrupting module gain control over data bus before it can raise interrupt request line

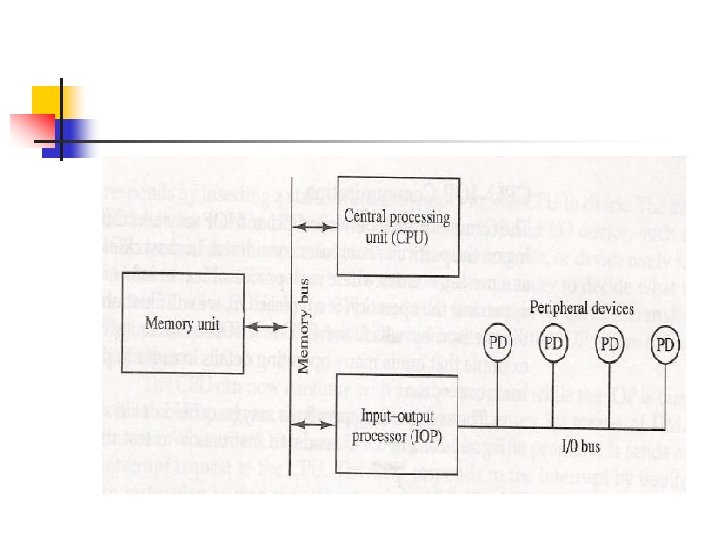

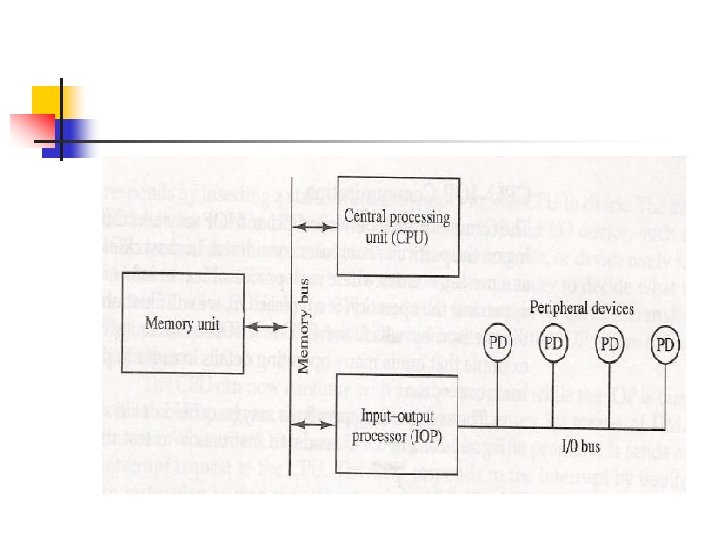

I/O processors (PPU) n n Dedicated for data transfer and CPU almost remain out of scene I/O processors = coprocessors Program for I/O processors is written in main memory I/O processors controls I/O devices

UPLOADED ON http: //www. ecepiet. blogspot. com