Topic 3 a Twos Complement Representation Introduction to

- Slides: 19

Topic 3 a Two’s Complement Representation Introduction to Computer Systems Engineering (CPEG 323) 2021/6/14 cpeg 323 -05 FTopic 3 a-323 1

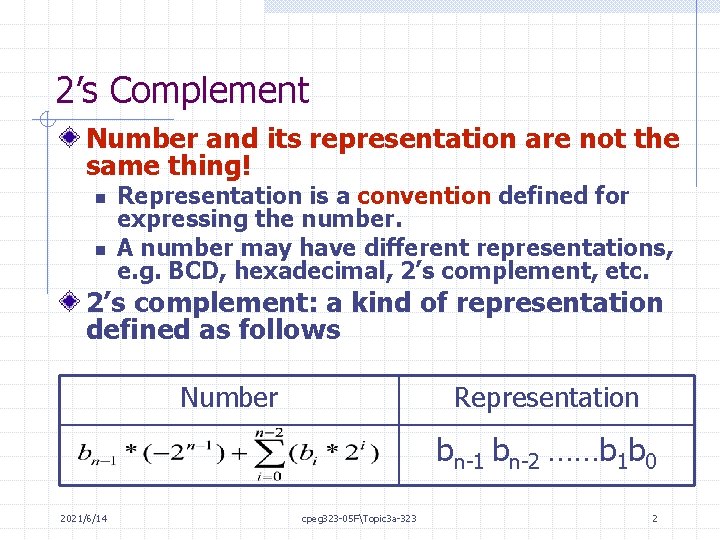

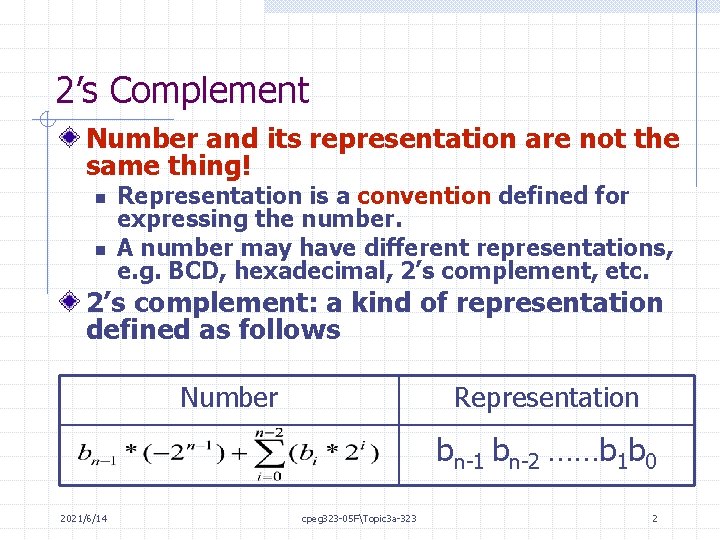

2’s Complement Number and its representation are not the same thing! n n Representation is a convention defined for expressing the number. A number may have different representations, e. g. BCD, hexadecimal, 2’s complement, etc. 2’s complement: a kind of representation defined as follows Number Representation bn-1 bn-2 ……b 1 b 0 2021/6/14 cpeg 323 -05 FTopic 3 a-323 2

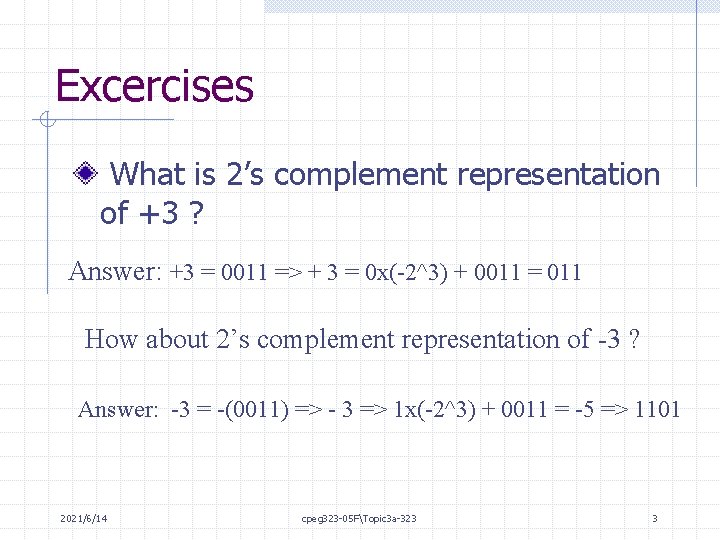

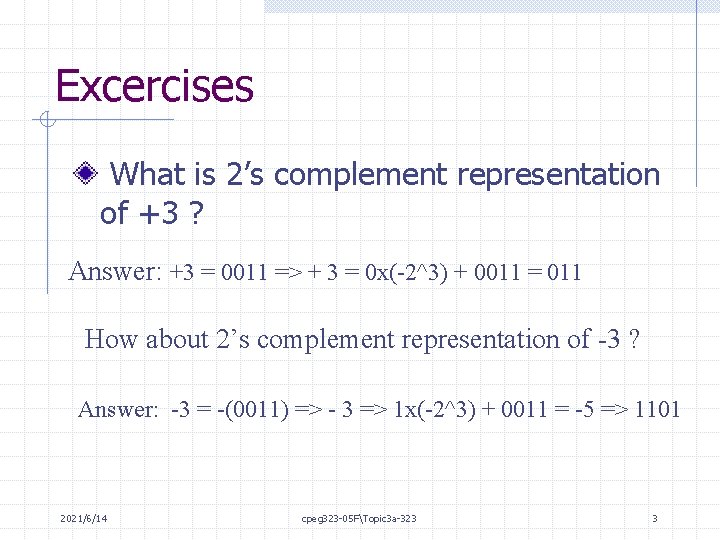

Excercises What is 2’s complement representation of +3 ? Answer: +3 = 0011 => + 3 = 0 x(-2^3) + 0011 = 011 How about 2’s complement representation of -3 ? Answer: -3 = -(0011) => - 3 => 1 x(-2^3) + 0011 = -5 => 1101 2021/6/14 cpeg 323 -05 FTopic 3 a-323 3

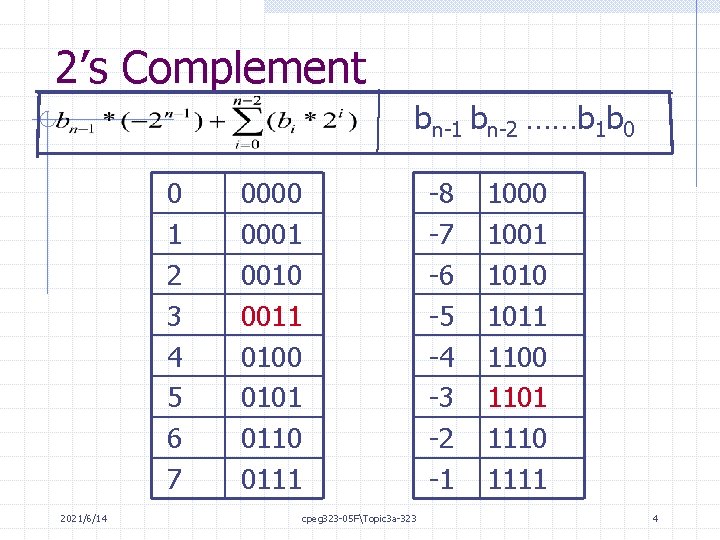

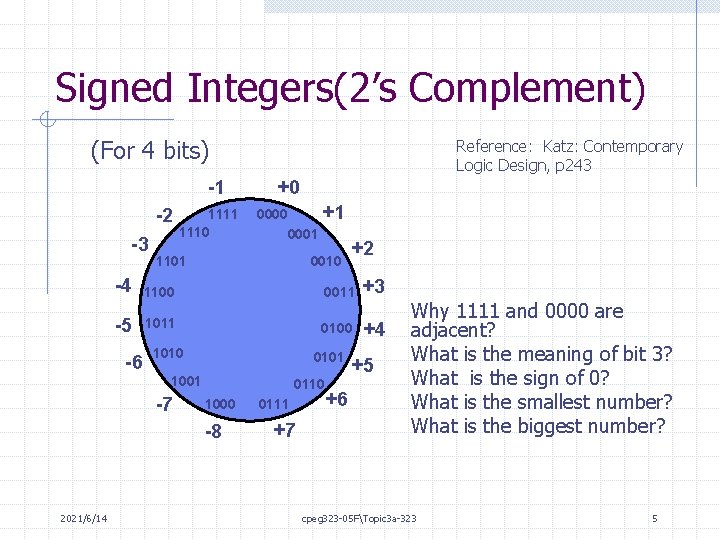

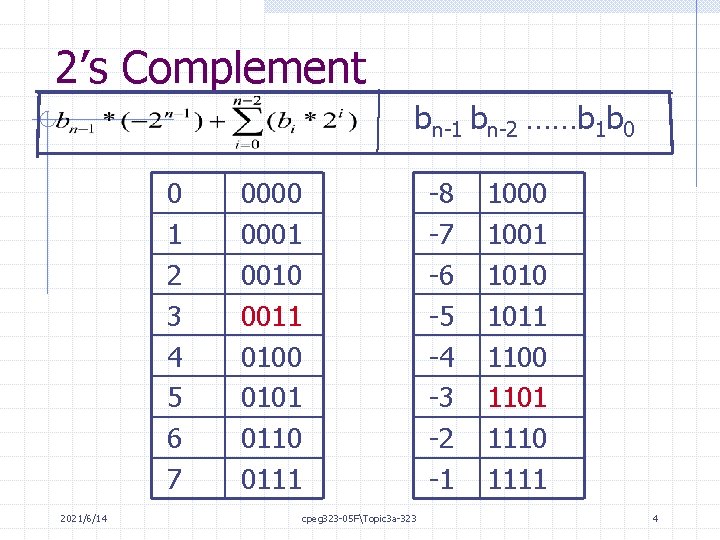

2’s Complement bn-1 bn-2 ……b 1 b 0 0 1 2 3 4 5 6 7 2021/6/14 0000 0001 0010 0011 0100 0101 0110 0111 -8 -7 -6 -5 -4 -3 -2 -1 cpeg 323 -05 FTopic 3 a-323 1000 1001 1010 1011 1100 1101 1110 1111 4

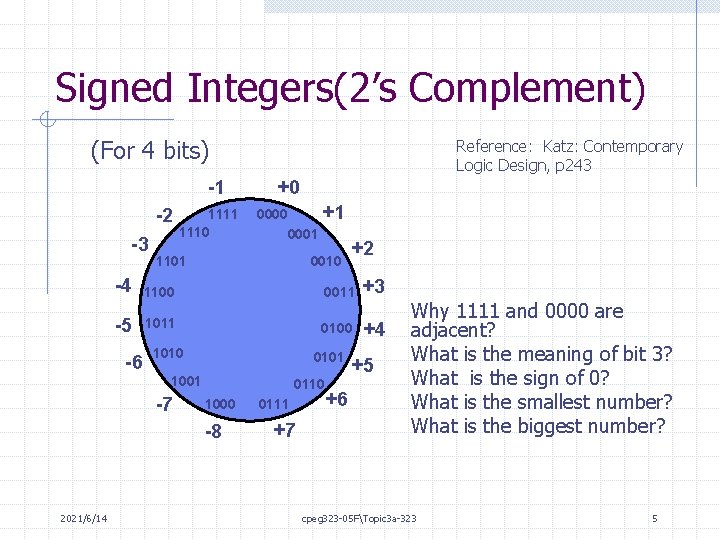

Signed Integers(2’s Complement) (For 4 bits) -1 -2 -3 1111 1110 Reference: Katz: Contemporary Logic Design, p 243 +0 0000 +1 0001 1101 0010 -4 1100 0011 +3 -5 1011 0100 +4 -6 1010 0101 1001 -7 0110 1000 -8 2021/6/14 +2 0111 +7 +6 +5 Why 1111 and 0000 are adjacent? What is the meaning of bit 3? What is the sign of 0? What is the smallest number? What is the biggest number? cpeg 323 -05 FTopic 3 a-323 5

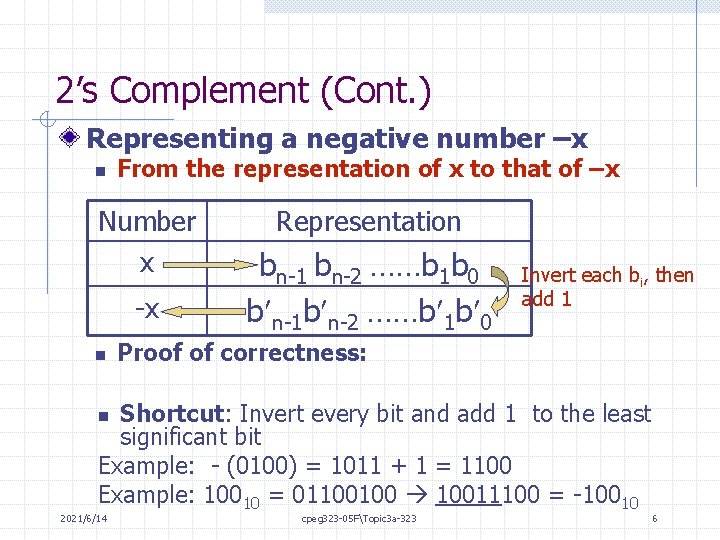

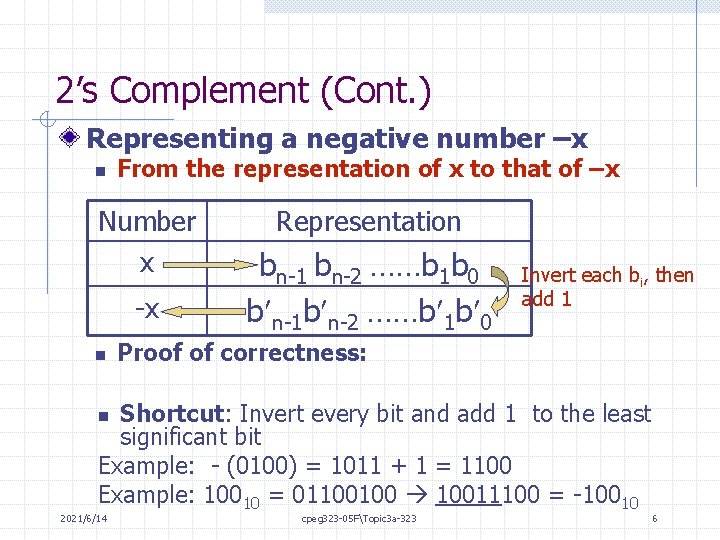

2’s Complement (Cont. ) Representing a negative number –x n From the representation of x to that of –x Number x -x n Representation bn-1 bn-2 ……b 1 b 0 b n-1 b n-2 ……b 1 b 0 Invert each bi, then add 1 Proof of correctness: Shortcut: Invert every bit and add 1 to the least significant bit Example: - (0100) = 1011 + 1 = 1100 Example: 10010 = 01100100 10011100 = -10010 n 2021/6/14 cpeg 323 -05 FTopic 3 a-323 6

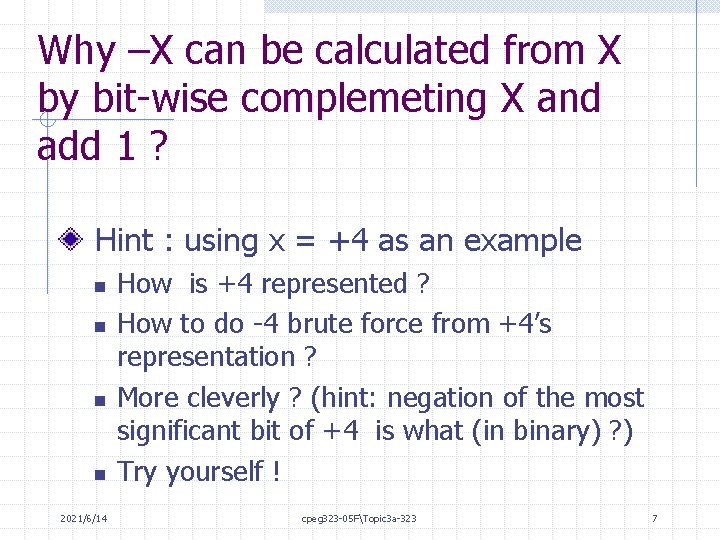

Why –X can be calculated from X by bit-wise complemeting X and add 1 ? Hint : using x = +4 as an example n n 2021/6/14 How is +4 represented ? How to do -4 brute force from +4’s representation ? More cleverly ? (hint: negation of the most significant bit of +4 is what (in binary) ? ) Try yourself ! cpeg 323 -05 FTopic 3 a-323 7

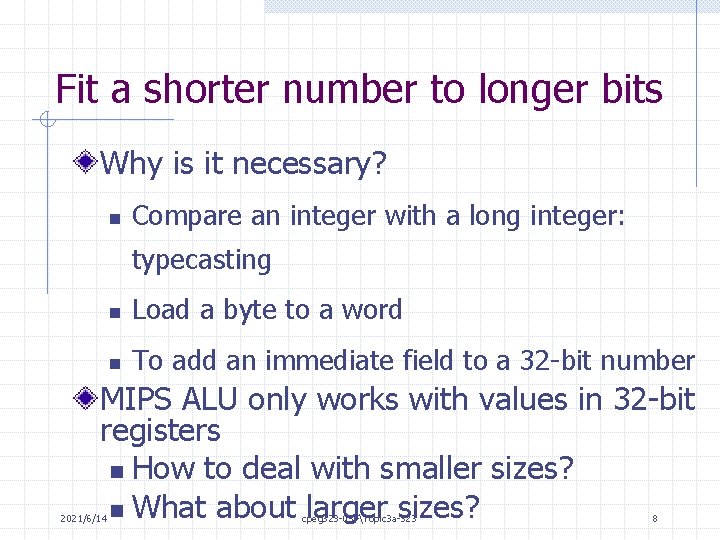

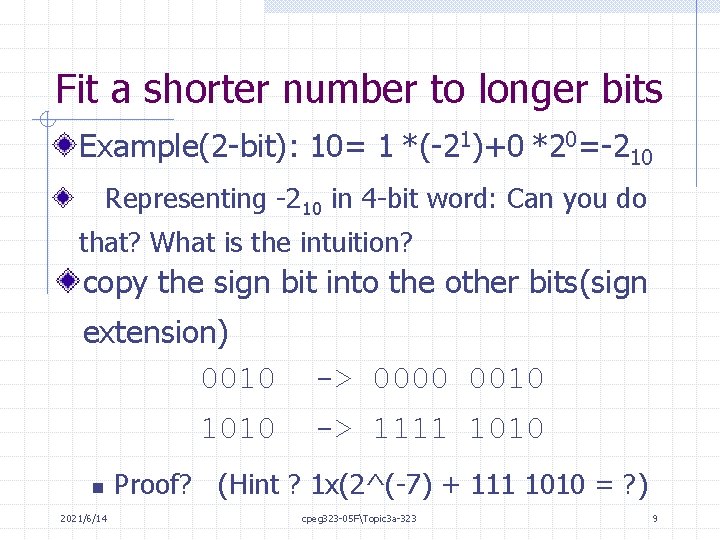

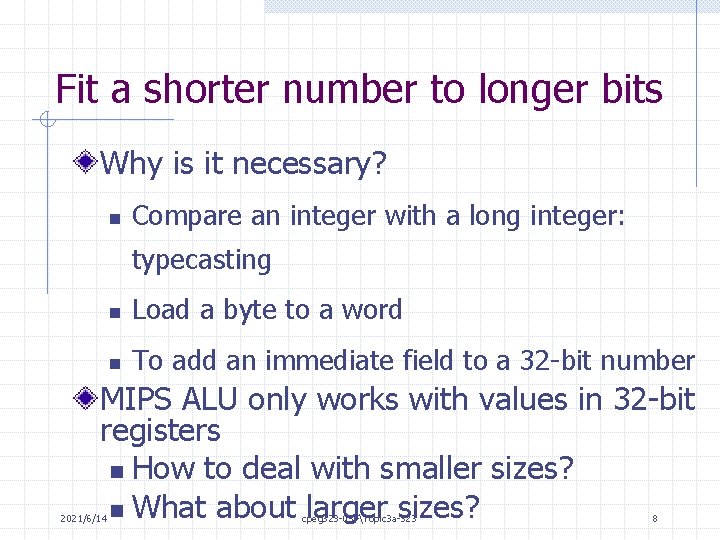

Fit a shorter number to longer bits Why is it necessary? n Compare an integer with a long integer: typecasting n Load a byte to a word n To add an immediate field to a 32 -bit number MIPS ALU only works with values in 32 -bit registers n How to deal with smaller sizes? n What about larger sizes? 2021/6/14 cpeg 323 -05 FTopic 3 a-323 8

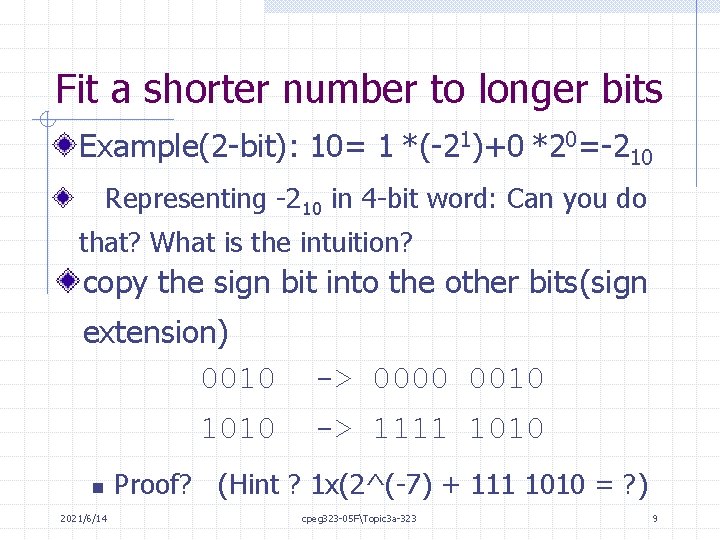

Fit a shorter number to longer bits Example(2 -bit): 10= 1 *(-21)+0 *20=-210 Representing -210 in 4 -bit word: Can you do that? What is the intuition? copy the sign bit into the other bits(sign extension) 0010 -> 0000 0010 1010 -> 1111 1010 n 2021/6/14 Proof? (Hint ? 1 x(2^(-7) + 111 1010 = ? ) cpeg 323 -05 FTopic 3 a-323 9

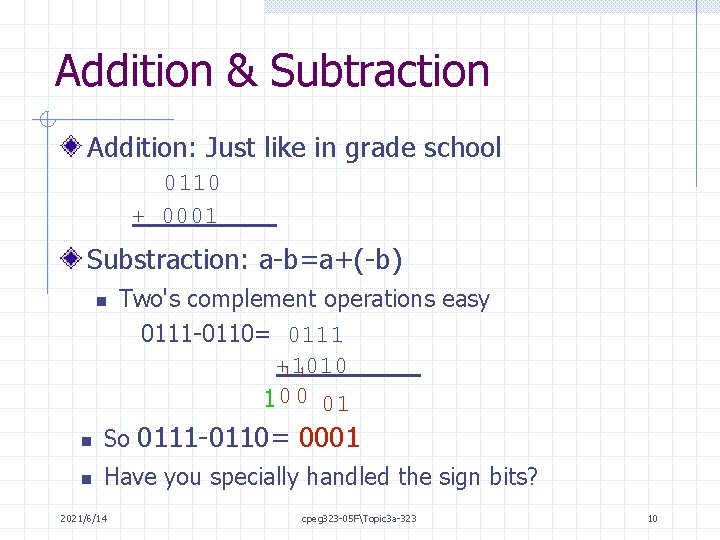

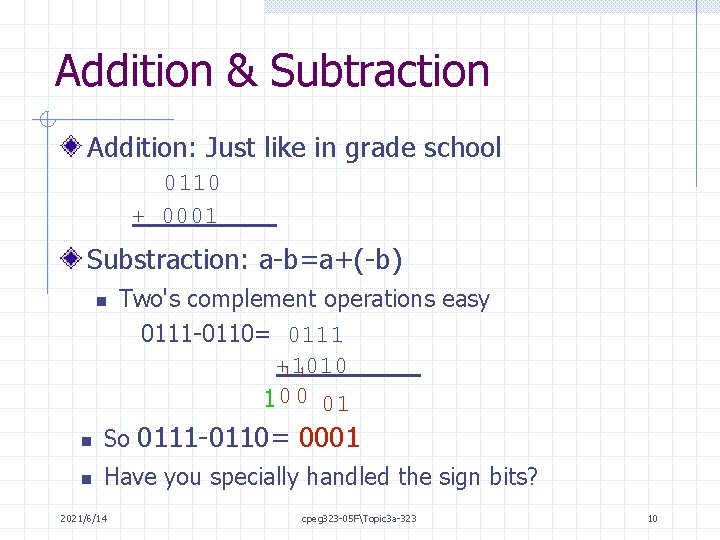

Addition & Subtraction Addition: Just like in grade school 0110 + 0001 Substraction: a-b=a+(-b) n Two's complement operations easy 0111 -0110= 0111 +1010 1 1 1 0 0 01 n So 0111 -0110= 0001 n Have you specially handled the sign bits? 2021/6/14 cpeg 323 -05 FTopic 3 a-323 10

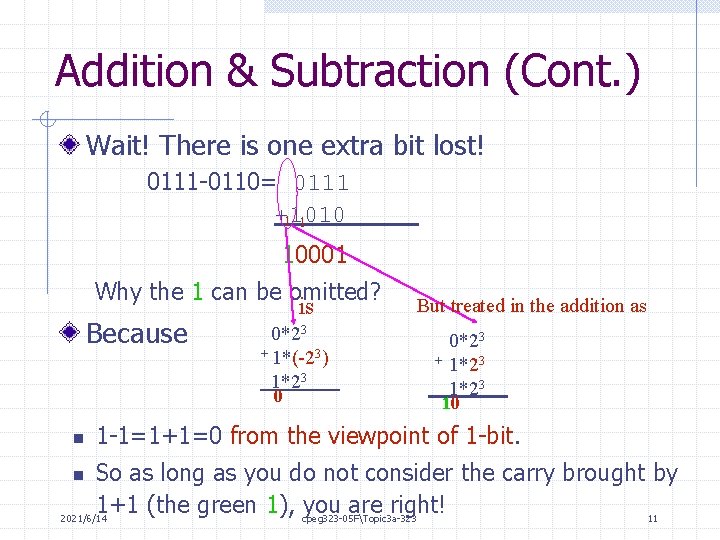

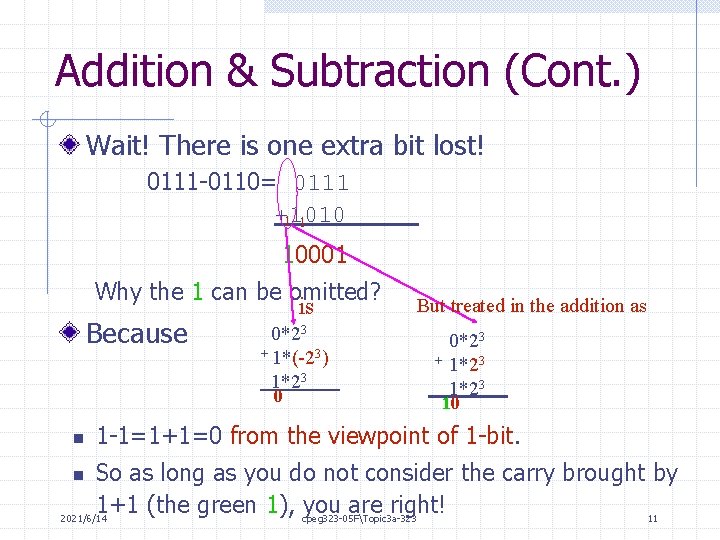

Addition & Subtraction (Cont. ) Wait! There is one extra bit lost! 0111 -0110= 0111 +1010 1 1 10001 Why the 1 can be omitted? is Because 0*23 + 1*(-23) 1*23 0 n But treated in the addition as 0*23 + 1*23 10 1 -1=1+1=0 from the viewpoint of 1 -bit. So as long as you do not consider the carry brought by 1+1 (the green 1), cpeg 323 -05 FTopic 3 a-323 you are right! 2021/6/14 11 n

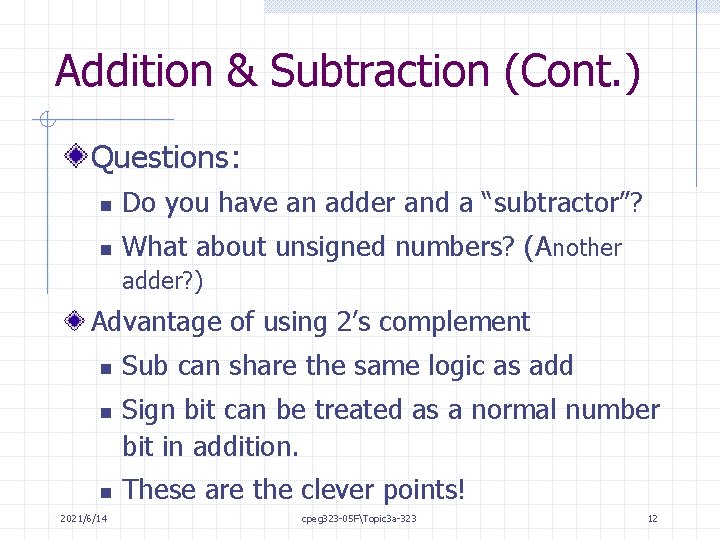

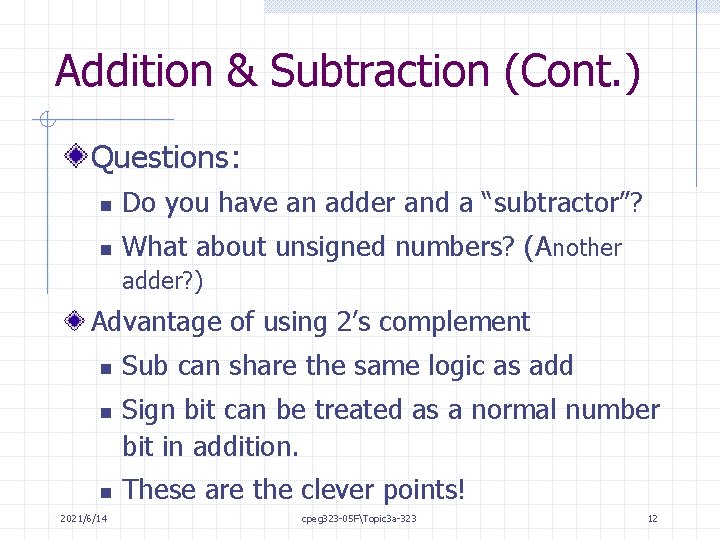

Addition & Subtraction (Cont. ) Questions: n Do you have an adder and a “subtractor”? n What about unsigned numbers? (Another adder? ) Advantage of using 2’s complement n n n 2021/6/14 Sub can share the same logic as add Sign bit can be treated as a normal number bit in addition. These are the clever points! cpeg 323 -05 FTopic 3 a-323 12

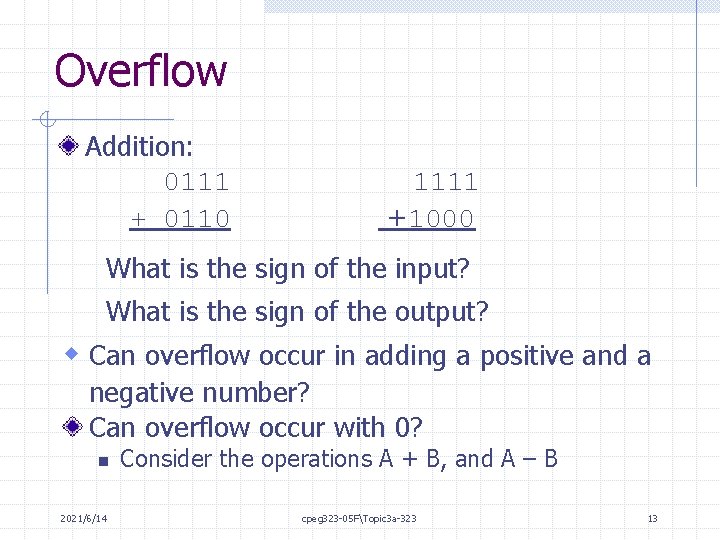

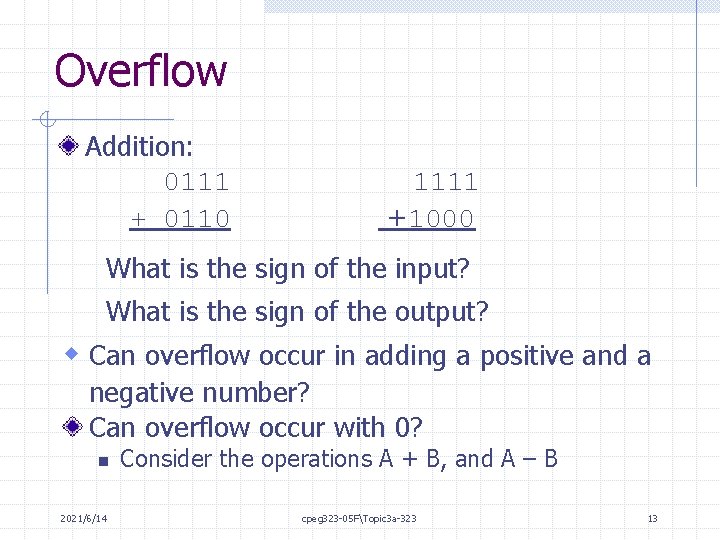

Overflow Addition: 0111 + 0110 1111 +1000 What is the sign of the input? What is the sign of the output? w Can overflow occur in adding a positive and a negative number? Can overflow occur with 0? n 2021/6/14 Consider the operations A + B, and A – B cpeg 323 -05 FTopic 3 a-323 13

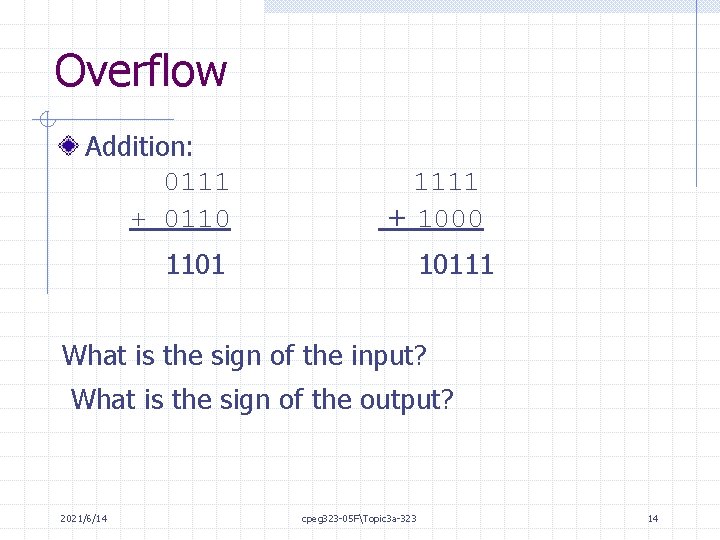

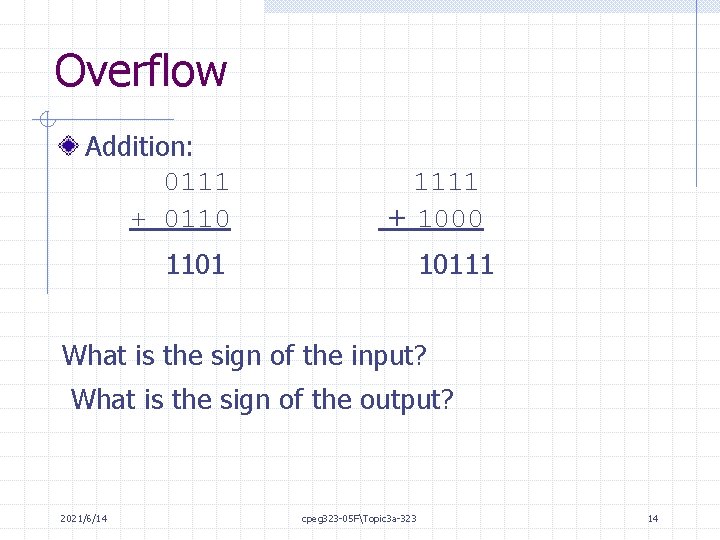

Overflow Addition: 0111 + 0110 1111 + 1000 1101 10111 What is the sign of the input? What is the sign of the output? 2021/6/14 cpeg 323 -05 FTopic 3 a-323 14

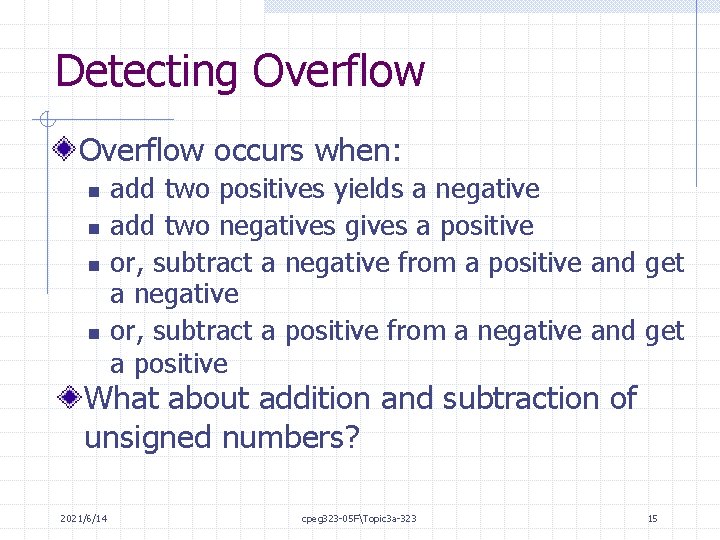

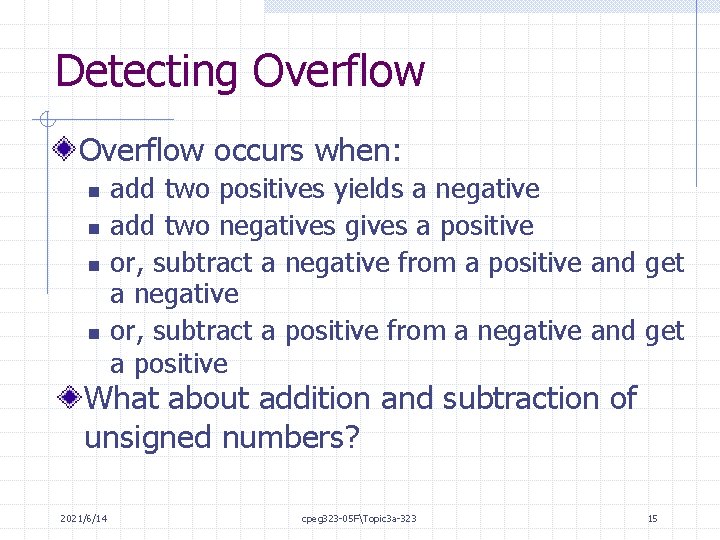

Detecting Overflow occurs when: n n add two positives yields a negative add two negatives gives a positive or, subtract a negative from a positive and get a negative or, subtract a positive from a negative and get a positive What about addition and subtraction of unsigned numbers? 2021/6/14 cpeg 323 -05 FTopic 3 a-323 15

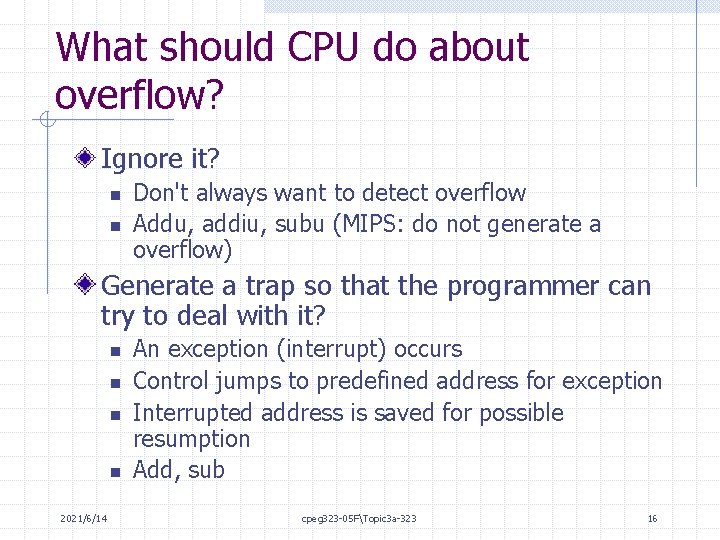

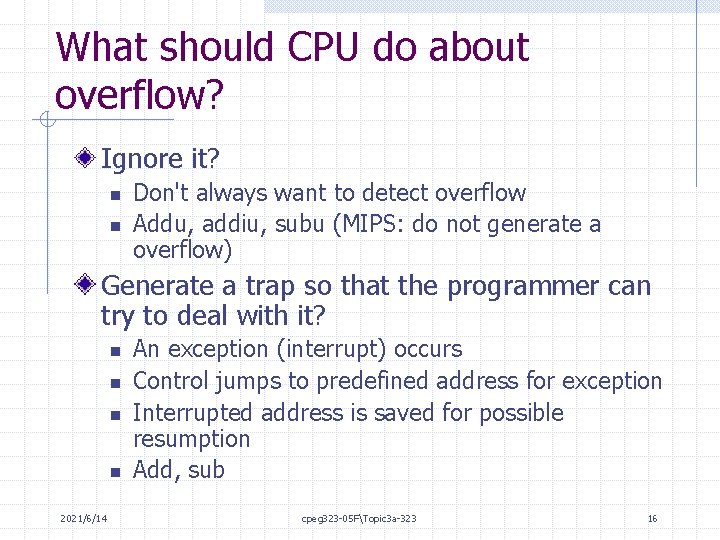

What should CPU do about overflow? Ignore it? n n Don't always want to detect overflow Addu, addiu, subu (MIPS: do not generate a overflow) Generate a trap so that the programmer can try to deal with it? n n 2021/6/14 An exception (interrupt) occurs Control jumps to predefined address for exception Interrupted address is saved for possible resumption Add, sub cpeg 323 -05 FTopic 3 a-323 16

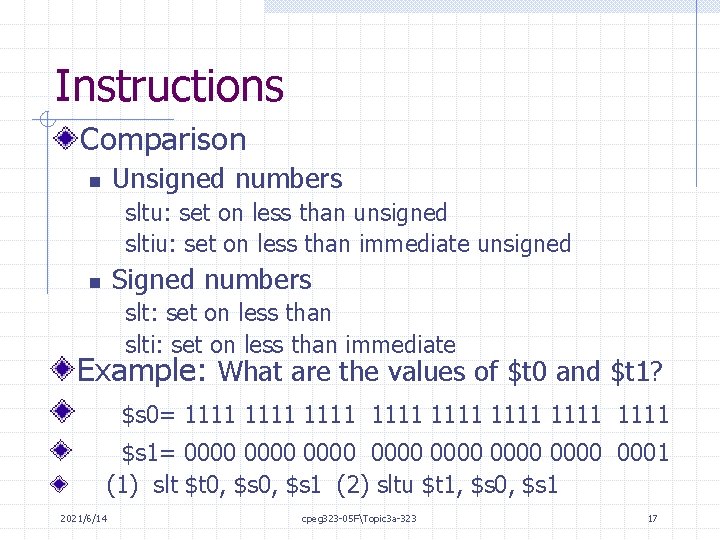

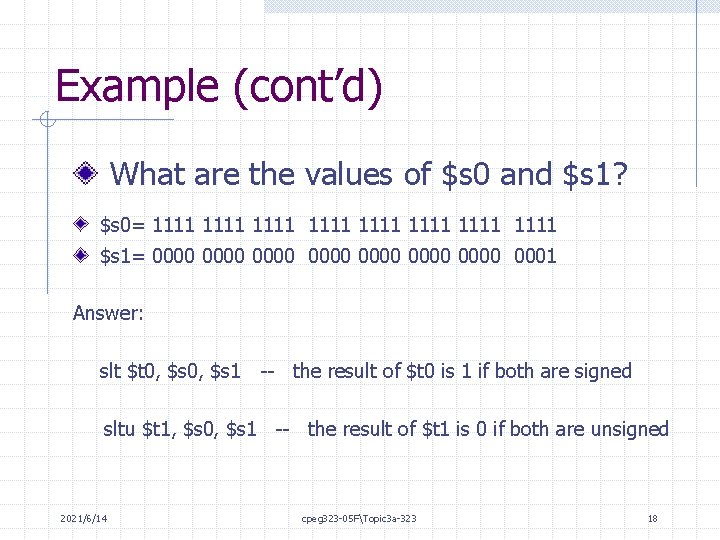

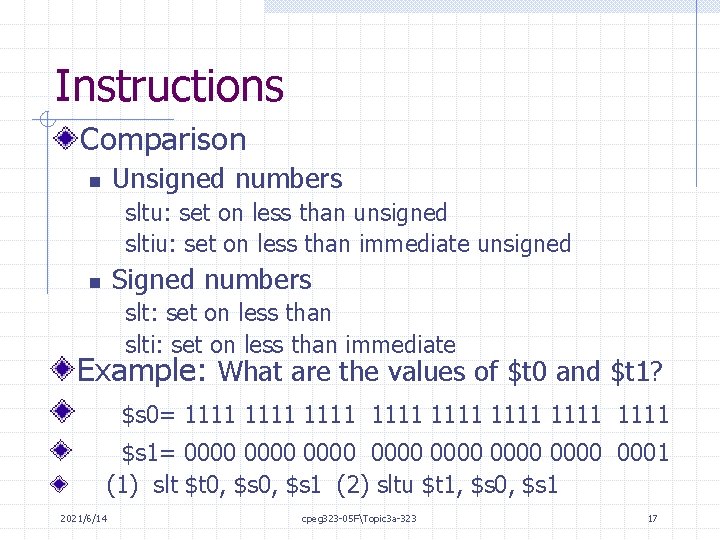

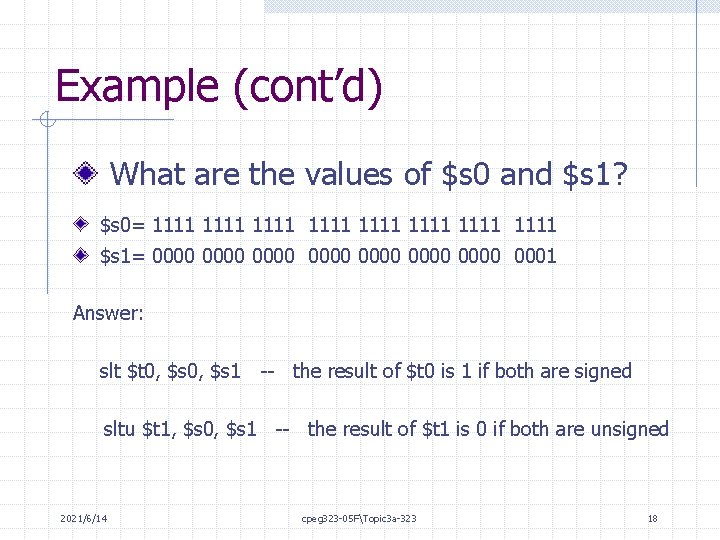

Instructions Comparison Unsigned numbers n sltu: set on less than unsigned sltiu: set on less than immediate unsigned Signed numbers n slt: set on less than slti: set on less than immediate Example: What are the values of $t 0 and $t 1? $s 0= 1111 1111 $s 1= 0000 0000 0001 (1) slt $t 0, $s 1 (2) sltu $t 1, $s 0, $s 1 2021/6/14 cpeg 323 -05 FTopic 3 a-323 17

Example (cont’d) What are the values of $s 0 and $s 1? $s 0= 1111 1111 $s 1= 0000 0000 0001 Answer: slt $t 0, $s 1 -- the result of $t 0 is 1 if both are signed sltu $t 1, $s 0, $s 1 -- the result of $t 1 is 0 if both are unsigned 2021/6/14 cpeg 323 -05 FTopic 3 a-323 18

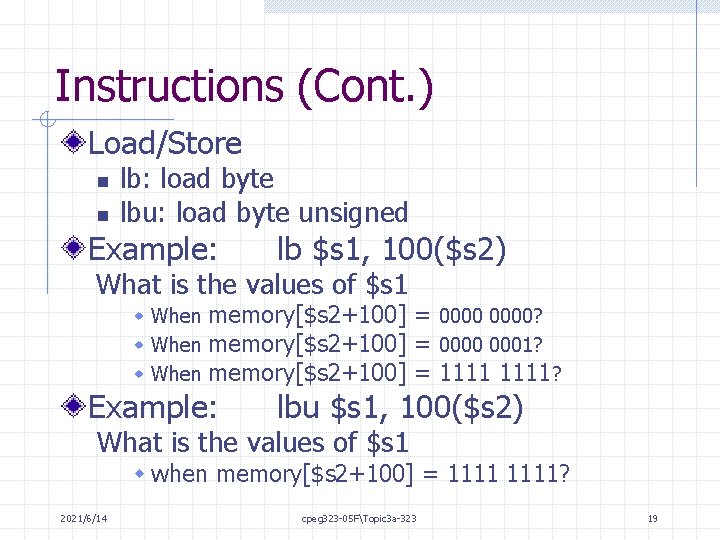

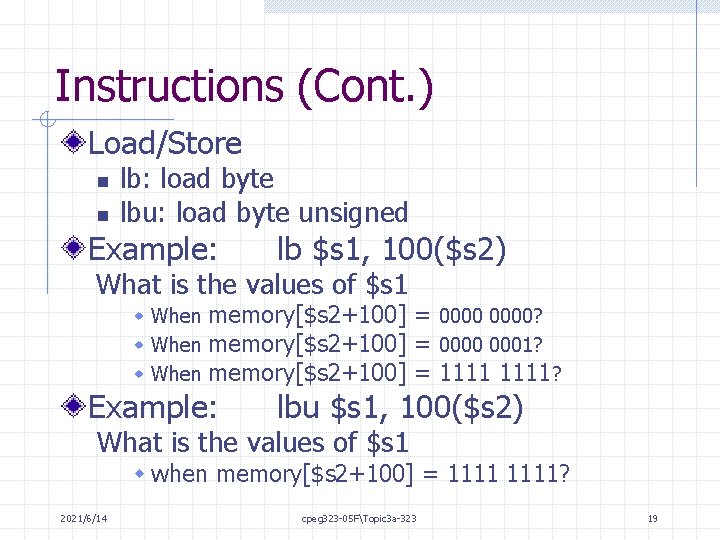

Instructions (Cont. ) Load/Store n n lb: load byte lbu: load byte unsigned Example: lb $s 1, 100($s 2) What is the values of $s 1 w When memory[$s 2+100] = 0000? memory[$s 2+100] = 0000 0001? memory[$s 2+100] = 1111? Example: lbu $s 1, 100($s 2) What is the values of $s 1 w when memory[$s 2+100] = 1111? 2021/6/14 cpeg 323 -05 FTopic 3 a-323 19