The First Integration Test of the ATLAS Endcap

- Slides: 14

The First Integration Test of the ATLAS End-cap Muon Level 1 Trigger System NSS 2002 in Norfolk, Virginia, USA Chikara Fukunaga Tokyo Metropolitan University On behalf of the ATLAS TGC electronics group Introduction Overview of ATLAS End-cap Muon Level 1 Trigger TGC electronics (Level 1 Trigger + TGC Readout) Slice Test Setup Test Results Summary 14/November/2002 CF 1

NSS 2002 in Norfolk, Virginia, USA Introduction 3 main ASICs out of total 7 have been made with full specifications. Stand-alone tests of ASICs have been finished. An overall integrated test has been required with all these ASICs in one test bed →Slice test (SLT) system. C++ based trigger simulation program has been needed and developed, and it could give the test patterns and answers to the SLT system. Integration test started in Sept. , ’ 01, all the components have been installed in Aug. , ’ 02. 14/November/2002 CF 2

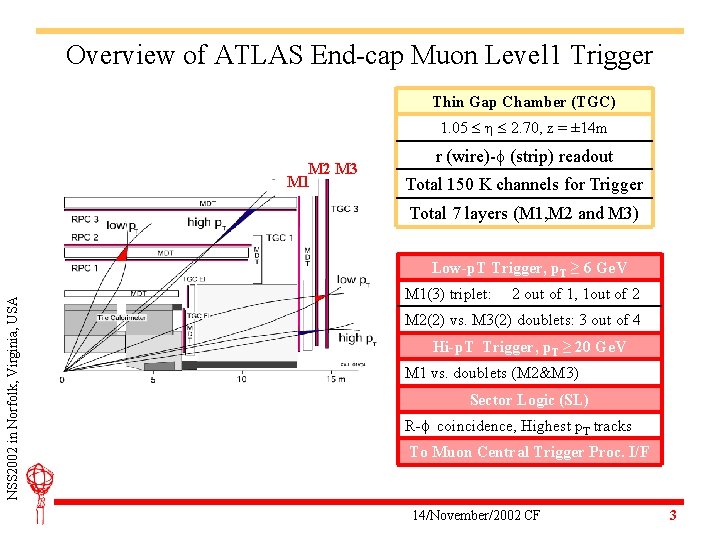

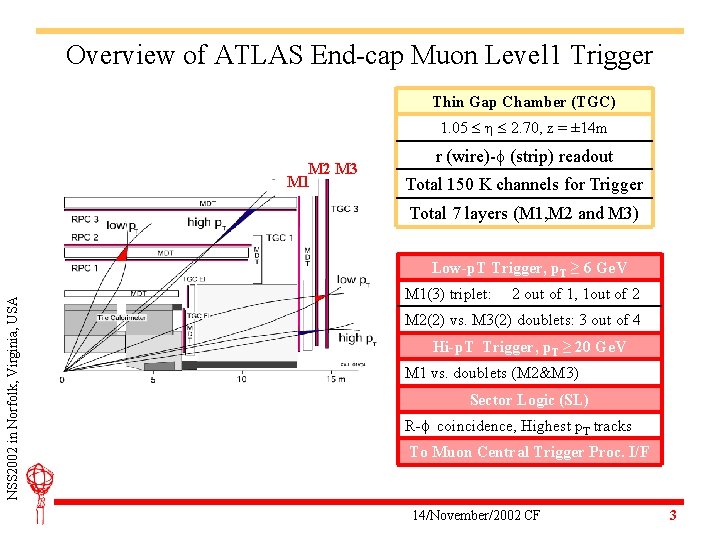

Overview of ATLAS End-cap Muon Level 1 Trigger Thin Gap Chamber (TGC) 1. 05 η 2. 70, z = ± 14 m M 2 M 3 M 1 r (wire)-f (strip) readout Total 150 K channels for Trigger Total 7 layers (M 1, M 2 and M 3) NSS 2002 in Norfolk, Virginia, USA Low-p. T Trigger, p. T ≥ 6 Ge. V M 1(3) triplet: 2 out of 1, 1 out of 2 M 2(2) vs. M 3(2) doublets: 3 out of 4 Hi-p. T Trigger, p. T ≥ 20 Ge. V M 1 vs. doublets (M 2&M 3) Sector Logic (SL) R-f coincidence, Highest p. T tracks To Muon Central Trigger Proc. I/F 14/November/2002 CF 3

TGC electronics (Level 1 Trigger + TGC Readout) On detector part Off detector part M 3 NSS 2002 in Norfolk, Virginia, USA M 2 M 1 14/November/2002 CF 4

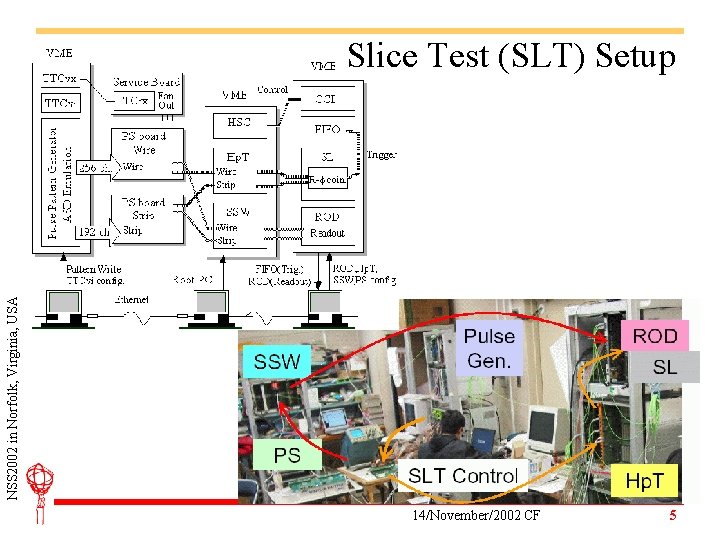

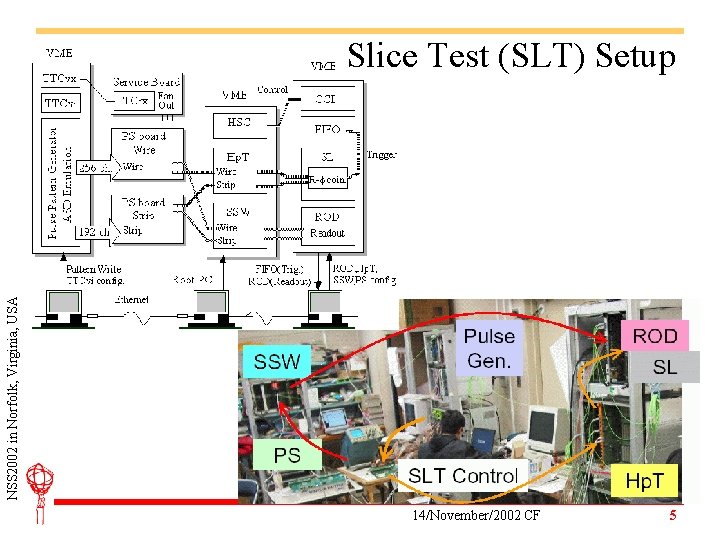

NSS 2002 in Norfolk, Virginia, USA Slice Test (SLT) Setup 14/November/2002 CF 5

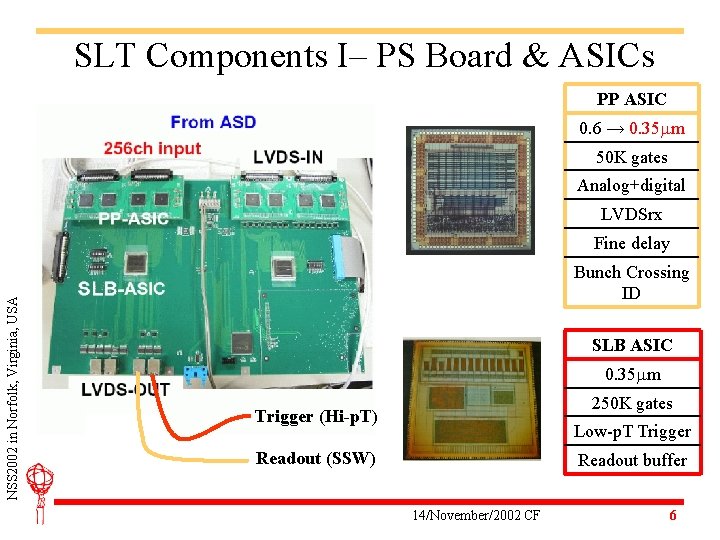

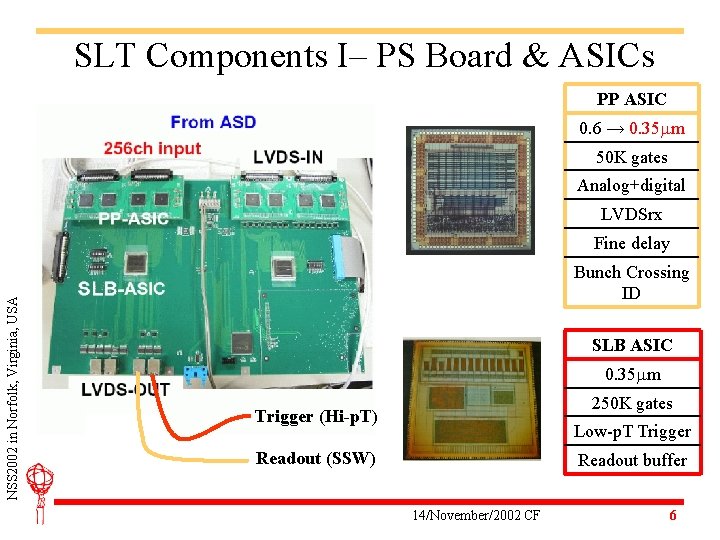

SLT Components I– PS Board & ASICs PP ASIC 0. 6 → 0. 35 mm 50 K gates Analog+digital LVDSrx NSS 2002 in Norfolk, Virginia, USA Fine delay Bunch Crossing ID SLB ASIC 0. 35 mm 250 K gates Trigger (Hi-p. T) Low-p. T Trigger Readout (SSW) Readout buffer 14/November/2002 CF 6

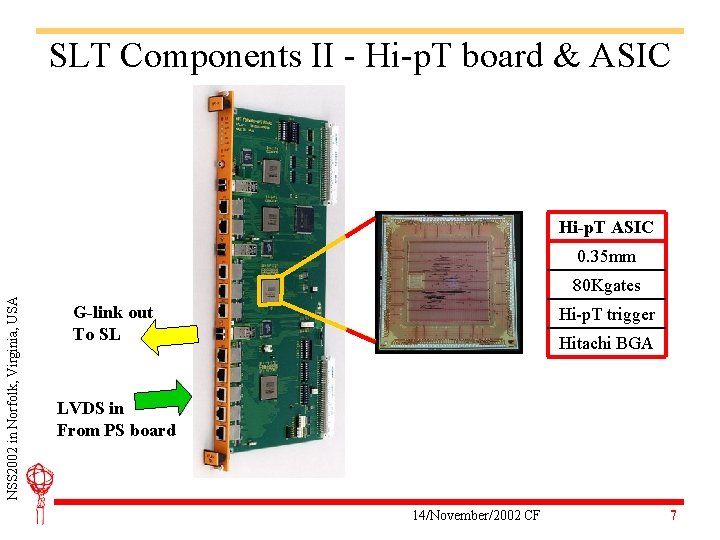

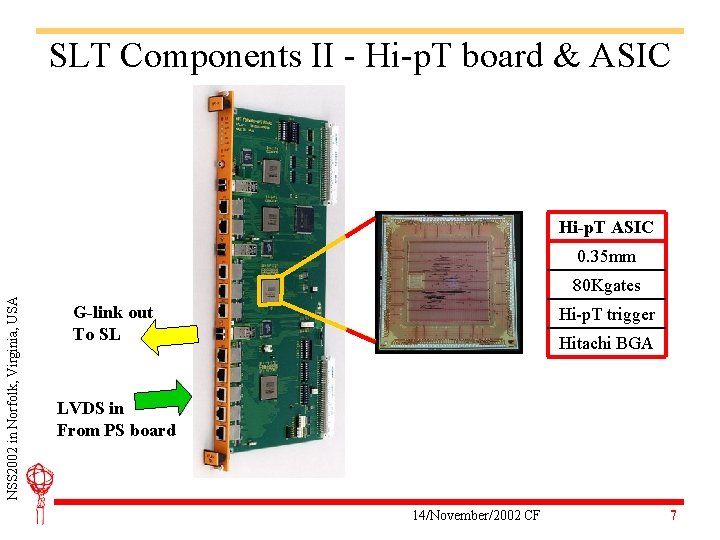

SLT Components II - Hi-p. T board & ASIC Hi-p. T ASIC 0. 35 mm NSS 2002 in Norfolk, Virginia, USA 80 Kgates G-link out To SL Hi-p. T trigger Hitachi BGA LVDS in From PS board 14/November/2002 CF 7

SLT Components III – Readout System Star Switch (SSW) LVDS in From PS board (SLB) CPU FIFO NSS 2002 in Norfolk, Virginia, USA SDRAM G-link in From SSW G-link out To ROD Read Out Driver (ROD) 14/November/2002 CF 8

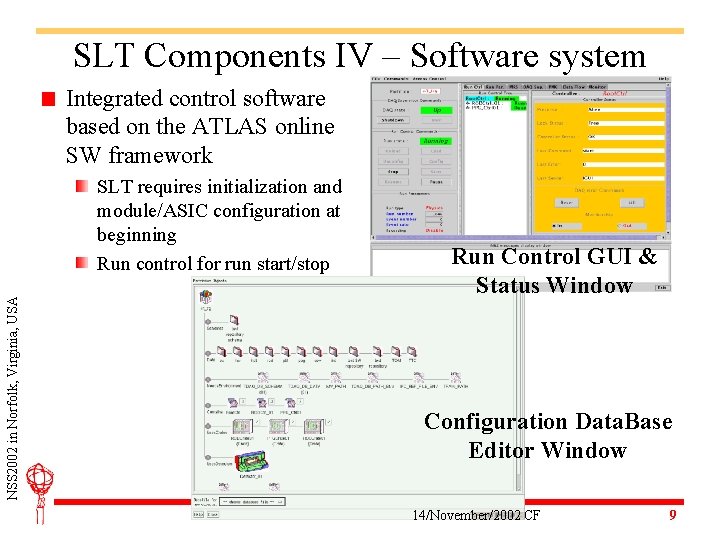

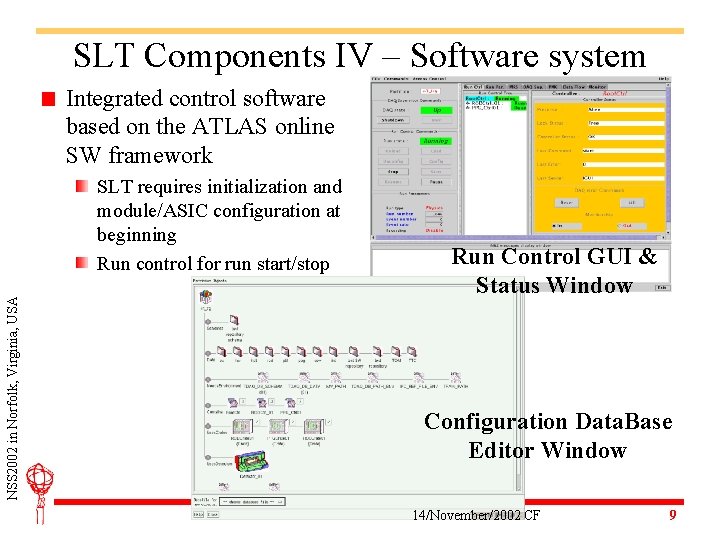

SLT Components IV – Software system Integrated control software based on the ATLAS online SW framework NSS 2002 in Norfolk, Virginia, USA SLT requires initialization and module/ASIC configuration at beginning Run control for run start/stop Run Control GUI & Status Window Configuration Data. Base Editor Window 14/November/2002 CF 9

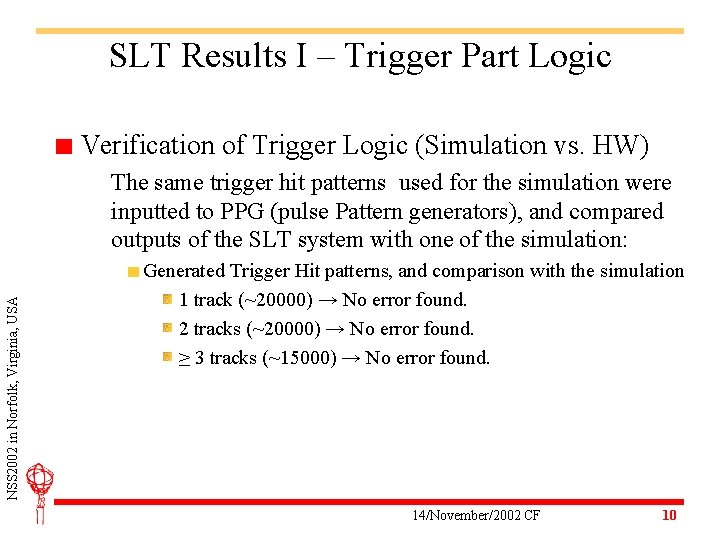

SLT Results I – Trigger Part Logic Verification of Trigger Logic (Simulation vs. HW) NSS 2002 in Norfolk, Virginia, USA The same trigger hit patterns used for the simulation were inputted to PPG (pulse Pattern generators), and compared outputs of the SLT system with one of the simulation: Generated Trigger Hit patterns, and comparison with the simulation 1 track (~20000) → No error found. 2 tracks (~20000) → No error found. ≥ 3 tracks (~15000) → No error found. 14/November/2002 CF 10

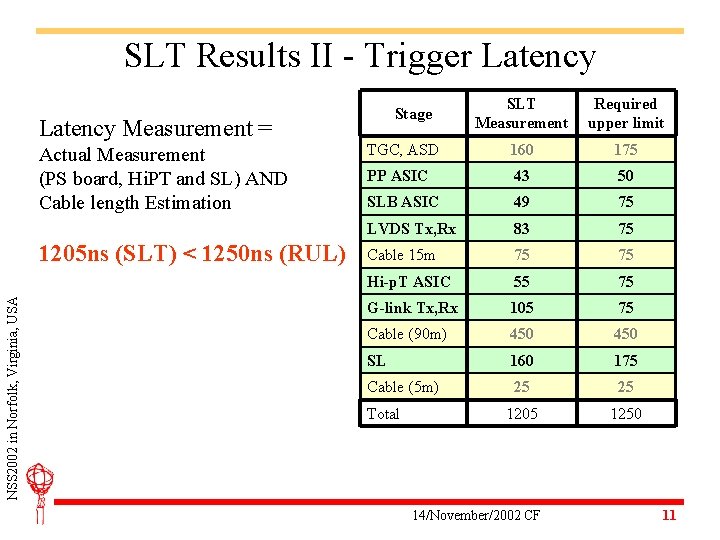

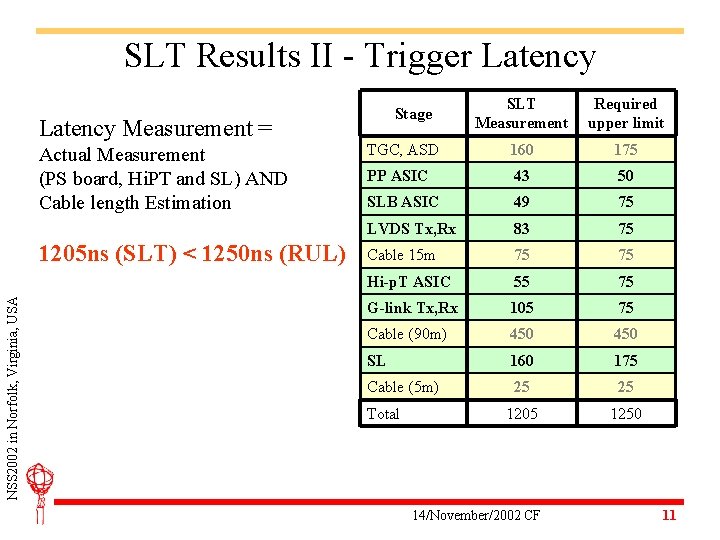

SLT Results II - Trigger Latency Measurement = Actual Measurement (PS board, Hi. PT and SL) AND Cable length Estimation NSS 2002 in Norfolk, Virginia, USA 1205 ns (SLT) < 1250 ns (RUL) SLT Measurement Required upper limit TGC, ASD 160 175 PP ASIC 43 50 SLB ASIC 49 75 LVDS Tx, Rx 83 75 Cable 15 m 75 75 Hi-p. T ASIC 55 75 G-link Tx, Rx 105 75 Cable (90 m) 450 SL 160 175 Cable (5 m) 25 25 1205 1250 Stage Total 14/November/2002 CF 11

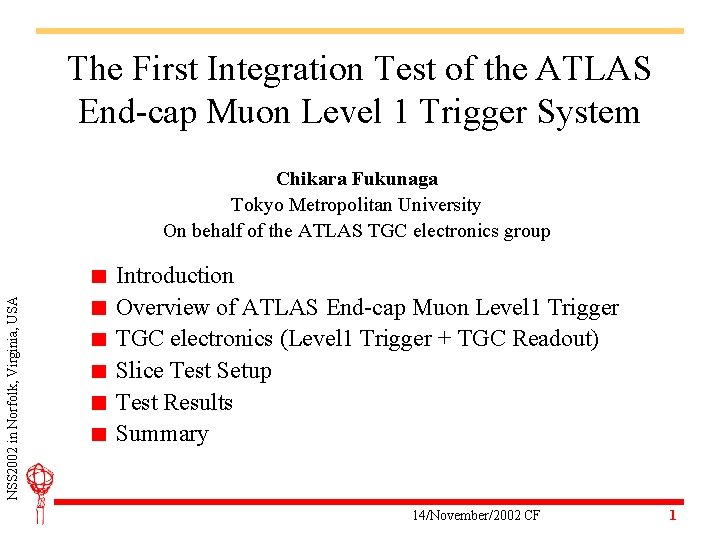

NSS 2002 in Norfolk, Virginia, USA SLT Results III – Readout test Since SSW has been delivered in this summer, full test of PS-board→SSW→ROD has not been done. PS-board→PT 4(SSW alternative)→ROD has been checked in 2001 with long run tests. 400 clock counts (40 MHz) can be used for SLB or SSW readout if Level 1 rate is 100 KHz. SLB uses 218 counts. If TGC occupancy is 4%, SSW needs 160 counts. SSW will not be bottle neck. (TGC Occupancy ~ 1%) 14/November/2002 CF 12

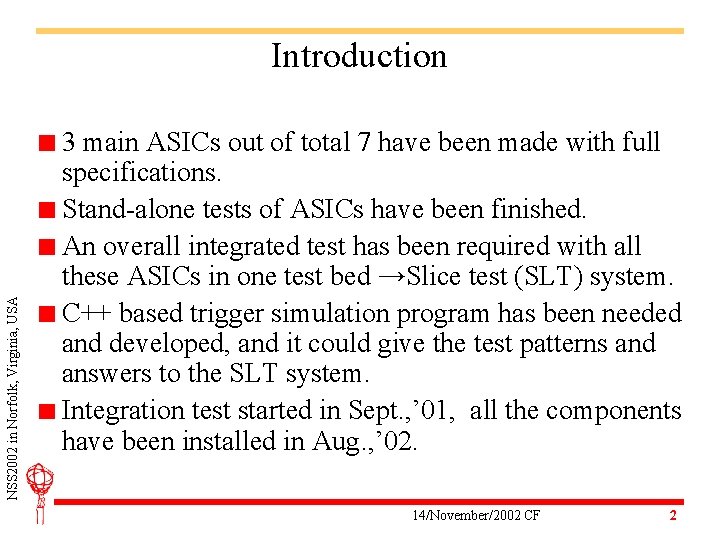

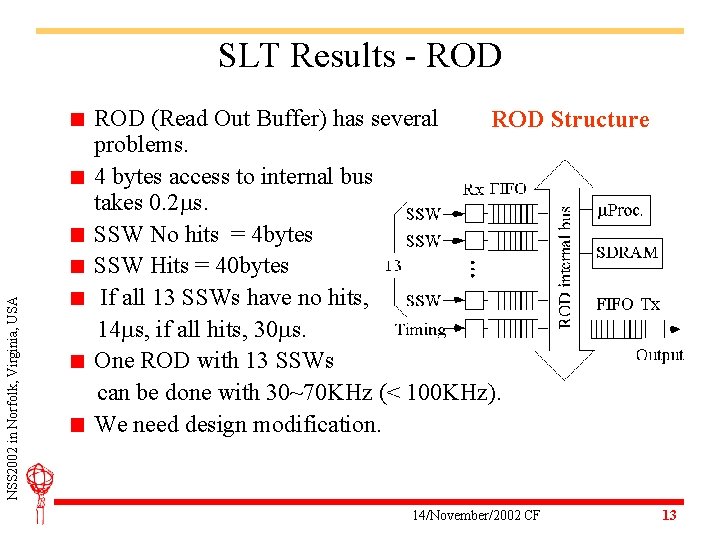

NSS 2002 in Norfolk, Virginia, USA SLT Results - ROD (Read Out Buffer) has several ROD Structure problems. 4 bytes access to internal bus takes 0. 2 ms. SSW No hits = 4 bytes SSW Hits = 40 bytes If all 13 SSWs have no hits, 14 ms, if all hits, 30 ms. One ROD with 13 SSWs can be done with 30~70 KHz (< 100 KHz). We need design modification. 14/November/2002 CF 13

Summary Block Trigger Part NSS 2002 in Norfolk, Virginia, USA Readout Part Software Test Integration@40 MHz Latency Integration Readout Rate SSW Readout Rate ROD Online DAQ Trigger Logic Simulation Control System HSC-CCI Status Done, pattern check OK OK 1205 ms<1250 ms Not yet, stand-alone OK 100 KHz 30~70 KHz OK, will be used for beam Need improvements OK for config. ASIC 14/November/2002 CF 14

Forward integration and backward integration

Forward integration and backward integration Backwards intergration

Backwards intergration Simultaneous integration meaning

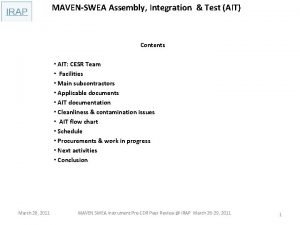

Simultaneous integration meaning Swea parts

Swea parts Integration test plan

Integration test plan Uatof

Uatof Hình ảnh bộ gõ cơ thể búng tay

Hình ảnh bộ gõ cơ thể búng tay Slidetodoc

Slidetodoc Bổ thể

Bổ thể Tỉ lệ cơ thể trẻ em

Tỉ lệ cơ thể trẻ em Voi kéo gỗ như thế nào

Voi kéo gỗ như thế nào Tư thế worms-breton

Tư thế worms-breton Chúa yêu trần thế

Chúa yêu trần thế Các môn thể thao bắt đầu bằng tiếng đua

Các môn thể thao bắt đầu bằng tiếng đua Thế nào là hệ số cao nhất

Thế nào là hệ số cao nhất