Techniques for Fast Packet Buffers Sundar Iyer Nick

Techniques for Fast Packet Buffers Sundar Iyer, Nick Mc. Keown (sundaes, nickm)@stanford. edu Departments of Electrical Engineering & Computer Science, Stanford University http: //klamath. stanford. edu

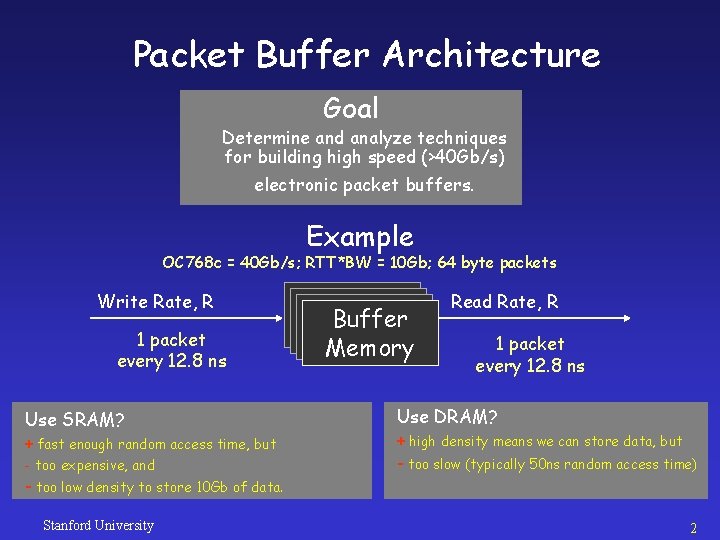

Packet Buffer Architecture Goal Determine and analyze techniques for building high speed (>40 Gb/s) electronic packet buffers. Example OC 768 c = 40 Gb/s; RTT*BW = 10 Gb; 64 byte packets Write Rate, R 1 packet every 12. 8 ns Use SRAM? + fast enough random access time, but - too expensive, and Buffer Memory Read Rate, R 1 packet every 12. 8 ns Use DRAM? + high density means we can store data, but - too slow (typically 50 ns random access time) - too low density to store 10 Gb of data. Stanford University 2

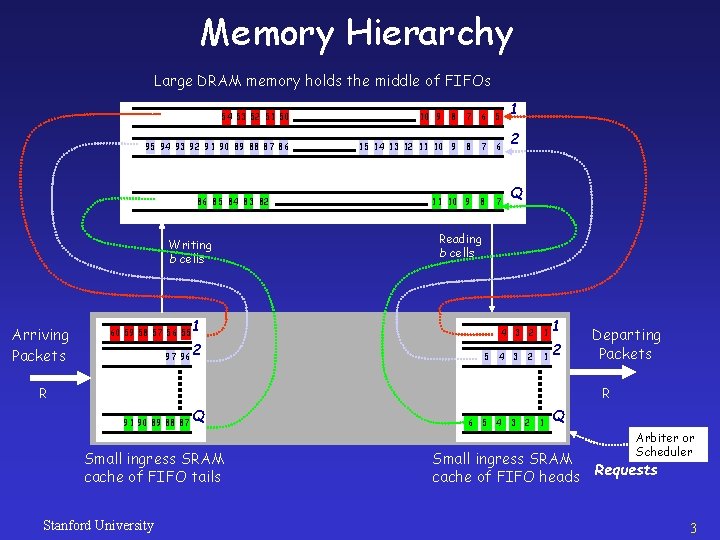

Memory Hierarchy Large DRAM memory holds the middle of FIFOs 54 53 52 51 50 95 94 93 92 91 90 89 88 87 86 86 85 84 83 82 Writing b cells Arriving Packets 60 59 58 57 56 55 1 97 96 2 10 9 8 7 6 5 15 14 13 12 11 10 9 8 7 6 11 10 9 8 7 1 2 Q Reading b cells 5 4 3 2 1 1 2 4 3 R Departing Packets R 91 90 89 88 87 Q Small ingress SRAM cache of FIFO tails Stanford University 6 5 4 3 2 1 Q Arbiter or Scheduler Small ingress SRAM cache of FIFO heads Requests 3

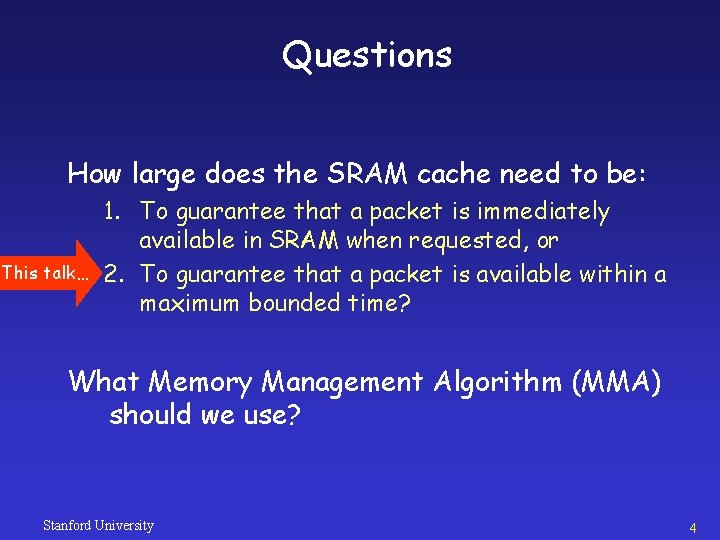

Questions How large does the SRAM cache need to be: This talk… 1. To guarantee that a packet is immediately available in SRAM when requested, or 2. To guarantee that a packet is available within a maximum bounded time? What Memory Management Algorithm (MMA) should we use? Stanford University 4

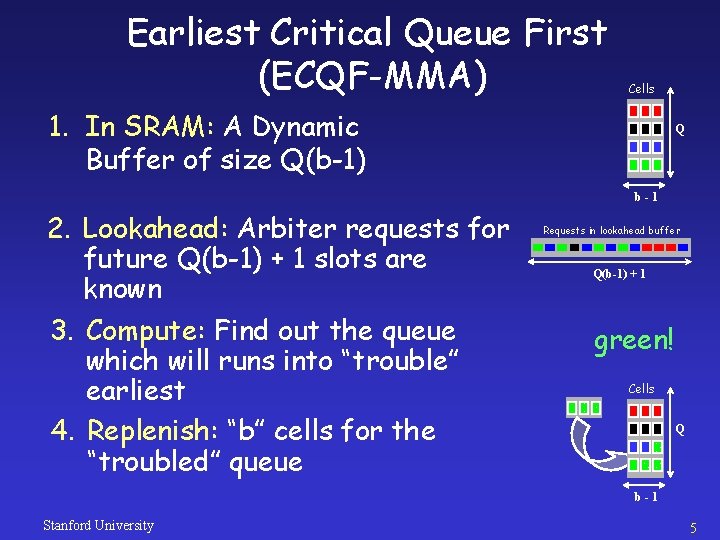

Earliest Critical Queue First (ECQF-MMA) Cells 1. In SRAM: A Dynamic Buffer of size Q(b-1) Q b-1 2. Lookahead: Arbiter requests for future Q(b-1) + 1 slots are known 3. Compute: Find out the queue which will runs into “trouble” earliest 4. Replenish: “b” cells for the “troubled” queue Requests in lookahead buffer Q(b-1) + 1 green! Cells Q b-1 Stanford University 5

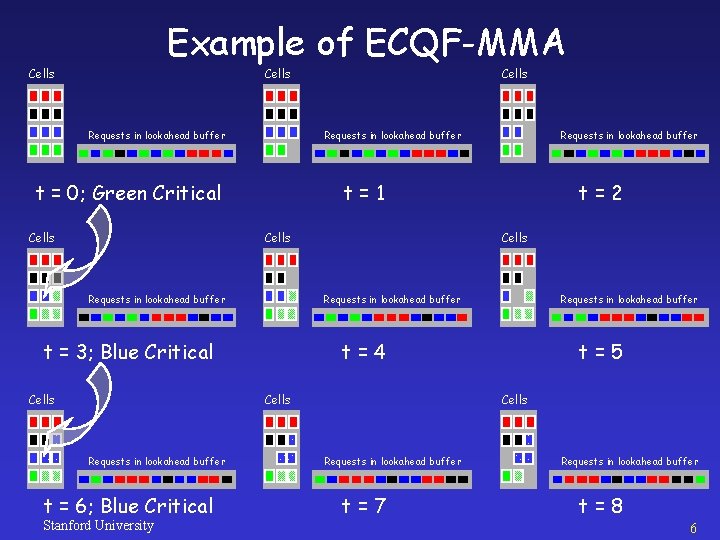

Example of ECQF-MMA Cells Requests in lookahead buffer t = 0; Green Critical Cells t=1 Cells Requests in lookahead buffer Cells t = 6; Blue Critical Stanford University Requests in lookahead buffer t=4 t=5 Cells Requests in lookahead buffer t=2 Requests in lookahead buffer t = 3; Blue Critical Cells Requests in lookahead buffer t=7 Requests in lookahead buffer t=8 6

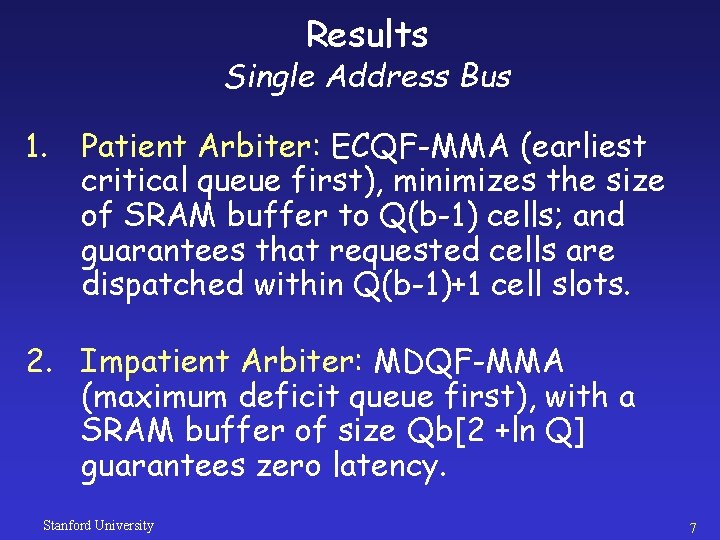

Results Single Address Bus 1. Patient Arbiter: ECQF-MMA (earliest critical queue first), minimizes the size of SRAM buffer to Q(b-1) cells; and guarantees that requested cells are dispatched within Q(b-1)+1 cell slots. 2. Impatient Arbiter: MDQF-MMA (maximum deficit queue first), with a SRAM buffer of size Qb[2 +ln Q] guarantees zero latency. Stanford University 7

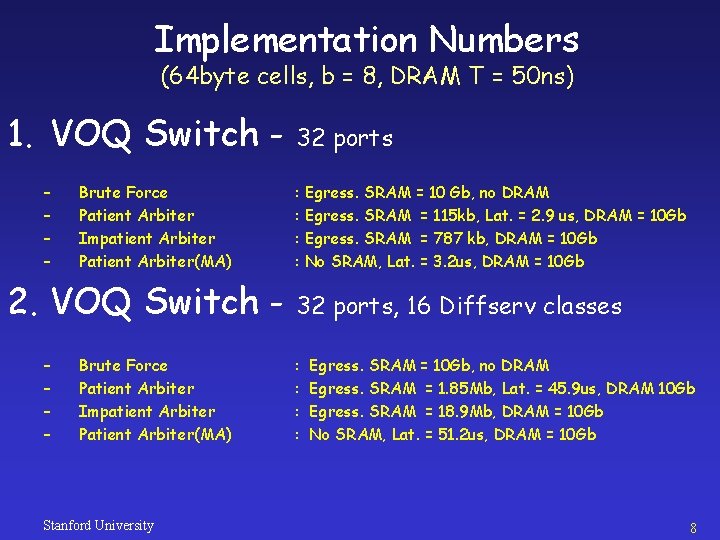

Implementation Numbers (64 byte cells, b = 8, DRAM T = 50 ns) 1. VOQ Switch – – Brute Force Patient Arbiter Impatient Arbiter Patient Arbiter(MA) 2. VOQ Switch – – Brute Force Patient Arbiter Impatient Arbiter Patient Arbiter(MA) Stanford University 32 ports : Egress. SRAM = 10 Gb, no DRAM : Egress. SRAM = 115 kb, Lat. = 2. 9 us, DRAM = 10 Gb : Egress. SRAM = 787 kb, DRAM = 10 Gb : No SRAM, Lat. = 3. 2 us, DRAM = 10 Gb 32 ports, 16 Diffserv classes : : Egress. SRAM = 10 Gb, no DRAM Egress. SRAM = 1. 85 Mb, Lat. = 45. 9 us, DRAM 10 Gb Egress. SRAM = 18. 9 Mb, DRAM = 10 Gb No SRAM, Lat. = 51. 2 us, DRAM = 10 Gb 8

- Slides: 8