Taming the Constraints Beast Auto Cons Manjeri Krishnan

Taming the Constraints Beast: Auto. Cons Manjeri Krishnan Brian Borchers Texas Instruments, Inc. 1

Agenda Ø Background Ø Auto. Cons Overview Ø Basic Concepts Ø Some Illustrations Ø Helper Scripts Ø Conclusion 2

“Necessity is the Mother of Invention” Ø Necessity § § § § Intensely manual effort of developing timing constraints Increasing SOC complexity Decreasing schedules and resources Differing requirements of analysis and optimization teams Differing requirements of chip and subchip teams Need for speedy and error-free constraints development Need for efficient management and maintenance of large amounts of constraints Ø Invention § Auto. Cons 3

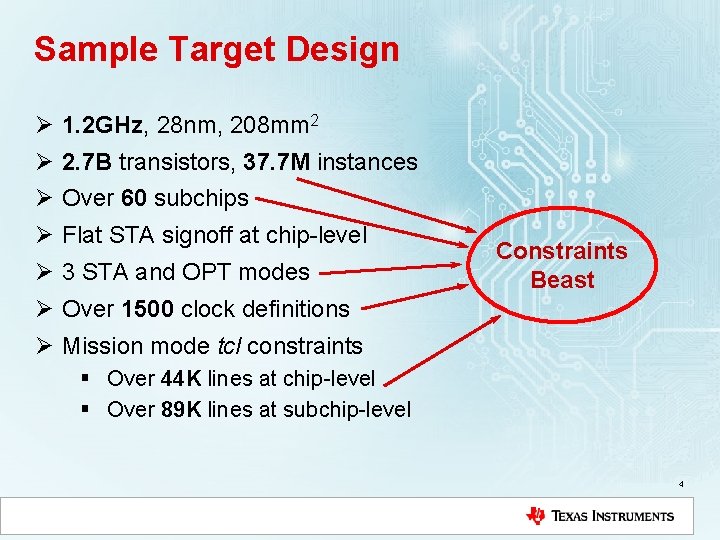

Sample Target Design Ø 1. 2 GHz, 28 nm, 208 mm 2 Ø 2. 7 B transistors, 37. 7 M instances Ø Over 60 subchips Ø Flat STA signoff at chip-level Ø 3 STA and OPT modes Constraints Beast Ø Over 1500 clock definitions Ø Mission mode tcl constraints § Over 44 K lines at chip-level § Over 89 K lines at subchip-level 4

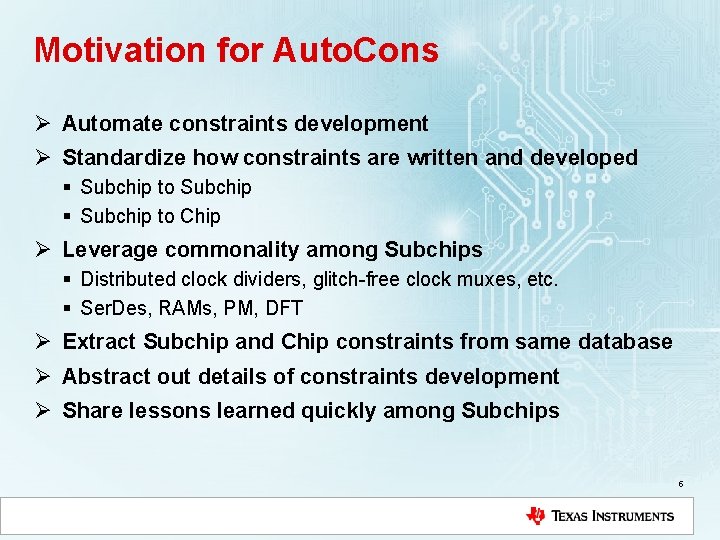

Motivation for Auto. Cons Ø Automate constraints development Ø Standardize how constraints are written and developed § Subchip to Subchip § Subchip to Chip Ø Leverage commonality among Subchips § Distributed clock dividers, glitch-free clock muxes, etc. § Ser. Des, RAMs, PM, DFT Ø Extract Subchip and Chip constraints from same database Ø Abstract out details of constraints development Ø Share lessons learned quickly among Subchips 5

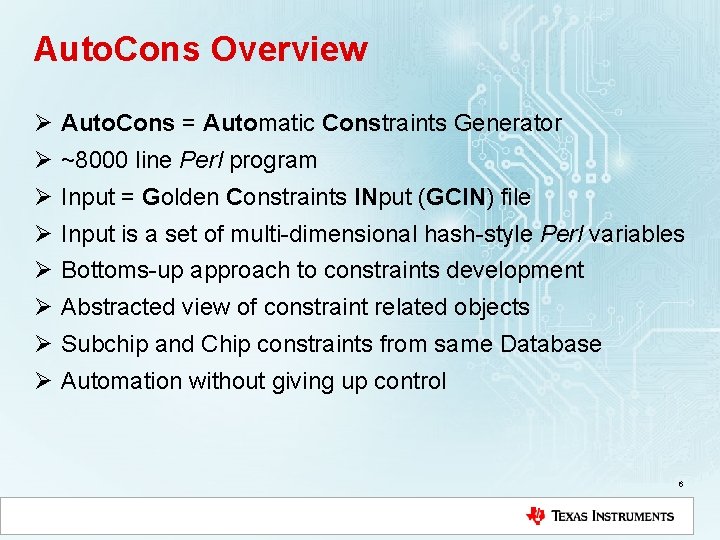

Auto. Cons Overview Ø Auto. Cons = Automatic Constraints Generator Ø ~8000 line Perl program Ø Input = Golden Constraints INput (GCIN) file Ø Input is a set of multi-dimensional hash-style Perl variables Ø Bottoms-up approach to constraints development Ø Abstracted view of constraint related objects Ø Subchip and Chip constraints from same Database Ø Automation without giving up control 6

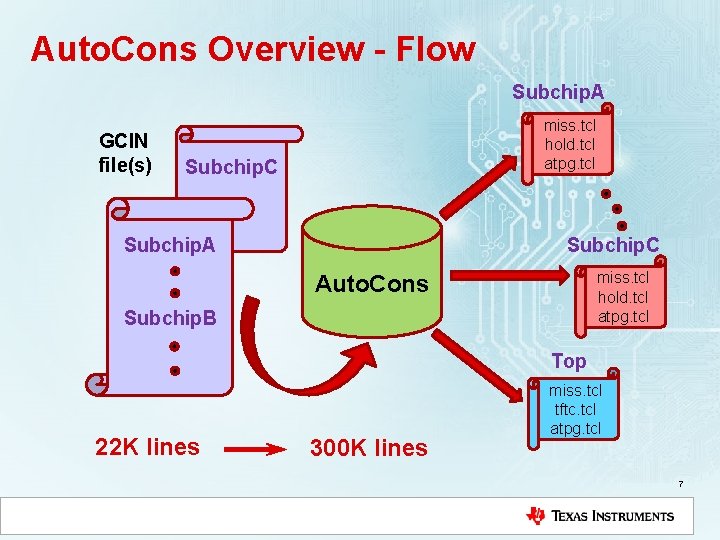

Auto. Cons Overview - Flow Subchip. A GCIN file(s) miss. tcl hold. tcl atpg. tcl Subchip. C Subchip. A miss. tcl hold. tcl atpg. tcl Auto. Cons Subchip. B Top 22 K lines 300 K lines miss. tcl tftc. tcl atpg. tcl 7

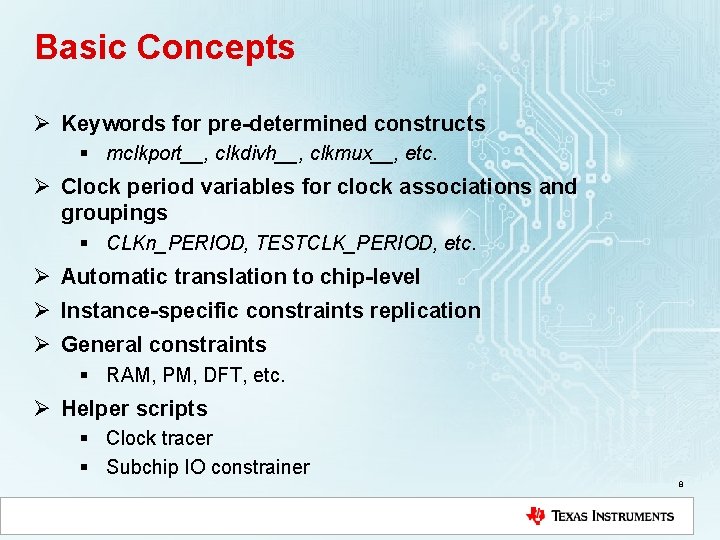

Basic Concepts Ø Keywords for pre-determined constructs § mclkport__, clkdivh__, clkmux__, etc. Ø Clock period variables for clock associations and groupings § CLKn_PERIOD, TESTCLK_PERIOD, etc. Ø Automatic translation to chip-level Ø Instance-specific constraints replication Ø General constraints § RAM, PM, DFT, etc. Ø Helper scripts § Clock tracer § Subchip IO constrainer 8

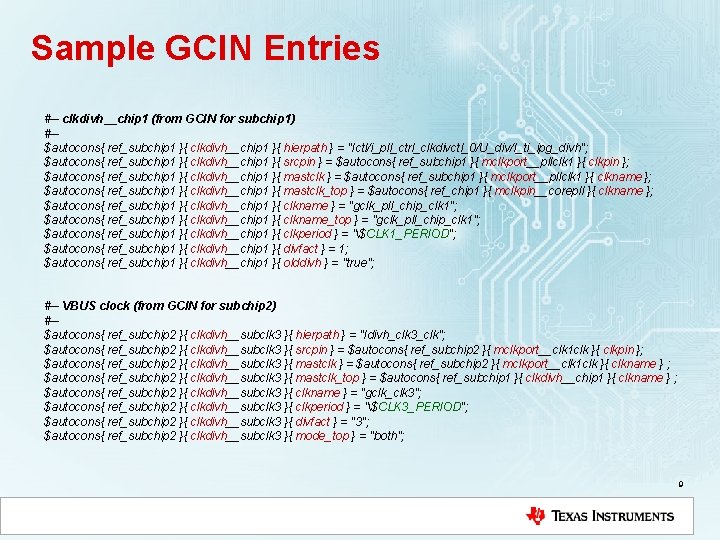

Sample GCIN Entries #-- clkdivh__chip 1 (from GCIN for subchip 1) #-$autocons{ ref_subchip 1 }{ clkdivh__chip 1 }{ hierpath } = "Ictl/i_pll_ctrl_clkdivctl_0/U_div/I_ti_ipg_divh"; $autocons{ ref_subchip 1 }{ clkdivh__chip 1 }{ srcpin } = $autocons{ ref_subchip 1 }{ mclkport__pllclk 1 }{ clkpin }; $autocons{ ref_subchip 1 }{ clkdivh__chip 1 }{ mastclk } = $autocons{ ref_subchip 1 }{ mclkport__pllclk 1 }{ clkname }; $autocons{ ref_subchip 1 }{ clkdivh__chip 1 }{ mastclk_top } = $autocons{ ref_chip 1 }{ mclkpin__corepll }{ clkname }; $autocons{ ref_subchip 1 }{ clkdivh__chip 1 }{ clkname } = "gclk_pll_chip_clk 1"; $autocons{ ref_subchip 1 }{ clkdivh__chip 1 }{ clkname_top } = "gclk_pll_chip_clk 1"; $autocons{ ref_subchip 1 }{ clkdivh__chip 1 }{ clkperiod } = "$CLK 1_PERIOD"; $autocons{ ref_subchip 1 }{ clkdivh__chip 1 }{ divfact } = 1; $autocons{ ref_subchip 1 }{ clkdivh__chip 1 }{ olddivh } = "true"; #-- VBUS clock (from GCIN for subchip 2) #-$autocons{ ref_subchip 2 }{ clkdivh__subclk 3 }{ hierpath } = "Idivh_clk 3_clk"; $autocons{ ref_subchip 2 }{ clkdivh__subclk 3 }{ srcpin } = $autocons{ ref_subchip 2 }{ mclkport__clk 1 clk }{ clkpin }; $autocons{ ref_subchip 2 }{ clkdivh__subclk 3 }{ mastclk } = $autocons{ ref_subchip 2 }{ mclkport__clk 1 clk }{ clkname } ; $autocons{ ref_subchip 2 }{ clkdivh__subclk 3 }{ mastclk_top } = $autocons{ ref_subchip 1 }{ clkdivh__chip 1 }{ clkname } ; $autocons{ ref_subchip 2 }{ clkdivh__subclk 3 }{ clkname } = "gclk_clk 3"; $autocons{ ref_subchip 2 }{ clkdivh__subclk 3 }{ clkperiod } = "$CLK 3_PERIOD"; $autocons{ ref_subchip 2 }{ clkdivh__subclk 3 }{ divfact } = "3"; $autocons{ ref_subchip 2 }{ clkdivh__subclk 3 }{ mode_top } = "both"; 9

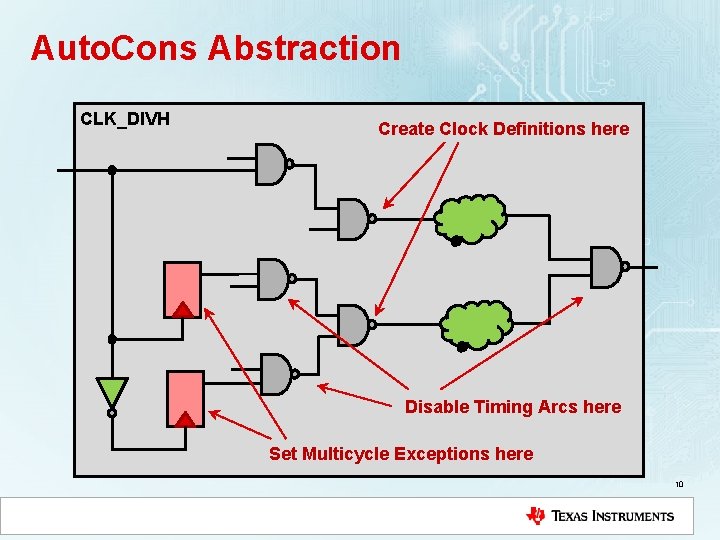

Auto. Cons Abstraction CLK_DIVH Create Clock Definitions here Disable Timing Arcs here Set Multicycle Exceptions here 10

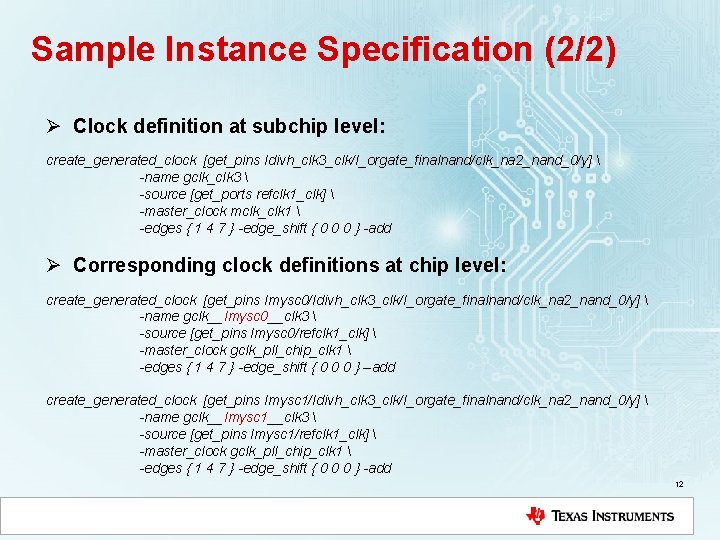

Sample Instance Specification (1/2) Ø Two instances of ref_subchip 3: § Imysc 0 § Imysc 1 Ø Specification in GCIN for subchip 3: $autocons{ ref_subchip 3 }{ instances } = "Imysc 0, Imysc 1"; ; #-- comma separated list of instances ; #-- (for use at chip-level) Ø Clock defined at ref_subchip 3 level: § gclk_myclk 1_clk Ø Corresponding clocks defined at chip level: § gclk__Imysc 0__myclk 1_clk § gclk__Imysc 1__myclk 1_clk 11

Sample Instance Specification (2/2) Ø Clock definition at subchip level: create_generated_clock [get_pins Idivh_clk 3_clk/I_orgate_finalnand/clk_na 2_nand_0/y] -name gclk_clk 3 -source [get_ports refclk 1_clk] -master_clock mclk_clk 1 -edges { 1 4 7 } -edge_shift { 0 0 0 } -add Ø Corresponding clock definitions at chip level: create_generated_clock [get_pins Imysc 0/Idivh_clk 3_clk/I_orgate_finalnand/clk_na 2_nand_0/y] -name gclk__Imysc 0__clk 3 -source [get_pins Imysc 0/refclk 1_clk] -master_clock gclk_pll_chip_clk 1 -edges { 1 4 7 } -edge_shift { 0 0 0 } –add create_generated_clock [get_pins Imysc 1/Idivh_clk 3_clk/I_orgate_finalnand/clk_na 2_nand_0/y] -name gclk__Imysc 1__clk 3 -source [get_pins Imysc 1/refclk 1_clk] -master_clock gclk_pll_chip_clk 1 -edges { 1 4 7 } -edge_shift { 0 0 0 } -add 12

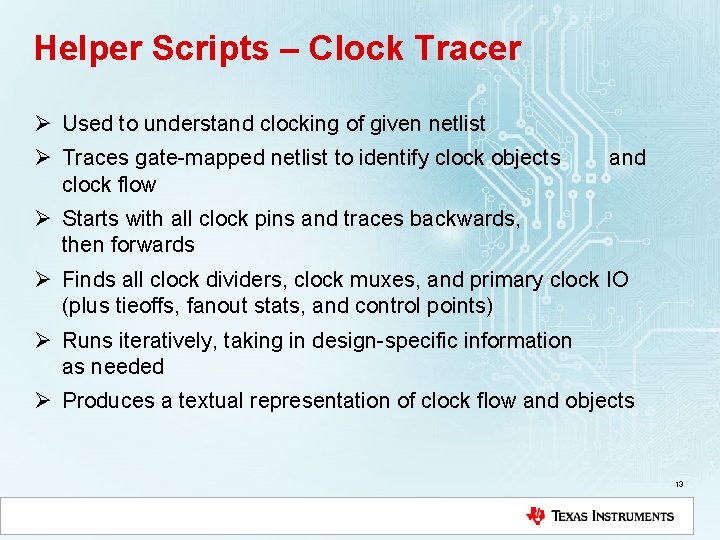

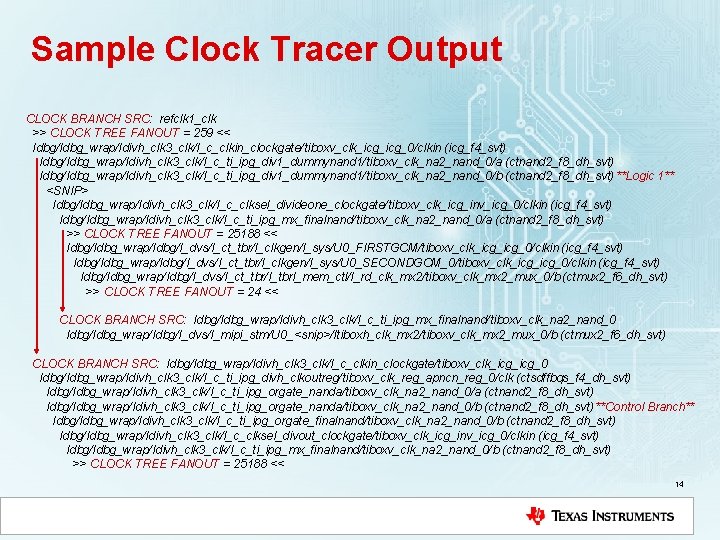

Helper Scripts – Clock Tracer Ø Used to understand clocking of given netlist Ø Traces gate-mapped netlist to identify clock objects and clock flow Ø Starts with all clock pins and traces backwards, then forwards Ø Finds all clock dividers, clock muxes, and primary clock IO (plus tieoffs, fanout stats, and control points) Ø Runs iteratively, taking in design-specific information as needed Ø Produces a textual representation of clock flow and objects 13

Sample Clock Tracer Output CLOCK BRANCH SRC: refclk 1_clk >> CLOCK TREE FANOUT = 259 << Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_clkin_clockgate/tiboxv_clk_icg_0/clkin (icg_f 4_svt) Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_ti_ipg_div 1_dummynand 1/tiboxv_clk_na 2_nand_0/a (ctnand 2_f 8_dh_svt) Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_ti_ipg_div 1_dummynand 1/tiboxv_clk_na 2_nand_0/b (ctnand 2_f 8_dh_svt) **Logic 1** <SNIP> Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_clksel_divideone_clockgate/tiboxv_clk_icg_inv_icg_0/clkin (icg_f 4_svt) Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_ti_ipg_mx_finalnand/tiboxv_clk_na 2_nand_0/a (ctnand 2_f 8_dh_svt) >> CLOCK TREE FANOUT = 25188 << Idbg/Idbg_wrap/Idbg/I_dvs/I_ct_tbr/I_clkgen/I_sys/U 0_FIRSTGCM/tiboxv_clk_icg_0/clkin (icg_f 4_svt) Idbg/Idbg_wrap/Idbg/I_dvs/I_ct_tbr/I_clkgen/I_sys/U 0_SECONDGCM_0/tiboxv_clk_icg_0/clkin (icg_f 4_svt) Idbg/Idbg_wrap/Idbg/I_dvs/I_ct_tbr/I_tbr. I_mem_ctl/I_rd_clk_mx 2/tiboxv_clk_mx 2_mux_0/b (ctmux 2_f 6_dh_svt) >> CLOCK TREE FANOUT = 24 << CLOCK BRANCH SRC: Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_ti_ipg_mx_finalnand/tiboxv_clk_na 2_nand_0 Idbg/Idbg_wrap/Idbg/I_dvs/I_mipi_stm/U 0_<snip>/Itiboxh_clk_mx 2/tiboxv_clk_mx 2_mux_0/b (ctmux 2_f 6_dh_svt) CLOCK BRANCH SRC: Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_clkin_clockgate/tiboxv_clk_icg_0 Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_ti_ipg_divh_clkoutreg/tiboxv_clk_reg_apncn_reg_0/clk (ctsdffbqs_f 4_dh_svt) Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_ti_ipg_orgate_nanda/tiboxv_clk_na 2_nand_0/a (ctnand 2_f 8_dh_svt) Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_ti_ipg_orgate_nanda/tiboxv_clk_na 2_nand_0/b (ctnand 2_f 8_dh_svt) **Control Branch** Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_ti_ipg_orgate_finalnand/tiboxv_clk_na 2_nand_0/b (ctnand 2_f 8_dh_svt) Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_clksel_divout_clockgate/tiboxv_clk_icg_inv_icg_0/clkin (icg_f 4_svt) Idbg/Idbg_wrap/Idivh_clk 3_clk/I_c_ti_ipg_mx_finalnand/tiboxv_clk_na 2_nand_0/b (ctnand 2_f 8_dh_svt) >> CLOCK TREE FANOUT = 25188 << 14

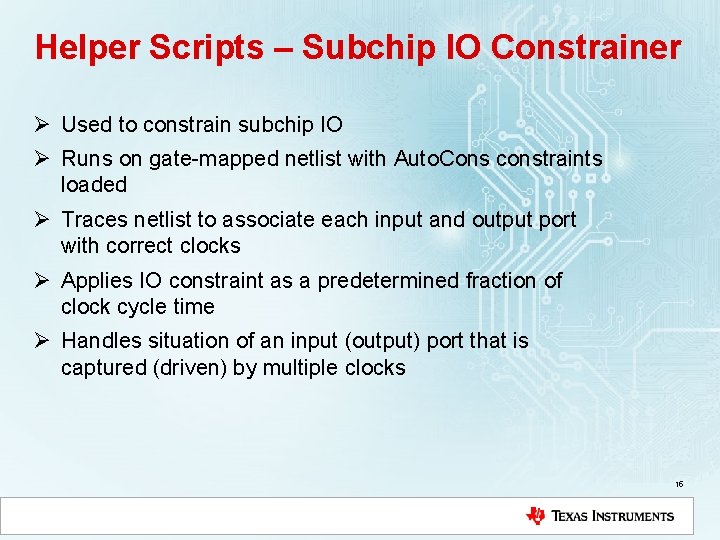

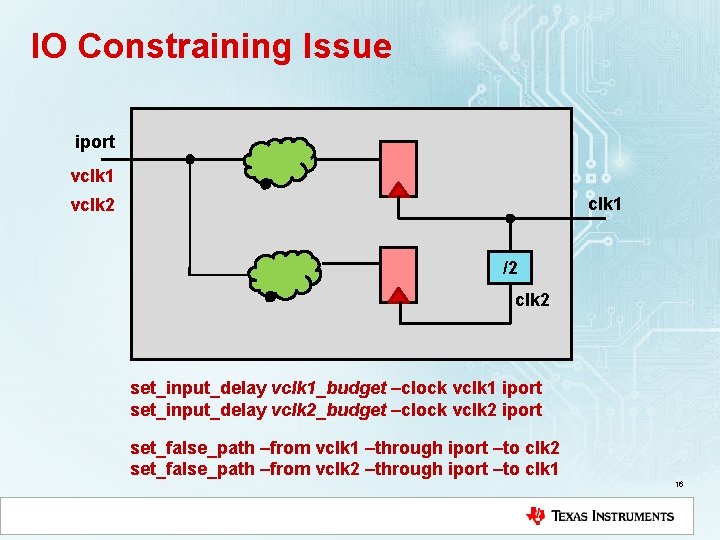

Helper Scripts – Subchip IO Constrainer Ø Used to constrain subchip IO Ø Runs on gate-mapped netlist with Auto. Cons constraints loaded Ø Traces netlist to associate each input and output port with correct clocks Ø Applies IO constraint as a predetermined fraction of clock cycle time Ø Handles situation of an input (output) port that is captured (driven) by multiple clocks 15

IO Constraining Issue iport vclk 1 vclk 2 /2 clk 2 set_input_delay vclk 1_budget –clock vclk 1 iport set_input_delay vclk 2_budget –clock vclk 2 iport set_false_path –from vclk 1 –through iport –to clk 2 set_false_path –from vclk 2 –through iport –to clk 1 16

Conclusion Ø Automation is the way forward Ø Auto. Cons is here to stay (4 successful SOCs so far) Ø Standardization is a key enabler for automation Ø Methodology changes to enable more automation 17

18

Backup Slides 19

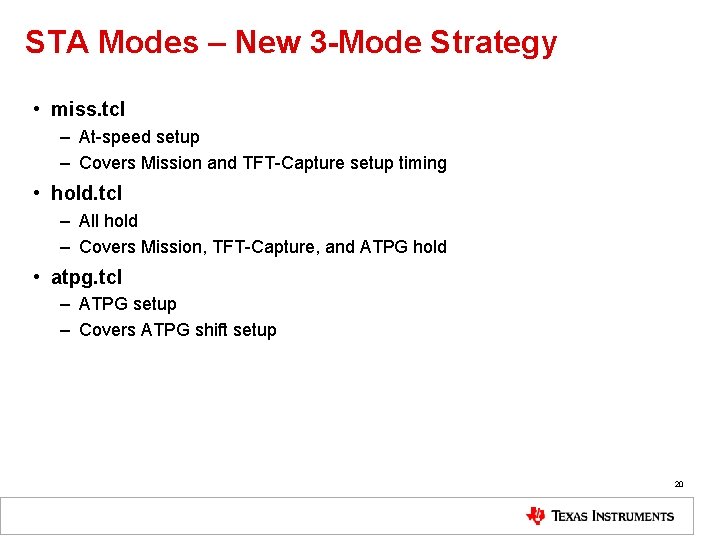

STA Modes – New 3 -Mode Strategy • miss. tcl – At-speed setup – Covers Mission and TFT-Capture setup timing • hold. tcl – All hold – Covers Mission, TFT-Capture, and ATPG hold • atpg. tcl – ATPG setup – Covers ATPG shift setup 20

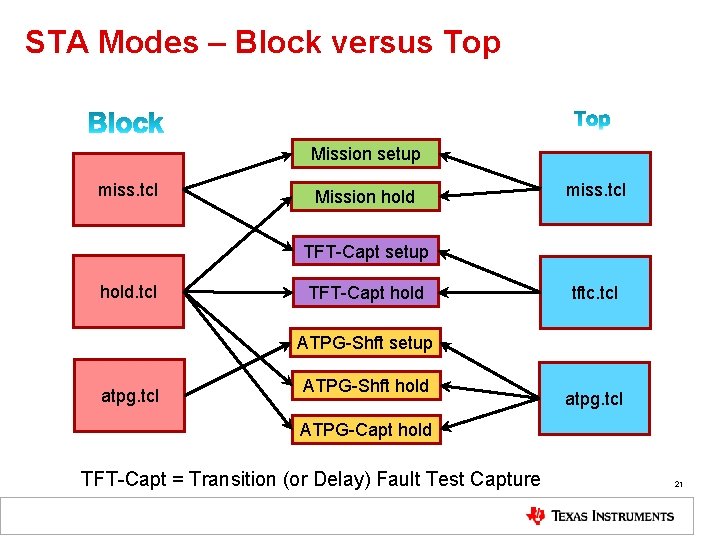

STA Modes – Block versus Top Mission setup miss. tcl Mission hold miss. tcl TFT-Capt setup hold. tcl TFT-Capt hold tftc. tcl ATPG-Shft setup atpg. tcl ATPG-Shft hold atpg. tcl ATPG-Capt hold TFT-Capt = Transition (or Delay) Fault Test Capture 21

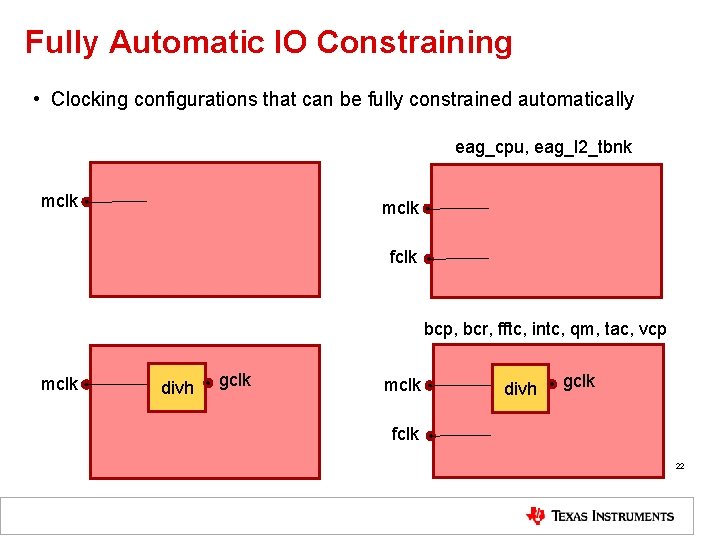

Fully Automatic IO Constraining • Clocking configurations that can be fully constrained automatically eag_cpu, eag_l 2_tbnk mclk fclk bcp, bcr, fftc, intc, qm, tac, vcp mclk divh gclk fclk 22

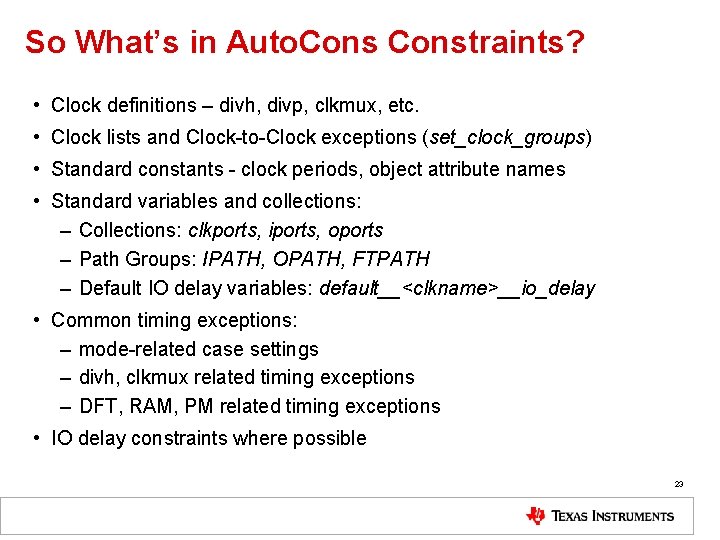

So What’s in Auto. Constraints? • Clock definitions – divh, divp, clkmux, etc. • Clock lists and Clock-to-Clock exceptions (set_clock_groups) • Standard constants - clock periods, object attribute names • Standard variables and collections: – Collections: clkports, iports, oports – Path Groups: IPATH, OPATH, FTPATH – Default IO delay variables: default__<clkname>__io_delay • Common timing exceptions: – mode-related case settings – divh, clkmux related timing exceptions – DFT, RAM, PM related timing exceptions • IO delay constraints where possible 23

- Slides: 23