Status of Tev IPMs June 20 2008 Andreas

- Slides: 13

Status of Tev IPMs June 20, 2008 Andreas Jansson

IPM Status • Since some time IPMs are now state driven, in the same way as flying wires. • Selected output is logged when data ready. • Automatic operation comes with new challenges. – Occasional synchronization problem causes data corruption. – This was easily rejected by eye when doing manual data taking. – Difficult to determine from data-logged end result whether raw data was valid or not. 12/28/2021 IPM status A. Jansson 2

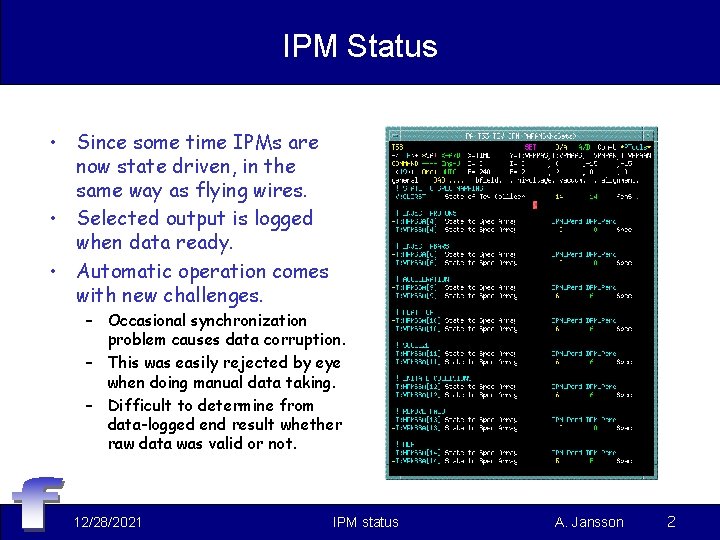

PSPEC settings 12/28/2021 IPM status A. Jansson 3

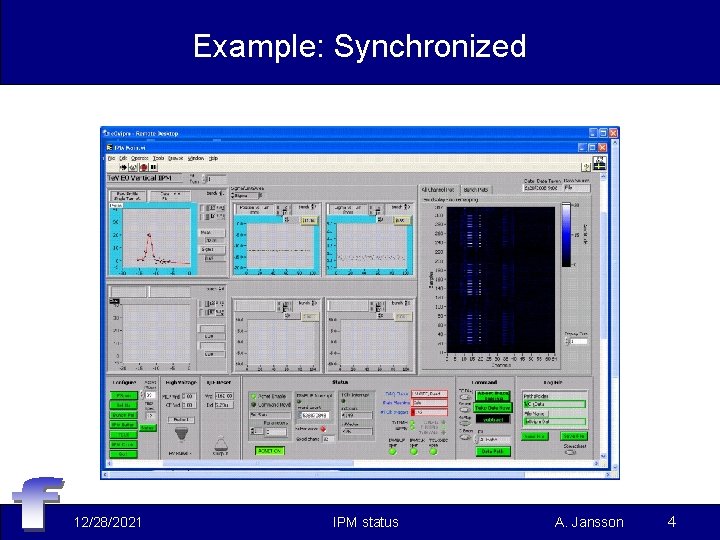

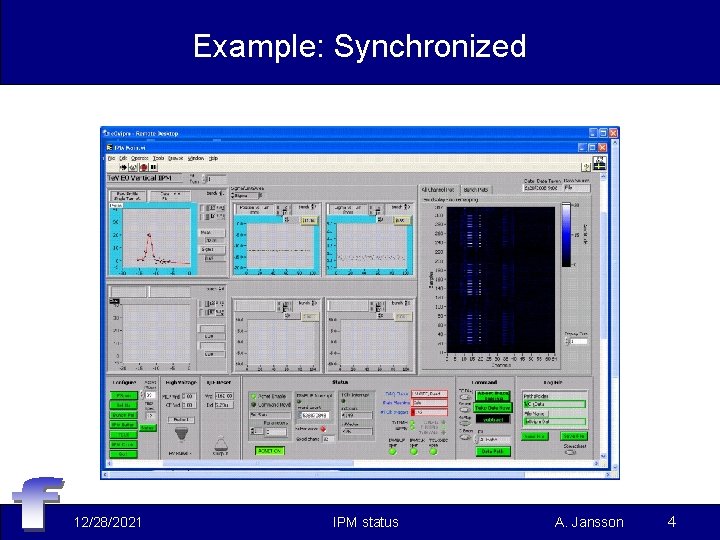

Example: Synchronized 12/28/2021 IPM status A. Jansson 4

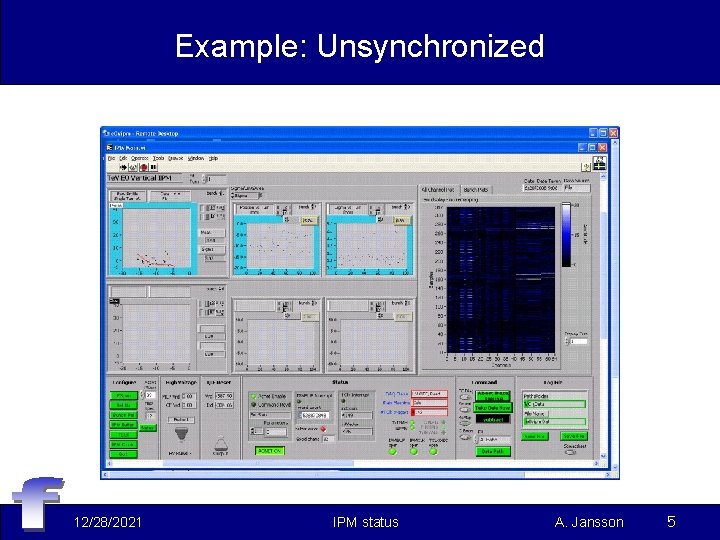

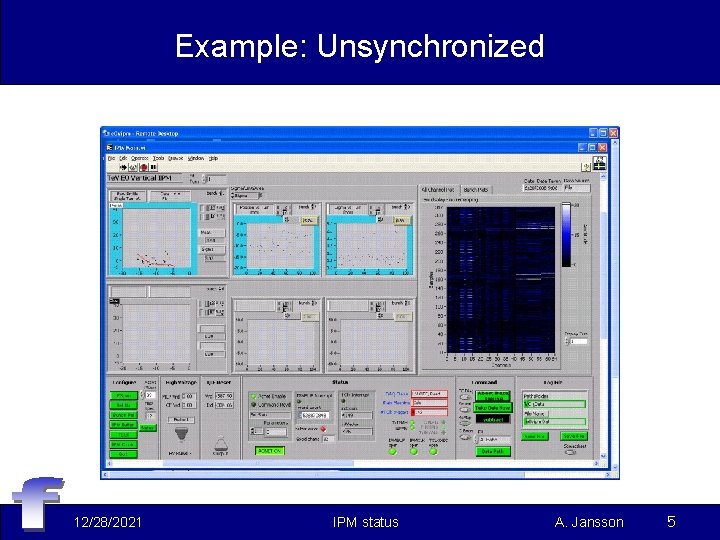

Example: Unsynchronized 12/28/2021 IPM status A. Jansson 5

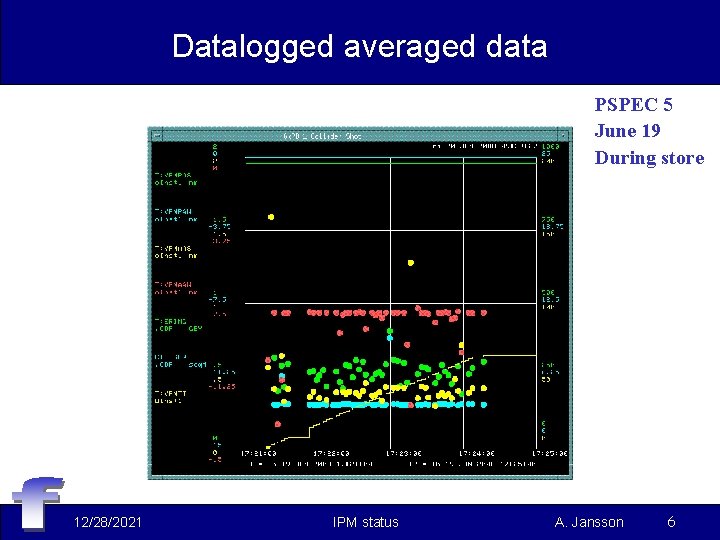

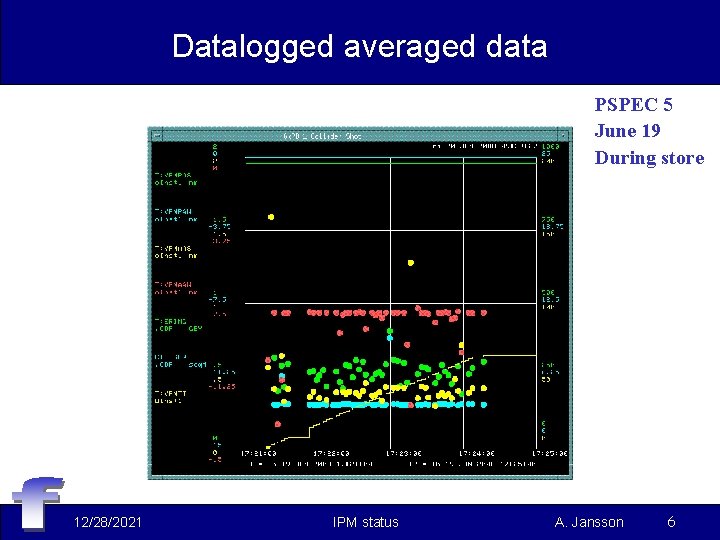

Datalogged averaged data PSPEC 5 June 19 During store 12/28/2021 IPM status A. Jansson 6

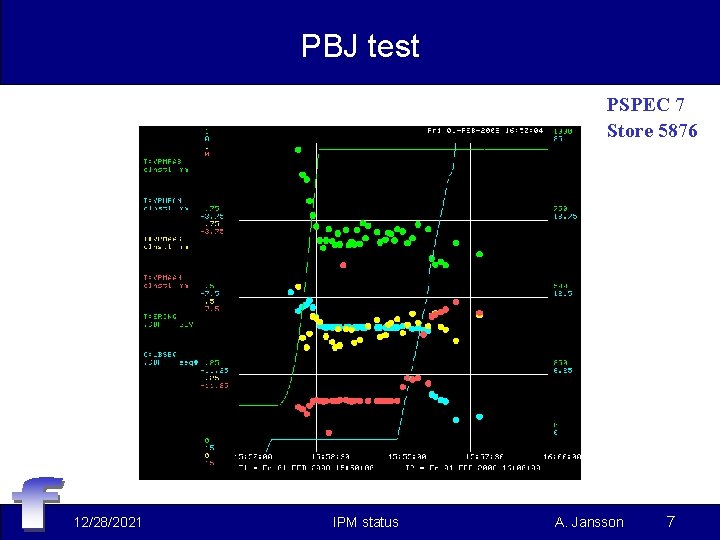

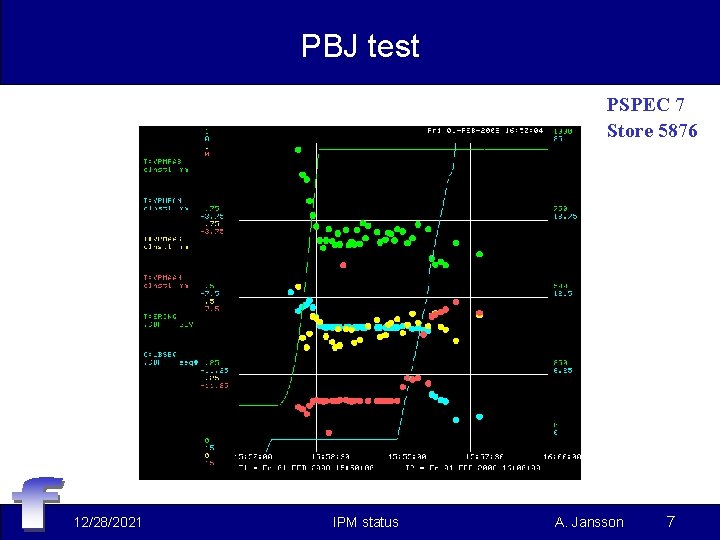

PBJ test PSPEC 7 Store 5876 12/28/2021 IPM status A. Jansson 7

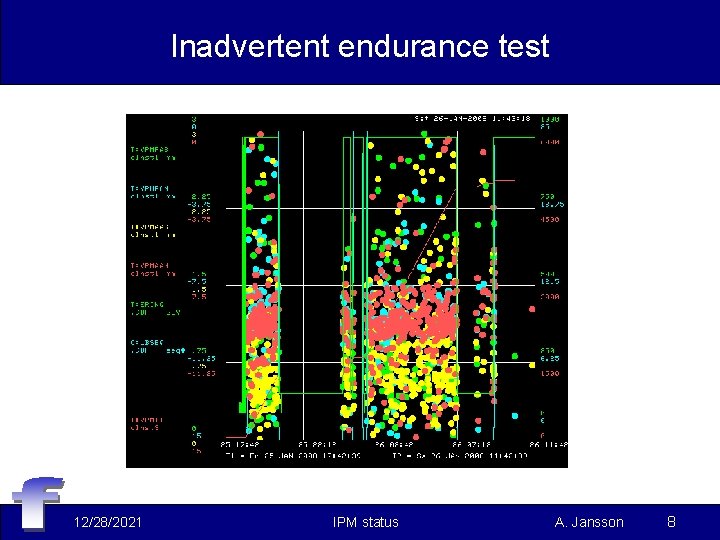

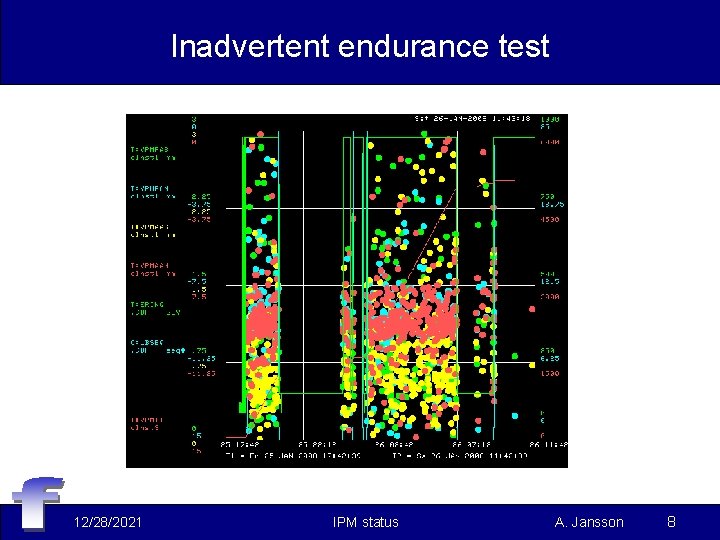

Inadvertent endurance test 12/28/2021 IPM status A. Jansson 8

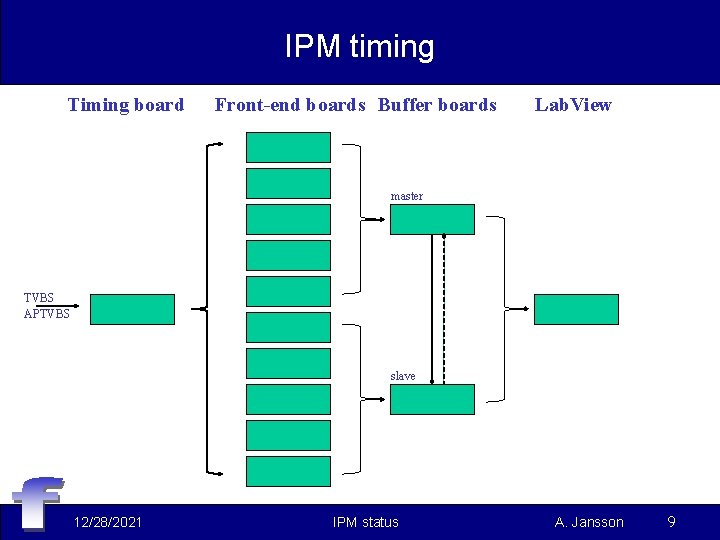

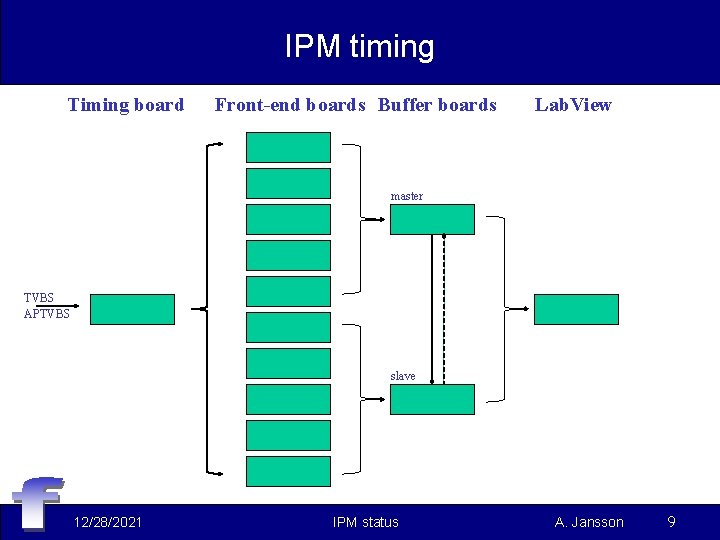

IPM timing Timing board Front-end boards Buffer boards Lab. View master TVBS APTVBS slave 12/28/2021 IPM status A. Jansson 9

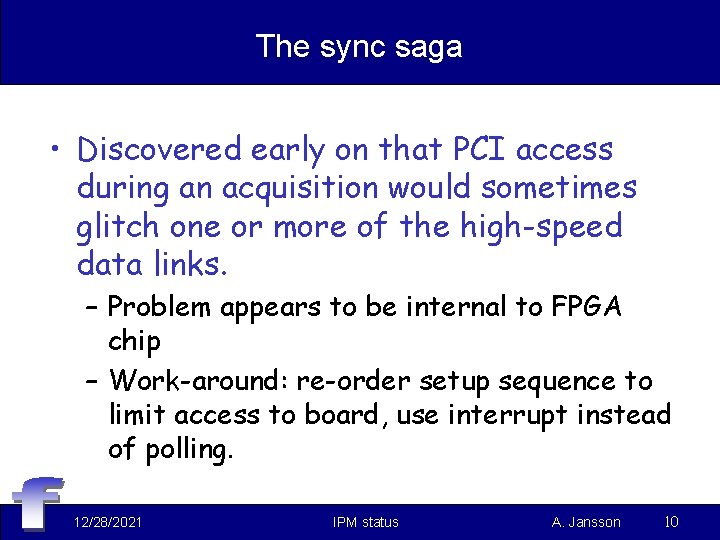

The sync saga • Discovered early on that PCI access during an acquisition would sometimes glitch one or more of the high-speed data links. – Problem appears to be internal to FPGA chip – Work-around: re-order setup sequence to limit access to board, use interrupt instead of polling. 12/28/2021 IPM status A. Jansson 10

Sync saga cont’d • But, de-synchronization still occurred relatively often, particularly for injection measurements – In original implementation, the entire chain was synchronized by a timing card reset just before an acquisition. – Added logic to allow links to resynchronize dynamically if needed while waiting for a trigger and during acquisition • Requires a “master link” • Difficult to implement between the two boards 12/28/2021 IPM status A. Jansson 11

Sync saga cont’d • Resync logic worked in teststand, but not in the Tevatron systems. – Main difference is that we used simulated TVBS in lab 5 teststand. • At this point, FY 08 omnibus budget came out, furloughs started and we lost our (PPD) FE board engineer to sunny Florida. • Buffer board engineer (CD) took over debugging of both boards, and we moved the teststand to FCC (closer and real TVBS available). – Discovered occasionally missing AA markers, and that FE board and buffer board treated this unspecified case differently, causing errors. 12/28/2021 IPM status A. Jansson 12

Sync saga cont’d • Also discovered “unexplained” PCI accesses during acquisition – Tried to have board ignore PCI requests during acquisition, but this caused total PC lock-up. – This problem is still being worked on. • In the meantime, released a intermediate full firmware version with fixes so far. – Error rate in test stand is now few per mil – Will test in Tevatron horizontal system. 12/28/2021 IPM status A. Jansson 13