Registers ECE 352 Digital System Fundamentals Registers 1

- Slides: 13

Registers ECE 352 Digital System Fundamentals Registers 1

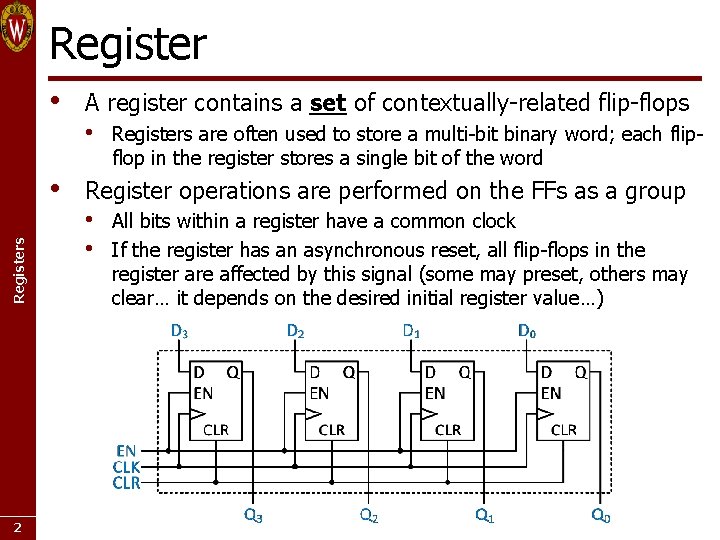

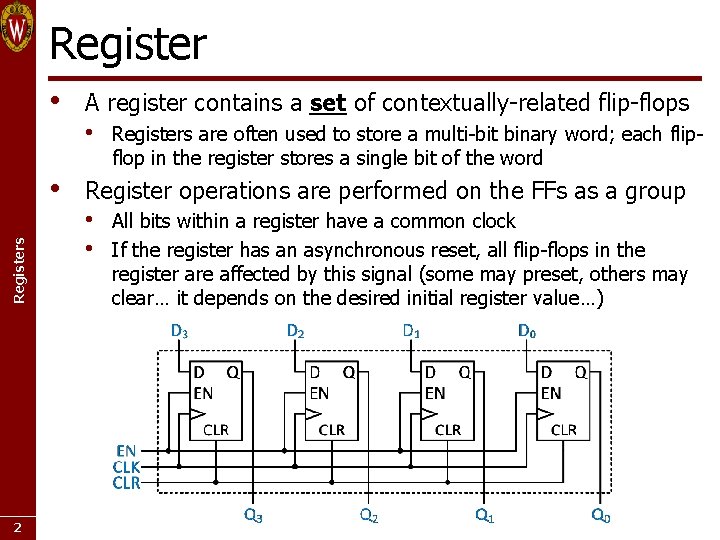

Register • Registers • 2 A register contains a set of contextually-related flip-flops • Registers are often used to store a multi-bit binary word; each flipflop in the register stores a single bit of the word Register operations are performed on the FFs as a group • • All bits within a register have a common clock If the register has an asynchronous reset, all flip-flops in the register are affected by this signal (some may preset, others may clear… it depends on the desired initial register value…)

Why Use Registers? Registers • • How would you design a 64 -bit up/down counter? • Thinking about the individual states of the counter isn’t useful! • • • 3 Draw a state diagram with 264 states? • 264 = 18, 446, 744, 073, 709, 551, 616 (!) Instead, think of a 64 -bit value stored in a register Connect a 64 -bit incrementer/decrementer to produce the next value to be stored in the register Use the up/down signal to control the incrementer/decrementer

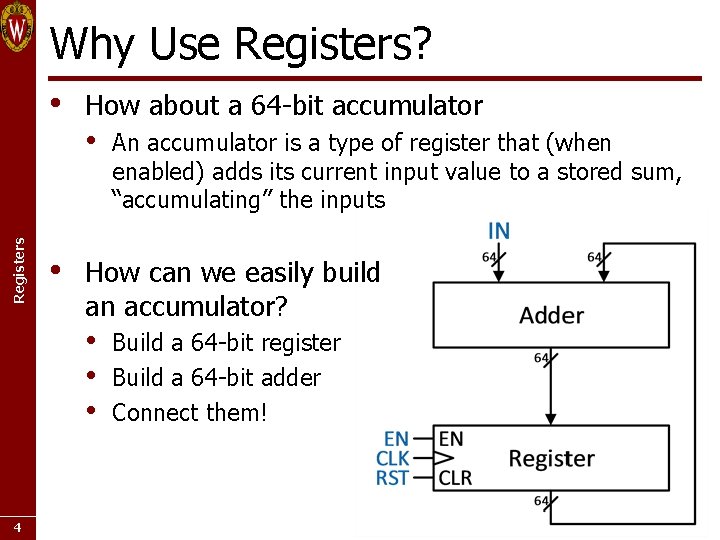

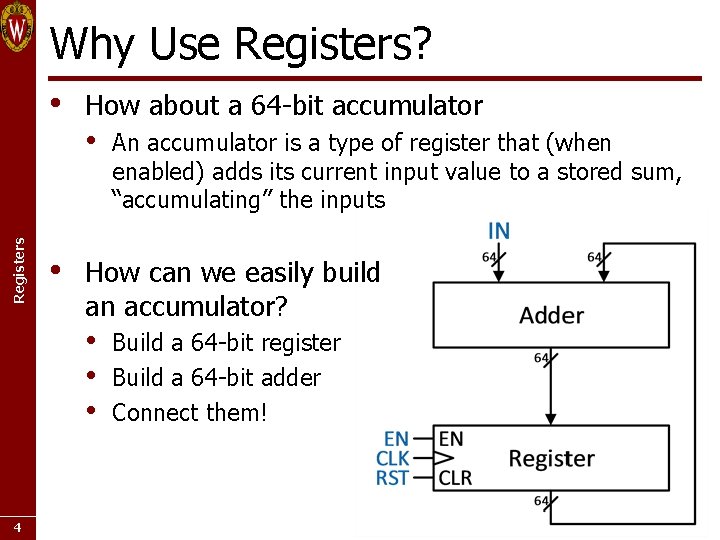

Why Use Registers? Registers • • How about a 64 -bit accumulator • How can we easily build an accumulator? • • • 4 An accumulator is a type of register that (when enabled) adds its current input value to a stored sum, “accumulating” the inputs Build a 64 -bit register Build a 64 -bit adder Connect them!

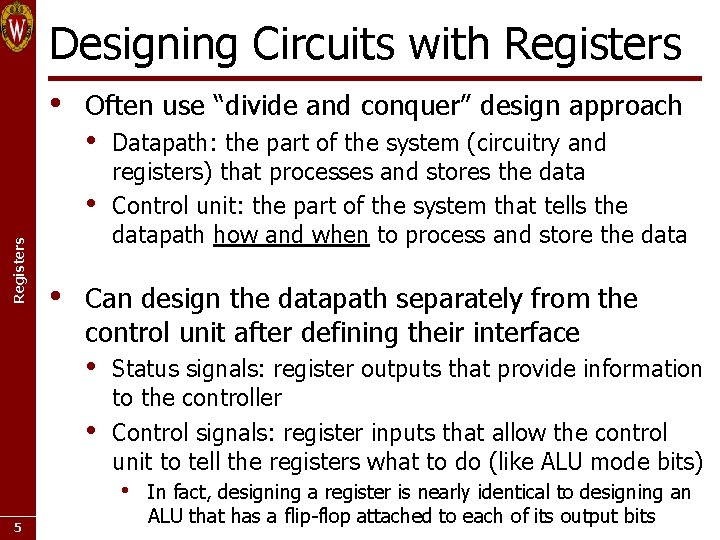

Designing Circuits with Registers • Often use “divide and conquer” design approach • Registers • • Datapath: the part of the system (circuitry and registers) that processes and stores the data Control unit: the part of the system that tells the datapath how and when to process and store the data Can design the datapath separately from the control unit after defining their interface • • Status signals: register outputs that provide information to the controller Control signals: register inputs that allow the control unit to tell the registers what to do (like ALU mode bits) • 5 In fact, designing a register is nearly identical to designing an ALU that has a flip-flop attached to each of its output bits

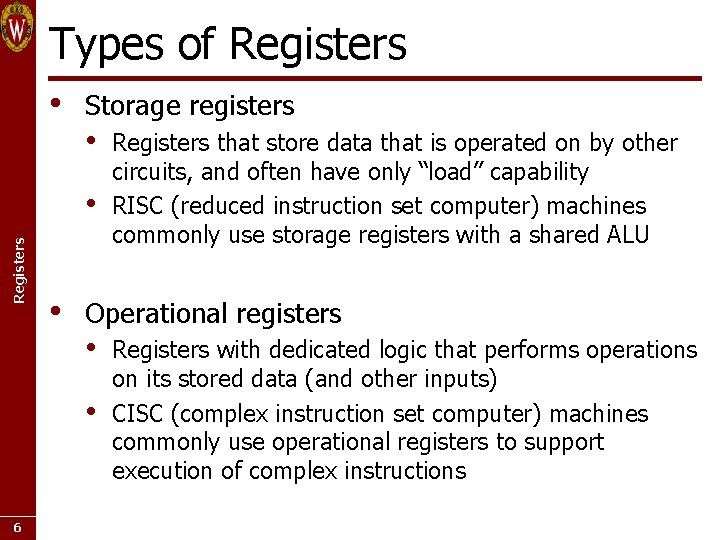

Types of Registers • Storage registers • Registers • • Operational registers • • 6 Registers that store data that is operated on by other circuits, and often have only “load” capability RISC (reduced instruction set computer) machines commonly use storage registers with a shared ALU Registers with dedicated logic that performs operations on its stored data (and other inputs) CISC (complex instruction set computer) machines commonly use operational registers to support execution of complex instructions

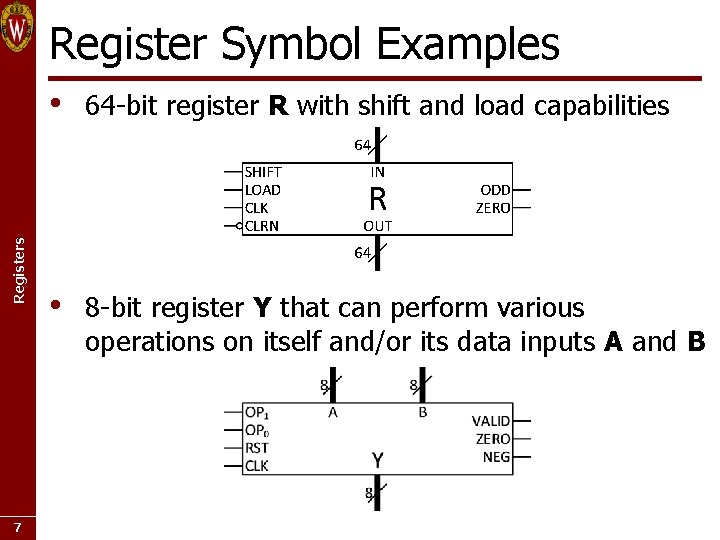

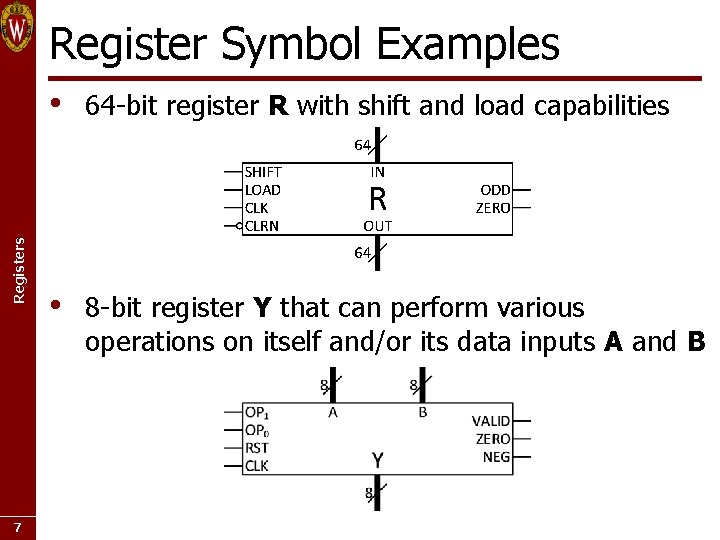

Registers Register Symbol Examples 7 • 64 -bit register R with shift and load capabilities • 8 -bit register Y that can perform various operations on itself and/or its data inputs A and B

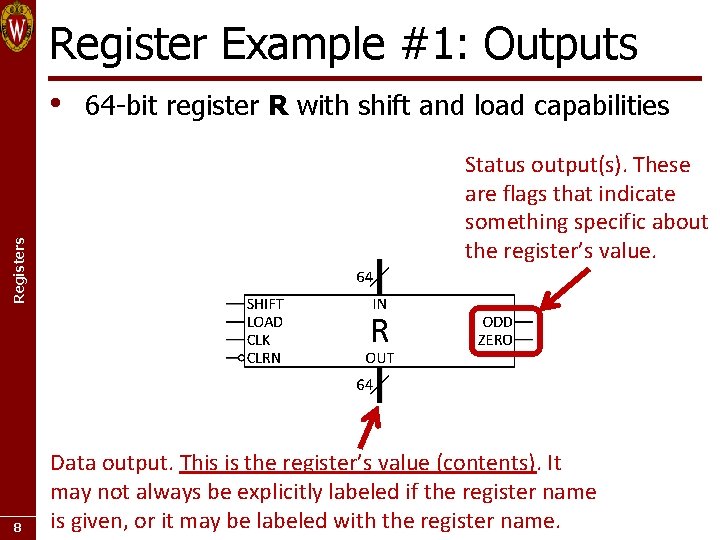

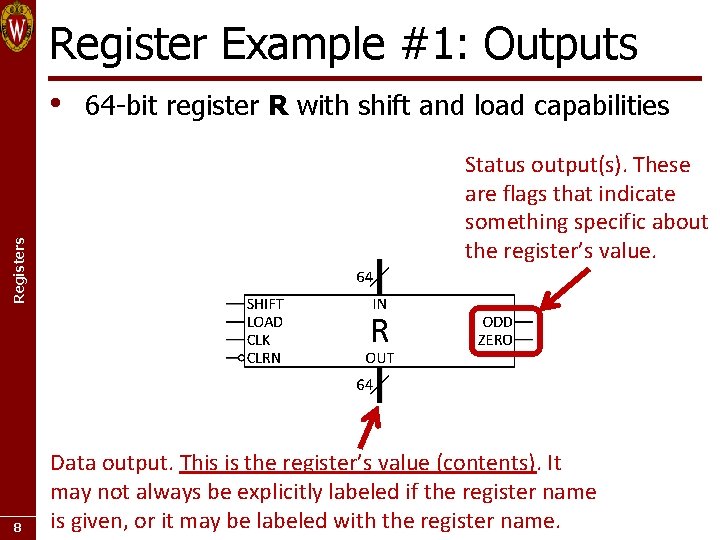

Register Example #1: Outputs Registers • 8 64 -bit register R with shift and load capabilities Status output(s). These are flags that indicate something specific about the register’s value. Data output. This is the register’s value (contents). It may not always be explicitly labeled if the register name is given, or it may be labeled with the register name.

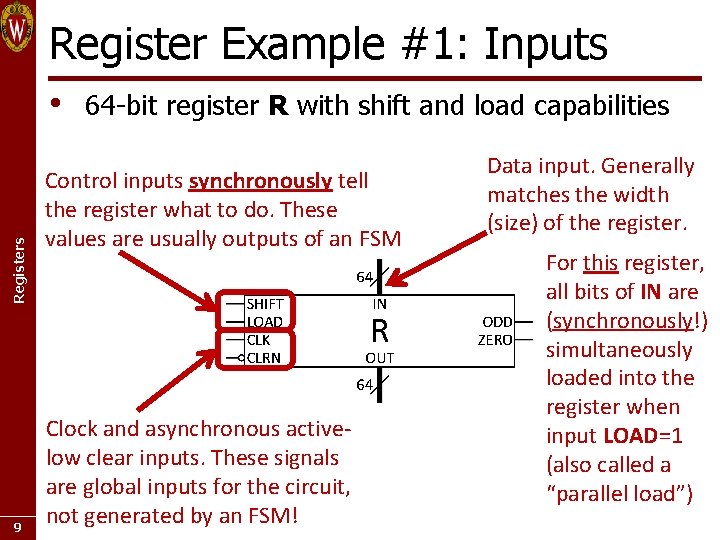

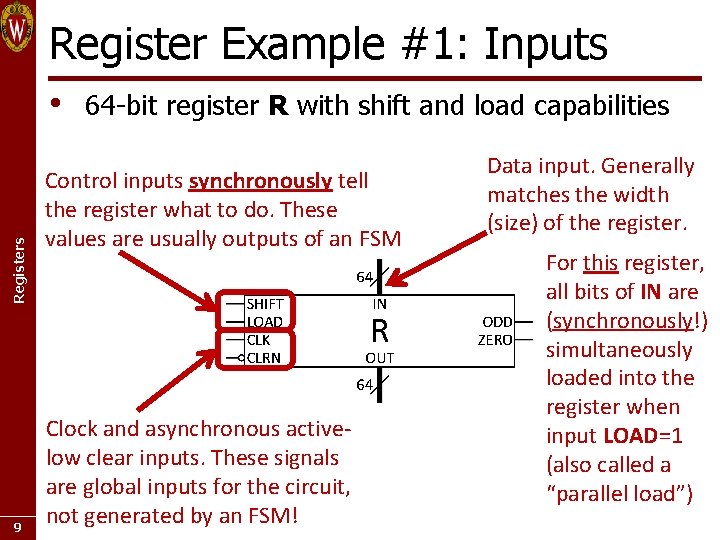

Register Example #1: Inputs Registers • 9 64 -bit register R with shift and load capabilities Control inputs synchronously tell the register what to do. These values are usually outputs of an FSM Clock and asynchronous activelow clear inputs. These signals are global inputs for the circuit, not generated by an FSM! Data input. Generally matches the width (size) of the register. For this register, all bits of IN are (synchronously!) simultaneously loaded into the register when input LOAD=1 (also called a “parallel load”)

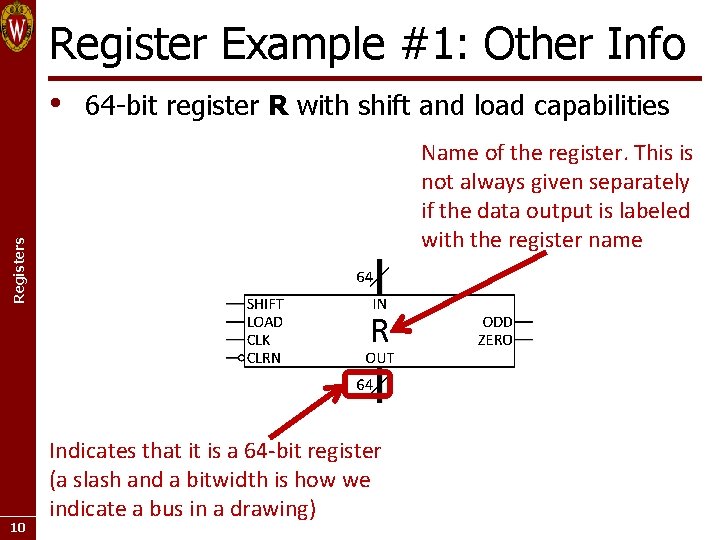

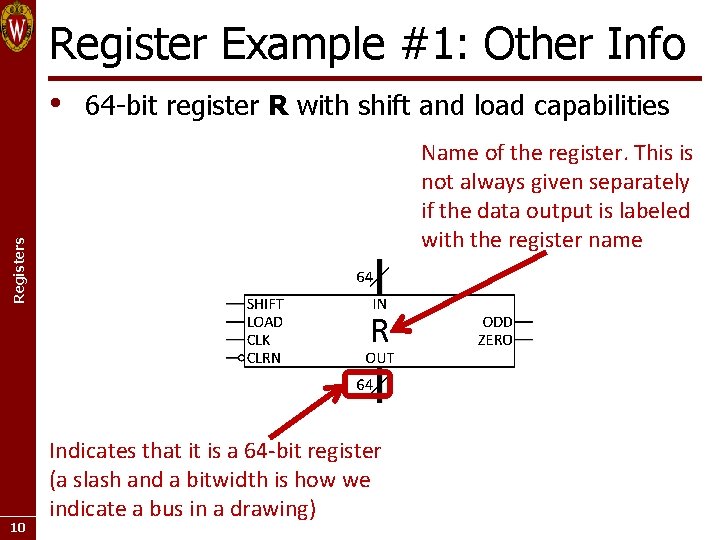

Register Example #1: Other Info • 64 -bit register R with shift and load capabilities Registers Name of the register. This is not always given separately if the data output is labeled with the register name 10 Indicates that it is a 64 -bit register (a slash and a bitwidth is how we indicate a bus in a drawing)

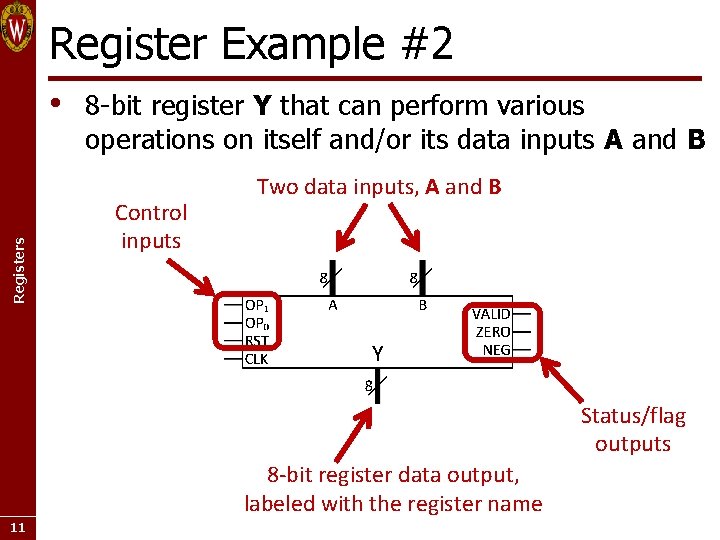

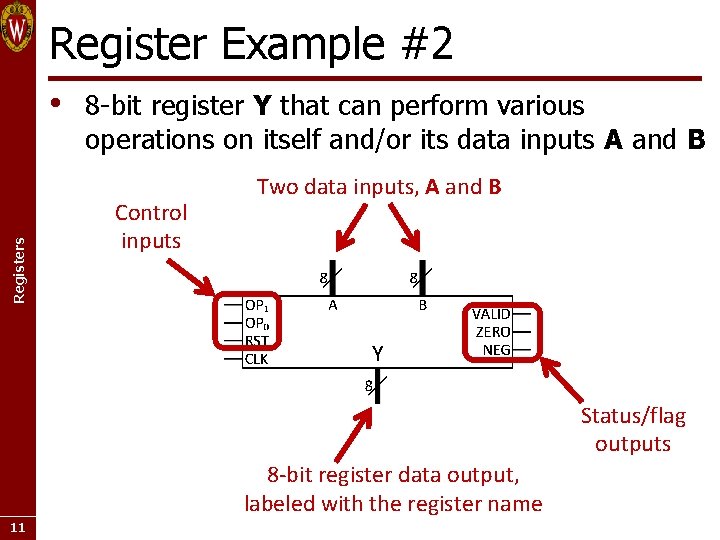

Register Example #2 Registers • 8 -bit register Y that can perform various operations on itself and/or its data inputs A and B Control inputs Two data inputs, A and B Status/flag outputs 8 -bit register data output, labeled with the register name 11

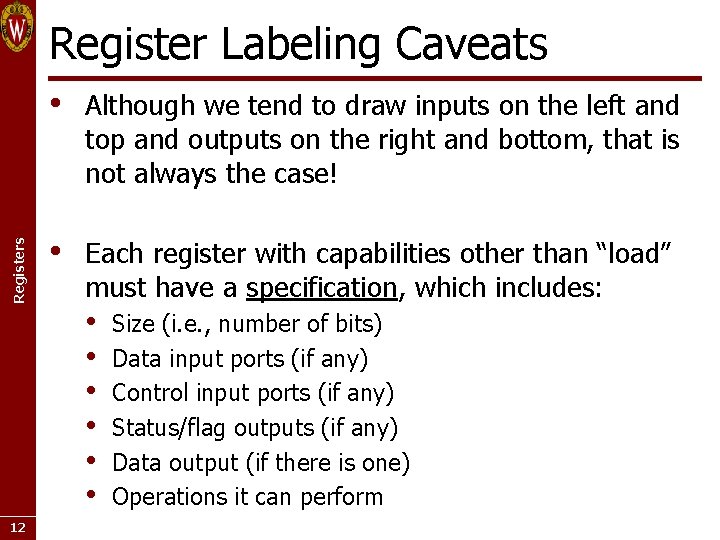

Registers Register Labeling Caveats • Although we tend to draw inputs on the left and top and outputs on the right and bottom, that is not always the case! • Each register with capabilities other than “load” must have a specification, which includes: • • • 12 Size (i. e. , number of bits) Data input ports (if any) Control input ports (if any) Status/flag outputs (if any) Data output (if there is one) Operations it can perform

Registers ECE 352 Digital System Fundamentals Registers 13