P 09311 Interface for MultiPurpose DriverData Acquisition System

- Slides: 8

P 09311: Interface for Multi-Purpose Driver/Data Acquisition System Adam Van Fleet Project Leader, EE David Howe Electrical Engineer DAQ Hardware Development USB & DAQ Hardware Design Mike Doroski Computer Engineer Andrew Weida Computer Engineer TJ Antonoff Computer Engineer FPGA-VHDL Design Bluetooth-VHDL & GUI Design USB-VHDL Design Sponsor: Dr. Marcin Lukowiak Rochester Institute of Technology Department of Computer Engineering

Project Overview • Main Goal: Investigate and implement a reliable FPGA interface, utilizing various communication channels, for the multi-purpose driver/data acquisition (DAQ) system designed in P 08311. • Key high level customer needs / engineering specs: – Graphical User Interface (GUI) Utilizes Windows OS Displays Connection Status Displays Connection Speed – USB Communication Channel 1. 5 -12 Mbps Transfer Rate 0% Data Transfer Loss – Bluetooth Comm. Channel 1. 2 -230 kbps Transfer Rate 0% Data Transfer Loss – Meet all P 08311 Design Req’s

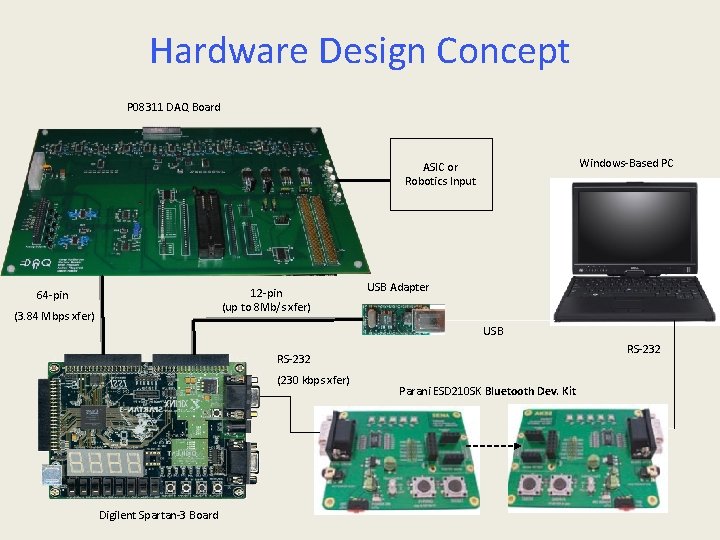

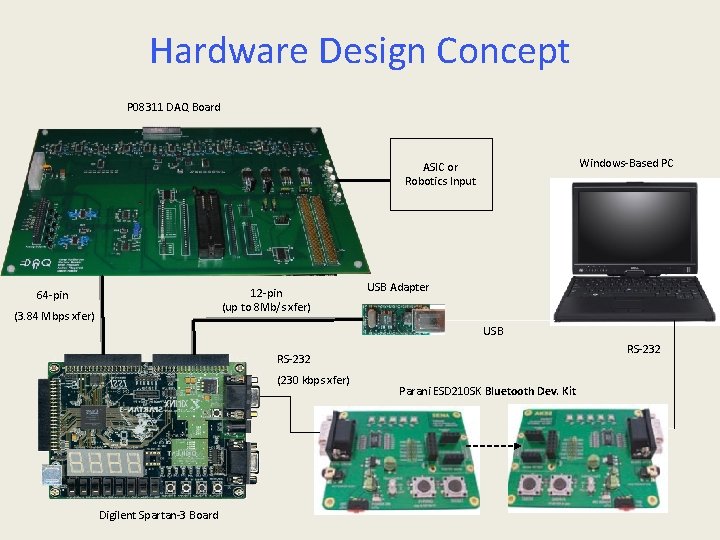

Hardware Design Concept P 08311 DAQ Board Windows-Based PC ASIC or Robotics Input 12 -pin (up to 8 Mb/s xfer) 64 -pin (3. 84 Mbps xfer) USB Adapter USB RS-232 (230 kbps xfer) Digilent Spartan-3 Board Parani ESD 210 SK Bluetooth Dev. Kit

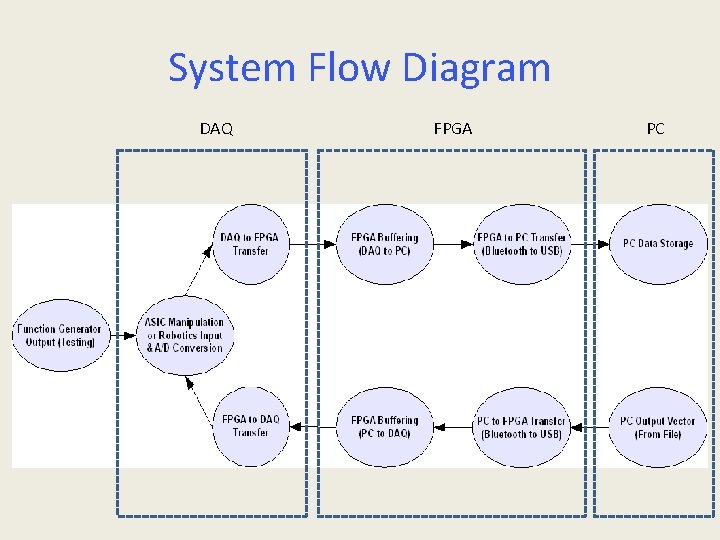

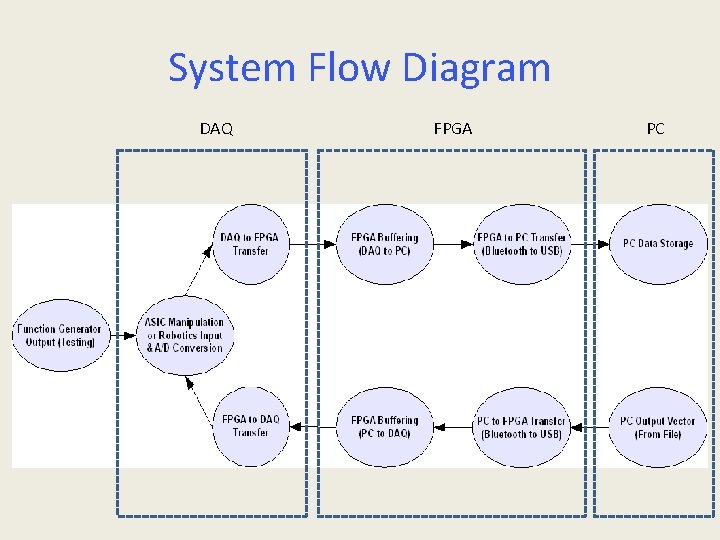

System Flow Diagram DAQ FPGA PC `

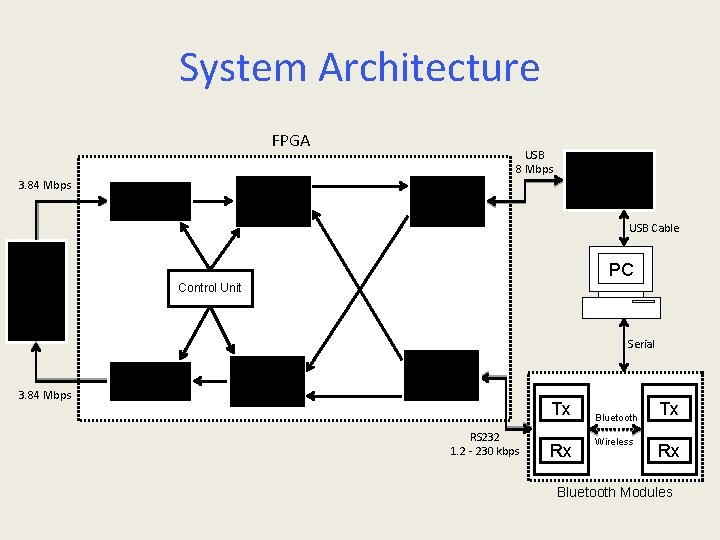

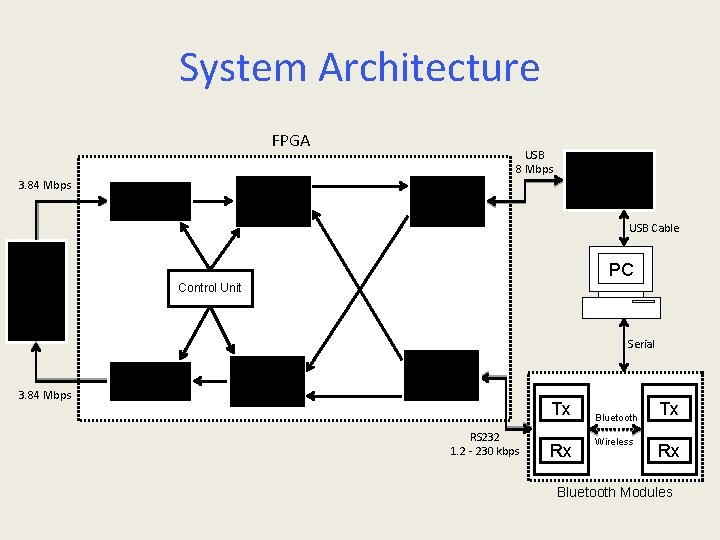

System Architecture FPGA 3. 84 Mbps Input Conditioning Output Subsystem USB 8 Mbps USB FIFO USB Data Routing Logic USB Cable PC DAQ Control Unit Serial 3. 84 Mbps Output Conditioning Input Subsystem UART Tx RS 232 1. 2 - 230 kbps Rx Bluetooth Wireless Tx Rx Bluetooth Modules

Major Risk Assessment • Risk: Possibility for data transmission bottlenecks at FPGA interfaces – Action: Calculation of data rates (min and max) to ensure proper data flow • Risk: Interfacing FPGA to DAQ to ensure properation / data flow – Action: Preliminary testing of DAQ board, research into hardware connection

Current State of Design • Customer needs are met with design • System design and subsystems meet project specifications • Status: – Mock-Up of GUI designed has been programmed in C# – UART for bluetooth has been programmed in VHDL with communication to FPGA validated – Initial coding of USB logic and FPGA control logic /buffers under way, verification pending

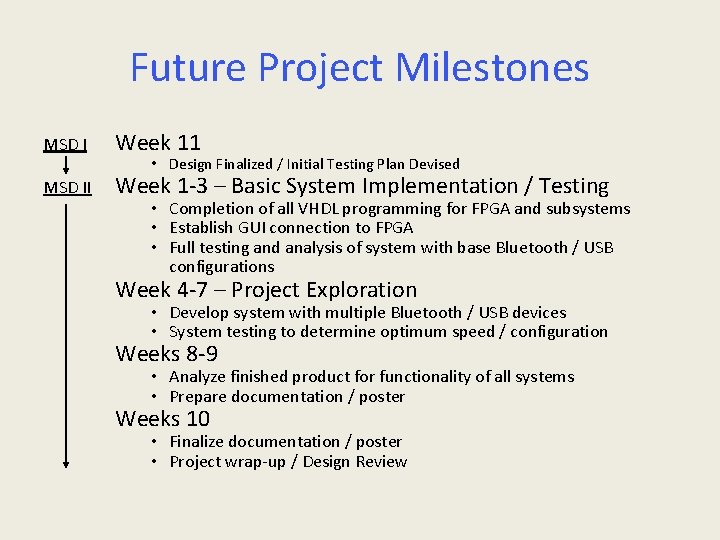

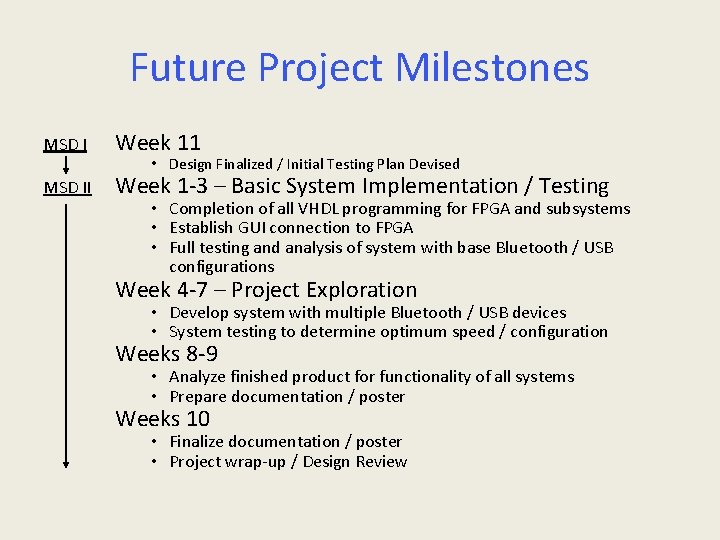

Future Project Milestones MSD I Week 11 MSD II Week 1 -3 – Basic System Implementation / Testing • Design Finalized / Initial Testing Plan Devised • Completion of all VHDL programming for FPGA and subsystems • Establish GUI connection to FPGA • Full testing and analysis of system with base Bluetooth / USB configurations Week 4 -7 – Project Exploration • Develop system with multiple Bluetooth / USB devices • System testing to determine optimum speed / configuration Weeks 8 -9 • Analyze finished product for functionality of all systems • Prepare documentation / poster Weeks 10 • Finalize documentation / poster • Project wrap-up / Design Review