Motivation and Project Goals Goals Propose an efficient

- Slides: 9

Motivation and Project Goals • Goals: – Propose an efficient architecture for encoding and decoding of the LDPC codes, and prove its feasibility by implementing it on an FPGA. – Based on the FPGA implementation, gain insight into the behavior of the LDPC codes at very low error rates and propose novel constructions void of error floors.

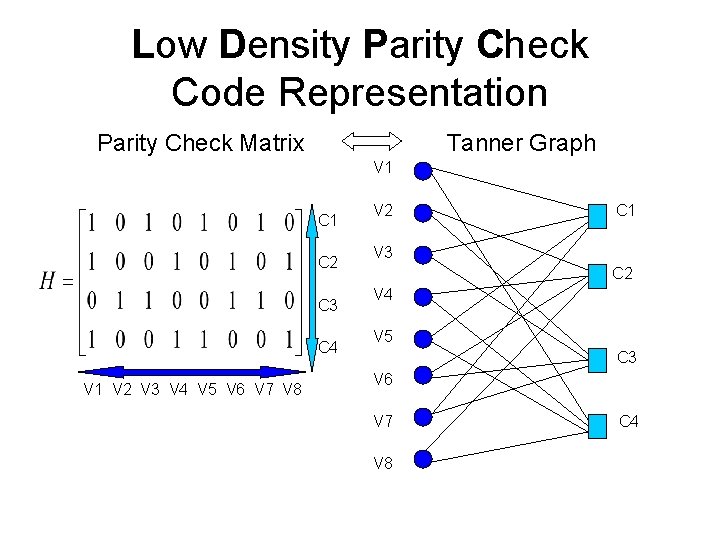

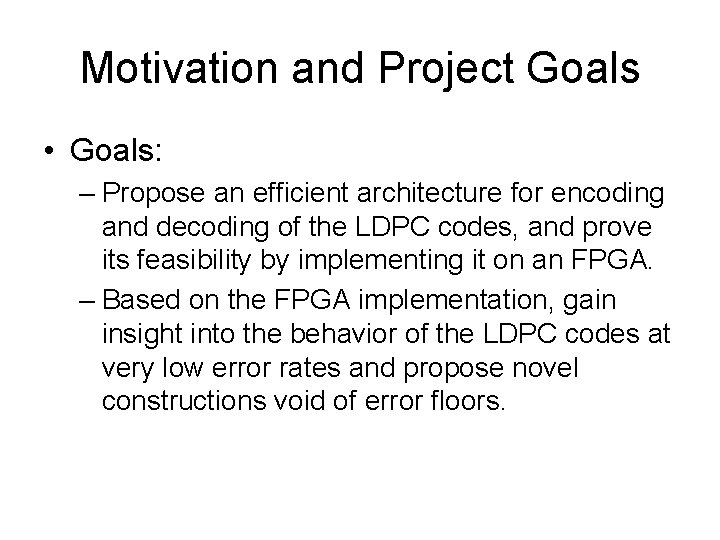

Low Density Parity Check Code Representation Parity Check Matrix Tanner Graph V 1 C 2 C 3 C 4 V 1 V 2 V 3 V 4 V 5 V 6 V 7 V 8 V 2 C 1 V 3 C 2 V 4 V 5 C 3 V 6 V 7 V 8 C 4

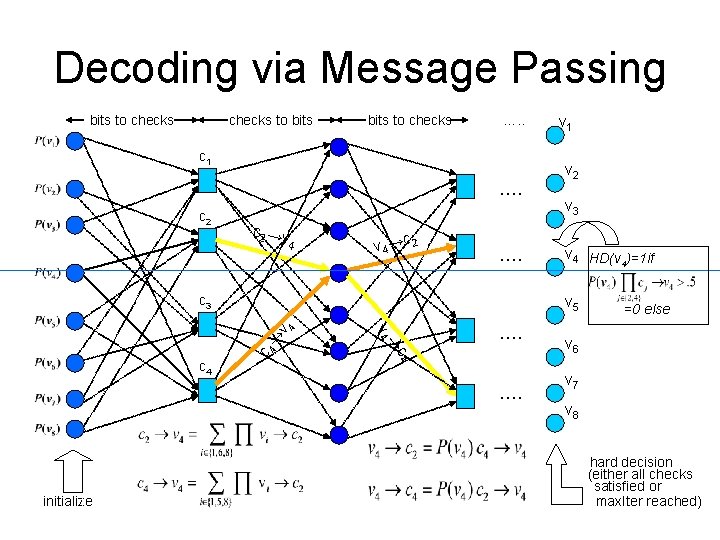

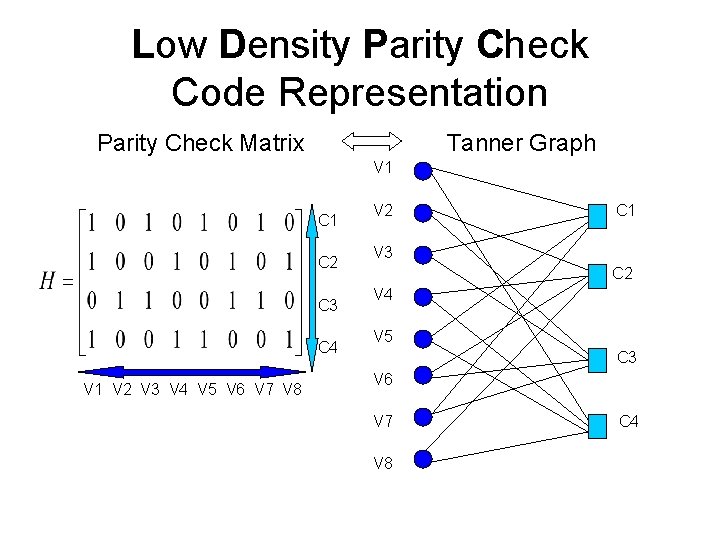

Decoding via Message Passing bits to checks to bits to checks …. . c 1 …. c 2 →v 4 v 4→c 2 …. c 3 4 v 4→ c 4 c …. …. initialize v 2 v 3 v 4 HD(v 4)=1 if v 5 → v 4 c 4 v 1 =0 else v 6 v 7 v 8 hard decision (either all checks satisfied or max. Iter reached)

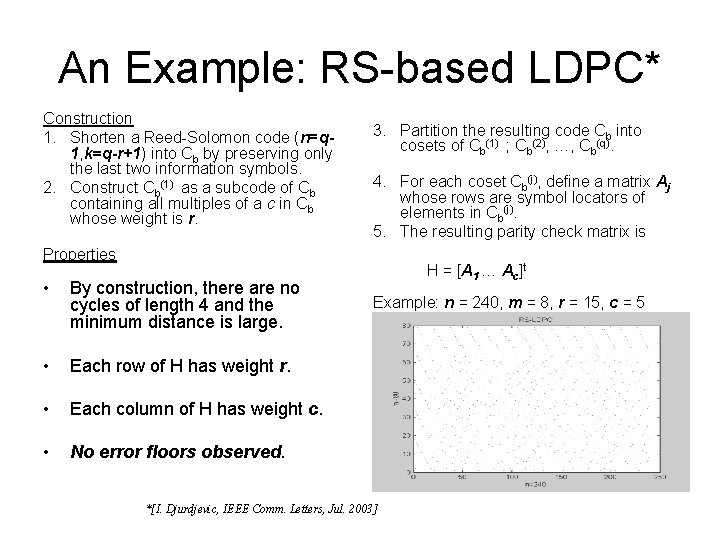

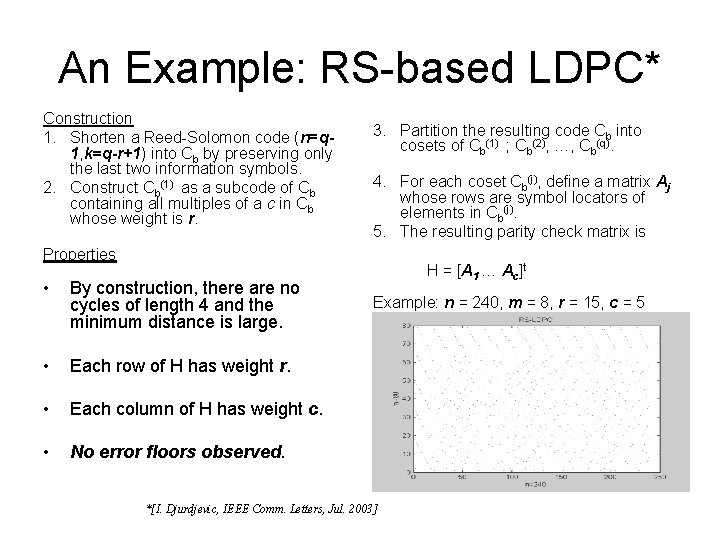

An Example: RS-based LDPC* Construction 1. Shorten a Reed-Solomon code (n=q 1, k=q-r+1) into Cb by preserving only the last two information symbols. 2. Construct Cb(1) as a subcode of Cb containing all multiples of a c in Cb whose weight is r. 3. Partition the resulting code Cb into cosets of Cb(1) ; Cb(2), …, Cb(q). 4. For each coset Cb(j), define a matrix Aj whose rows are symbol locators of elements in Cb(j). 5. The resulting parity check matrix is Properties • By construction, there are no cycles of length 4 and the minimum distance is large. • Each row of H has weight r. • Each column of H has weight c. • No error floors observed. H = [A 1 … Ac]t Example: n = 240, m = 8, r = 15, c = 5 *[I. Djurdjevic, IEEE Comm. Letters, Jul. 2003]

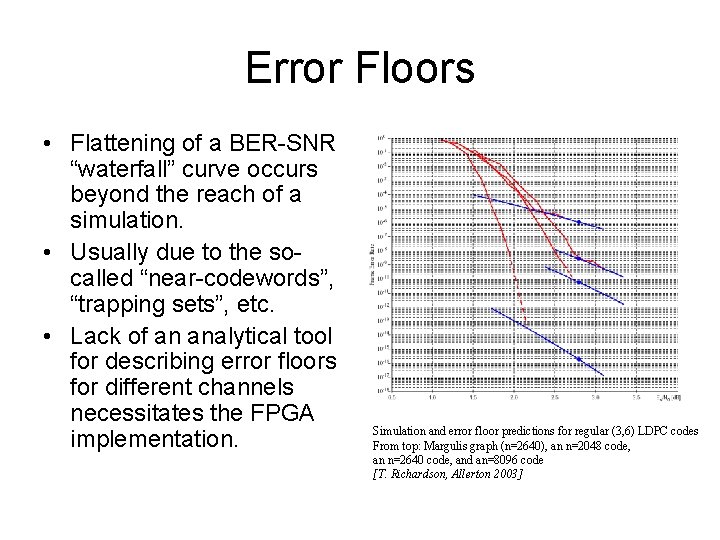

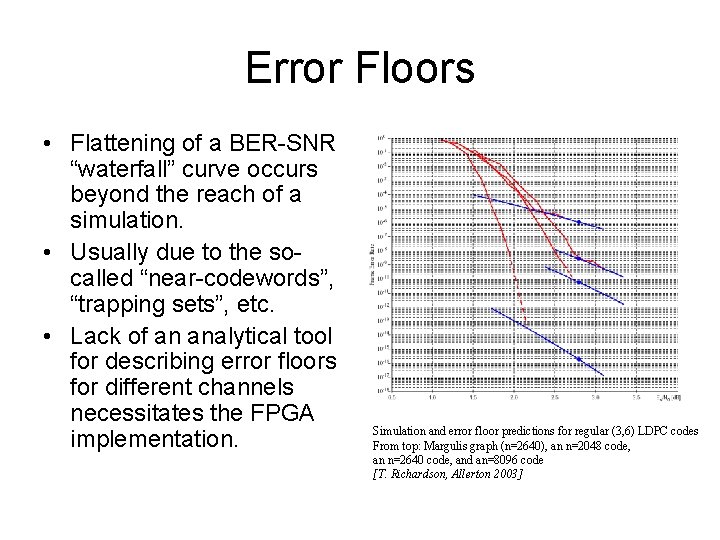

Error Floors • Flattening of a BER-SNR “waterfall” curve occurs beyond the reach of a simulation. • Usually due to the socalled “near-codewords”, “trapping sets”, etc. • Lack of an analytical tool for describing error floors for different channels necessitates the FPGA implementation. Simulation and error floor predictions for regular (3, 6) LDPC codes From top: Margulis graph (n=2640), an n=2048 code, an n=2640 code, and an=8096 code [T. Richardson, Allerton 2003]

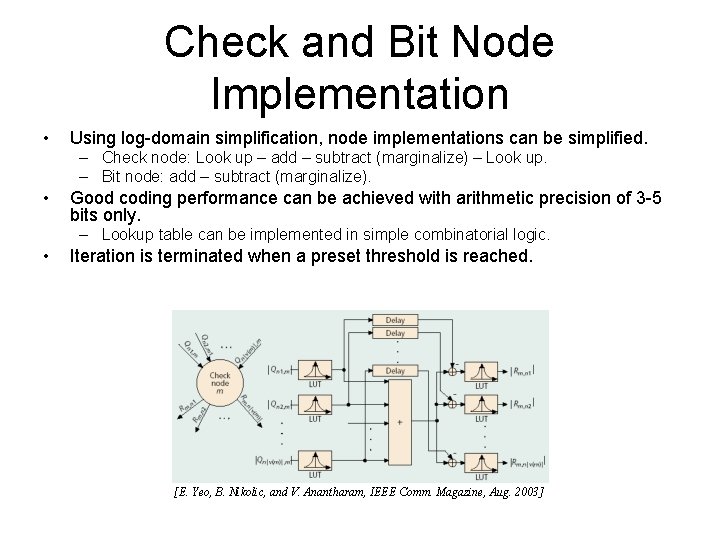

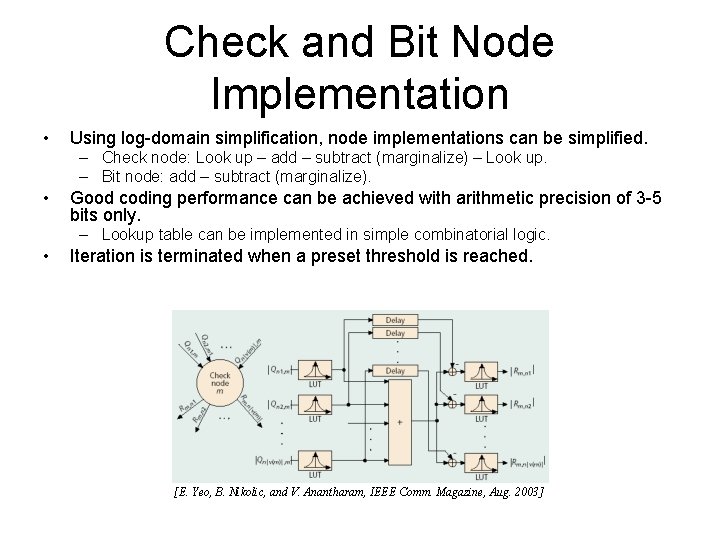

Check and Bit Node Implementation • Using log-domain simplification, node implementations can be simplified. – Check node: Look up – add – subtract (marginalize) – Look up. – Bit node: add – subtract (marginalize). • Good coding performance can be achieved with arithmetic precision of 3 -5 bits only. – Lookup table can be implemented in simple combinatorial logic. • Iteration is terminated when a preset threshold is reached. [E. Yeo, B. Nikolic, and V. Anantharam, IEEE Comm. Magazine, Aug. 2003]

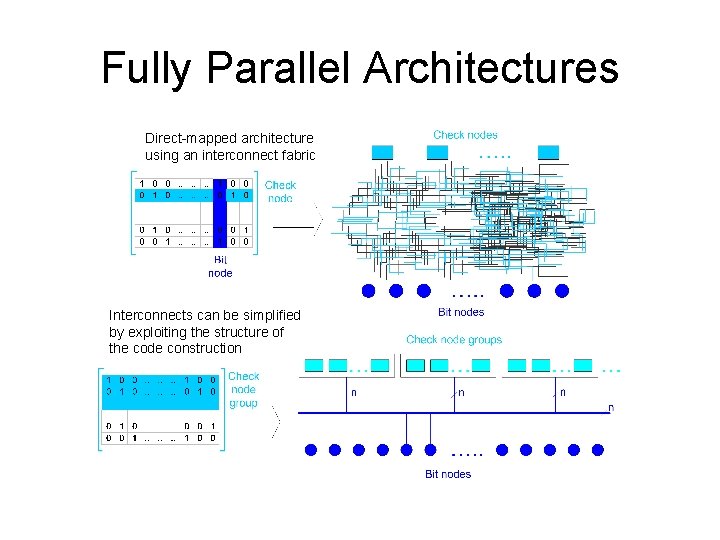

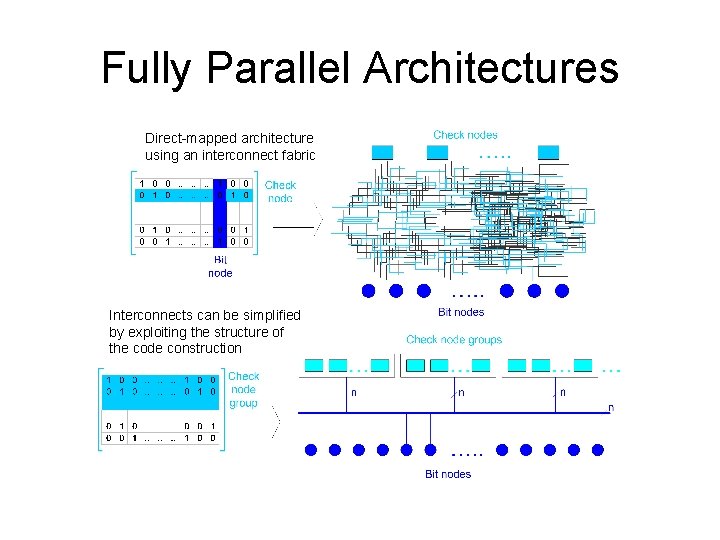

Fully Parallel Architectures Direct-mapped architecture using an interconnect fabric Interconnects can be simplified by exploiting the structure of the code construction

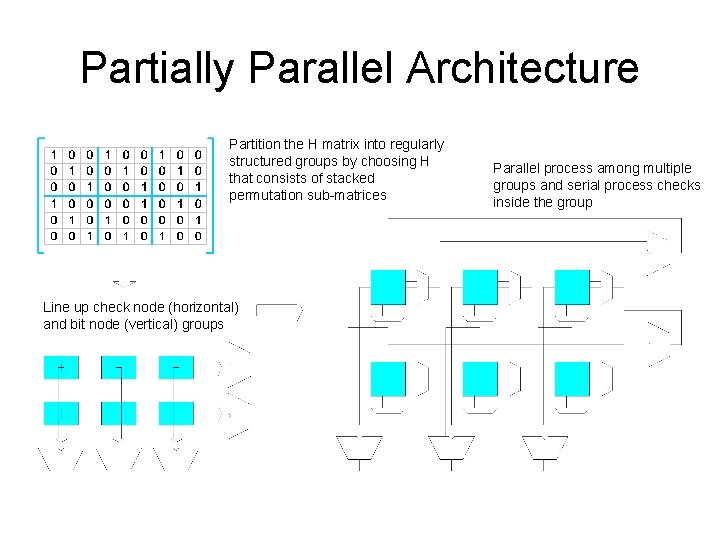

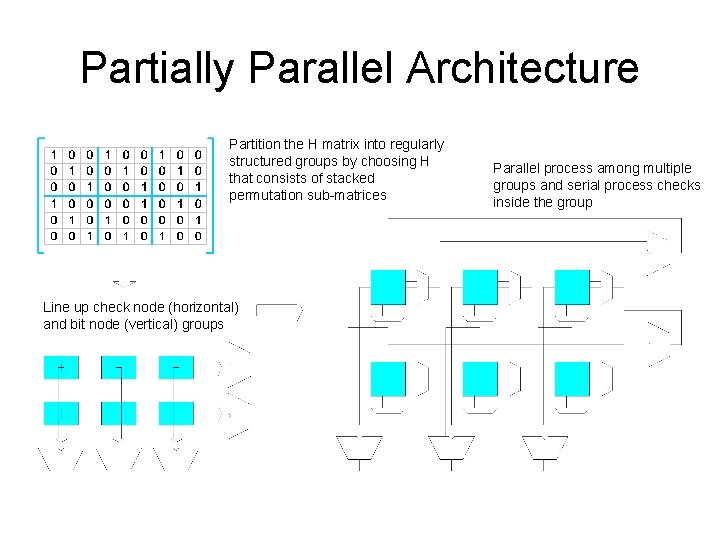

Partially Parallel Architecture Partition the H matrix into regularly structured groups by choosing H that consists of stacked permutation sub-matrices Line up check node (horizontal) and bit node (vertical) groups Parallel process among multiple groups and serial process checks inside the group

Future Research • Code construction – Experiment with existing code constructions and investigate the nature of error floors. • Architectural exploration – Flexible and efficient architecture which allows for fast prototyping of different code constructions. • Error floor simulation – Real-time hardware emulation of codes to verify BER performance.